Заявка относится к технике обработки сигналов радиолокационных станций (РЛС).

Из уровня техники известен некогерентный приемник (Авторское свидетельство СССР №1525933, Н 04 L 17/30, 1989) с повышенной помехоустойчивостью, но он не производит обработку фазовой структуры сигнала.

Известно устройство распознавания движущихся объектов (Свидетельство РФ на полезную модель №21250, G 01 K 9/00, 2001), которое определяет класс объекта, но не решает задачу расширения динамического диапазона приемника.

Радиоприемное устройство когерентной РЛС (Заявка РФ на изобретение №2000120020, бюллетень "Изобретения, полезные модели" №16, 2002, с.126) не обеспечивает цифрового гетеродинирования обрабатываемого сигнала и имеет ошибку при цифровой корректировке квадратур принимаемых сигналов.

Наиболее близким по технической сущности является некогерентный обнаружитель сигналов в шумах (Заявка РФ на изобретение №200102468, бюллетень "Изобретения, полезные модели" №8, 2002, с.71), включающий некогерентный гетеродин, фазосдвигающую цепочку, аналого-цифровой преобразователь, первый и второй смесители частот, первый и второй фильтры промежуточной частоты, первые входы упомянутых смесителей соединены с входом сигнала, второй вход первого смесителя соединен с выходом гетеродина через фазосдвигающую цепочку, второй вход второго смесителя частоты соединен также с выходом гетеродина, выходы первого и второго смесителей соединены с входами первого и второго фильтров промежуточной частоты соответственно, в схему введены первый и второй компараторы напряжений, логическая схема ″Исключающее ″ИЛИ″, счетчик-делитель на 2n, N-разрядный накапливающий сумматор, третий компаратор чисел и m-разрядный регистр, выход одного из фильтров промежуточной частоты соединен с сигнальным входом аналого-цифрового преобразователя и неинвертирующим входом первого компаратора напряжений, выход второго фильтра соединен с неинвертирующим входом второго компаратора напряжений, инвертирующие входы упомянутых компараторов соединены с нулевым потенциалом, выходы первого и второго компараторов соединены с первым и вторым входами логической схемы ″Исключающее “ИЛИ″, выход упомянутой схемы соединен с тактовым входом упомянутого аналого-цифрового преобразователя и с входом счетчика-делителя на n, шина цифрового выхода упомянутого аналого-цифрового преобразователя без знакового разряда соединена с входом N-разрядного накапливающего сумматора, m=N-n выходных старших разрядов накапливающего сумматора соединены с входом третьего компаратора чисел, второй вход третьего компаратора чисел соединен с выходом m-разрядного регистра, в который записан двоичный код порога, управляющий вход упомянутого компаратора чисел соединен с выходом упомянутого счетчика-делителя на n.

Однако при его использовании он не обеспечивает оптимальной фильтрации (временного сжатия фазо-кодо-манипулированного сигнала) и когерентной обработки принимаемого сигнала, так как это схемно-конструктивно в известном техническом решении не предусмотрено.

Технический результат предлагаемого технического решения направлен на расширение функциональных возможностей и улучшение основных технических параметров РЛС.

Технический результат достигается тем, что радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала содержит первый аналого-цифровой преобразователь, первый и второй смесители частот, первый N-разрядный накапливающий сумматор, первый и второй компараторы напряжения, а в первый канал приема входит устройство квадратурного фазового детектирования А1 и устройство предварительной обработки A3, при этом устройство квадратурного фазового детектирования А1 первого канала содержит сумматор, блок усилителей с временной автоматической регулировкой усиления, первый и второй смесители частот, первый и второй операционные усилители, первый и второй компараторы напряжений, первый и второй фильтры низких частот, первый и второй интеграторы, первую и вторую схемы контроля, схему формирования сигнала исправности, в свою очередь устройство предварительной обработки A3 первого канала состоит из первого и второго аналого-цифрового преобразователя, первого и второго цифроаналоговых преобразователей, устройства цифрового гетеродинирования, постоянного запоминающего устройства цифрового гетеродинирования, первого и второго реверсивных счетчиков, первого и второго накапливающих N-разрядных сумматоров, первого и второго мультиплексоров, формирователя адреса записи, первого и второго оперативных запоминающих устройств через-периодной обработки, формирователя адреса чтения, первого и второго оптимальных фильтров, формирователя опорных сигналов, первой и второй микросхем FiFo "первый вошел, первый вышел", устройства управления, первого и второго коммутаторов, при этом второй канал приема содержит устройство квадратурного фазового детектирования А2 и устройство предварительной обработки А4, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования А1 первого канала и устройству предварительной обработки A3 первого канала, а также в радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала включены первый и второй дешифраторы, кварцевый генератор, преобразователь уровня, делитель частоты, полосовой фильтр, дифференцирующая цепочка, интегрирующая цепочка, первый и второй резонансные усилители, третий и четвертый мультиплексоры, синхронизатор сигналов, при этом вход приемника по первому каналу соединен с первым входом устройства квадратурного фазового детектирования А1 первого канала, первый выход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом устройства предварительной обработки A3 первого канала, первый выход устройства предварительной обработки A3 первого канала соединен с первым входом третьего мультиплексора, выход третьего мультиплексора соединен с разъемом выходного сигнала реальной составляющей, разъем входного опорного сигнала соединен с входом делителя частоты и входом преобразователя уровня, выход делителя частоты соединен с входом полосового фильтра, выход полосового фильтра соединен с входом дифференцирующей цепочки и входом интегрирующей цепочки, выход дифференцирующей цепочки соединен с входом первого резонансного усилителя, первый выход резонансного усилителя соединен со вторым входом устройства квадратурного фазового детектирования А1 первого канала, второй выход первого резонансного усилителя соединен со вторым входом устройства квадратурного фазового детектирования А2 второго канала, выход интегрирующей цепочки соединен с входом второго резонансного усилителя, первый выход второго резонансного усилителя соединен с третьим входом устройства квадратурного фазового детектирования А1 первого канала, второй выход второго резонансного усилителя соединен с третьим входом устройства квадратурного фазового детектирования А2 второго канала, первый выход устройства квадратурного фазового детектирования А2 второго канала соединен со вторым входом устройства предварительной обработки А4 второго канала, первый выход устройства предварительной обработки А4 второго канала соединен со вторым входом четвертого мультиплексора, выход четвертого мультиплексора соединен с разъемом выходного сигнала мнимой составляющей, первый выход синхронизатора сигналов соединен с входом кварцевого генератора, первый выход кварцевого генератора соединен с четвертым входом устройства квадратурного фазового детектирования А1 первого канала, второй выход кварцевого генератора соединен с четвертым входом устройства квадратурного фазового детектирования А2 второго канала, второй выход синхронизатора сигналов соединен с входом первого дешифратора, выход первого дешифратора соединен с пятым входом устройства квадратурного фазового детектирования А1 первого канала, третий выход синхронизатора сигналов соединен с входом второго дешифратора, выход второго дешифратора соединен с пятым входом устройства квадратурного фазового детектирования А2 второго канала, выход преобразователя уровня соединен с первым входом синхронизатора сигналов, второй выход устройства квадратурного фазового детектирования А2 второго канала соединен с третьим входом синхронизатора сигналов, третий выход устройства квадратурного фазового детектирования А2 второго канала соединен с третьим входом устройства предварительной обработки А4 второго канала, второй выход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом синхронизатора сигналов, третий выход устройства квадратурного фазового детектирования А1 первого канала соединен с третьим входом устройства предварительной обработки A3 первого канала, пятый выход синхронизатора сигналов соединен с четвертым входом устройства предварительной обработки А4 второго канала, шестой выход синхронизатора сигналов соединен с пятым входом устройства предварительной обработки А4 второго канала, седьмой выход синхронизатора сигналов соединен с шестым входом устройства предварительной обработки А4 второго канала, восьмой выход синхронизатора сигналов соединен с седьмым входом устройства предварительной обработки А4 второго канала, девятый выход синхронизатора сигналов соединен с восьмым входом устройства предварительной обработки А4 второго канала, десятый выход синхронизатора сигналов соединен с девятым входом устройства предварительной обработки А4 второго канала, одиннадцатый выход синхронизатора сигналов соединен с контактом импульса для формирования строба перестройки антенны, двенадцатый выход синхронизатора сигналов соединен с контактом сигнала запуска оконечной ступени передатчика, тринадцатый выход синхронизатора сигналов соединен с контактом сигнала, определяющего длительность импульса запуска передатчика, четырнадцатый выход синхронизатора сигналов соединен с контактом сигнала, определяющего фазу импульса запуска передатчика, пятнадцатый выход синхронизатора сигналов соединен с контактом сигнала импульса бланкирования приемника, шестнадцатый выход синхронизатора сигналов соединен с контактом импульса, сопровождающего основной сигнал, семнадцатый выход синхронизатора сигналов соединен с контактом импульса начала передачи, восемнадцатый выход синхронизатора сигналов соединен с десятым входом устройства предварительной обработки А4 второго канала, девятнадцатый выход синхронизатора сигналов соединен с третьим входом третьего мультиплексора и третьим входом четвертого мультиплексора, двадцатый выход синхронизатора сигналов соединен с четвертым входом устройства предварительной обработки A3 первого канала, двадцать первый выход синхронизатора сигналов соединен с пятым входом устройства предварительной обработки A3 первого канала, двадцать второй выход синхронизатора сигналов соединен с шестым входом устройства предварительной обработки A3 первого канала, двадцать третий выход синхронизатора сигналов соединен с седьмым входом устройства предварительной обработки A3 первого канала, двадцать четвертый выход синхронизатора сигналов соединен с восьмым входом устройства предварительной обработки A3 первого канала, двадцать пятый выход синхронизатора сигналов соединен с девятым входом устройства предварительной обработки A3 первого канала, двадцать шестой выход синхронизатора сигналов соединен с десятым входом устройства предварительной обработки A3 первого канала, разъем магистрали параллельной информации соединен с первым и одиннадцатым входами устройства предварительной обработки A3 первого канала, с первым и одиннадцатым входами устройства предварительной обработки А4 второго канала и с четвертым выходом синхронизатора сигналов, второй выход устройства предварительной обработки A3 первого канала соединен с первым входом четвертого мультиплексора, второй выход устройства предварительной обработки А4 второго канала соединен со вторым входом третьего мультиплексора, в устройстве квадратурного фазового детектирования А1 первого канала первый вход соединен с первым входом сумматора, выход сумматора соединен с первым входом блока усилителей с временной автоматической регулировкой усиления, выход блока усилителей с временной автоматической регулировкой усиления соединен с первым входом первого смесителя частот и с первым входом второго смесителя частот, выход первого смесителя частот соединен с первым входом первого операционного усилителя, выход первого операционного усилителя соединен с входом первого фильтра низких частот, выход первого фильтра низких частот соединен с первым выходом устройства квадратурного фазового детектирования А1 первого канала, с входом первой схемы контроля и с входом первого интегратора, выход первого интегратора соединен с входом первого компаратора напряжений, выход первого компаратора напряжений соединен со вторым входом первого операционного усилителя, выход второго смесителя частот соединен с первым входом второго операционного усилителя, выход второго операционного усилителя соединен с входом второго фильтра низких частот, выход фильтра низких частот соединен с третьим выходом устройства квадратурного фазового детектирования А1 первого канала, с входом второй схемы контроля и с входом второго интегратора, выход второго интегратора соединен с входом второго компаратора напряжений, выход второго компаратора напряжений соединен со вторым входом второго операционного усилителя, выход первой схемы контроля соединен с первым входом схемы формирования сигнала исправности, выход второй схемы контроля соединен со вторым входом схемы формирования сигнала исправности, выход схемы формирования сигнала исправности соединен со вторым выходом устройства квадратурного фазового детектирования А1 первого канала, четвертый вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом сумматора, второй вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом первого смесителя частот, третий вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом второго смесителя частот, пятый вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом блока усилителей с временной автоматической регулировкой усиления, разъем входного сигнала второго канала соединен с первым входом устройства фазового детектирования А2 второго канала, первый вход устройства предварительной обработки A3 первого канала соединен с третьим входом первого мультиплексора, второй вход устройства предварительной обработки A3 первого канала соединен со вторым входом первого аналого-цифрового преобразователя, выход первого аналого-цифрового преобразователя соединен с пятым входом устройства цифрового гетеродинирования, первый выход устройства цифрового гетеродинирования соединен с первым входом первого N-разрядного накапливающего сумматора, первый выход первого N-разрядного накапливающего сумматора соединен с первым входом первого мультиплексора, выход первого мультиплексора соединен с первым входом оперативного запоминающего устройства череспериодной обработки и со вторым входом первого коммутатора, выход первого оперативного запоминающего устройства череспериодной обработки соединен с первым входом оптимального фильтра, выход первого оптимального фильтра соединен с первым входом первой микросхемы FiFo, выход первой микросхемы FiFo соединен с первым входом первого коммутатора напряжений, выход первого коммутатора напряжений соединен с первым выходом устройства предварительной обработки A3 первого канала, третий вход устройства предварительной обработки A3 первого канала соединен с первым входом второго аналого-цифрового преобразователя, выход второго аналого-цифрового преобразователя соединен со вторым входом устройства цифрового гетеродинирования, второй выход устройства цифрового гетеродинирования соединен с первым входом второго N-разрядного накапливающего сумматора, первый выход второго N-разрядного накапливающего сумматора соединен с первым входом второго мультиплексора, выход второго мультиплексора соединен с первым входом второго оперативного запоминающего устройства череспериодной обработки и со вторым входом второго коммутатора, выход второго оперативного запоминающего устройства череспериодной обработки соединен с первым входом второго оптимального фильтра, выход второго оптимального фильтра соединен с первым входом второй микросхемы FiFo, выход второй микросхемы FiFo соединен с первым входом второго коммутатора, выход второго коммутатора соединен со вторым выходом устройства предварительной обработки A3 первого канала, второй выход первого N-разрядного накапливающего сумматора соединен с первым входом первого реверсивного счетчика, выход первого реверсивного счетчика соединен с входом первого цифроаналогового преобразователя, выход первого цифроаналогового преобразователя соединен с первым входом первого аналого-цифрового преобразователя, второй выход второго N-разрядного накапливающего сумматора соединен с первым входом второго реверсивного счетчика, выход второго реверсивного счетчика соединен с входом второго цифроаналогового преобразователя, выход второго цифроаналогового преобразователя соединен со вторым входом аналого-цифрового преобразователя, четвертый вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго аналого-цифрового преобразователя, с третьим входом первого аналого-цифрового преобразователя, с первым входом устройства цифрового гетеродинирования, пятый вход устройства предварительной обработки A3 первого канала соединен с входом постоянного запоминающего устройства устройства цифрового гетеродинирования, первый выход постоянного запоминающего устройства устройства цифрового гетеродинирования соединен с третьим входом устройства цифрового гетеродинирования, второй выход постоянного запоминающего устройства цифрового гетеродинирования соединен с четвертым входом устройства цифрового гетеродинирования, шестой вход устройства предварительной обработки A3 первого канала соединен со вторым входом второго N-разрядного накапливающего сумматора и со вторым входом первого N-разрядного накапливающего сумматора, седьмой вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго N-разрядного накапливающего сумматора и с третьим входом первого N-разрядного накапливающего сумматора, восьмой вход устройства предварительной обработки A3 первого канала соединен со вторым входом второго реверсивного счетчика, со вторым входом второго мультиплексора, с входом формирователя адреса записи, со вторым входом первого мультиплексора и со вторым входом первого реверсивного счетчика, девятый вход устройства предварительной обработки A3 первого канала соединен с входом формирователя адреса чтения, с входом формирователя опорных сигналов, со вторым входом второй микросхемы FiFo, с входом устройства управления и со вторым входом первой микросхемы FiFo, десятый вход устройства предварительной обработки A3 первого канала соединен с третьим входом первого коммутатора и третьим входом второго коммутатора, первый выход устройства управления соединен с третьим входом первой микросхемы FiFo, второй выход устройства управления соединен с четвертым входом первой микросхемы FiFo, третий выход устройства управления соединен с третьим входом второй микросхемы FiFo, четвертый выход устройства управления соединен с четвертым входом второй микросхемы FiFo, первый выход формирователя опорных сигналов соединен со вторым входом первого оптимального фильтра, второй выход формирователя опорных сигналов соединен со вторым входом второго оптимального фильтра, выход формирователя адреса записи соединен со вторым входом первого оперативного запоминающего устройства череспериодной обработки и вторым входом второго оперативного запоминающего устройства череспериодной обработки, выход формирователя адреса чтения соединен с третьим входом первого оперативного запоминающего устройства череспериодной обработки и с третьим входом второго оперативного запоминающего устройства череспериодной обработки, одиннадцатый вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго мультиплексора, межкаскадные связи в устройстве квадратурного фазового детектирования А2 второго канала аналогичны межкаскадным связям в устройстве квадратурного фазового детектирования А1 первого канала, межкаскадные связи устройства предварительной обработки А4 второго канала аналогичны межкаскадным связям в устройстве предварительной обработки A3 первого канала.

Отличительными признаками от прототипа является то, что в первый канал приема входит устройство квадратурного фазового детектирования А1 и устройство предварительной обработки A3, при этом устройство квадратурного фазового детектирования А1 первого канала содержит сумматор, блок усилителей с временной автоматической регулировкой усиления, первый и второй смесители частот, первый и второй операционные усилители, первый и второй компараторы напряжений, первый и второй фильтры низких частот, первый и второй интеграторы, первую и вторую схемы контроля и схему формирования сигнала исправности, в свою очередь устройство предварительной обработки A3 первого канала состоит из первого и второго аналого-цифровых преобразователей, первого и второго цифроаналоговых преобразователей, устройства цифрового гетеродинирования, постоянного-запоминающего устройства устройства цифрового гетеродинирования, первого и второго реверсивных счетчиков, первого и второго накапливающих сумматоров, первого и второго мультиплексоров, формирователя адреса записи, первого и второго оперативных запоминающих устройств череспериодной обработки, формирователя адреса чтения, первого и второго оптимальных фильтров, формирователя опорных сигналов, первой и второй микросхем FiFo "первый вошел, первый вышел", устройства управления, первого и второго коммутаторов, при этом второй канал приема содержит устройство квадратурного фазового детектирования А2 и устройство предварительной обработки А4, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования А1 первого канала и устройству предварительной обработки A3 первого канала, а также в радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала включены первый и второй дешифраторы, кварцевый генератор, преобразователь уровня, делитель частоты, полосовой фильтр, дифференцирующая цепочка, интегрирующая цепочка, первый и второй резонансные усилители, третий и четвертый мультиплексоры, синхронизатор сигналов и новые межкаскадные связи между ними.

Предлагаемое техническое решение обеспечивает управляемое усиление, преобразование частоты, разложение на квадратурные составляющие, аналого-цифровое преобразование сигналов, цифровое гетеродинирование, накопление, оптимальную фильтрацию фазо-кодо-манипулированных сигналов, поступающих с высокочастотного приемника РЛС.

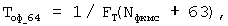

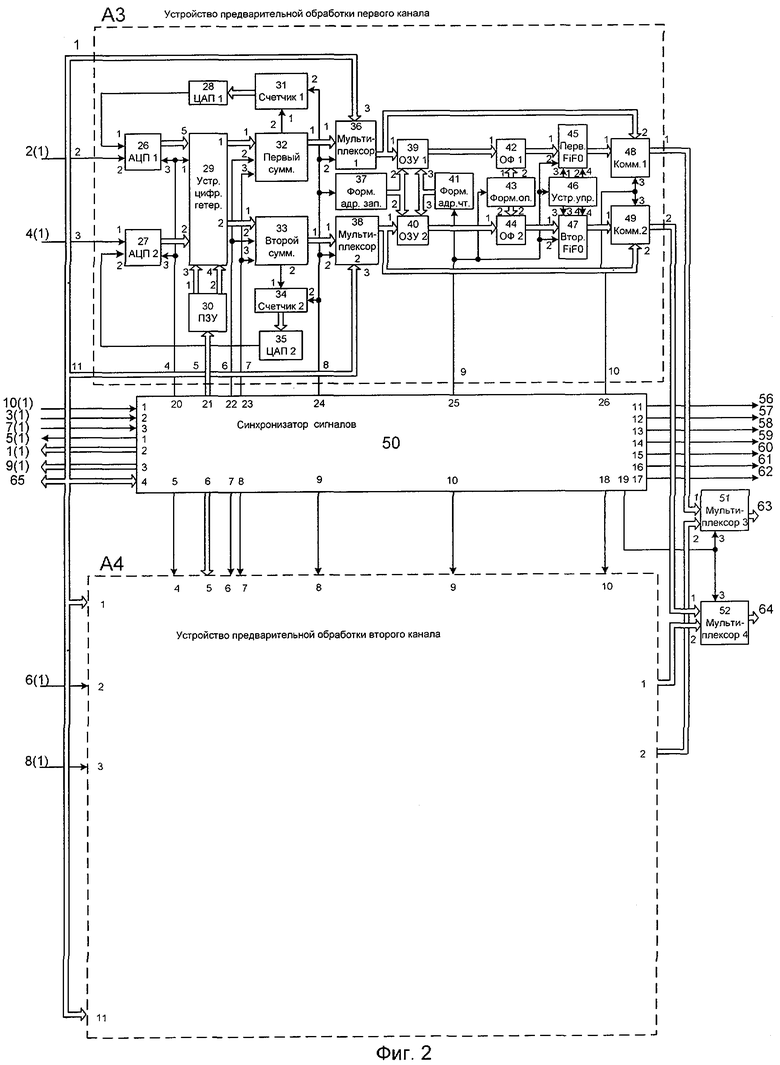

На фиг.1 приведена функциональная электрическая схема предлагаемого устройства, на фиг.2 - то же, продолжение фиг.1.

Радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала содержит первый и второй каналы приема.

В первый канал приема входит устройство квадратурного фазового детектирования А1 и устройство предварительной обработки A3, при этом устройство квадратурного фазового детектирования А1 первого канала содержит сумматор 9, блок усилителей с временной автоматической регулировкой усиления 12, первый 13 и второй 14 смесители частот, первый 15 и второй 17 операционные усилители, первый 16 и второй 18 компараторы напряжений, первый 19 и второй 21 фильтры низких частот, первый 20 и второй 22 интеграторы, первую 23, вторую 24 схемы контроля и схему формирования сигнала исправности 25. В свою очередь устройство предварительной обработки A3 первого канала состоит из первого 26 и второго 27 аналого-цифровых преобразователей, первого 28 и второго 35 цифроаналоговых преобразователей, устройства цифрового гетеродинирования 29, постоянного запоминающего устройства устройства цифрового гетеродинирования 30, первого 31 и второго 34 реверсивных счетчиков, первого 32 и второго 33 N-разрядных накапливающих сумматоров, первого 36 и второго 38 мультиплексоров, формирователя адреса записи 37, первого 39 и второго 40 оперативных-запоминающих устройств череспериодной обработки, формирователя адреса чтения 41, первого 42 и второго 44 оптимальных фильтров, формирователя опорных сигналов 43, первой 45 и второй 47 микросхем FiFo ("первый вошел, первый вышел"), устройства управления 46, первого 48 и второго 49 коммутаторов.

Второй канал приема содержит устройство квадратурного фазового детектирования А2 и устройство предварительной обработки А4, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования А1 первого канала и устройству предварительной обработки A3 первого канала.

В радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала включены первый 5 и второй 4 дешифраторы, кварцевый генератор 3, преобразователь уровня 1, делитель частоты 2, полосовой фильтр 6, дифференцирующая цепочка 7, интегрирующая цепочка 8, первый 10 и второй 11 резонансные усилители, третий 51 и четвертый 52 мультиплексоры и синхронизатор сигналов 50.

Устройство также содержит разъем входного сигнала 53 первого канала, разъем входного опорного сигнала 54, разъем входного сигнала второго канала 55, контакт импульса для формирования строба перестройки антенны 56, контакт сигнала запуска оконечной ступени передатчика 57, контакт сигнала, определяющего длительность импульса запуска передатчика 58, контакт сигнала, определяющего фазу импульса запуска передатчика 59, контакт сигнала импульса бланкирования приемника 60, контакт импульса, сопровождающего основной сигнал 61, контакт импульса начала передачи 62, разъем выходного сигнала реальной составляющей 63, разъем выходного сигнала мнимой составляющей 64 и магистраль параллельной информации 65.

Разъем входного сигнала первого канала 53 соединен с первым входом устройства квадратурного фазового детектирования А1 первого канала. Первый выход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом устройства предварительной обработки A3 первого канала. Первый выход устройства предварительной обработки A3 первого канала соединен с первым входом третьего мультиплексора 51.

Выход третьего мультиплексора 51 соединен с разъемом выходного сигнала реальной составляющей 63. Разъем входного опорного сигнала 54 соединен с входом делителя частоты 2 и входом преобразователя уровня 1. Выход делителя частоты 2 соединен с входом полосового фильтра 6. Выход полосового фильтра 6 соединен с входом дифференцирующей цепочки 7 и входом интегрирующей цепочки 8. Выход дифференцирующей цепочки 7 соединен с входом первого резонансного усилителя 10. Первый выход резонансного усилителя 10 соединен со вторым входом устройства квадратурного фазового детектирования А1 первого канала.

Второй выход первого резонансного усилитиля 10 соединен со вторым входом устройства квадратурного фазового детектирования А2 второго канала. Выход интегрирующей цепочки 8 соединен с входом второго резонансного усилителя 11. Первый выход второго резонансного усилителя 11 соединен с третьим входом устройства квадратурного фазового детектирования А1 первого канала. Второй выход второго резонансного усилителя 11 соединен с третьим входом устройства квадратурного фазового детектирования А2 второго канала.

Разъем входного сигнала второго канала 55 соединен с первым входом устройства квадратурного фазового детектирования А2 второго канала. Первый выход устройства квадратурного фазового детектирования А2 второго канала соединен со вторым входом устройства предварительной обработки А4 второго канала.

Первый выход устройства предварительной обработки А4 второго канала соединен со вторым входом четвертого мультиплексора 52. Выход четвертого мультиплексора 52 соединен с разъемом выходного сигнала мнимой составляющей 64.

Первый выход синхронизатора сигналов 50 соединен с входом кварцевого генератора 3. Первый выход кварцевого генератора 3 соединен с четвертым входом устройства квадратурного фазового детектирования А1 первого канала. Второй выход кварцевого генератора 3 соединен с четвертым входом устройства квадратурного фазового детектирования А2 второго канала.

Второй выход синхронизатора сигналов 50 соединен с входом первого дешифратора 5. Выход первого дешифратора 5 соединен с пятым входом устройства квадратурного фазового детектирования А1 первого канала.

Третий выход синхронизатора сигналов 50 соединен с входом второго дешифратора 4. Выход второго дешифратора 4 соединен с пятым входом устройства квадратурного фазового детектирования А2 второго канала. Выход преобразователя уровня 1 соединен с первым входом синхронизатора сигналов 50. Второй выход устройства квадратурного фазового детектирования А2 второго канала соединен с третьим входом синхронизатора сигналов 50. Третий выход устройства квадратурного фазового детектирования А2 второго канала соединен с третьим входом устройства предварительной обработки А4 второго канала.

Второй выход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом синхронизатора сигналов 50.

Третий выход устройства квадратурного фазового детектирования А1 первого канала соединен с третьим входом устройства предварительной обработки A3 первого канала.

Пятый выход синхронизатора сигналов 50 соединен с четвертым входом устройства предварительной обработки А4 второго канала.

Шестой выход синхронизатора сигналов 50 соединен с пятым входом устройства предварительной обработки А4 второго канала.

Седьмой выход синхронизатора сигналов 50 соединен с шестым входом устройства предварительной обработки А4 второго канала.

Восьмой выход синхронизатора сигналов 50 соединен с седьмым входом устройства предварительной обработки А4 второго канала.

Девятый выход синхронизатора сигналов 50 соединен с восьмым входом устройства предварительной обработки А4 второго канала.

Десятый выход синхронизатора сигналов 50 соединен с девятым входом устройства предварительной обработки А4 второго канала.

Одиннадцатый выход синхронизатора сигналов 50 соединен с контактом импульса для формирования строба перестройки антенны 56.

Двенадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала запуска оконечной ступени передатчика 57.

Тринадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала, определяющего длительность импульса запуска передатчика 58.

Четырнадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала, определяющего фазу импульса запуска передатчика 59.

Пятнадцатый выход синхронизатора сигналов 50 соединен с контактом сигнала импульса бланкирования приемника 60.

Шестнадцатый выход синхронизатора сигналов 50 соединен с контактом импульса, сопровождающего основной сигнал 61.

Семнадцатый выход синхронизатора сигналов 50 соединен с контактом импульса начала передачи 62.

Восемнадцатый выход синхронизатора сигналов 50 соединен с десятым входом устройства предварительной обработки А4 второго канала.

Девятнадцатый выход синхронизатора сигналов 50 соединен с третьим входом третьего мультиплексора 51 и третьим входом четвертого мультиплексора 52.

Двадцатый выход синхронизатора сигналов соединен с четвертым входом устройства предварительной обработки A3 первого канала.

Двадцать первый выход синхронизатора сигналов 50 соединен с пятым входом устройства предварительной обработки A3 первого канала.

Двадцать второй выход синхронизатора сигналов 50 соединен с шестым входом устройства предварительной обработки A3 первого канала.

Двадцать третий выход синхронизатора сигналов 50 соединен с седьмым входом устройства предварительной обработки A3 первого канала.

Двадцать четвертый выход синхронизатора сигналов 50 соединен с восьмым входом устройства предварительной обработки A3 первого канала.

Двадцать пятый выход синхронизатора сигналов 50 соединен с девятым входом устройства предварительной обработки A3 первого канала.

Двадцать шестой выход синхронизатора сигналов 50 соединен с десятым входом устройства предварительной обработки A3 первого канала.

Разъем магистрали параллельной информации 65 соединен с первым и одиннадцатым входами устройства предварительной обработки A3 первого канала, с первым и одиннадцатым входами устройства предварительной обработки А4 второго канала и четвертым выходом синхронизатора сигналов 50.

Второй выход устройства предварительной обработки A3 первого канала соединен с первым входом четвертого мультиплексора 52.

Второй выход устройства предварительной обработки А4 второго канала соединен со вторым входом третьего мультиплексора 51.

В устройстве квадратурного фазового детектирования А1 первого канала первый вход соединен с первым входом сумматора 9. Выход сумматора 9 соединен с первым входом блока усилителей с временной автоматической регулировкой усиления 12. Выход блока усилителей с временной автоматической регулировкой усиления соединен с первым входом первого смесителя частоты 13 и с первым входом второго смесителя частоты 14.

Выход первого смесителя частот 13 соединен с первым входом первого операционного усилителя 15. Выход первого операционного усилителя 15 соединен с входом первого фильтра низких частот 19. Выход первого фильтра низких частот 19 соединен с первым выходом устройства квадратурного фазового детектирования А1 первого канала, с входом первой схемы контроля 23 и с входом первого интегратора 20.

Выход первого интегратора 20 соединен с входом первого компаратора напряжений 16. Выход первого компаратора напряжений 16 соединен со вторым входом первого операционного усилителя 15. Выход второго смесителя частот 14 соединен с первым входом второго операционного усилителя 17. Выход второго операционного усилителя 17 соединен с входом второго фильтра низких частот 21. Выход фильтра низких частот 21 соединен с третьим выходом устройства квадратурного фазового детектирования А1 первого канала, с входом второй схемы контроля 24, с входом второго интегратора 22.

Выход второго интегратора 22 соединен с входом второго компаратора напряжений 18. Выход второго компаратора напряжений 18 соединен со вторым входом второго операционного усилителя 17. Выход первой схемы контроля 23 соединен с первым входом схемы формирования сигнала исправности 25.

Выход второй схемы контроля 24 соединен со вторым входом схемы формирования сигнала исправности 25. Выход схемы формирования сигнала исправности 25 соединен со вторым выходом устройства квадратурного фазового детектирования А1 первого канала.

Четвертый вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом сумматора 9.

Второй вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом первого смесителя частот 13.

Третий вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом второго смесителя частот 14.

Пятый вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом блока усилителей с временной автоматической регулировкой усиления 12.

Первый вход устройства предварительной обработки A3 первого канала соединен с третьим входом первого мультиплексора 36.

Второй вход устройства предварительной обработки A3 первого канала соединен со вторым входом первого аналого-цифрового преобразователя 26.

Выход первого аналого-цифрового преобразователя 26 соединен с пятым входом устройства цифрового гетеродинирования 29.

Первый выход устройства цифрового гетерадирования 29 соединен с первым входом первого N-разрядного накапливающего сумматора 32. Первый выход первого N-разрядного накапливающего сумматора 32 соединен с первым входом первого мультиплексора 36. Выход первого мультиплексора 36 соединен с первым входом оперативного запоминающего устройства череспериодной обработки 39 и со вторым входом первого коммутатора 48. Выход первого оперативного запоминающего устройства череспериодной обработки 39 соединен с первым входом оптимального фильтра 42. Выход первого оптимального фильтра 42 соединен с первым входом первой микросхемы FiFo 45. Выход первой микросхемы FiFo 45 соединен с первым входом первого коммутатора напряжений 48.

Выход первого коммутатора напряжений 48 соединен с первым выходом устройства предварительной обработки A3 первого канала.

Третий вход устройства предварительной обработки A3 первого канала соединен с первым входом второго аналого-цифрового преобразователя 27. Выход второго аналого-цифрового преобразователя 27 соединен со вторым входом устройства цифрового гетеродинирования 29. Второй выход устройства цифрового гетеродинирования 29 соединен с первым входом второго N-разрядного накапливающего сумматора 33. Первый выход второго N-разрядного накапливающего сумматора 33 соединен с первым входом второго мультиплексора 38. Выход второго мультиплексора 38 соединен с первым входом второго оперативного запоминающего устройства череспериодной обработки 40 и со вторым входом второго коммутатора 49. Выход второго оперативного запоминающего устройства череспериодной обработки 40 соединен с первым входом второго оптимального фильтра 44. Выход второго оптимального фильтра 44 соединен с первым входом второй микросхемы FiFo 47. Выход второй микросхемы FiFo 47 соединен с первым входом второго коммутатора 49. Выход второго коммутатора 49 соединен со вторым выходом устройства предварительной обработки A3 первого канала. Второй выход первого N-разрядного накапливающего сумматора 32 соединен с первым входом первого реверсивного счетчика 31. Выход первого реверсивного счетчика 31 соединен с входом первого цифроаналогового преобразователя 28. Выход первого цифроаналогового преобразователя 28 соединен с первым входом первого аналого-цифрового преобразователя 26. Второй выход второго N-разрядного накапливающего сумматора 33 соединен с первым входом второго реверсивного счетчика 34. Выход второго реверсивного счетчика 34 соединен с входом второго цифроаналогового преобразователя 35. Выход второго цифроаналогового преобразователя 35 соединен со вторым входом аналого-цифрового преобразователя 27.

Четвертый вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго аналого-цифрового преобразователя 27, с третьим входом первого аналого-цифрового преобразователя 26, с первым входом устройства цифрового гетеродинирования 29.

Пятый вход устройства предварительной обработки A3 первого канала соединен с входом постоянного запоминающего устройства устройства цифрового гетеродинирования 30. Первый выход постоянного запоминающего устройства устройства цифрового гетеродинирования 30 соединен с третьим входом устройства цифрового гетеродинирования 29. Второй выход постоянно запоминающего устройства цифрового гетеродинирования 30 соединен с четвертым входом устройства цифрового гетеродинирования 29.

Шестой вход устройства предварительной обработки A3 первого канала соединен со вторым входом второго N-разрядного накапливающего сумматора 33, со вторым входом первого N-разрядного накапливающего сумматора 32.

Седьмой вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго N-разрядного накапливающего сумматора 33, с третьим входом первого N-разрядного накапливающего сумматора 3.

Восьмой вход устройства предварительной обработки A3 первого канала соединен со вторым входом второго реверсивного счетчика 34, со вторым входом второго мультиплексора 38, с входом формирователя адреса записи 37, со вторым входом первого мультиплексора 36, со вторым входом первого реверсивного счетчика 31.

Девятый вход устройства предварительной обработки A3 первого канала соединен с входом формирователя адреса чтения 41, с входом формирователя опорных сигналов 43, со вторым входом второй микросхемы FiFo 47, с входом устройства управления 46, со вторым входом первой микросхемы FiFo 45.

Десятый вход устройства предварительной обработки A3 первого канала соединен с третьим входом первого коммутатора 48 и третьим входом второго коммутатора 49. Первый выход устройства управления 46 соединен с третьим входом первой микросхемы FiFo 45. Второй выход устройства управления 46 соединен с четвертым входом первой микросхемы FiFo 45. Третий выход устройства управления 46 соединен с третьим входом второй микросхемы FiFo 47. Четвертый выход устройства управления 46 соединен с четвертым входом второй микросхемы FiFo 47. Первый выход формирователя опорных сигналов 43 соединен со вторым входом первого оптимального фильтра 42. Второй выход формирователя опорных сигналов 43 соединен со вторым входом второго оптимального фильтра 44. Выход формирователя адреса записи 37 соединен со вторым входом первого оперативного запоминающего устройства череспериодной обработки 39 и со вторым входом второго оперативного запоминающего устройства череспериодной обработки 40. Выход формирователя адреса чтения 41 соединен с третьим входом первого оперативного запоминающего устройства череспериодной обработки 39 и с третьим входом второго оперативного запоминающего устройства череспериодной обработки 40.

Одиннадцатый вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго мультиплексора 38.

Межкаскадные связи в устройстве квадратурного фазового детектирования А2 второго канала аналогичны межкаскадным связям в устройстве квадратурного фазового детектирования А1 первого канала, межкаскадные связи устройства предварительной обработки А4 второго канала аналогичны межкаскадным связям в устройстве предварительной обработки A3 первого канала.

Устройство квадратурного фазового детектирования А1 первого канала обеспечивает дискретное управляемое усиление сигналов, разложение их на квадратурные составляющие (cos и sin), последетекторную фильтрацию низких частот, привязку постоянной составляющей выходных сигналов к средней точке аналого-цифрового преобразователя и контроль исправности устройства.

Устройство работает следующим образом.

Входной сигнал с первого канала РЛС на промежуточной частоте (fпч), содержащий доплеровское смещение частоты с разъема входного сигнала первого канала 53 поступает на первый вход сумматора 9, затем на блок усилителей с временной автоматической регулировкой усиления 12, которые усиливают принятый сигнал. Коэффициент передачи усилителей изменяется дискретно по командам, поступающим с первого дешифратора 5. Команды управления на первый дешифратор 5 поступают с синхронизатора сигналов 50, управление которыми происходит по магистрали параллельной информации 65. Изменение коэффициента передачи блока усилителей обеспечивается за счет дискретного изменения величины последовательной отрицательной обратной связи ключами на полевых транзисторах.

После усиления сигнала в устройстве квадратурного фазового детектирования происходят преобразование частоты сигнала, разложение его на квадратурные составляющие (cos-I квадратура и sin-II квадратура), стабилизация постоянной составляющей напряжения выходного сигнала по квадратурам и проверка исправности устройства квадратурного фазового детектирования. Сигнал с выхода блока усилителей с временной автоматической регулировкой усиления 12 поступает на первый вход первого смесителя частот 13 и на первый вход второго смесителя частот 14.

Формирование опорных сигналов (гетеродинов) для смесителей частот обеспечивается делением на два частоты входного опорного сигнала в делителе частоты 2, последующей фильтрацией гармоник полосовым фильтром 6, сдвигом фаз в дифференцирующей и интегрирующей цепях и усилителем сигналов в усилителях 10 и 11 частоты гетеродина.

Вследствие сдвига фаз сигналов в дифференцирующей и интегрирующей цепях в противоположные стороны на 45° сдвиг по фазе сигналов гетеродина на вторых входах смесителей частот 13 и 14 составляет примерно 90°. Усилители 10 и 11 частоты гетеродина выполнены резонансными и точная установка сдвига фаз сигналов гетеродинов, равная 90°, обеспечивается настройкой резонансных контуров.

С выхода первого смесителя частот 13 низкочастотные сигналы с частотой, соответствующей доплеровскому смещению частоты входного сигнала, суммируются в первом операционном усилителе 15 с напряжением схемы стабилизации постоянной составляющей выходного сигнала, проходят через фильтр низких частот 19 и поступают по цепи реальной составляющей первого канала (ReIk(cos)) на второй вход первого аналого-цифрового преобразователя 26 устройства предварительной обработки A3 первого канала. Выходной сигнал со второго смесителя 14 обрабатывается аналогично во втором операционном усилителе 17, во втором фильтре низких частот 21 и по цепи мнимой составляющей первого канала (ImIk(sin)) поступает на первый вход второго аналого-цифрового преобразователя 27 устройства предварительной обработки A3 первого канала.

Первый 19 и второй 21 фильтры низких частот выполнены в виде Т-образного пассивного фильтра пятого порядка с аппроксимацией Баттерворта на LC-элементах с частотой среза амплитудно-частотной характеристики, равной 3 МГц.

Для стабилизации постоянной составляющей напряжения выходного сигнала на первом выходе устройства квадратурного фазового детектирования (выход I-ой квадратуры) выходной сигнал проходит через первый интегратор 20, имеющий большую постоянную времени интегрирования, и поступает на вход первого компаратора 16, где сравнивается с потенциалом, значение которого близко к нулевому. Выходной сигнал первого компаратора поступает на второй вход первого операционного усилителя и обеспечивает стабилизацию постоянной составляющей напряжения на выходе первой квадратуры.

Стабилизация постоянной составляющей напряжения выходного сигнала на третьем выходе устройства квадратурного фазового детектирования (выход II-ой квадратуры) производится аналогично стабилизации постоянной составляющей напряжения выходного сигнала I-ой квадратуры через второй интегратор 22, второй компаратор 18.

Коэффициенты передачи сигналов по выходам квадратур в устройстве квадратурного фазового детектирования А1 первого канала одинаковы, а фазы сигналов сдвинуты на 90°. Первая схема контроля 23, вторая схема контроля 24 и схема формирования сигнала исправности 25 формируют сигнал ″Исправность устройства квадратурного фазового детектирования А1 первого канала″.

Первая схема контроля 23 осуществляет контроль исправности устройства квадратурного фазового детектирования А1 первого канала реальной составляющей сигнала, а вторая схема контроля осуществляет контроль исправности по мнимой составляющей сигнала. Контроль обеспечивается двухполярной пороговой проверкой уровня сигнала на выходе каждой квадратуры. В схеме контроля уровни сигнала на компараторах сравниваются с уровнями пороговых напряжений. Если уровни сигнала превышают уровни напряжения порогов, выдается сигнал, поступающий на схему формирования сигнала исправности 25. Аналогично работает вторая схема контроля 24 по мнимой составляющей сигнала первого канала. При наличии сигналов с обоих схем контроля 23 и 24 схема формирования сигнала исправности 25 выдает сигнал "Исправность", который поступает в синхронизатор сигналов 50 и по магистрали параллельной информации 65 поступает на выход радиоприемного устройства когерентной РЛС с оптимальной фильтрацией сигнала ("Формирование и измерение сигналов в импульсной технике", Г.М.Гонтаренко, Н.Г.Крыжановская, издательство стандартов, 1992, стр.89).

Входной сигнал второго канала РЛС с разъема входного сигнала второго канала 55 поступает на первый вход устройства квадратурного фазового детектирования А2 второго канала.

Устройство квадратурного фазового детектирования А2 второго канала обеспечивает аналогичную обработку сигнала второго канала приема и схемно-конструктивно выполнено аналогично устройству А1.

Второй дешифратор 4 выполняет функции аналогично первому дешифратору только для второго канала приема. С выхода устройства квадратурного фазового детектирования А2 второго канала реальная и мнимая составляющие низкочастотного сигнала поступают на второй и третий входы устройства предварительной обработки А4 второго канала.

Устройство предварительной обработки A3 первого канала выполняет следующие операции:

- преобразование четырех аналоговых входных сигналов (Re 1к, Im 1к, Re 2к, Im 2к) в двенадцатиразрядный код;

- производит цифровое гетеродинирование;

- обеспечивает оптимальную фильтрацию сигналов;

- производит мультиплексирование каналов;

- формирует корректирующие коэффициенты для цифрового гетеродинирования;

- компенсирует постоянную составляющую, возникающую на входах аналого-цифровой преобразователей.

Работает устройство предварительной обработки A3 первого канала следующим образом.

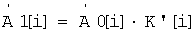

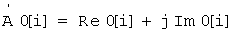

Первый аналого-цифровой преобразователь 26 производит перевод аналогового сигнала реальной составляющей в цифровую форму. Второй аналого-цифровой преобразователь 27 производит перевод аналогового сигнала мнимой составляющей в цифровую форму. После аналого-цифровых преобразователей 26 и 27 устройство цифрового гетеродинирования 29 производит цифровое гетеродинирование, частота гетеродина задается по магистрали параллельной информации с точностью 0,8 Гц. Устройство цифрового гетеродинирования 29 выполняет операцию перемножения двух комплексных чисел:

где  - поступающие из аналого-цифрового преобразователя коды выборок квадратурных составляющих сигнала,

- поступающие из аналого-цифрового преобразователя коды выборок квадратурных составляющих сигнала,

K’[i]=cos ϕ[i]-j sin ϕ[i] - корректирующие коэффициенты, поступающие из цифрового гетеродина,

ϕ[i]=ϕ[i-1]+Δϕ; Δϕ - фазовый набег.

Постоянное запоминающее устройство 30 устройства цифрового гетеродинирования выполнено на базе двух постоянных запоминающих устройств AT29C1024-70JI. Адрес чтения информации из постоянного запоминающего устройства 30 устройства цифрового гетеродинирования непрерывно формируется в соответствии с кодом Δϕ. Чтение значений корректирующих коэффициентов происходит с частотой дискретизации аналого-цифрового преобразователя.

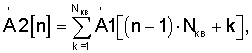

После гетеродинирования производится суммирование отсчетов сигнала на интервале одного элемента дальности

где n - номер элемента дальности,

реальной составляющей в первом N-разрядном накапливающем сумматоре 32, мнимой составляющей во втором N-разрядном накапливающем сумматоре 33.

Количество суммирующих выборок определяется кодом Nкв и может принимать значения от единицы до шестидесяти трех.

Первый аналого-цифровой преобразователь 26 охвачен цепью обратной связи, состоящей из реверсивного счетчика 31 и цифроаналогового преобразователя 28 для балансировки постоянной составляющей. Второй аналого-цифровой преобразователь 27 аналогично охвачен цепью обратной связи, состоящей из второго реверсивного счетчика 34 и второго цифроаналогового преобразователя 35 для балансировки постоянной составляющей. Для предотвращения переполнения разрядной сетки накопителей имеются первый 36 и второй 38 мультиплексоры, первое 39 и второе 40 оперативные запоминающие устройства череспериодной обработки предназначены для череспериодной обработки информации в первом 42 и втором 44 оптимальных фильтрах. Первый 48 и второй 49 коммутаторы осуществляют подачу информации на выходы третьего 51 и четвертого 52 мультиплексоров или непосредственно с первого 36 и второго 38 мультиплексоров или с первого 42 и второго 44 выходов оптимальных фильтров.

Синхронизатор сигналов 50 выдает сигналы управления для передающего канала, высокочастотного приемника, которые поступают на контакты: импульса для формирования строба перестройки антенны 56, сигнала запуска оконченной ступени передатчика 57, сигнала, определяющего длительность импульса запуска передатчика 58, сигнала, определяющего фазу импульса запуска передатчика 59, сигнала импульса бланкирования приемника 60, импульса, сопровождающего основной сигнал 61, импульса начала передачи 62 и для синхронизации устройства предварительной обработки.

Для временного сжатия фазо-кодо-манипулированного сигнала используется череспериодная обработка информации, поступающая из накопителя. Для хранения данных сигнала предыдущего такта и записи данных текущего такта используются двухпортовые оперативные запоминающие устройства. Формирование адресов записи и чтения для двухпортовых оперативных запоминающих устройств осуществляется в формирователе адресов записи 37 и формирователе адресов чтения 41. Формирователь опорных сигналов 43 формирует массивы опорных функций для различных типов фазо-кодо-манипулированных сигналов. Устройство управления 46 формирует сигналы управления первой 45 и второй 47 микросхем FiFo в зависимости от режима работы РЛС.

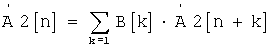

При сжатии фазо-кодо-манипулированного сигнала для каждого элемента дальности вычисляется значение свертки:

Nк-1

где B[k] - элемент массива опорной функции.

С целью сокращения времени обработки информации в устройстве предварительной обработки А1 первого канала используются шестидесят четыре параллельно работающих устройства сжатия фазо-кодо-манипулированных сигналов, таким образом одновременно обрабатывается информация для шестидесяти четырех элементов дальности.

Время обработки шеститесяти четырех элементов дальности определяется длиной фазо-кодо-манипулированной последовательности Nфкмс

где FТ - тактовая частота устройств сжатия, определяемая быстродействием микросхемы. В данном случае FT=7 МГц.

Так как необходимое число элементов дальности в общем случае больше шестидесяти четырех, сжатие фазо-кодо-манипулированных сигналов производится за несколько циклов  причем необходимое число циклов может быть дробным числом. Данные из оптимальных фильтров 42 и 44 записываются оперативно-запоминающим устройством типа FiFo в конце каждого цикла. После обработки всех элементов дальности производится передача всего массива данных FiFo во внешнее устройство в соответствии с заданным протоколом обмена. Частота передачи определяется параметрами внешнего устройства и в данном случае после мультиплексирования составляет 14 МГц.

причем необходимое число циклов может быть дробным числом. Данные из оптимальных фильтров 42 и 44 записываются оперативно-запоминающим устройством типа FiFo в конце каждого цикла. После обработки всех элементов дальности производится передача всего массива данных FiFo во внешнее устройство в соответствии с заданным протоколом обмена. Частота передачи определяется параметрами внешнего устройства и в данном случае после мультиплексирования составляет 14 МГц.

Устройство управления управляет процессами записи информации из оптимального фильтра в FiFo и чтения информации из FiFo в соответствии с заданным количеством элементов дальности и временной диаграммой оптимального фильтра.

С выходов первого 42 и второго 44 оптимальных фильтров данные записываются в первую 45 и вторую 47 микросхемы FiFо соответственно, после окончания обработки всех элементов дальности данные из первой 45 и второй 47 микросхем FiFо подаются на выходные третий 51 и четвертый 52 мультиплексоры соответственно.

Устройство предварительной обработки А4 второго канала обеспечивает аналогичную обработку выходного сигнала устройства квадратурного фазового детектирования А2 второго канала, как в устройстве предварительной обработки A3 первого канала, и схемно-конструктивно выполнено аналогично устройству предварительной обработки A3 первого канала.

Точность при цифровой корректировке квадратур принимаемых сигналов обеспечивается формированием контрольного сигнала на кварцевом генераторе 3.

Расширение динамического диапазона приемного устройства обеспечивается за счет высокой линейности амплитудных характеристик блока усилителей с временной автоматической регулировкой усиления и смесителей. Первый 13 и второй 14 смесители выполнены по ключевой балансной схеме с управлением сигналом гетеродина величиной последовательной отрицательной обратной связи в усилителях смесителя.

Сигнал опорной частоты для синхронизатора сигналов 50 формируется в преобразователе уровня 1 из сигнала опорной частоты, поступающей с входного разъема входного опорного сигнала 54.

С третьего мультиплексора 51 выходной сигнал поступает на разъем выходного сигнала реальной составляющей 63, а с четвертого мультиплексора 52 выходной сигнал поступает на разъем выходного сигнала мнимой составляющей 64.

Применение предлагаемого устройства расширяет функциональные возможности за счет дополнительного выполнения следующих функций:

- выдает сигналы управления для передающего канала, высокочастотного приемника и синхронизации устройства предварительной обработки;

- компенсирует постоянную составляющую на входах аналого-цифрового преобразователя;

- формирует корректирующие коэффициенты для цифрового гетеродинирования;

- обеспечивает оптимальную фильтрацию сигналов;

- производит мультиплексирование каналов;

- производит цифровое гетеродинирование.

Улучшение основных технических параметров осуществляется за счет увеличения динамического диапазона устройства и увеличения точности при цифровой корректировке квадратур принимаемых сигналов.

По предлагаемому техническому решению изготовлены опытные образцы. Технические параметры подтверждены положительными результатами предварительных и летных испытаний.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОГЕРЕНТНЫЙ ПРИЕМНИК РЛС С ЦИФРОВЫМ УСТРОЙСТВОМ ДЛЯ АМПЛИТУДНОЙ И ФАЗОВОЙ КОРРЕКТИРОВКИ КВАДРАТУРНЫХ СОСТАВЛЯЮЩИХ ПРИНИМАЕМОГО СИГНАЛА | 2004 |

|

RU2273860C2 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С КАНАЛАМИ ВЫСОКОГО РАЗРЕШЕНИЯ | 2007 |

|

RU2344436C1 |

| МОДУЛЬ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ | 2005 |

|

RU2290662C1 |

| БЛОК ПРИЕМА И СИНХРОНИЗАЦИИ | 2012 |

|

RU2497148C1 |

| Способ обработки радиолокационных сигналов в моноимпульсной РЛС | 2017 |

|

RU2659807C1 |

| Способ обработки радиолокационных сигналов в моноимпульсной РЛС | 2016 |

|

RU2636058C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С ЦИФРОВЫМ ГЕТЕРОДИНИРОВАНИЕМ | 2002 |

|

RU2225623C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2020 |

|

RU2759511C1 |

| МНОГОКАНАЛЬНЫЙ ПЕРЕПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ПРИЕМНЫЙ ТРАКТ | 2004 |

|

RU2289202C2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ДИАГРАММЫ НАПРАВЛЕННОСТИ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2011 |

|

RU2495449C2 |

Изобретение относится к технике обработки сигналов радиолокационных станций (РЛС). Технический результат предлагаемого технического решения направлен на расширение функциональных возможностей и улучшение основных технических параметров РЛС. Заявленное устройство содержит первый и второй каналы приема. В первый канал приема входит устройство квадратурного фазового детектирования А1 и устройство предварительной обработки A3, при этом устройство квадратурного фазового детектирования А1 первого канала содержит сумматор, блок усилителей с временной автоматической регулировкой усиления, первый и второй смесители частот, первый и второй операционные усилители, первый и второй компараторы напряжений, первый и второй фильтры низких частот, первый и второй интеграторы, первую, вторую схемы контроля и схему формирования сигнала исправности. В свою очередь устройство предварительной обработки A3 первого канала состоит из первого и второго аналого-цифровых преобразователей, первого и второго цифроаналоговых преобразователей, устройства цифрового гетеродинирования, постоянного запоминающего устройства устройства цифрового гетеродинирования, первого и второго реверсивных счетчиков, первого и второго N-разрядных накапливающих сумматоров, первого и второго мультиплексоров, формирователя адреса записи, первого и второго оперативных-запоминающих устройств череспериодной обработки, формирователя адреса чтения, первого и второго оптимальных фильтров, формирователя опорных сигналов, первой и второй микросхем FiFo (“первый вошел, первый вышел”), устройства управления, первого и второго коммутаторов. Второй канал приема содержит устройство квадратурного фазового детектирования А2 и устройство предварительной обработки А4, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования А1 первого канала и устройству предварительной обработки A3 первого канала. В радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала включены первый и второй дешифраторы, кварцевый генератор, преобразователь уровня, делитель частоты, полосовой фильтр, дифференцирующая цепочка, интегрирующая цепочка, первый и второй резонансные усилители, третий и четвертый мультиплексоры и синхронизатор сигналов. Устройство также содержит разъем входного сигнала первого канала, разъем входного опорного сигнала, разъем входного сигнала второго канала, контакт импульса для формирования строба перестройки антенны, контакт сигнала запуска оконечной ступени передатчика, контакт сигнала, определяющего длительность импульса запуска передатчика, контакт сигнала, определяющего фазу импульса запуска передатчика, контакт сигнала импульса бланкирования приемника, контакт импульса, сопровождающего основной сигнал, контакт импульса начала передачи, разъем выходного сигнала реальной составляющей, разъем выходного сигнала мнимой составляющей и магистраль параллельной информации. 2 ил.

Радиоприемное устройство когерентной РЛС с оптимальной фильтрацией сигнала, содержащее первый канал приема, в который входит устройство квадратурного фазового детектирования А1 и устройство предварительной обработки A3, при этом устройство квадратурного фазового детектирования А1 первого канала содержит сумматор, блок усилителей с временной автоматической регулировкой усиления, первый и второй смесители частот, первый и второй операционные усилители, первый и второй компараторы напряжений, первый и второй фильтры низких частот, первый и второй интеграторы, первую и вторую схемы контроля, схему формирования сигнала исправности, в свою очередь, устройство предварительной обработки A3 первого канала состоит из первого и второго аналого-цифрового преобразователей, первого и второго цифроаналоговых преобразователей, устройства цифрового гетеродинирования, постоянного запоминающего устройства устройства цифрового гетеродинирования, первого и второго реверсивных счетчиков, первого и второго накапливающих N-разрядных сумматоров, первого и второго мультиплексоров, формирователя адреса записи, первого и второго оперативных запоминающих устройств череспериодной обработки, формирователя адреса чтения, первого и второго оптимальных фильтров, формирователя опорных сигналов, первой и второй микросхем FiFo “первый вошел, первый вышел”, устройства управления, первого и второго коммутаторов, при этом второй канал приема содержит устройство квадратурного фазового детектирования А2 и устройство предварительной обработки А4, которые схемно-конструктивно выполнены аналогично устройству квадратурного фазового детектирования А1 первого канала и устройству предварительной обработки A3 первого канала, а также в него включены первый и второй дешифраторы, кварцевый генератор, преобразователь уровня, делитель частоты, полосовой фильтр, дифференцирующая цепочка, интегрирующая цепочка, первый и второй резонансные усилители, третий и четвертый мультиплексоры и синхронизатор сигналов, при этом вход приемника по первому каналу соединен с первым входом устройства квадратурного фазового детектирования А1 первого канала, первый выход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом устройства предварительной обработки A3 первого канала, первый выход устройства предварительной обработки A3 первого канала соединен с первым входом третьего мультиплексора, выход третьего мультиплексора соединен с разъемом выходного сигнала реальной составляющей, разъем входного опорного сигнала соединен с входом делителя частоты и входом преобразователя уровня, выход делителя частоты соединен с входом полосового фильтра, выход полосового фильтра соединен с входом дифференцирующей цепочки и входом интегрирующей цепочки, выход дифференцирующей цепочки соединен с входом первого резонансного усилителя, первый выход первого резонансного усилителя соединен со вторым входом устройства квадратурного фазового детектирования А1 первого канала, второй выход первого резонансного усилителя соединен со вторым входом устройства квадратурного фазового детектирования А2 второго канала, выход интегрирующей цепочки соединен с входом второго резонансного усилителя, первый выход второго резонансного усилителя соединен с третьим входом устройства квадратурного фазового детектирования А1 первого канала, второй выход второго резонансного усилителя соединен с третьим входом устройства квадратурного фазового детектирования А2 второго канала, первый выход устройства квадратурного фазового детектирования А2 второго канала соединен со вторым входом устройства предварительной обработки А4 второго канала, первый выход устройства предварительной обработки А4 второго канала соединен со вторым входом четвертого мультиплексора, выход четвертого мультиплексора соединен с разъемом выходного сигнала мнимой составляющей, первый выход синхронизатора сигналов соединен с входом кварцевого генератора, первый выход кварцевого генератора соединен с четвертым входом устройства квадратурного фазового детектирования А1 первого канала, второй выход кварцевого генератора соединен с четвертым входом устройства квадратурного фазового детектирования А2 второго канала, второй выход синхронизатора сигналов соединен с входом первого дешифратора, выход первого дешифратора соединен с пятым входом устройства квадратурного фазового детектирования А1 первого канала, третий выход синхронизатора сигналов соединен с входом второго дешифратора, выход второго дешифратора соединен с пятым входом устройства квадратурного фазового детектирования А2 второго канала, выход преобразователя уровня соединен с первым входом синхронизатора сигналов, второй выход устройства квадратурного фазового детектирования А2 второго канала соединен с третьим входом синхронизатора сигналов, третий выход устройства квадратурного фазового детектирования А2 второго канала соединен с третьим входом устройства предварительной обработки А4 второго канала, второй выход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом синхронизатора сигналов, третий выход устройства квадратурного фазового детектирования А1 первого канала соединен с третьим входом устройства предварительной обработки A3 первого канала, пятый выход синхронизатора сигналов соединен с четвертым входом устройства предварительной обработки А4 второго канала, шестой выход синхронизатора сигналов соединен с пятым входом устройства предварительной обработки А4 второго канала, седьмой выход синхронизатора сигналов соединен с шестым входом устройства предварительной обработки А4 второго канала, восьмой выход синхронизатора сигналов соединен с седьмым входом устройства предварительной обработки А4 второго канала, девятый выход синхронизатора сигналов соединен с восьмым входом устройства предварительной обработки А4 второго канала, десятый выход синхронизатора сигналов соединен с девятым входом устройства предварительной обработки А4 второго канала, одиннадцатый выход синхронизатора сигналов соединен с контактом импульса для формирования строба перестройки антенны, двенадцатый выход синхронизатора сигналов соединен с контактом сигнала запуска оконечной ступени передатчика, тринадцатый выход синхронизатора сигналов соединен с контактом сигнала определяющего длительность импульса запуска передатчика, четырнадцатый выход синхронизатора сигналов соединен с контактом сигнала определяющего фазу импульса запуска передатчика, пятнадцатый выход синхронизатора сигналов соединен с контактом сигнала импульса бланкирования приемника, шестнадцатый выход синхронизатора сигналов соединен с контактом импульса сопровождающего основной сигнал, семнадцатый выход синхронизатора сигналов соединен с контактом импульса начала передачи, восемнадцатый выход синхронизатора сигналов соединен с десятым входом устройства предварительной обработки А4 второго канала, девятнадцатый выход синхронизатора сигналов соединен с третьим входом третьего мультиплексора и третьим входом четвертого мультиплексора, двадцатый выход синхронизатора сигналов соединен с четвертым входом устройства предварительной обработки A3 первого канала, двадцать первый выход синхронизатора сигналов соединен с пятым входом устройства предварительной обработки A3 первого канала, двадцать второй выход синхронизатора сигналов соединен с шестым входом устройства предварительной обработки A3 первого канала, двадцать третий выход синхронизатора сигналов соединен с седьмым входом устройства предварительной обработки A3 первого канала, двадцать четвертый выход синхронизатора сигналов соединен с восьмым входом устройства предварительной обработки A3 первого канала, двадцать пятый выход синхронизатора сигналов соединен с девятым входом устройства предварительной обработки A3 первого канала, двадцать шестой выход синхронизатора сигналов соединен с десятым входом устройства предварительной обработки A3 первого канала, разъем магистрали параллельной информации соединен с первым и одиннадцатым входами устройства предварительной обработки A3 первого канала, с первым и одиннадцатым входами устройства предварительной обработки А4 второго канала, и с четвертым выходом синхронизатора сигналов, второй выход устройства предварительной обработки A3 первого канала соединен с первым входом четвертого мультиплексора, второй выход устройства предварительной обработки А4 второго канала соединен со вторым входом третьего мультиплексора, в устройстве квадратурного фазового детектирования А1 первого канала первый вход соединен с первым входом сумматора, выход сумматора соединен с первым входом блока усилителей с временной автоматической регулировкой усиления, выход блока усилителей с временной автоматической регулировкой усиления соединен с первым входом первого смесителя частот и с первым входом второго смесителя частот, выход первого смесителя частот соединен с первым входом первого операционного усилителя, выход первого операционного усилителя соединен с входом первого фильтра низких частот, выход первого фильтра низких частот соединен с первым выходом устройства квадратурного фазового детектирования А1 первого канала, с входом первой схемы контроля и с входом первого интегратора, выход первого интегратора соединен с входом первого компаратора напряжений, выход первого компаратора напряжений соединен со вторым входом первого операционного усилителя, выход второго смесителя частот соединен с первым входом второго операционного усилителя, выход второго операционного усилителя соединен с входом второго фильтра низких частот, выход фильтра низких частот соединен с третьим выходом устройства квадратурного фазового детектирования А1 первого канала, с входом второй схемы контроля и со входом второго интегратора, выход второго интегратора соединен с входом второго компаратора напряжений, выход второго компаратора напряжений соединен со вторым входом второго операционного усилителя, выход первой схемы контроля соединен с первым входом схемы формирования сигнала исправности, выход второй схемы контроля соединен со вторым входом схемы формирования сигнала исправности, выход схемы формирования сигнала исправности соединен со вторым выходом устройства квадратурного фазового детектирования А1 первого канала, четвертый вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом сумматора, второй вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом первого смесителя частот, третий вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом второго смесителя частот, пятый вход устройства квадратурного фазового детектирования А1 первого канала соединен со вторым входом блока усилителей с временной автоматической регулировкой усиления, разъем входного сигнала второго канала соединен с первым входом устройства квадратурного фазового детектирования А2 второго канала, первый вход устройства предварительной обработки A3 первого канала соединен с третьим входом первого мультиплексора, второй вход устройства предварительной обработки A3 первого канала соединен со вторым входом первого аналого-цифрового преобразователя, выход первого аналого-цифрового преобразователя соединен с пятым входом устройства цифрового гетеродинирования, первый выход устройства цифрового гетеродинирования соединен с первым входом первого N-разрядного накапливающего сумматора, первый выход первого N-разрядного накапливающего сумматора соединен с первым входом первого мультиплексора, выход первого мультиплексора соединен с первым входом оперативного запоминающего устройства череспериодной обработки и со вторым входом первого коммутатора, выход первого оперативного запоминающего устройства череспериодной обработки соединен с первым входом оптимального фильтра, выход первого оптимального фильтра соединен с первым входом первой микросхемы FiFo, выход первой микросхемы FiFo соединен с первым входом первого коммутатора напряжений, выход первого коммутатора напряжений соединен с первым выходом устройства предварительной обработки A3 первого канала, третий вход устройства предварительной обработки A3 первого канала соединен с первым входом второго аналого-цифрового преобразователя, выход второго аналого-цифрового преобразователя соединен со вторым входом устройства цифрового гетеродинирования, второй выход устройства цифрового гетеродинирования соединен с первым входом второго N-разрядного накапливающего сумматора, первый выход второго N-разрядного накапливающего сумматора соединен с первым входом второго мультиплексора, выход второго мультиплексора соединен с первым входом второго оперативного запоминающего устройства череспериодной обработки и со вторым входом второго коммутатора, выход второго оперативного запоминающего устройства череспериодной обработки соединен с первым входом второго оптимального фильтра, выход второго оптимального фильтра соединен с первым входом второй микросхемы FiFo, выход второй микросхемы FiFo соединен с первым входом второго коммутатора, выход второго коммутатора соединен со вторым выходом устройства предварительной обработки A3 первого канала, второй выход первого N-разрядного накапливающего сумматора соединен с первым входом первого реверсивного счетчика, выход первого реверсивного счетчика соединен с входом первого цифроаналогового преобразователя, выход первого цифроаналогового преобразователя соединен с первым входом первого аналого-цифрового преобразователя, второй выход второго N-разрядного накапливающего сумматора соединен с первым входом второго реверсивного счетчика, выход второго реверсивного счетчика соединен с входом второго цифроаналогового преобразователя, выход второго цифроаналогового преобразователя соединен со вторым входом второго аналого-цифрового преобразователя, четвертый вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго аналого-цифрового преобразователя, с третьим входом первого аналого-цифрового преобразователя, с первым входом устройства цифрового гетеродинирования, пятый вход устройства предварительной обработки A3 первого канала соединен с входом постоянного запоминающего устройства устройства цифрового гетеродинирования, первый выход постоянного запоминающего устройства устройства цифрового гетеродинирования соединен с третьим входом устройства цифрового гетеродинирования, второй выход постоянного запоминающего устройства устройства цифрового гетеродинирования соединен с четвертым входом устройства цифрового гетеродинирования, шестой вход устройства предварительной обработки A3 первого канала соединен со вторым входом второго N-разрядного накапливающего сумматора и со вторым входом первого N-разрядного накапливающего сумматора, седьмой вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго N-разрядного накапливающего сумматора и с третьим входом первого N-разрядного накапливающего сумматора, восьмой вход устройства предварительной обработки A3 первого канала соединен со вторым входом второго реверсивного счетчика, со вторым входом второго мультиплексора, с входом формирователя адреса записи, со вторым входом первого мультиплексора и со вторым входом первого реверсивного счетчика, девятый вход устройства предварительной обработки A3 первого канала соединен с входом формирователя адреса чтения, с входом формирователя опорных сигналов, со вторым входом второй микросхемы FiFo, с входом устройства управления и со вторым входом первой микросхемы FiFo, десятый вход устройства предварительной обработки A3 первого канала соединен с третьим входом первого коммутатора и третьим входом второго коммутатора, первый выход устройства управления соединен с третьим входом первой микросхемы FiFo, второй выход устройства управления соединен с четвертым входом первой микросхемы FiFo, третий выход устройства управления соединен с третьим входом второй микросхемы FiFo, четвертый выход устройства управления соединен с четвертым входом второй микросхемы FiFo, первый выход формирователя опорных сигналов соединен со вторым входом первого оптимального фильтра, второй выход формирователя опорных сигналов соединен со вторым входом второго оптимального фильтра, выход формирователя адреса записи соединен со вторым входом первого оперативного запоминающего устройства череспериодной обработки и вторым входом второго оперативного запоминающего устройства череспериодной обработки, выход формирователя адреса чтения соединен с третьим входом первого оперативного запоминающего устройства череспериодной обработки и с третьим входом второго оперативного запоминающего устройства череспериодной обработки, одиннадцатый вход устройства предварительной обработки A3 первого канала соединен с третьим входом второго мультиплексора, межкаскадные связи в устройстве квадратурного фазового детектирования А2 второго канала аналогичны межкаскадным связям в устройстве квадратурного фазового детектирования А1 первого канала, межкаскадные связи устройства предварительной обработки А4 второго канала аналогичны межкаскадным связям в устройстве предварительной обработки A3 первого канала.

| RU 2000102468 А, 20.03.2002 | |||

| РАДИОПРИЕМНОЕ УСТРОЙСТВО КОГЕРЕНТНОЙ РЛС | 2000 |

|

RU2189054C2 |

| US 5019826, 28.05.1991 | |||

| US 5959573 A, 28.09.1999 | |||

| ЕР 0499706 А2, 26.08.1992 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

2005-06-27—Публикация

2003-10-23—Подача