Изобретение относится к приемному тракту радиолокационных или аналогичных систем и предназначено для обеспечения высокопроизводительной первичной цифровой обработки сигналов в реальном масштабе времени во всех режимах работы бортовой радиолокационной станции (БРЛС).

Одним из основных факторов, определяющих структуру модуля аналого-цифрового преобразователя, является выбранный метод обработки сигнала на промежуточной частоте: разделение на квадратурные составляющие и перенос спектра сигнала на видеочастоту с обеспечением возможности перестройки частоты гетеродина.

В настоящее время для этой цели широко используются аналоговые фазовые детекторы. [Дудник П.И., Чересов Ю.И. Авиационные радиолокационные устройства. - М.: ВВИА им. Проф. Н.Е.Жуковского, 1986, с.247, рис.8.15]. При этом сигнал гетеродина может быть фиксированным (fг=fп) или перестраиваемым по частоте. В первом случае для управления значением центральной частоты полосы анализа применяется метод цифрового гетеродинирования после оцифровки сигнала [патент РФ 2225623, МПК G 01 S 7/285, 7/26, 2004]. Во втором случае для получения сигнала гетеродина применяются специальные, довольно сложные устройства - цифровые управляемые гетеродины [патент US 4292635 А, 1996, патент РФ 2123709, 1998]. При этом количество цифровых управляемых гетеродин в БРЛС должно быть равно количеству приемных каналов, количество фазовых детекторов или синхронных преобразователей должно быть равно двум в каждом приемном канале.

Наиболее близким по технической сущности и выбран в качестве прототипа радиолокационный приемник с цифровым гетеродинированием [патент РФ 2225623, МПК G 01 S 7/285, 7/26, 2004], содержащий кварцевый генератор, формирователь опорного сигнала, два цифровых сумматора, магистраль параллельной информации, n каналов приема, состоящие каждый из аналогового сумматора и когерентного приемника с цифровым выходом, при этом когерентный приемник с цифровым выходом состоит из дешифратора, блока резонансных усилителей с временной автоматической регулировкой усиления, двух синхронных преобразователей частоты, двух фильтров низкой частоты, двух аналого-цифровых преобразователей, фазовращателя, устройства цифрового гетеродинирования и постоянно-запоминающего устройства. В известном приемнике использован аналоговый метод преобразования сигнала. Использование аналогового метода переноса спектра сигнала на видеочастоту ограничивается следующими факторами:

- неортогональность опорных сигналов для фазового детектора;

- различие коэффициентов передачи квадратурных каналов;

- неидентичность амплитудно-частотных характеристик и фазочастотных характеристик квадратурных каналов;

- дрейф нуля фазового детектора;

- нелинейность фазового детектора.

Наличие первых двух факторов существенно снижает эффективность цифровой обработки сигналов, в частности, цифрового гетеродинирования. Для устранения влияния дрейфа нуля фазовых детекторов на результаты цифровой обработки сигналов в состав каждого квадратурного канала необходимо вводить специальные устройства компенсации постоянной составляющей. Нелинейность фазовых детекторов приводит к снижению динамического диапазона БРЛС.

На основании вышеизложенного можно сделать вывод, что использование в перспективных бортовых радиолокационных станциях (БРЛС) аналоговых методов обработки сигналов на промежуточной частоте и технически и экономически нецелесообразно.

От всех перечисленных недостатков свободны цифровые методы разложения сигналов на квадратурные составляющие и переноса спектра на видеочастоту, которые раньше не применялись из-за отсутствия соответствующей элементной базы.

Технический результат, на который направлено изобретение, является расширение динамического диапазона, повышение точности преобразования широкополосных аналоговых сигналов в последовательности цифровых от счетов, формирование реальной и мнимой квадратурных составляющих оцифрованных сигналов, с выхода каждого из приемных каналов бортовой РЛС, подготовка первичной информации об обнаруженных и сопровождаемых объектах и выдачи ее в системы управления бортовой РЛС, при этом конструктивное исполнение должно быть выполнено в габаритах "Евромеханика 3U".

Технический результат достигается тем, что модуль аналого-цифрового преобразователя (АЦП) содержит два канала цифровой обработки сигнала, состоящих каждый из формирователя дифференциальных сигналов, аналого-цифрового преобразователя, цифрового формирователя квадратур, устройства цифрового гетеродинирования, постоянного запоминающего устройства, цифрового сумматора, оптимального фильтра, мультиплексора и контроллера низковольтной дифференциальной линии передачи информации, кроме того, в модуль введены общие для обоих каналов цифровой обработки сигнала формирователь частоты дискретизации и устройство управления. При этом вход формирователя дифференциальных сигналов является первым входом канала цифровой обработки сигнала. Выход формирователя дифференциальных сигналов соединен с первым входом аналого-цифрового преобразователя. Второй вход аналого-цифрового преобразователя является вторым входом канала цифровой обработки сигнала. Первый выход аналого-цифрового преобразователя соединен с первым входом цифрового формирователя квадратур. Второй выход аналого-цифрового преобразователя соединен со вторым входом цифрового формирователя квадратур. Выход цифрового формирователя квадратур соединен с первым входом устройства цифрового гетеродинирования. Второй вход устройства цифрового гетеродинирования соединен с выходом постоянного запоминающего устройства. Третий вход устройства цифрового гетеродинирования является третьим входом канала цифровой обработки сигнала. Первый выход устройства цифрового гетеродинирования соединен с первым входом цифрового сумматора. Второй выход устройства цифрового гетеродинирования соединен с входом постоянного запоминающего устройства. Второй вход цифрового сумматора является четвертым входом канала цифровой обработки сигнала. Выход цифрового сумматора соединен с первым входом оптимального фильтра и с первым входом мультиплексора. Второй вход оптимального фильтра является пятым входом канала цифровой обработки сигнала. Выход оптимального фильтра соединен со вторым входом мультиплексора. Третий вход мультиплексора является шестым входом канала цифровой обработки сигнала. Выход мультиплексора соединен с входом контроллера низковольтной дифференциальной линии передачи информации, выход которого является выходом канала цифровой обработки сигнала. Вход формирователя частоты дискретизации является входом опорного сигнала. Первый выход формирователя частоты дискретизации соединен со вторым входом первого канала цифровой обработки сигнала. Второй выход формирователя частоты дискретизации соединен со вторым входом второго канала цифровой обработки сигнала. Первый вход устройства управления является входом последовательной линии связи по управляющей информации. Второй вход устройства управления является входом импульса начала отсчета. Первый выход устройства управления соединен с третьим входом первого канала цифровой обработки сигнала. Второй выход устройства управления соединен с четвертым входом первого канала цифровой обработки сигнала. Третий выход устройства управления соединен с пятым входом первого канала цифровой обработки сигнала. Четвертый выход устройства управления соединен с шестым входом первого канала цифровой обработки сигнала. Пятый выход устройства управления соединен с третьим входом второго канала цифровой обработки сигнала. Шестой выход устройства управления соединен с четвертым входом второго канала цифровой обработки сигнала. Седьмой выход устройства управления соединен с пятым входом второго канала цифровой обработки сигнала. Восьмой выход устройства управления соединен с шестым входом второго канала цифровой обработки сигнала.

Отличительными признаками от прототипа является то, что в каждый канал цифровой обработки сигнала введены формирователь дифференциальных сигналов, цифровой формирователь квадратур, оптимальный фильтр, мультиплексор и контроллер низковольтной дифференциальной линии передачи информации, кроме этого в модуль аналого-цифрового преобразователя введены общие для обоих каналов цифровой обработки сигнала формирователь частоты дискретизации и устройство управления, а также связи между ними.

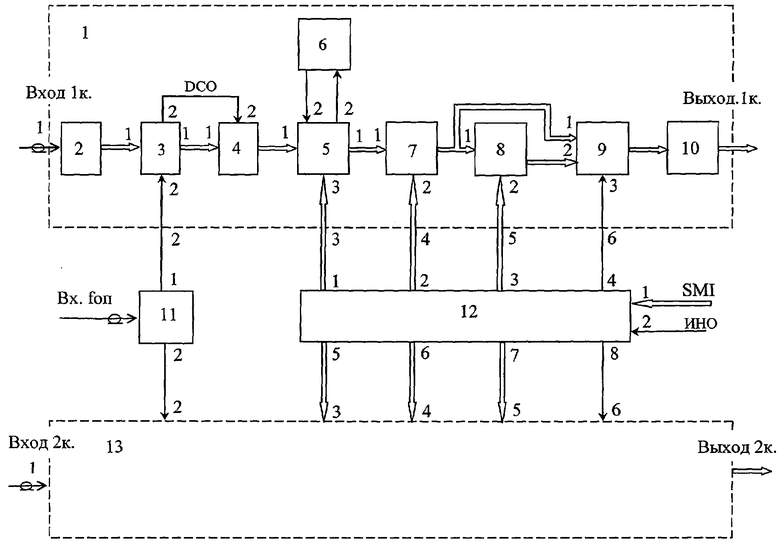

На чертеже представлена функциональная схема модуля аналого-цифрового преобразователя.

Модуль аналого-цифрового преобразователя содержит два канала цифровой обработки сигнала первый 1 и второй 13, состоящих каждый из формирователя дифференциальных сигналов 2, аналого-цифрового преобразователя 3, цифрового формирователя квадратур 4, устройства цифрового гетеродинирования 5, постоянного запоминающего устройства 6, цифрового сумматора 7, оптимального фильтра 8, мультиплексора 9 и контроллера низковольтной дифференциальной линии передачи информации 10, кроме того, в модуль введены общие для первого 1 и второго 13 каналов цифровой обработки сигнала формирователь частоты дискретизации 11 и устройство управления 12.

При этом вход формирователя дифференциальных сигналов 2 является первым входом первого 1 канала цифровой обработки сигнала. Выход формирователя дифференциальных сигналов 2 соединен с первым входом аналого-цифрового преобразователя 3. Второй вход аналого-цифрового преобразователя 3 является вторым входом первого 1 канала цифровой обработки сигнала. Первый выход аналого-цифрового преобразователя 3 соединен с первым входом цифрового формирователя квадратур 4. Второй выход аналого-цифрового преобразователя 3 соединен со вторым входом цифрового формирователя квадратур 4. Выход цифрового формирователя квадратур 4 соединен с первым входом устройства цифрового гетеродинирования 5. Второй вход устройства цифрового гетеродинирования 5 соединен с выходом постоянного запоминающего устройства 6. Третий вход устройства цифрового гетеродинирования 5 является третьим входом первого 1 канала цифровой обработки сигнала. Первый выход устройства цифрового гетеродинирования 5 соединен с первым входом цифрового сумматора 7. Второй выход устройства цифрового гетеродинирования 5 соединен с входом постоянного запоминающего устройства 6. Второй вход цифрового сумматора 7 является четвертым входом первого 1 канала цифровой обработки сигнала. Выход цифрового сумматора 7 соединен с первым входом оптимального фильтра 8 и с первым входом мультиплексора 9. Второй вход оптимального фильтра 8 является пятым входом первого 1 канала цифровой обработки сигнала. Выход оптимального фильтра 8 соединен со вторым входом мультиплексора 9. Третий вход мультиплексора 9 является шестым входом первого 1 канала цифровой обработки сигнала. Выход мультиплексора 9 соединен с входом контроллера низковольтной дифференциальной линии передачи информации 10, выход которого является выходом первого 1 канала цифровой обработки сигнала. Вход формирователя частоты дискретизации 11 является входом опорного сигнала Bx.fоп. Первый выход формирователя частоты дискретизации 11 соединен со вторым входом первого 1 канала цифровой обработки сигнала. Второй выход формирователя частоты дискретизации 11 соединен со вторым входом второго канала цифровой обработки сигнала 13. Первый вход устройства управления 12 является входом последовательной линии связи по управляющей информации SMI (Serial Management Interface). Второй вход устройства управления 12 является входом импульса начала обработки ИНО. Первый выход устройства управления 12 соединен с третьим входом первого 1 канала цифровой обработки сигнала. Второй выход устройства управления 12 соединен с четвертым входом первого 1 канала цифровой обработки сигнала. Третий выход устройства управления 12 соединен с пятым входом первого 1 канала цифровой обработки сигнала. Четвертый выход устройства управления 12 соединен с шестым входом первого 1 канала цифровой обработки сигнала. Пятый выход устройства управления 12 соединен с третьим входом второго 13 канала цифровой обработки сигнала. Шестой выход устройства управления 12 соединен с четвертым входом второго 13 канала цифровой обработки сигнала. Седьмой выход устройства управления 12 соединен с пятым входом второго 13 канала цифровой обработки сигнала. Восьмой выход устройства управления 12 соединен с шестым входом второго 13 канала цифровой обработки сигнала.

Работает модуль аналого-цифрового преобразователя следующим образом.

Входные сигналы на промежуточной частоте поступают по высокочастотным кабельным соединениям на первый вход первого 1 канала цифровой обработки сигнала и далее на вход формирователя дифференциальных сигналов 2.

Формирователь дифференциальных сигналов 2 выполнен на высокочастотном трансформаторе, с выхода которого снимается дифференциальный сигнал и подается на первый вход аналого-цифрового преобразователя 3.

Аналого-цифровой преобразователь 3 обеспечивает дискретизацию сигналов по уровню с формированием двенадцати разрядных данных. Для исключения наводок от выходных сигналов аналого-цифрового преобразователя 3 на входные цепи передача данных от аналого-цифрового преобразователя 3 на цифровой формирователь квадратур 4 производится по низковольтным дифференциальным линиям передачи Low-Voltage Differential Signaling (LVDS). Синхронизация работы аналого-цифрового преобразователя 3 обеспечивается сигналами, поступающими на аналого-цифровой преобразователь 3 от формирователя частоты дискретизации 11, с первого выхода формирователя частоты дискретизации 11 на второй вход аналого-цифрового преобразователя 3. Входной сигнал для формирователя частоты дискредитации 11 с частотой входа опорного сигнала fоп поступает в модуль аналого-цифрового преобразователя из приемопередающего модуля БРЛС (на схеме не показано). Формируется сигнал дискретизации умножением на два частоты опорного сигнала. При этом обеспечивается когерентность сигнала дискретизации аналого-цифрового преобразователя 3 с входным сигналом и сигналами синхронизатора БРЛС.

Цифровой формирователь квадратур 4 обеспечивает представление сигналов в комплексной форме с формированием реальной (Re) и мнимой (Im) квадратурных составляющих. Синхронизация цифрового формирователя квадратур 4 по приему информации от аналого-цифрового преобразователя 3 и обработке обеспечивается сигналом с выхода синхронизации данных DCO (Data Clock Output) от аналого-цифрового преобразователя 3, поступающим со второго выхода аналого-цифрового преобразователя 3 на второй вход цифрового формирователя квадратур 4.

С цифрового формирователя квадратур 4 реальная и мнимая квадратурные составляющие сигнала поступают на первый вход устройства цифрового гетеродинирования 5, на второй вход которого поступают с выхода постоянного запоминающего устройства 6 корректирующие коэффициенты. Адрес чтения информации из постоянного запоминающего устройства 6 передается на вход постоянного запоминающего устройства 6 со второго выхода устройства цифрового гетеродинирования 5. Устройство цифрового гетеродинирования 5 выполняет операцию перемножения двух комплексных чисел: выборок составляющих квадратур сигнала, поступающих из цифрового формирователя квадратур 4, и корректирующих коэффициентов, поступающих из постоянного запоминающего устройства 6. Код частоты гетеродина поступает на третий вход устройства цифрового гетеродинирования 5 с первого выхода устройства управления 12.

После гетеродинирования сигнал поступает на первый вход цифрового сумматора 7, где происходит суммирование отсчетов сигнала на интервале одного элемента дальности. Количество суммирующих выборок определяется кодом, поступающим на второй вход цифрового сумматора 7 со второго выхода устройства управления 12. После суммирования, при наличии команды "Включение оптимального фильтра", поступающей на третий вход мультиплексора 9 с четвертого выхода устройства управления 12, сигнал проходит оптимальную фильтрацию (сжатие фазокодомодулированного сигнала (ФКМС) в оптимальном фильтре 8 и поступает на второй вход мультиплексора 9. Номер кода ФКМС поступает на второй вход оптимального фильтра 8 с третьего выхода устройства управления 12. При отсутствии команды "Включение оптимального фильтра" сигнал после суммирования поступает на первый вход мультиплексора 9. С мультиплексора 9 сигнал поступает на контроллер низковольтной дифференциальной линии передачи информации 10.

Управление работой устройства цифрового гетеродинирования 5, цифрового сумматора 7, оптимального фильтра 8 и мультиплексора 9 обеспечивается от устройства управления 12, которое выполняет преобразование последовательного кода управляющей информации, поступающей по последовательной линии связи по управляющей информации SMI в параллельный код управляющих сигналов. Синхронизация работы устройства управления 12 обеспечивается импульсом начала обработки ИНО, поступающим в модуль от внешнего модуля синхронизации.

Контроллер низковольтной дифференциальной линии передачи информации 10 обеспечивает передачу выходной цифровой информации модуля аналого-цифрового преобразователя в модуль вторичной обработки сигналов БРЛС одновременно (раздельно) по реальной и мнимой квадратурам.

Работа второго 13 канала цифровой обработки сигналов аналогична работе первого 1 канала цифровой обработки сигналов модуля аналого-цифрового преобразователя.

Для подтверждения возможности реализации технического решения был изготовлен опытный образец модуля аналого-цифрового преобразователя с тактико-техническими характеристиками для конкретной БРЛС.

Возможность реализации цифрового формирования квадратур 4 определена наличием аналого-цифрового преобразователя 3 с высокой частотой дискретизации. Цифровое формирование квадратур обеспечивается умножением дискретизированного входного сигнала на два дискретных опорных гармонических сигнала, сдвиг по фазе между которыми составляет 90 градусов, с последующей фильтрацией гармоник сигнала цифровыми фильтрами нижних частот. Реализация цифрового формирователя квадратур 4 обеспечивается использованием программируемой логической интегральной схемы (ПЛИС). Цифровая обработка сигналов в модуле аналого-цифрового преобразователя обеспечивает накопление информации в пределах дискрета дальности, цифровое гетеродинирование, оптимальную фильтрацию (временное сжатие ФКМС) для различных видов ФКМС. Цифровая обработка сигналов в модуле функционально обеспечивается использованием ПЛИС. Цифровое гетеродинирование осуществляется в соответствии с алгоритмом:

Re2[i]=Re1[i]·Kr[i]+Im1[i]·Ki[i]

Im2[i]=Im1[i]·Kr[i]-Re1[i]·Ki[i]

где Re2[i], Im2[i] - квадратурные составляющие выходного сигнала устройства цифрового гетеродинирования 5;

Re1[i], Im1[i] - квадратурные составляющие входного сигнала устройства цифрового гетеродинирования 5;

Kr[i], Ki[i] - корректирующие коэффициенты цифрового гетеродинирования из постоянно запоминающего устройства 6.

Управление режимами работы модуля аналого-цифрового преобразователя производится от центрального процессора с использованием интерфейса SMI (Serial Management Interface). Интерфейс SMI представляет собой последовательную синхронную двухпроводную шину, обеспечивающую доступ по записи и чтению к 16-разрядным регистрам устройств. Шина является хост-центричной, ею управляет один контроллер, инициирующий транзакции, а все подключаемые устройства являются ведомыми. Интерфейс SMI реализован на ПЛИС.

Передача данных из модуля аналого-цифрового преобразователя производится по четырем встроенным в ПЛИС каналам LVDS. Одновременно передаются реальные и мнимые квадратуры первого 1 и второго 13 каналов цифровой обработки сигнала модуля аналого-цифрового преобразователя.

Интерфейс LVDS использует дифференциальную передачу сигналов с малыми сигнальными уровнями. Передатчик управляет дифференциальной линией. В линию выдается токовая посылка с током 3,5 мА. Нагрузкой линии служат параллельно включенные дифференциальный LVDS-приемник и 100 Ом резистор. Сам приемник имеет высокое входное сопротивление, и основное формирование сигнала происходит на нагрузочном резисторе. При токе линии 3,5 мА на нем формируется падение напряжения 350 мВ, которое и детектируется приемником. При переключении направления тока в линии меняется полярность напряжения на нагрузочном резисторе, формируя состояния логического нуля и логической единицы.

Интерфейс LVDS имеет высокую скорость передачи данных. При выбранной тактовой частоте 56 МГц скорость составляет 560 Мбит/с. Используемый дифференциальный метод передачи сигналов позволяет максимально снизить влияние внешних наводок и, следовательно, расширить динамический диапазон приемника. Малое изменение напряжения, симметричные линии передачи и низкое нарастание напряжения (1 В/нс) обусловливают малый уровень наводок от самого интерфейса. В свою очередь, малый уровень перекрестных наводок и низкая чувствительность к внешним наводкам позволяют использовать высокую плотность соединений как на печатной плате, так и в кабеле. Метод передачи LVDS не зависит от напряжения питания и работает при напряжении питания передатчика и приемника 5, 3 или 2,5 В. Используемый метод передачи позволяет также существенно снизить энергопотребление интерфейса. На 100 Ом нагрузке LVDS при падении напряжения 400 мВ составляет 1,2 мВт.

Конструктивное исполнение модуля аналого-цифрового преобразователя выполнено в габаритах "ЕВРОМЕХАНИКА-3U". Реализация модуля в заданных габаритах обеспечена использованием безкорпусных элементов (поверхностный монтаж) и выполнением устройства управления 12 и цифрового формирователя квадратур 4, устройства цифрового гетеродинирования 5, оптимального фильтра 8, мультиплексора 9, контроллера низковольтной дифференциальной линии передачи информации 10 для обоих каналов на базе одной ПЛИС. Стыковочный с внешними устройствами разъем использован стандарта DIN, имеющий 60 н/ч контактов и 4 в/ч соединения. Масса модуля не более 200 г.

Исполнение модуля аналого-цифрового преобразователя в габаритах "ЕВРОМЕХАНИКА-3U" позволяет конструктивно в едином корпусе выполнить цифровой приемник и вычислительный комплекс. Проектирование современного высокопроизводительного бортового вычислительного комплекса, способного обеспечить решение всего требуемого объема задач цифровой обработки сигналов, является актуальным направлением развития бортовых РЛС. Встраивание бортового вычислительного комплекса в модернизируемые РЛС представляется необходимым и очень важным этапом совершенствования авиационной техники с целью улучшения ее характеристик.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С КАНАЛАМИ ВЫСОКОГО РАЗРЕШЕНИЯ | 2007 |

|

RU2344436C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК | 2007 |

|

RU2332682C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С УСТРОЙСТВОМ УПРАВЛЕНИЯ | 2013 |

|

RU2535931C1 |

| БЛОК ПРИЕМА И СИНХРОНИЗАЦИИ | 2012 |

|

RU2497148C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2008 |

|

RU2399088C2 |

| Блок приема и синхронизации с функцией формирования дополнительных бланкирующих импульсов | 2023 |

|

RU2821958C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО КОГЕРЕНТНОЙ РЛС С ОПТИМАЛЬНОЙ ФИЛЬТРАЦИЕЙ СИГНАЛА | 2003 |

|

RU2255351C1 |

| КОГЕРЕНТНЫЙ ПРИЕМНИК РЛС С ЦИФРОВЫМ УСТРОЙСТВОМ ДЛЯ АМПЛИТУДНОЙ И ФАЗОВОЙ КОРРЕКТИРОВКИ КВАДРАТУРНЫХ СОСТАВЛЯЮЩИХ ПРИНИМАЕМОГО СИГНАЛА | 2004 |

|

RU2273860C2 |

| ПРОЦЕССОР ЦИФРОВОГО РАЗДЕЛЕНИЯ КВАДРАТУР | 2022 |

|

RU2784002C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ДИАГРАММЫ НАПРАВЛЕННОСТИ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2011 |

|

RU2495449C2 |

Изобретение относится к приемному тракту радиолокационных или аналогичных систем. Техническим результатом является расширение динамического диапазона, повышение точности преобразования широкополосных аналоговых сигналов в последовательности цифровых от счетов, формирование реальной и мнимой квадратурных составляющих оцифрованных сигналов с выхода каждого из приемных каналов бортовой РЛС, подготовка первичной информации об обнаруженных и сопровождаемых объектах и выдачи ее в системы управления бортовой РЛС. Модуль аналого-цифрового преобразователя содержит два канала цифровой обработки сигнала, состоящих каждый из формирователя дифференциальных сигналов, аналого-цифрового преобразователя, цифрового формирователя квадратур, устройства цифрового гетеродинирования, постоянного запоминающего устройства, цифрового сумматора, оптимального фильтра, мультиплексора и контроллера низковольтной дифференциальной линии передачи информации, кроме того, в модуль введены общие для обоих каналов цифровой обработки сигнала формирователь частоты дискретизации и устройство управления. 1 ил.

Модуль аналого-цифрового преобразователя (АЦП), содержащий два канала цифровой обработки сигнала, состоящих каждый из аналого-цифрового преобразователя, устройства цифрового гетеродинирования, постоянного запоминающего устройства и цифрового сумматора, отличающийся тем, что в каждый канал цифровой обработки сигнала введены формирователь дифференциальных сигналов, цифровой формирователь квадратур, оптимальный фильтр, мультиплексор и контроллер низковольтной дифференциальной линии передачи информации, кроме этого в модуль АЦП введены общие для обоих каналов цифровой обработки сигнала формирователь частоты дискретизации и устройство управления, при этом вход формирователя дифференциальных сигналов является первым входом канала цифровой обработки сигнала, выход формирователя дифференциальных сигналов соединен с первым входом аналого-цифрового преобразователя, второй вход аналого-цифрового преобразователя является вторым входом канала цифровой обработки сигнала, первый выход аналого-цифрового преобразователя соединен с первым входом цифрового формирователя квадратур, второй выход аналого-цифрового преобразователя соединен со вторым входом цифрового формирователя квадратур, выход цифрового формирователя квадратур соединен с первым входом устройства цифрового гетеродинирования, второй вход устройства цифрового гетеродинирования соединен с выходом постоянно запоминающего устройства, третий вход устройства цифрового гетеродинирования является третьим входом канала цифровой обработки сигнала, первый выход устройства цифрового гетеродинирования соединен с первым входом цифрового сумматора, второй выход устройства цифрового гетеродинирования соединен с входом постоянного запоминающего устройства, второй вход цифрового сумматора является четвертым входом канала цифровой обработки сигнала, выход цифрового сумматора соединен с первым входом оптимального фильтра и с первым входом мультиплексора, второй вход оптимального фильтра является пятым входом канала цифровой обработки сигнала, выход оптимального фильтра соединен со вторым входом мультиплексора, третий вход мультиплексора является шестым входом канала цифровой обработки сигнала, выход мультиплексора соединен с входом контроллера низковольтной дифференциальной линии передачи информации, выход которого является выходом канала цифровой обработки сигнала, вход формирователя частоты дискретизации является входом опорного сигнала, первый выход формирователя частоты дискретизации соединен со вторым входом первого канала цифровой обработки сигнала, второй выход формирователя частоты дискретизации соединен со вторым входом второго канала цифровой обработки сигнала, первый вход устройства управления является входом последовательной линии связи по управляющей информации, второй вход устройства управления является входом импульса начала отсчета, первый выход устройства управления соединен с третьим входом первого канала цифровой обработки сигнала, второй выход устройства управления соединен с четвертым входом первого канала цифровой обработки сигнала, третий выход устройства управления соединен с пятым входом первого канала цифровой обработки сигнала, четвертый выход устройства управления соединен с шестым входом первого канала цифровой обработки сигнала, пятый выход устройства управления соединен с третьим входом второго канала цифровой обработки сигнала, шестой выход устройства управления соединен с четвертым входом второго канала цифровой обработки сигнала, седьмой выход устройства управления соединен с пятым входом второго канала цифровой обработки сигнала, восьмой выход устройства управления соединен с шестым входом второго канала цифровой обработки сигнала.

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С ЦИФРОВЫМ ГЕТЕРОДИНИРОВАНИЕМ | 2002 |

|

RU2225623C1 |

| УСТРОЙСТВО ПЕРВИЧНОЙ ОБРАБОТКИ СИГНАЛА КОГЕРЕНТНОЙ РЛС | 2002 |

|

RU2208237C1 |

| ПРИЕМНИК КОГЕРЕНТНОЙ РЛС С БОЛЬШИМ ДИНАМИЧЕСКИМ ДИАПАЗОНОМ | 2002 |

|

RU2231807C2 |

| US 2004090950 В1, 13.05.2004 | |||

| US 6340945 А, 22.01.2002 | |||

| US 65118909 А, 11.02.2003. | |||

Авторы

Даты

2006-12-27—Публикация

2005-06-01—Подача