Область изобретения

Настоящее изобретение, в общем, относится к виртуальным машинам, а более конкретно, к обеспечению поддержки процессора для монитора виртуальной машины.

Предшествующий уровень техники

Известный монитор виртуальной машины (МВМ, VMM) обычно выполняется на компьютере и для другого программного обеспечения представляет абстракцию одной или более виртуальных машин. Каждая виртуальная машина может функционировать как автономная платформа, выполняя собственную "гостевую операционную систему" (то есть, операционную систему, которая назначена МВМ в качестве ведущей). Предполагается, что гостевая операционная система функционирует таким образом, будто она выполняется на выделенном компьютере, а не на виртуальной машине. То есть предполагается, что гостевая операционная система управляет различными операциями компьютера и во время этих операций имеет доступ к аппаратным ресурсам. Аппаратные ресурсы могут включать в себя ресурсы, постоянно находящиеся в процессоре (например, регистры управления), и ресурсы, постоянно находящиеся в памяти (например, таблицы дескрипторов). Однако в среде виртуальной машины для обеспечения корректной работы виртуальных машин и защиты от виртуальных машин и между ними требуется, чтобы МВМ обладал максимальным контролем над этими ресурсами. Для этого МВМ обычно перехватывает и принимает решение по всем попыткам доступа к аппаратным ресурсам, осуществляемым гостевой операционной системой.

Существующие в настоящее время реализации МВМ могут быть основаны на программных технологиях, предназначенных для управления доступом к аппаратным ресурсам, осуществляемым гостевой операционной системой. Однако эти программные технологии могут иметь недостаточные возможности для предотвращения доступа гостевого программного обеспечение к некоторым полям в регистрах управления в процессоре и к памяти. Например, не может быть предотвращен доступ гостевой операционной системы к полю уровня привилегии запрашивающей стороны (УПЗ, RPL) в регистре сегмента кода микропроцессоров IA-32. Кроме того, существующим программным технологиям обычно характерны проблемы, связанные с эффективностью. Следовательно, требуется альтернативный механизм для поддержки работы МВМ.

Перечень фигур

На фигурах, на которых идентичные номера позиций относятся к подобным элементам, настоящее изобретение изображено в качестве примера, но не в качестве ограничения.

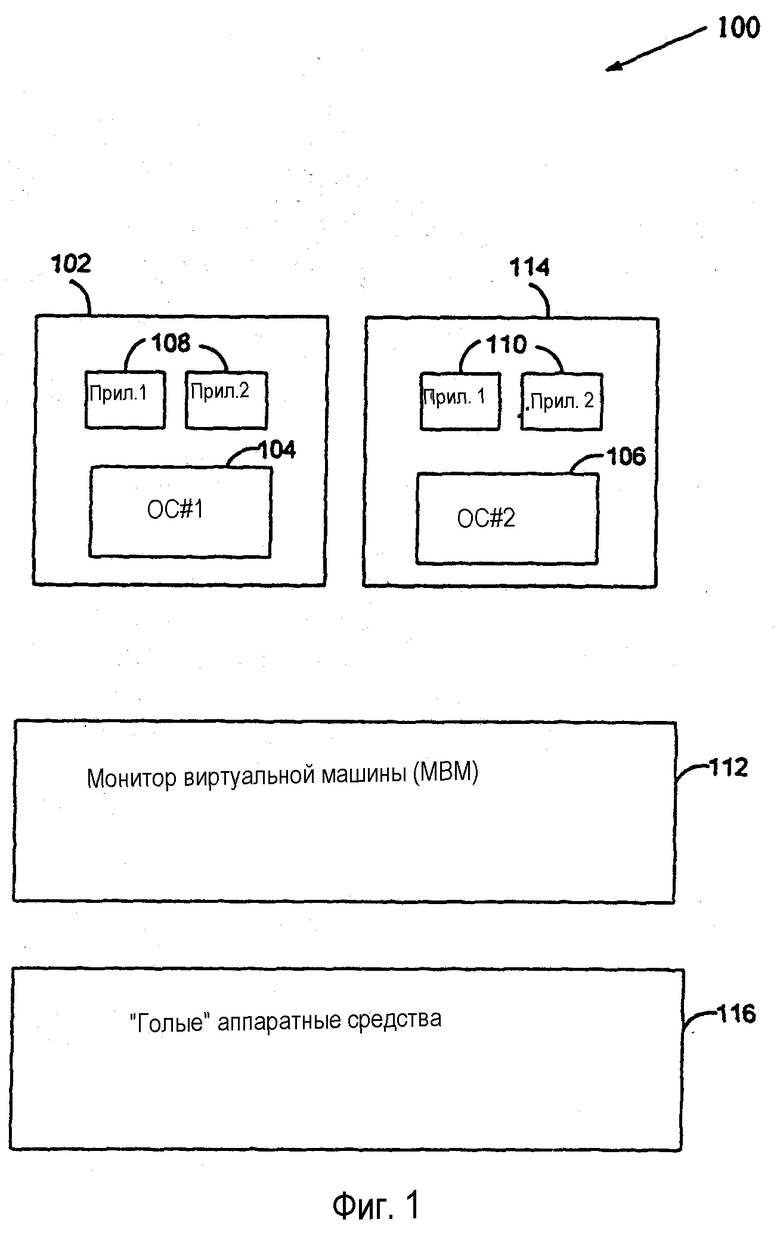

Фиг.1 изображает один вариант осуществления среды виртуальной машины.

Фиг.2 иллюстрирует работу монитора виртуальной машины на основе лишения гостя привилегий.

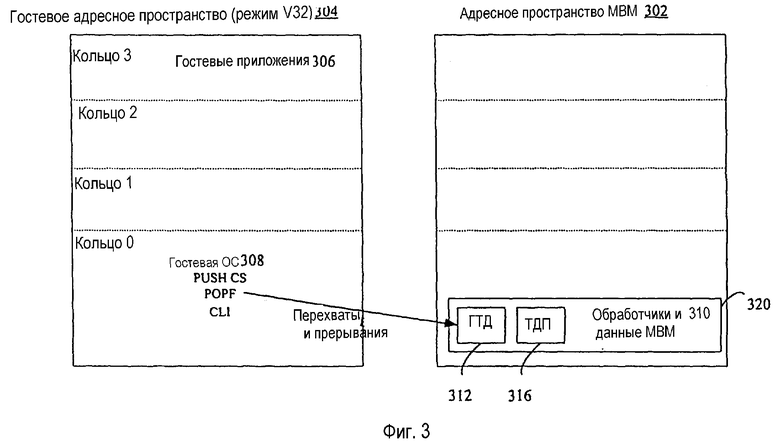

Фиг.3 изображает блок-схему системы, предназначенной для обеспечения поддержки процессора для монитора виртуальной машины, согласно одному варианту осуществления настоящего изобретения.

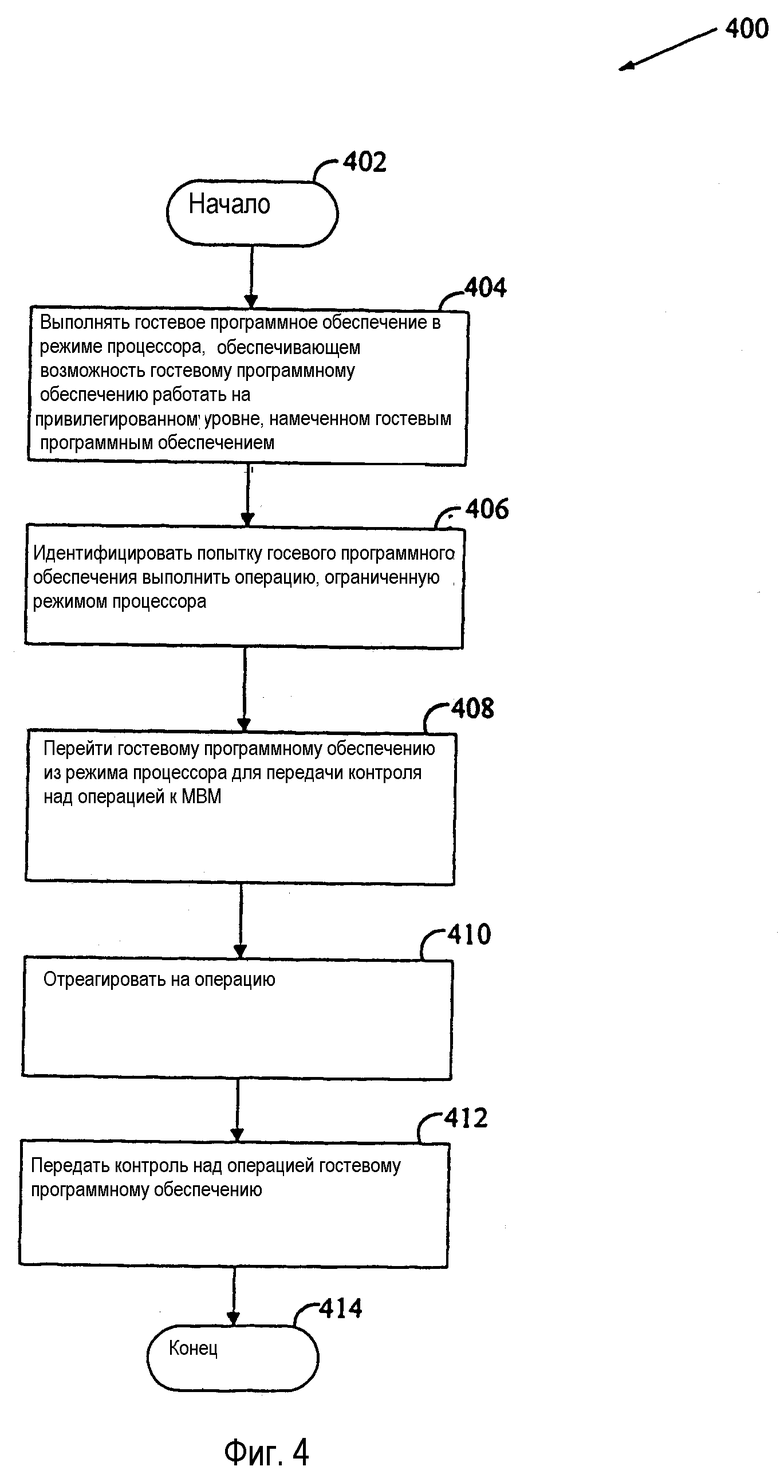

Фиг.4 изображает блок-схему алгоритма для способа обеспечения поддержки процессором для монитора виртуальной машины, согласно одному варианту осуществления настоящего изобретения.

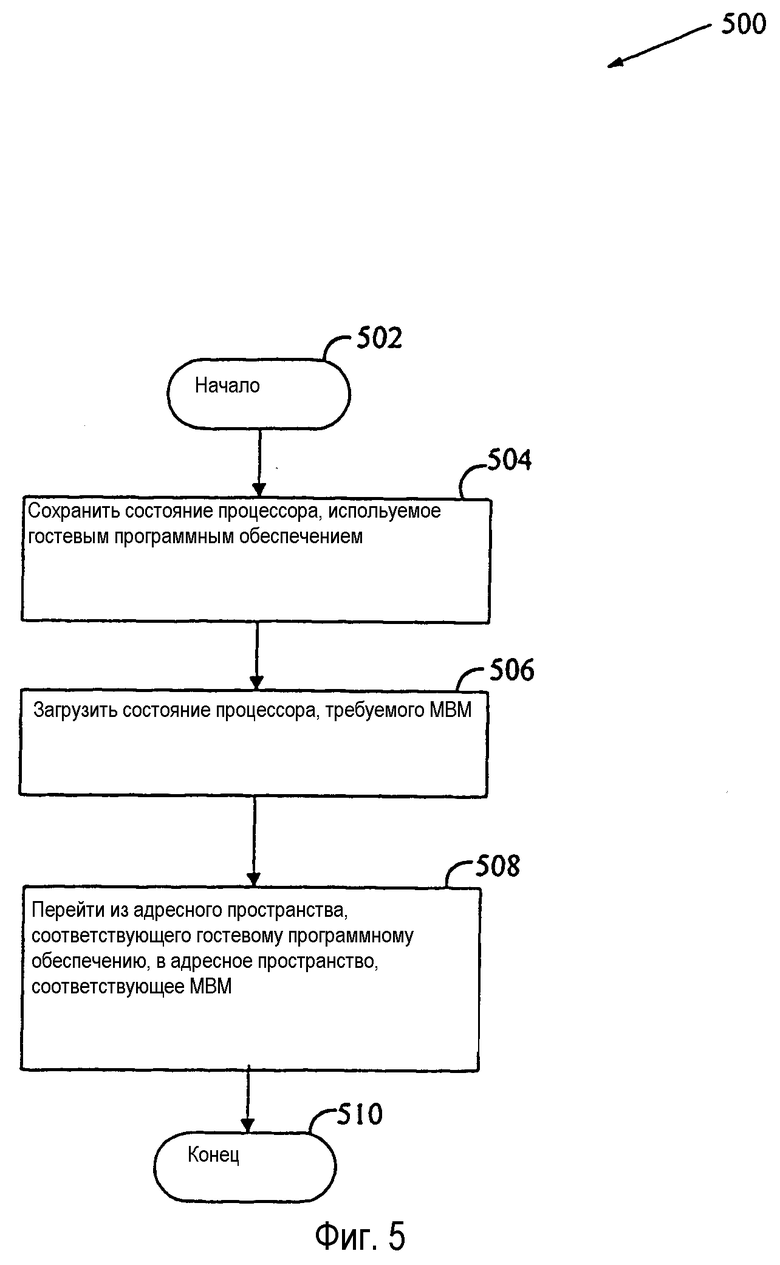

Фиг.5 изображает блок-схему алгоритма для способа выполнения перехода из режима V32, согласно одному варианту осуществления настоящего изобретения.

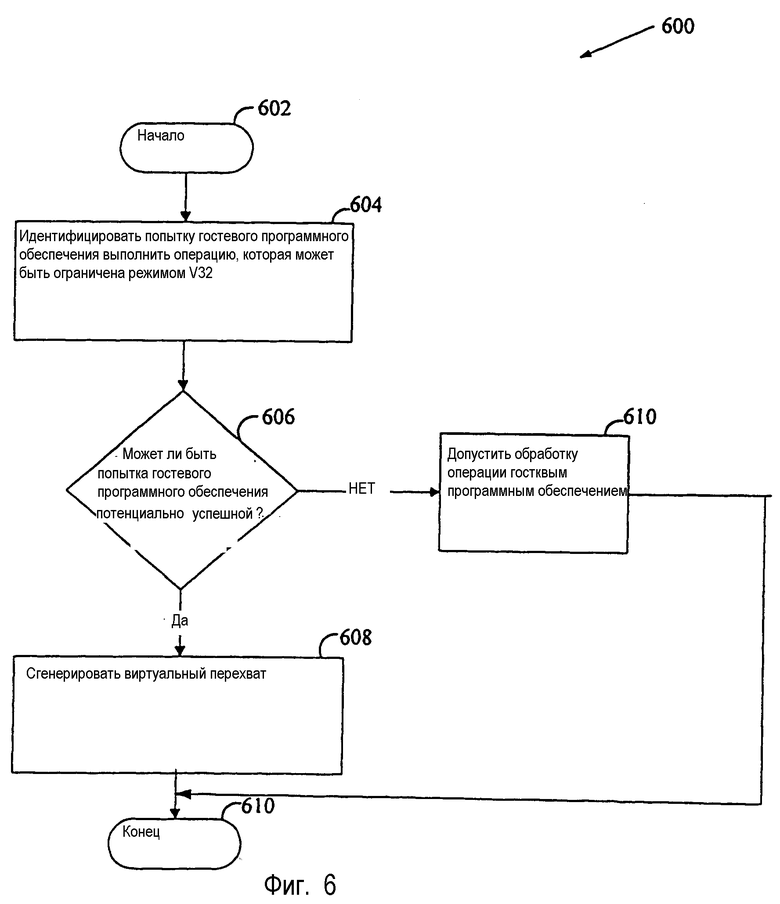

Фиг.6 изображает блок-схему алгоритма для способа генерирования виртуального перехвата, согласно одному варианту осуществления настоящего изобретения.

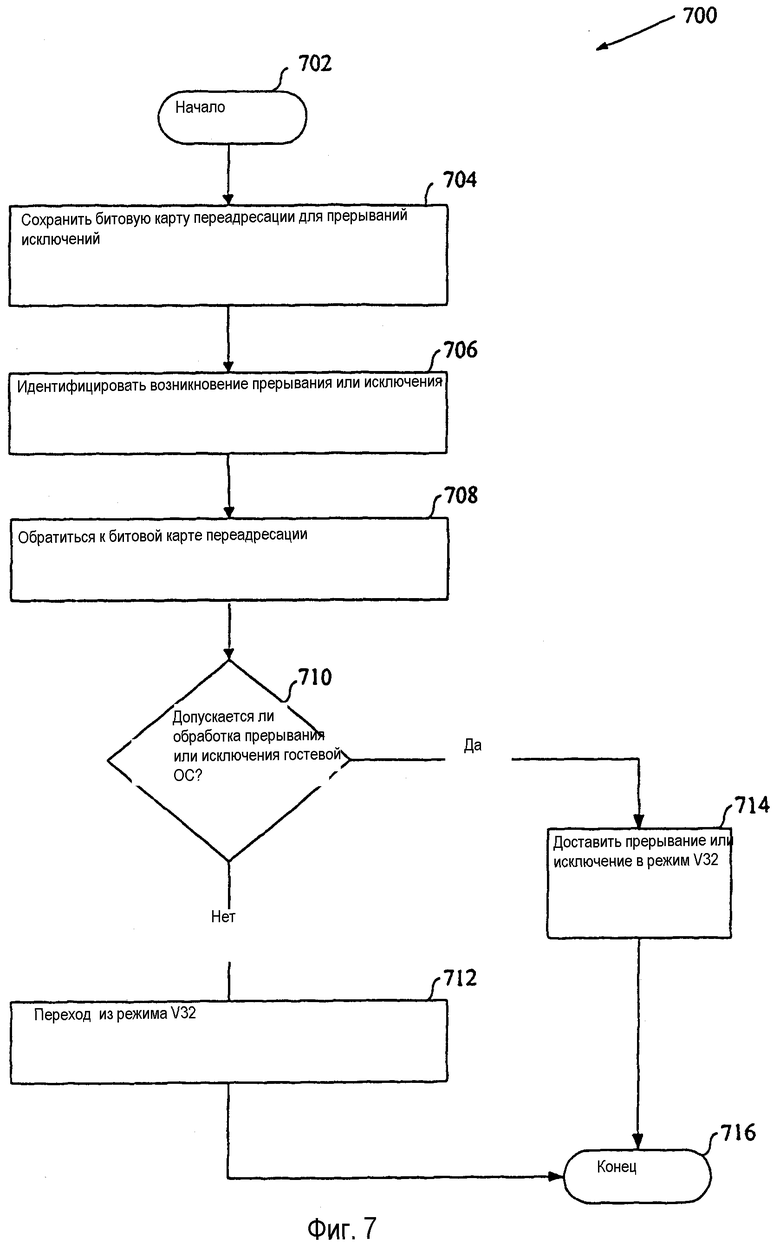

Фиг.7 изображает блок-схему алгоритма для способа поддержания карты матрицы переадресации, согласно одному варианту осуществления настоящего изобретения.

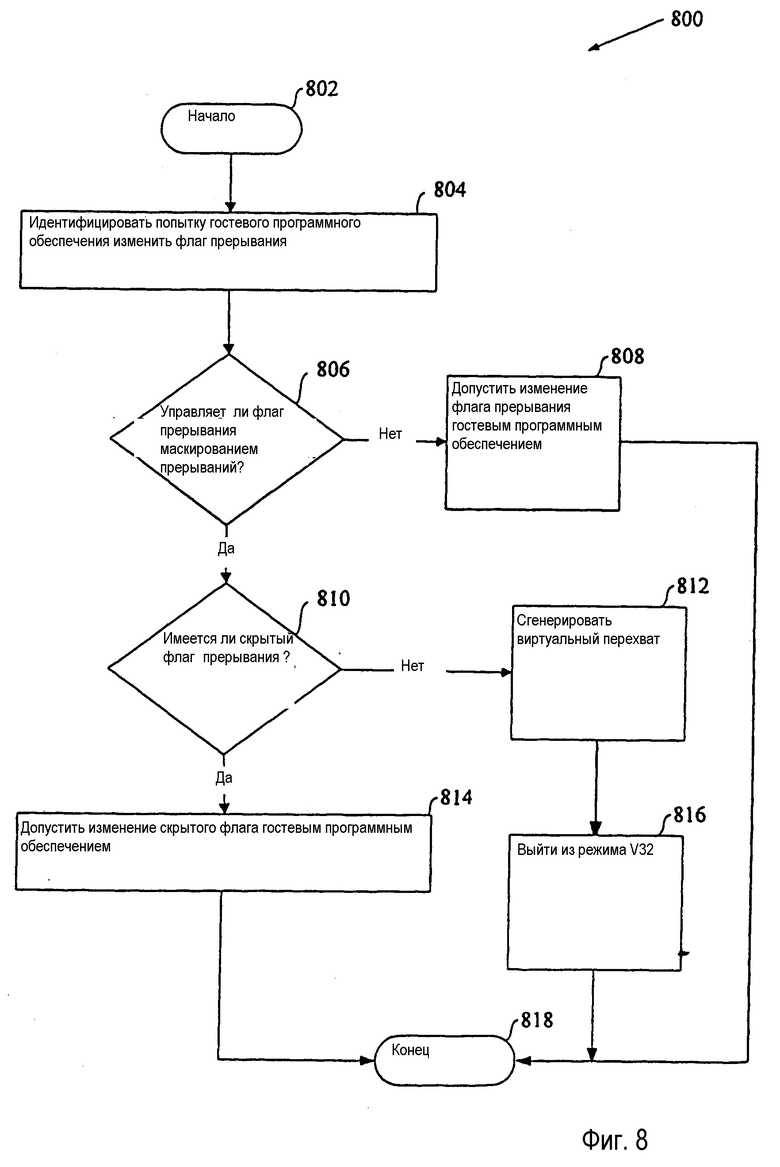

Фиг.8 изображает блок-схему алгоритма для способа для управления маскированием прерываний, согласно одному варианту осуществления настоящего изобретения.

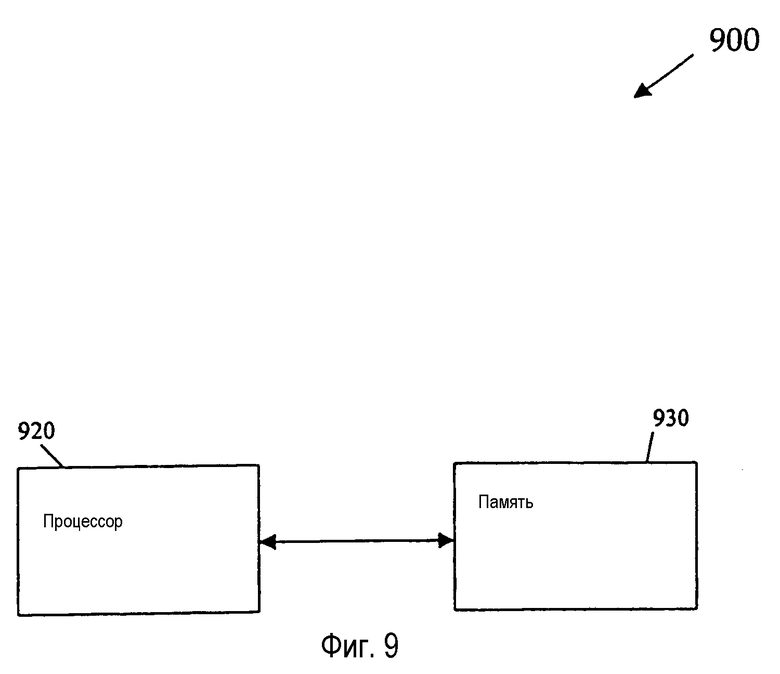

Фиг.9 изображает блок-схему одного варианта осуществления системы обработки данных.

Описание вариантов осуществления

Описаны способ и устройство, предназначенные для обеспечения поддержки процессора для монитора виртуальной машины. В последующем описании, чтобы обеспечить полное понимание настоящего изобретения, в пояснительных целях, изложены многочисленные специфические подробности. Однако для специалистов в данной области техники очевидно, что настоящее изобретение может быть реализовано без указанных специфических подробностей.

Некоторые фрагменты последующего подробного описания приведены в терминах алгоритмов и символических представлений операций над битами данных в памяти компьютера. Эти алгоритмические описания и представления являются средством, используемым специалистами в области обработки данных для выражения наиболее эффективным способом сущности своей работы для других специалистов в этой области техники. Алгоритм, здесь и в общем, полагается самосогласованной последовательностью этапов, ведущих к желаемому результату. Этапы представляют собой то, что требует физических манипуляций физическими величинами. Обычно, но не обязательно, эти величины принимают форму электрических или магнитных сигналов, которые можно сохранить, передать, объединить, сравнить, а также ими можно манипулировать иным образом. Эти сигналы, главным образом по причинам общего использования, иногда удобно определять как биты, значения, элементы, символы, знаки, термы, числа и т.д.

Однако следует иметь в виду, что все указанные и подобные им термины должны быть сопоставлены соответствующим физическим величинам и являются просто удобными обозначениями, применяемыми к этим величинам. Как ясно из последующего описания, если специально не оговорено иначе, в настоящем изобретении описания, в которых используются такие термины, как "обработка", "вычисление", "расчет", "определение" или "отображение" или подобные им, могут относиться к действию и процессам в вычислительной системе или в аналогичном электронном вычислительном устройстве, которое манипулирует данными, представленными как физические (электронные) величины в регистрах вычислительной системы и блоках памяти, и преобразует их в другие данные, аналогично представленные как физические величины в блоках памяти или регистрах вычислительной системы или в других подобных устройствах хранения информации, передачи или отображения.

Настоящее изобретение также относится к устройству, предназначенному для выполнения в нем операций. Это устройство может быть сконструировано специально для требуемых целей или может содержать компьютер общего назначения, активируемый избирательным образом или переконфигурируемый компьютерной программой, которая хранится в самом компьютере. Такая компьютерная программа может храниться на машинно-читаемом носителе информации, например на диске любого типа, включая гибкие диски, оптические диски, компакт-диски (CD-ROM) и магнитно-оптические диски, в постоянных запоминающих устройствах (ПЗУ, ROM), запоминающих устройствах с произвольной выборкой (ЗУПВ, RAM), стираемых программируемых ПЗУ (СППЗУ, EPROM), электронно-перепрограммируемых ПЗУ (ЭППЗУ, EEPROM), на магнитных или оптических картах, или любом типе носителя информации, пригодном для хранения электронных инструкций, каждый из которых присоединен к системной шине компьютера, при этом машинно-читаемый носитель информации не ограничивается вышеперечисленным. Инструкции выполняются с использованием одного или большего количества устройств обработки данных (например, процессоров, центральных процессоров и т.д.). Приведенные здесь алгоритмы и изображения, по существу, не относятся к определенному компьютеру или другому устройству. В соответствии с определенными здесь идеями изобретения программами могут использоваться различные машины общего назначения, или для выполнения необходимых этапов способа может оказаться удобным создание более специализированного устройства. Структура, которая требуется для множества таких машин, будет описана ниже. Кроме того, настоящее изобретение не описано в отношении какого-либо конкретного языка программирования. Будет ясно, что для реализации описанных здесь идей изобретения могут использоваться разнообразные языки программирования.

В последующем подробном описании вариантов осуществления делается ссылка на приложенные чертежи, где в качестве иллюстрации показаны конкретные варианты осуществления, в которых может быть реализовано изобретение. На чертежах идентичные символы на протяжении ряда изображений, в основном, относятся к подобным компонентам. Эти варианты осуществления описаны достаточно подробно, чтобы обеспечить специалистам в данной области техники возможность реализовать изобретение. Можно использовать и другие варианты осуществления, и можно вносить структурные, логические и электротехнические изменения, не выходя за рамки объема настоящего изобретения. Более того, следует понимать, что различные варианты осуществления изобретения, хотя и отличны друг от друга, не обязательно являются взаимоисключающими. Например, конкретное свойство, структура или характеристика, описанные в одном варианте осуществления, могут быть включены в другие варианты осуществления. Следовательно, последующее подробное описание не должно восприниматься в качестве ограничения, и объем настоящего изобретения определен только приложенной формулой изобретения, полностью охватывая эквиваленты, к которым применима формула изобретения.

Способ и устройство настоящего изобретения обеспечивают поддержку процессора для монитора виртуальной машины (МВМ). Фиг.1 изображает один вариант осуществления среды 100 виртуальной машины, в которой может функционировать настоящее изобретение. В этом варианте осуществления «голые» аппаратные средства 116 (без программного обеспечения) содержат вычислительную платформу, которая, например, может обеспечить выполнение стандартной операционной системы (ОС) или монитора виртуальной машины (МВМ), например МВМ 112. Хотя МВМ обычно реализуют в виде программого обеспечения, он может экспортировать для программного обеспечения более высокого уровня «голый» машинный интерфейс, например, посредством эмуляции. Такое программное обеспечение более высокого уровня может содержать стандартную ОС или ОС, работающую в реальном масштабе времени, хотя объем изобретения не ограничен в этом отношении, и в качестве альтернативы МВМ, например, может выполняться внутри или поверх другого МВМ. Мониторы МВМ и их типичные отличительные признаки и функциональные возможности известны специалистам в данной области техники и могут быть реализованы, например, в виде программного обеспечения, программно - аппаратного обеспечения или путем комбинирования различных способов.

Как описано выше, МВМ представляет для другого программного обеспечения (то есть, «гостевого» программного обеспечения) абстракцию одной или более виртуальных машин (ВМ, VM). На фиг.1 изображены две ВМ 102 и 114. Гостевое программное обеспечение для каждой ВМ включает в себя гостевую ОС, например гостевую ОС 104 или 106, и различные гостевые программные приложения 108-110. Предполагается, что каждая из гостевых ОС 104 и 106 осуществляет контроль доступа к физическим ресурсам (например, регистрам процессора, памяти и устройствам ввода/вывода с распределением памяти) в пределах аппаратной платформы, на которой выполняется гостевая ОС 104 или 106, и выполняет другие функции. Однако в среде виртуальной машины МВМ 112 должен быть обеспечен возможностью абсолютного контроля над физическими ресурсами для обеспечения надлежащей работы ВМ 102 и 114 и защиты от ВМ 102 и 114 и между ними. МВМ 112 достигает этого путем перехвата всех попыток доступа гостевых ОС 104 и 106 к физическим ресурсам компьютера. Для обеспечения МВМ 112 возможности перехвата указанных попыток доступа могут использоваться различные способы. Одним из таких способов является способ лишения гостя привилегий, который принудительным образом вызывает выполнение всего гостевого программного обеспечения на уровне привилегии аппаратных средств, не допускающем доступ этого программного обеспечения к некоторым аппаратным ресурсам. В результате, при попытке гостевой ОС 104 или 106 осуществить доступ к любому из этих аппаратных ресурсов, она «перехватывается» МВМ 112, то есть если операция, инициализированная гостевой ОС, включает в себя доступ к таким аппаратным ресурсам, то управление операцией получает МВМ 112. Фиг.2 изображает известный вариант осуществления работы МВМ, поддерживающий лишение гостя привилегий. Как описано выше, лишение гостя привилегий принудительным образом вызывает выполнение гостевой ОС в менее привилегированном режиме выполнения. Для микропроцессоров IA-32 сущность страничной защиты состоит в том, что все гостевое программное обеспечение выполняется на наименее привилегированном уровне (то есть, кольцо 3). То есть гостевая ОС 206 и гостевые приложения 204 выполняются на одном уровне привилегий. В результате гостевая ОС 206 может оказаться неспособной обеспечить себе защиту от гостевых приложений 206, вследствие чего, возможно, целостность гостевой ОС 206 подвергается риску. Эта проблема известна как кольцевое сжатие.

Лишение гостя привилегий может также привести к проблеме сжатия адресного пространства. Как описано выше, некоторые попытки доступа к аппаратным ресурсам, осуществляемые гостевым программным обеспечением, приводят к перехватам, которые осуществляют передачу управления к МВМ 220. Для обеспечения возможности такой передачи управления часть кода МВМ и/или структур данных может постоянно находиться, согласно требованиям архитектуры, в том же виртуально-адресном пространстве, что и гостевая ОС 206. Например, архитектура системы команд (АСК, ISA) IA-32 может требовать, чтобы таблица дескрипторов прерываний (ТДП, IDT) 212, глобальная таблица дескрипторов (ГТД, GDT) 210 и процедуры, обрабатывающие перехваты, постоянно находились в том же виртуальном пространстве, что и гостевая ОС 206. Код МВМ и структуры данных 220, которые постоянно находятся в виртуальном пространстве 202, должны быть защищены от доступа гостевого программного обеспечения (например, путем выполнения в кольце 0). Соответственно, гостевая ОС 206 не управляет всем адресным пространством 202, как полагается гостевой ОС 206. Это приводит к проблеме сжатия адресного пространства.

Другое ограничение мониторов МВМ, использующих лишение гостя привилегий, относится к некоторым случаям, в которых процессорам не удается предотвратить считывание гостевым программным обеспечением привилегированных аппаратных ресурсов. Например, микропроцессоры IA-32 допускают выполнение гостевой ОС 206 инструкций PUSH CS, которые сохраняют в память регистр кодового сегмента. В одном из полей этого регистра хранится информация о текущем уровне привилегий. Соответственно, гостевая ОС 206, считывая из памяти значение текущего уровня привилегии, может получить информацию о том, что ее уровень привилегии равен 3, а не 0, как полагает гостевая ОС 206. В результате гостевая ОС 206 может обнаружить, что она выполняется на виртуальной машине, и целостность гостевой ОС 206 может быть подвержена риску.

Аналогично в некоторых случаях процессоры не перехватывают попытку гостевого программного обеспечения изменить привилегированные программные ресурсы. Например, процессоры IA-32 допускают выдачу гостевой ОС 206 инструкций POPF, которые пытаются загрузить EFLAGS, и вместо генерирования перехвата просто игнорируют все или часть таких попыток гостевой ОС 206, так как гостевая ОС 206 выполняет эти инструкции с недостаточной привилегией. В результате гостевая ОС 206 полагает, что соответствующее поле EFLAGS было изменено, но МВМ 220 не получает информации об этом и не может правильно эмулировать это изменение. Соответственно, гостевая ОС 206 может обнаружить, что она выполняется на виртуальной машине, и целостность гостевой ОС 206 может быть подвержена риску.

Еще одно ограничение мониторов ВМ, которые используют лишение гостя привилегий, обусловлено избыточным перехватом. Так как количество элементов аппаратных ресурсов, которые необходимо защитить от доступа со стороны гостевого программного обеспечения, значительно, и такие попытки доступа могут осуществляться часто, то перехваты могут происходить часто. Например, микропроцессоры IA-32 поддерживают инструкции CLI. Инструкции CLI выдаются для изменения флага прерывания, который является элементом привилегированных аппаратных ресурсов и к которому, следовательно, не может осуществить доступ непривилегированное программное обеспечение. Гостевая ОС 206 обычно выдает такие инструкции во время своей работы, тем самым обуславливая частые перехваты со стороны МВМ 220. Частые перехваты отрицательно влияют на эффективность системы и уменьшают полезность МВМ 220.

Настоящее изобретение решает упомянутые выше проблемы и снимает различные другие ограничения, обеспечивая для МВМ поддержку процессора. Фиг.3 является блок-схемой системы, предназначенной для обеспечения поддержки процессора для монитора виртуальной машины, согласно одному варианту осуществления настоящего изобретения.

Согласно фиг.3, все гостевое программное обеспечение выполняется в режиме процессора, определенном здесь как виртуальный 32-битовый режим (режим V32). Режим V32 допускает выполнение гостевого программного обеспечения на своем намеченном уровне привилегий. Например, для АСК IA-32 гостевая ОС 308 выполняется на наиболее привилегированном уровне (то есть, кольцо 0), а гостевые приложения 306 выполняются на наименее привилегированном уровне (то есть, кольцо 3). Режим V32 ограничивает функционирование гостевого программного обеспечения, предотвращая выполнение гостевым программным обеспечением операций, которые могут привести к его доступу к некоторым привилегированным аппаратным ресурсам. При попытке гостевого программного обеспечения выполнить такую операцию осуществляется выход из режима V32.

МВМ 320 выполняется вне режима V32. Когда происходит переход из режима V32, МВМ 320 получает контроль над операцией, инициализированной гостевой ОС 308 или гостевым приложением 306. Затем МВМ 320 выполняет эту операцию и передает управление обратно гостевому программному обеспечению посредством входа в режим V32, вследствие этого эмулируя функциональные возможности, которые требуются для гостевого программного обеспечения.

В одном варианте осуществления режим V32 реализуется путем сохранения флага в одном из регистров управления процессора (например, CR0) для указания, находится ли процессор в режиме V32. В другом варианте осуществления этот флаг (определенный здесь как EFLAGS.V32) сохраняют в одном из зарезервированных битов в верхней половине EFLAGS. При переходе либо из режима V32, либо в режим V32 флаг EFLAGS.V32 изменяется. В одном варианте осуществления информация о возможности процессора поддерживать режим V32 выдается с использованием одного из зарезервированных дополнительных битов, которые возвращаются в EDX при выполнении инструкции CPUID со значением 1 в EAX. Следует отметить, что можно без потери общности использовать разнообразные механизмы для реализации режима V32 и передачи информации о возможности процессора поддерживать режим V32.

В одном варианте осуществления некоторые исключения и прерывания приводят к переходу из режима V32. В указанные исключения и прерывания входят "виртуальные перехваты". Виртуальный перехват генерируется при попытке гостевого программного обеспечения, выполняемого в режиме V32, выполнить операцию, которая может привести к доступу к некоторым привилегированным аппаратным ресурсам. В одном варианте осуществления при переходе из режима V32 гостевое адресное пространство 304 автоматически заменяется на адресное пространство 302 МВМ. Кроме того, состояние процессора, которое использовалось гостевым программным обеспечением, сохраняют и хранят во временных регистрах, и загружают состояние процессора, требуемое для МВМ 320.

В одном варианте осуществления при переходе в режим V32 состояние процессора, которое было сохранено при переходе из режима V32 (то есть, в МВМ 320), автоматически восстанавливается, адресное пространство 302 МВМ заменяются на гостевое адресное пространство 304, и управление возвращаются гостевой ОС 308.

В одном варианте осуществления при выполнении гостевого программного обеспечения в режиме V32 программные прерывания (например, прерывания, вызванные выполнением инструкций BOUND, INT или INTO) обрабатываются гостевой ОС 308 с использованием гостевой ТДП (то есть, ТДП, постоянно находящейся в гостевом адресном пространстве 304). Все остальные прерывания и исключения, включая виртуальные перехваты, вызывают переход из режима V32, что приводит к замене гостевого адресного пространства 304 на адресное пространство 302 МВМ. Далее ТДП 316 используется для указания на код, который обрабатывает соответствующее исключение или прерывание.

В одном варианте осуществления поддерживается новый флаг прерывания (то есть, флаг прерывания виртуальной машины) для попыток доступа, осуществляемых гостевым программным обеспечением. Всякий раз, когда гостевое программное обеспечение осуществляет попытку доступа к флагу прерывания (ФП, IF), оно вместо этого осуществляет доступ к флагу прерывания виртуальной машины (ФПВМ, VMIF). В одном варианте осуществления попытка гостевого программного обеспечения осуществить доступ к ФПВМ (например, используя инструкцию CLI) не приводит к переходу из режима V32, за исключением случая, когда гостевая ОС 308 только что установила ФПВМ в 1 (например, посредством инструкции STI), и МВМ 320 предпочитает выдать задержанное прерывание гостевой ОС 308. Такие задержанные прерывания, определенные здесь как "виртуальные задержанные прерывания", генерируют виртуальные перехваты, обеспечивающие МВМ 320 возможность выдать задержанное прерывание гостевому программному обеспечению, когда гостевая ОС 308 сигнализирует о готовности обработать такое прерывание. В одном варианте осуществления один из зарезервированных битов в верхней половине регистра EFLAGS используется для сохранения флага, указывающего, имеет ли гостевое программное обеспечение задержанное виртуальное прерывание.

Реализация режима V32 позволяет решить все проблемы, вызванные лишением гостя привилегий, как описано выше. В частности, так как гостевое программное обеспечение выполняется в режиме V32 на своем намеченном уровне привилегий, устраняется проблема кольцевого сжатия. Кроме того, сжатие адресного пространства больше не является проблемой, поскольку виртуальный перехват автоматически приводит к переключению на адресное пространство 302 МВМ, и, следовательно, не требуется размещение таблиц, управляющих такими переходами, и кода, обрабатывающего соответствующий виртуальный перехват, в гостевом адресном пространстве 304.

Помимо этого, поскольку режим V32 обеспечивает возможность выполнения гостевого программного обеспечения на своем намеченном уровне привилегий, аппаратные ресурсы, которые должны быть защищены, больше не содержат те элементы аппаратных ресурсов, которые управляют уровнем привилегий. Например, с помощью описанной выше инструкции PUSH CS гостевая ОС 308 не сможет больше выяснить, что она выполняется на виртуальной машине, так как поле регистра кодового сегмента, хранящее информацию о текущем уровне привилегий, теперь хранит уровень привилегий, назначенный гостевой ОС 308. Аналогично, инструкции POPF, осуществляющие попытку загрузить EFLAGS, более не игнорируются при их выполнении гостевой ОС 308, так как гостевая ОС 206 выполняет эти инструкции с достаточной привилегией.

Соответственно, уменьшается количество элементов аппаратных ресурсов, которые должны быть защищены. Если какие-либо из них позволяют гостевому программному обеспечению осуществлять неперехватываемый доступ для считывания или записи, то они специально разработаны для вызова перехватов при выполнении в режиме V32. Следовательно, устранены проблемы, вызванные неперехватываемым доступом для чтения и записи. Более того, поскольку реализация режима V32 уменьшает количество элементов аппаратных ресурсов, которые должны быть защищены, количество перехватов, происходящих при попытке доступа гостевого программного обеспечения к этим элементам, также уменьшается. Частота перехватов дополнительно уменьшается путем предоставления механизмов для исключения перехватов, вызванных наиболее часто используемыми инструкциями. Например, инструкции STI более не вызывают перехваты, за исключением случаев, когда гостевое программное обеспечение имеет задержанное виртуальное прерывание.

Фиг.4 является блок-схемой алгоритма для способа 400 обеспечения поддержки процессора для монитора виртуальной машины, согласно одному варианту осуществления настоящего изобретения. В блоке 404 обработки гостевое программное обеспечение выполняется в режиме процессора (то есть, режиме V32), который обеспечивает возможность функционирования гостевого программного обеспечения на уровне привилегий, намеченном гостевым программным обеспечением. То есть гостевая ОС может функционировать на уровне привилегий супервизора, а гостевые приложения могут функционировать на уровне привилегий пользователя.

В блоке 406 обработки идентифицируют попытку гостевого программного обеспечения выполнить операцию, ограниченную режимом V32. В ответ на эту попытку осуществляют выход из режима V32 для передачи контроля над операцией, инициированной гостевым программным обеспечением, к МВМ, выполняемому вне режима V32 (блок 408 обработки). В одном варианте осуществления, как будет описано более подробно ниже со ссылкой на фиг.7, МВМ задает конфигурацию, определяющую, какие операции должны приводить к переходу из режима V32. В одном варианте осуществления такие операции генерируют виртуальные перехваты, которые приводят к переходу из режима V32. В качестве альтернативы, для вызова перехода из режима V32 может использоваться любой другой известный механизм. Один вариант осуществления выполнения перехода из режима V32 описан более подробно ниже со ссылками на фиг.5.

Далее, МВМ реагирует на операцию, намеченную гостевым программным обеспечением (блок 410 обработки). После этого осуществляют повторный ввод в режим V32 для передачи контроля над этой операцией обратно гостевому программному обеспечению (блок 412 обработки), и способ 400 возвращается к блоку 404 обработки. В одном варианте осуществления при переходе в режим V32 автоматически восстанавливается состояние процессора, ожидаемое гостевым программным обеспечением, и адресное пространство МВМ заменяется на гостевое адресное пространство.

Фиг.5 является блок-схемой алгоритма для способа 500 выполнения перехода из режима V32, согласно одному варианту осуществления настоящего изобретения. Способ 500 начинается с сохранения состояния процессора, которое используется гостевым программным обеспечением (блок 504 обработки). В одном варианте осуществления сохраненное состояние процессора хранится во временных регистрах процессора. В блоке 506 обработки в регистры процессора загружают состояние процессора, требуемое МВМ. В одном варианте осуществления загрузка состояния процессора приводит к замене гостевого адресного пространства адресным пространством МВМ (например, состояние процессора загружается путем загрузки регистра CR3 управления). В альтернативном варианте осуществления загрузка состояния процессора не приводит к изменению в адресном пространстве. В таком варианте осуществления в блоке 508 обработки выполняют переключение адресного пространства для перехода из гостевого адресного пространства в адресное пространство МВМ. Соответственно, при возникновении прерывания или исключения, приводящего к переходу, автоматически используется ТДП, постоянно находящаяся в адресном пространстве МВМ, для указания на постоянно находящийся в МВМ код, предназначенный для обработки этого прерывания или исключения.

Фиг.6 является блок-схемой алгоритма для способа 600 генерирования виртуальных перехватов, согласно одному варианту осуществления настоящего изобретения. Способ 600 начинается с идентификации попытки гостевого программного обеспечения выполнить операцию, которая может быть ограниченной режимом V32 (блок 604 обработки). В блоке 606 принятия решения определяют, может ли потенциально попытка гостевого программного обеспечения быть успешной. Если результат определения положительный, то генерируют виртуальный перехват (блок обработки 608). В качестве альтернативы, виртуальный перехват не генерируют, и гостевое программное обеспечение возобновляет операцию (блок 610 обработки). Например, согласно АСК IA-32, инструкция RDMSR может быть выполнена только программным обеспечением, выполняющимся с привилегией супервизора. Следовательно, если ОС гостевого программного обеспечения, работающая с привилегией супервизора, выполняет эту инструкцию, то ее попытка может быть успешной. Если гостевое приложение, работающее с привилегией пользователя, выполняет эту инструкцию, то попытка будет неуспешной, и произойдет сбой общей защиты. Соответственно, попытка гостевой ОС выполнить инструкцию RDMSR вызовет виртуальный перехват, а попытка гостевого приложения будет обработана гостевой ОС.

В одном варианте осуществления виртуальные перехваты будут вызываться потенциально успешными попытками доступа гостевой ОС к регистрам управления процессора (например, CR0 - CR4). Например, для процессоров IA-32 виртуальные перехваты будут генерироваться в ответ на попытку гостевого программного обеспечения выполнить инструкции MOV CR (за исключением попыток сохранить CR2, которые не обязательно должны вызывать виртуальные перехваты), CLTS, LMSW или SMSW, или переключить задачи. Виртуальные перехваты могут быть также вызваны потенциально успешной попыткой гостевого программного обеспечения установить флаг ФП прерывания (например, посредством инструкций STI, POPF или IRET), если гостевое программное обеспечение имеет задержанное виртуальное прерывание. Для АСК IA-32 успешные попытки выполнить такие инструкции, как, например, HLT, IN, INS/ INSB/ INSW/ INSD, INVD, OUT, OUTS/ OUTSB/ OUTSW/ OUTSD, RDMSR и WRMSR, вызовут виртуальные перехваты. Эти виртуальные перехваты предотвратят останов процессора и прямой доступ к портам ввода/вывода, кэшу или специфичным для модели регистрам со стороны гостевого программного обеспечения. Кроме того, виртуальные перехваты могут быть вызваны попытками выполнить инструкции CPUID, чтобы обеспечить МВМ возможность представить абстракции отличительных признаков процессора, выбранных МВМ; попытками выполнить инструкции INVLPG, чтобы обеспечить МВМ возможность правильно транслировать виртуальные адреса, и попытками выполнить инструкции IRET (если IRET используется для перехода в режим V32), используемых гостевым программным обеспечением для реализации МВМ, чтобы сделать возможными рекурсивно вложенные МВМ.

Фиг.7 является блок-схемой алгоритма для способа 700 поддержания карты переадресации, согласно одному варианту осуществления настоящего изобретения. Согласно этому варианту осуществления МВМ поддерживает карту переадресации для конфигурирования того, какие прерывания и исключения должны привести к виртуальному прерыванию (блок 704 обработки). В блоке 706 обработки идентифицируют возникновение прерывания или исключения. Затем обращаются к карте переадресации, чтобы найти бит, соответствующий этому прерыванию или исключению в битовой карте переадресации (блок 708 обработки). В блоке 710 принятия решения определяют, допускается ли обработка этого прерывания гостевой ОС. Если результат определения положительный, то прерывание или исключение доставляют в режим V32 и обрабатывают гостевой ОС (блок 714 обработки). В качестве альтернативы, генерируются виртуальный перехват, вызывая переход из режима V32 (блок 712 обработки).

Фиг.8 является блок-схемой алгоритма для способа 800 управления маскированием прерываний, согласно одному варианту осуществления настоящего изобретения. Для управления маскированием прерываний могут использоваться различные варианты осуществления. В одном варианте осуществления все прерывания не маскированы при выполнении гостевого программного обеспечения. В этом варианте осуществления гостевому программному обеспечению разрешается манипулировать флагом прерывания (например, для микропроцессоров IA-32 этот флаг идентифицируют как EFLAGS.IF), но это манипулирование будет игнорироваться в отношении маскирования прерываний. В другом варианте осуществления маскирование прерываний зависит от флага прерывания. В этом варианте осуществления гостевому программному обеспечению не разрешается манипулировать флагом прерывания. В частности, может быть предотвращен доступ гостевого программного обеспечения к флагу прерывания путем предоставления скрытого флага прерывания (например, EFLAGS.VMIF) для изменений, осуществляемых гостевым программным обеспечением, путем генерирования виртуального перехвата в ответ на такую попытку со стороны гостевого программного обеспечения или путем использования любого другого известного способа. Способ 800 начинается с идентификации попытки гостевого программного обеспечения изменить флаг прерывания, посредством чего потенциально можно осуществить управление маскированием прерываний (блок 804 обработки). В блоке 806 принятия решения определяют, управляет ли флаг прерывания маскированием прерываний. Если результат определения отрицательный, то есть все прерывания не маскированы, то гостевому программному обеспечению обеспечивается возможность изменить флаг прерывания (блок 808 обработки). Как описано выше, это изменение не будет воздействовать на маскирование прерываний.

В противном случае, если маскирование прерываний зависит от флага прерывания, то затем определяют, имеется ли скрытый флаг прерывания, то есть воздействует ли на скрытый флаг попытка гостевого программного обеспечения воздействовать на маскирование прерываний (блок 810 принятия решения). Если результат определения отрицательный, то есть гостевое программное обеспечение осуществляет попытку изменить фактический флаг прерывания, то происходит виртуальный перехват (блок 812 обработки), который приводит к переходу из режима V32 (блок 816 обработки). В качестве альтернативы, если фактический флаг прерывания не доступен для гостевого программного обеспечения, то гостевому программному обеспечению предоставляется возможность изменить скрытый флаг прерывания (блок 814 обработки).

Фиг.9 изображает блок-схему одного варианта осуществления системы обработки данных. Система 900 обработки данных включает в себя процессор 920 и память 930. Процессором 920 может быть любой тип процессора, обеспечивающего возможность выполнения программного обеспечения, например микропроцессор, процессор цифровых сигналов, микроконтроллер и т.д. Системой 900 обработки данных может быть персональный компьютер (ПК), универсальная вычислительная машина, портативное устройство, переносной компьютер, компьютерная приставка к телевизору или любая другая система, содержащая программное обеспечение.

Памятью 930 может быть жесткий диск, гибкий диск, запоминающее устройство с произвольной выборкой (ЗУПВ), постоянное запоминающее устройство (ПЗУ), флэш-память или любой другой тип носителя информации вычислительной машины, который может считываться процессором 920. Память 930 может хранить инструкции для выполнения вариантов осуществления различных способов настоящего изобретения, таких как способы 400, 500, 600, 700 и 800 (фиг.4-8).

Ясно, что приведенное выше описание предназначено для пояснения, а не ограничения. При чтении и осмыслении приведенного выше описания для специалистов в данной области техники станут очевидны многие другие варианты осуществления. Следовательно, объем изобретения должен определяться согласно приложенной формуле изобретения, полностью охватывая эквиваленты, к которым применима формула изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ РАЗРЕШЕНИЯ КОНФЛИКТОВ ПО АДРЕСНОМУ ПРОСТРАНСТВУ МЕЖДУ МОНИТОРОМ ВИРТУАЛЬНЫХ МАШИН И ГОСТЕВОЙ ОПЕРАЦИОННОЙ СИСТЕМОЙ | 2001 |

|

RU2259582C2 |

| СИСТЕМЫ И СПОСОБЫ ИСПОЛЬЗОВАНИЯ СИНТЕЗИРОВАННЫХ КОМАНД В ВИРТУАЛЬНОЙ МАШИНЕ | 2004 |

|

RU2374675C2 |

| СИСТЕМА И СПОСОБЫ АУДИТА ВИРТУАЛЬНОЙ МАШИНЫ | 2017 |

|

RU2691187C1 |

| ФИЛЬТРАЦИЯ СОБЫТИЙ ДЛЯ ПРИЛОЖЕНИЙ БЕЗОПАСНОСТИ ВИРТУАЛЬНЫХ МАШИН | 2017 |

|

RU2723668C1 |

| СИСТЕМЫ И СПОСОБЫ МНОГОУРОВНЕВОЙ ОБРАБОТКИ ПЕРЕХВАТОВ В ВИРТУАЛЬНОЙ МАШИННОЙ СРЕДЕ | 2006 |

|

RU2412468C2 |

| МЕХАНИЗМ ДЛЯ УПРАВЛЕНИЯ ВНЕШНИМИ ПРЕРЫВАНИЯМИ В СИСТЕМЕ ВИРТУАЛЬНЫХ МАШИН | 2003 |

|

RU2263343C2 |

| ДВИЖОК ИНТРОСПЕКЦИИ ПАМЯТИ ДЛЯ ЗАЩИТЫ ЦЕЛОСТНОСТИ ВИРТУАЛЬНЫХ МАШИН | 2014 |

|

RU2640300C2 |

| СИСТЕМЫ И СПОСОБЫ ПРЕДОСТАВЛЕНИЯ РЕЗУЛЬТАТА ТЕКУЩЕЙ КОМАНДЫ ПРОЦЕССОРА ПРИ ВЫХОДЕ ИЗ ВИРТУАЛЬНОЙ МАШИНЫ | 2015 |

|

RU2686552C2 |

| ВНЕСЕНИЕ ОШИБКИ СТРАНИЦЫ В ВИРТУАЛЬНЫХ МАШИНАХ | 2014 |

|

RU2659472C2 |

| ЗАЩИТА РЕСУРСОВ ОПЕРАЦИОННОЙ СИСТЕМЫ | 2007 |

|

RU2462747C2 |

Изобретение относится к виртуальным машинам. Техническим результатом является повышение надежности работы за счет предотвращения несанкционированного доступа гостевого программного обеспечения. В способе для гостевого программного обеспечения предоставляют режим процессора. Режим процессора обеспечивает возможность гостевому программному обеспечению работать на уровне привилегий, намеченном гостевым программным обеспечением. При попытке гостевого программного обеспечения выполнить операцию, ограниченную режимом процессора, осуществляется выход из режима процессора для передачи управления операцией монитору виртуальной машины, выполняющемуся вне этого режима процессора. Система реализует заявленный способ. 3 н. и 27 з.п. ф-лы, 9 ил.

загружают состояние процессора, требуемое МВМ.

| СПОСОБ ЗАЩИТЫ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ | 1999 |

|

RU2159953C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ЩИТОВОЙ ДЛЯ ВОДОЕМОВ ЗАТВОР | 1922 |

|

SU2000A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ЩИТОВОЙ ДЛЯ ВОДОЕМОВ ЗАТВОР | 1922 |

|

SU2000A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Топка с качающимися колосниковыми элементами | 1921 |

|

SU1995A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Предохранительное устройство для паровых котлов, работающих на нефти | 1922 |

|

SU1996A1 |

Авторы

Даты

2005-12-10—Публикация

2001-11-27—Подача