Изобретение относится к области радиотехники и может быть использовано в системах связи широкополосного радиодоступа с ППРЧ, функционирующих в условиях неопределенных помех.

Известны радиолинии с псевдослучайной перестройкой рабочей частоты, реализованные, например, в устройстве, описанном в US № 4653068 /10/ «Frequency hopping data communication system», опубликованное 24.03.87, бюл. № 06/662,753.

Изобретение относится к системам радиосвязи, а именно к передаче информации сигналами с ППРЧ, и может найти применение при передаче информации в системах подвижной радиосвязи и в системах тропосферной связи.

В данном устройстве разработана система передачи информации в радиолиниях с ППРЧ, особенностью которой является то, что по каналу обратной связи в двоичном коде передается номер частотной позиции в генератор ППРЧ передатчика, которая определяется по результатам измерения отношения сигнал/шум на входе приемника путем выбора номера частотной позиции на каждый случай одного двоичного условия (состояния): в первом случае исключающую пораженную помехой частотную позицию ППРЧ из перечня всех позиций, во втором - допускающую не пораженную помехой частотную позицию в перечень всех позиций на следующий такт работы радиолинии с ППРЧ.

Однако при быстрых изменениях помеховой обстановки в данном устройстве инерционность предложенного алгоритма с равновероятным выбором частотных позиций фиксированного качества, судя по результатам предшествующих переключению измерений, может привести к существенному ухудшению качества связи.

Известны радиолинии с псевдослучайной перестройкой рабочей частоты, реализованные, например, в устройстве, описанном в патенте РФ № 2273954 С1 «Способ передачи дискретной информации в радиолинии с псевдослучайной перестройкой рабочей частоты», опубликованное 10.04.2006, бюл. № 10.

Изобретение относится к радиосвязи, а именно к передаче дискретной информации сигналами с ППРЧ, и может найти применение при передаче дискретной информации в дуплексных радиолиниях с ППРЧ любой протяженности, функционирующих в общей полосе частот с радиосредствами различной принадлежности и с различными принципами работы в условиях сложной помеховой обстановки.

В данном устройстве разработан способ передачи дискретной информации в радиолинии с ППРЧ, обеспечивающий повышение достоверности принимаемой дискретной информации в дуплексных радиолиниях различной протяженности в условиях сложной помеховой обстановки, когда большое число рабочих частот подвержено воздействию помех, часть из которых имеет относительно не высокий уровень, при котором соотношение сигнал/помеха на этих частотах выше минимально допустимого за счет управления выбором несущих частот передатчика, находящихся на передающем и приемном концах радиолинии по результатам контроля помеховой обстановки соответственно на приемном и передающем концах радиолинии путем измерения и взаимного сравнения уровня помех на контролируемых частотах и выбора из них частот с минимальным уровнем помехи для передатчиков, находящихся соответственно на передающем и приемном концах радиолинии.

Однако при быстрых изменениях помеховой обстановки в данном устройстве инерционность адаптивных алгоритмов с равновероятным выбором частотных позиций допустимого качества, судя по результатам предшествующей переключению проверки, может привести к существенному ухудшению качества связи.

Известные аналоги содержат устройства, обеспечивающие перестройку рабочей частоты за счет алгоритмов равновероятного переключения рабочих частот, что приводит к неэффективному использованию частотных каналов при наличии стационарных помех, нестационарных помех при наличии долговременной неоднородности частотных каналов. Общим недостатком аналогов является то, что реализованные в радиолиниях адаптивные алгоритмы с равновероятным выбором частотных позиций допустимого качества могут привести к существенному ухудшению качества связи при быстром изменении помеховой обстановки.

Наиболее близким аналогом (прототипом) по своей технической сущности к заявленному устройству является «Радиолиния с псевдослучайной перестройкой рабочей частоты» по патенту РФ №2185029 С1, МПК 7 Н04В 15/00, опубликованное 10.07.2002, бюл. № 19.

Устройство-прототип содержит на передающей стороне последовательно соединенные по сигнальным входам/выходам кодер, модулятор, усилитель мощности и передающую антенну, а также блок синхронизации, генератор псевдослучайной последовательности, преобразователь псевдослучайной последовательности, блок управления и синтезатор частот, причем выход блока синхронизации подключен к тактовому входу преобразователя псевдослучайной последовательности и к входу генератора псевдослучайной последовательности, выход которого подключен к управляющему входу преобразователя псевдослучайной последовательности, выход которого подключен к входу блока управления, выход которого подключен к входу синтезатора частот, выход которого подключен к задающему входу модулятора, причем вход кодера является входом радиолинии, а на приемной стороне, содержащей последовательно соединенные по сигнальным входам/выходам приемную антенну, входной усилитель, смеситель-гетеродин, детектор, решающее устройство и декодер, а также блок синхронизации, генератор псевдослучайной последовательности, преобразователь псевдослучайной последовательности, блок управления и блок автоматической регулировки усиления, причем вход блока синхронизации соединен с выходом решающего устройства, а выход подключен к тактовому входу преобразователя псевдослучайной последовательности и к входу генератора псевдослучайной последовательности, выход которого подключен к управляющему входу преобразователя псевдослучайной последовательности, выход которого подключен к управляющему входу блока управления, вход блока автоматической регулировки усиления соединен с дополнительным выходом детектора, а выход подключен к управляющему входу входного усилителя и к подстроечному входу блока управления, управляющий выход которого подключен к управляющему входу смесителя-гетеродина, а тактовый выход подключен к тактовому входу решающего устройства, причем выход декодера является выходом радиолинии.

Используемый в прототипе алгоритм псевдослучайной перестройки (переключения) рабочих частот позволяет повысить помехоустойчивость радиолинии в условиях воздействия нестационарных помех при наличии долговременной неоднородности частотных каналов за счет использования алгоритма неравновероятной перестройки рабочих частот, обеспечивающей выравнивание итоговой достоверности (качества связи) во всех используемых частотных каналах. При этом в соответствии с данным алгоритмом часть заведомо подавленных частотных каналов может вообще исключаться из состава переключаемых частот путем закрепления за ними нулевой вероятности выбора.

Однако устройство-прототип имеет следующий недостаток. В нем не реализована возможность управления выбором частотных позиций, что не позволяет в полной мере обеспечить достоверность передачи информации в сложной помеховой обстановке.

Целью изобретения является разработка радиолинии с ППРЧ, позволяющей повысить помехоустойчивость радиолинии в условиях воздействия стационарных и нестационарных помех при наличии долговременного неоднородного качества отдельных частотных каналов.

Поставленная цель достигается тем, что в известной радиолинии с псевдослучайной перестройкой рабочей частоты, состоящей из приемной и передающей частей, при этом передающая часть включает кодер, блок синхронизации передающей части радиолинии, генератор ПСП передающей части радиолинии, преобразователь ПСП передающей части радиолинии, блок управления, синтезатор частот, модулятор, усилитель мощности, передающую антенну. Причем выход блока синхронизации передающей части радиолинии соединен с входом генератора псевдослучайной последовательности и синхровходом преобразователя псевдослучайной последовательности передающей части радиолинии. Информационный вход преобразователя псевдослучайной последовательности передающей части радиолинии соединен с выходом генератора псевдослучайной последовательности. Вход блока управления соединен с выходом преобразователя псевдослучайной последовательности передающей части радиолинии, а выход - с входом синтезатора частот. Выход синтезатора частот соединен с модулирующим входом модулятора. Информационный вход модулятора соединен с выходом кодера, причем вход кодера является входом радиолинии. Выход модулятора соединен с входом усилителя мощности. Выход усилителя мощности подключен к передающей антенне. Приемная часть содержит приемную антенну, входной усилитель, смеситель-гетеродин, детектор, блок АРУ, решающее устройство, декодер, блок синхронизации приемной части радиолинии, генератор ПСП приемной части радиолинии, преобразователь ПСП приемной части радиолинии, блок управления. Причем выход декодера является выходом радиолинии, а вход подключен к выходу решающего устройства и входу блока синхронизации приемной части радиолинии. Управляющий вход решающего устройства подключен к первому управляющему выходу блока управления, а информационный вход - к первому информационному выходу детектора. Второй информационный выход детектора подключен к входу блока автоматической регулировки усиления. Вход детектора подключен к выходу смесителя-гетеродина. Информационный и управляющий входы смесителя-гетеродина подключены соответственно к выходу входного усилителя и второму управляющему выходу блока управления. Информационный вход блока управления подключен к выходу блока автоматической регулировки усиления и к управляющему входу входного усилителя. Информационный вход входного усилителя подключен к выходу приемной антенны. Управляющий вход блока управления подключен к выходу преобразователя псевдослучайной последовательности приемной части радиолинии. Синхро и информационный входы преобразователя псевдослучайной последовательности приемной части радиолинии подключены соответственно к выходу блока синхронизации приемной части радиолинии и выходу генератора псевдослучайной последовательности. Выход блока синхронизации приемной части радиолинии подключен к входу генератора псевдослучайной последовательности. В передающей части дополнительно введен радиоприемник канала обратной связи, вход которого подключен к приемной антенне, а выход - к управляющему входу преобразователя псевдослучайной последовательности передающей части радиолинии. В приемной части дополнительно введены анализатор помех, делитель, БВМУПиС, вычислитель, передатчик канала обратной связи, выход которого подключен к передающей антенне. Вход делителя подключен к выходу блока синхронизации приемной части радиолинии. Первый и второй синхровыходы делителя подключены соответственно к первым и вторым синхровходам анализатора помех и блока вычисления минимального уровня помехи и сигнала. Второй синхровыход делителя подключен к первому синхровходу вычислителя. Второй синхровход вычислителя подключен к третьему синхровыходу делителя. Управляющий вход анализатора помех подключен к выходу преобразователя псевдослучайной последовательности приемной части радиолинии. Первый и второй информационные входы анализатора помех подключены соответственно к выходу входного усилителя и первому информационному выходу блока вычисления минимального уровня помехи и сигнала. Второй информационный выход блока вычисления минимального уровня помехи и сигнала подключен к первому информационному входу вычислителя. N информационных и N управляющих выходов анализатора помех, где N > 2, подключены соответственно к N информационным и N управляющим входам блока вычисления минимального уровня помехи и сигнала. Первая и вторая группы по N информационным выходам блока вычисления минимального уровня помехи и сигнала подключены соответственно к N информационным входам анализатора помех и N информационным входам вычислителя. Управляющий и второй информационный входы вычислителя подключены соответственно к выходам блока автоматической регулировки усиления и анализатора помех. Информационный и управляющий выходы вычислителя подключены соответственно к входу передатчика канала обратной связи и управляющему входу преобразователя псевдослучайной последовательности приемной части радиолинии.

Анализатор помех состоит из N смеситель-гетеродинов, N детекторов, N измерителей, N интеграторов, первого сумматора, вычитателя, N постоянно запоминающих устройств, N блоков сравнения, N элементов переключения, второго сумматора. Причем информационные входы N смеситель-гетеродинов объединены и являются первым информационным входом анализатора помех. Управляющий вход i-го смеситель-гетеродина соединен с выходом i-го постоянно запоминающего устройства и с входом i-го блока сравнения. Управляющие входы N блоков сравнения объединены и являются управляющим входом анализатора помех. Выход i-го блока сравнения соединен с информационным входом i-го элемента переключения. Синхровходы N элементов переключения, N измерителей и N интеграторов объединены и являются первым синхровходом анализатора помех. Управляющие выходы N элементов переключения и информационные выходы N измерителей являются соответственно N управляющими и N информационными выходами анализатора помех. Информационные входы N интеграторов подключены к информационным выходам соответствующих N измерителей. Выход i-го смеситель-гетеродина соединен с входом i-го детектора. Информационный вход i-го измерителя соединен с выходом i-го детектора. Выходы N интеграторов объединены с входами соответствующих N информационных входов первого сумматора. Синхровход первого сумматора, вычитателя и синхровходы N интеграторов объединены и являются вторым синхровходом анализатора помех. Информационный выход первого сумматора соединен с первым информационным входом вычитателя. Второй информационный вход вычитателя является вторым информационным входом анализатора помех. Третий информационный вход вычитателя подключен к выходу второго сумматора. Выход вычитателя является выходом анализатора помех. N информационных входов второго сумматора являются соответствующими N информационными входами анализатора помех.

Делитель состоит из первого делителя частоты, второго делителя частоты и линии задержки. Причем синхровход первого делителя частоты, второй синхровход второго делителя частоты и второй синхровход линии задержки объединены и являются синхровходом делителя. Первые синхровыходы первого и второго делителей частоты, а так же синхровход линии задержки являются соответственно первым, вторым и третьим синхровходами делителя. Второй синхровыход первого делителя частоты подключен к первому синхровходу второго делителя частоты. Второй синхровыход второго делителя частоты подключен к первому синхровходу линии задержки.

Блок вычисления минимального уровня помехи и сигнала (БВМУПиС) состоит из переключателя входов, N первых компараторов, N первых регистров хранения, N вторых компараторов, N вторых регистров хранения, N счетчиков, N вычитателей и сумматора. Причем N информационных входов переключателя входов является N информационными входами блока вычисления минимального уровня помехи и сигнала. Входы N счетчиков соединены с соответствующими N управляющими входами переключателя входов и являются N управляющими входами блока вычисления минимального уровня помехи и сигнала. Синхро входы N счетчиков, N первых и N вторых регистров хранения объединены и являются вторым синхровходом блока вычисления минимального уровня помехи и сигнала. Синхровходы N первых и N вторых компараторов объединены и являются первым синхровходом блока вычисления минимального уровня помехи и сигнала. Выходы N счетчиков соединены с соответствующими N управляющими входами сумматора. Вторые информационные выходы N первых регистров хранения соединены со вторыми информационными входами соответствующих N вторых регистров хранения, первыми информационными входами N вычитателей и являются соответствующими информационными выходами в первой и второй группах информационных выходов блока вычисления минимального уровня помехи и сигнала. Первые информационные входы N первых компараторов подключены к соответствующим N информационным выходам первой группы N информационных выходов переключателя входов. Первые информационные входы N вторых компараторов подключены к соответствующим информационным выходам второй группы из N информационных выходов переключателя входов. Вторые информационные входы N первых компараторов подключены к соответствующим первым информационным выходам N первых регистров хранения. Вторые информационные входы N вторых компараторов подключены к соответствующим первым информационным выходам N вторых регистров хранения. N информационных выходов первого компаратора подключены к соответствующим N информационным входам N первого регистра хранения. Информационные выходы N вторых компараторов подключены к соответствующим первым информационным входам N вторых регистров хранения. Вторые информационные выходы N вторых регистров хранения подключены к вторым информационным входам соответствующих N вычитателей. Выходы N вычитателей соединены с соответствующими N информационными входами сумматора. Информационный выход сумматора является первым и вторым информационными выходами блока вычисления минимального уровня помехи и сигнала.

Вычислитель состоит из компаратора, первого делителя, первого постоянно запоминающего устройства, N умножителей, второго постоянно запоминающего устройства, второго делителя, дешифратора, первого регистра хранения, второго регистра хранения. Причем управляющий вход компаратора является управляющим входом вычислителя. Выход компаратора подключен к управляющему входу первого делителя. Первый и второй информационные входы первого делителя являются соответственно вторым и первым информационными входами вычислителя. Второй информационный вход первого делителя подключен к информационному входу второго делителя. Выход первого постоянно запоминающего устройства подключен к третьему информационному входу первого делителя. Вторые информационные входы N умножителей являются соответствующими N информационными входами вычислителя. Первые информационные входы N умножителей объединены и подключены к выходу второго постоянно запоминающего устройства. Выходы N умножителей подключены к соответствующим N информационным входам второго делителя. N информационных выходов второго делителя соединены с соответствующими N информационными входами дешифратора. Дополнительный информационный вход дешифратора подключен к выходу первого делителя. N выходов дешифратора подключены к соответствующим N входам первого регистра хранения. Выход первого регистра хранения подключен к информационному входу второго регистра хранения и является информационным выходом вычислителя. Синхровходы первого и второго регистров хранения являются соответственно первым и вторым синхровходами вычислителя. Выход второго регистра хранения является управляющим выходом вычислителя.

Благодаря указанной новой совокупности существенных признаков в заявляемой радиолинии обеспечивается прием и анализ сигнально-помеховой обстановки, выработка управляющих воздействий на формирование рабочих частот, что обеспечивает повышение помехоустойчивости радиолинии.

Заявляемое устройство поясняется чертежами, на которых показаны:

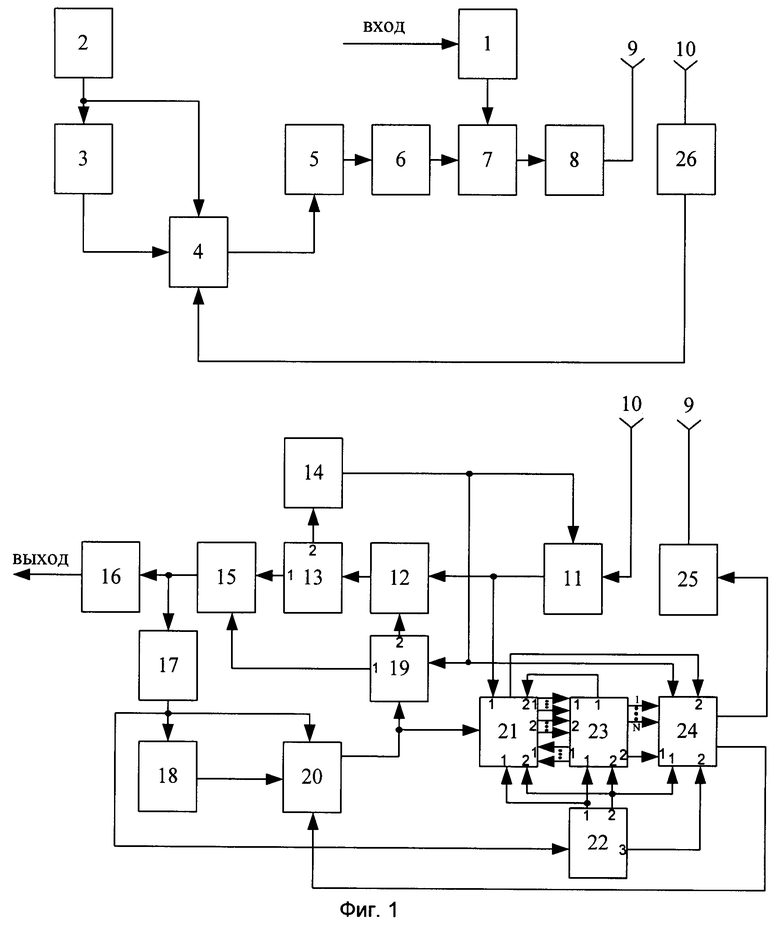

фиг.1 - структурная схема радиолинии с псевдослучайной перестройкой рабочей частоты;

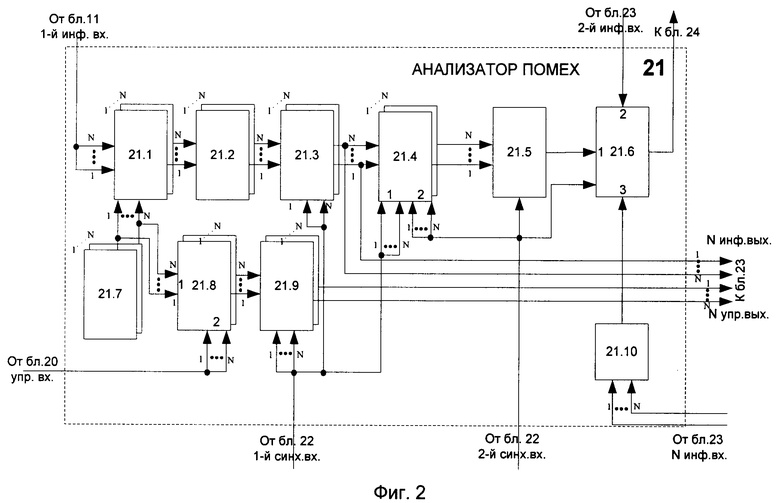

фиг.2 - структурная схема анализатора помех;

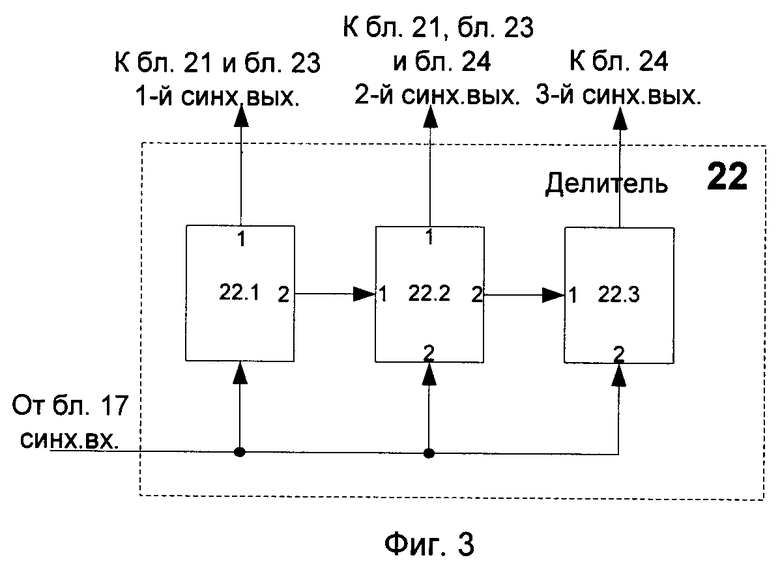

фиг.3 - структурная схема делителя;

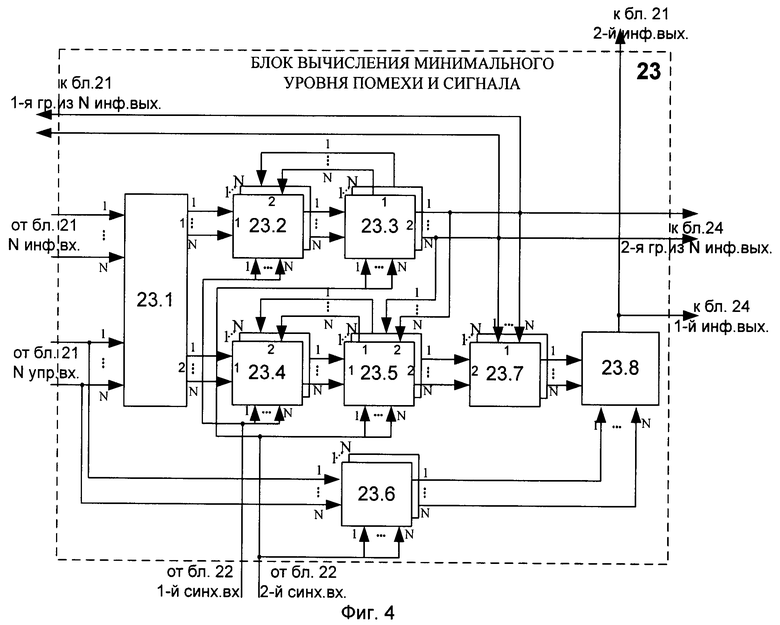

фиг.4 - структурная схема БВМУПиС;

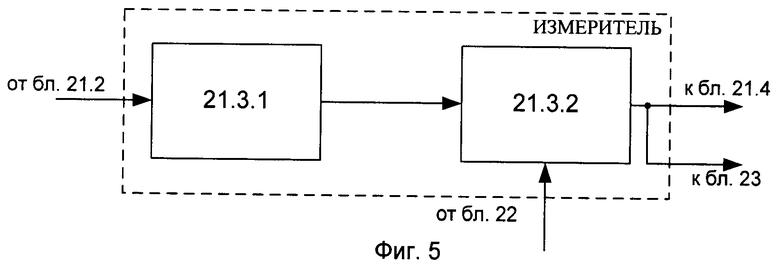

фиг.5 - структурная схема измерителя;

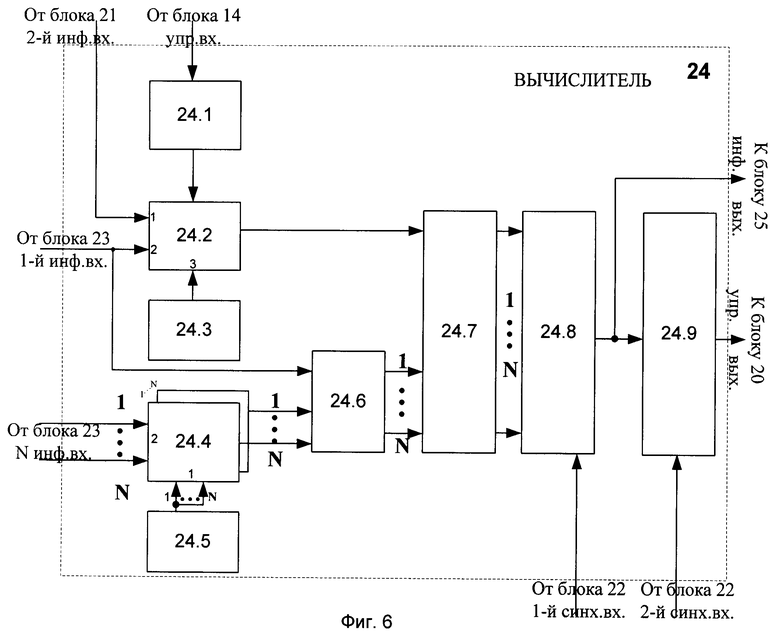

фиг.6 - структурная схема вычислителя;

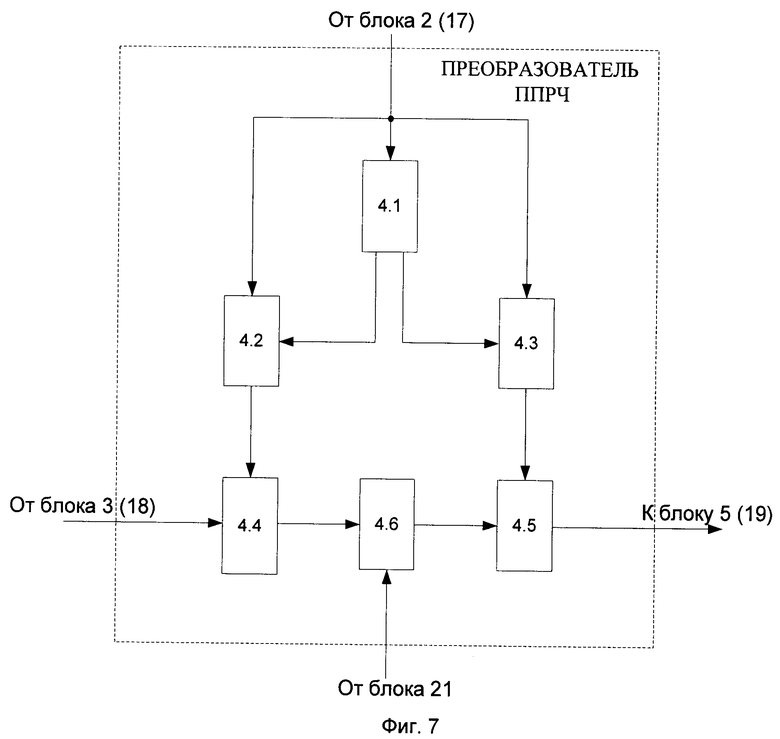

фиг.7 - структурная схема преобразователя ППРЧ.

Заявляемая радиолиния с псевдослучайной перестройкой рабочей частоты, представленная на фиг. 1, состоит из приемной и передающей частей. Передающая часть состоит из кодера 1, блока синхронизации 2, генератора ПСП 3, преобразователя ПСП 4, блока управления 5, синтезатора частот 6, модулятора 7, усилителя мощности 8, передающей антенны 9, приемной антенны 10, радиоприемника канала обратной связи 26. Выход блока синхронизации 2 соединен с входом генератора псевдослучайной последовательности 3 и синхровходом преобразователя псевдослучайной последовательности 4. Информационный вход преобразователя псевдослучайной последовательности 4 соединен с выходом генератора псевдослучайной последовательности 3. Вход блока управления 5 соединен с выходом преобразователя псевдослучайной последовательности 4, а выход - с входом синтезатора частот 6. Выход синтезатора частот 6 соединен с модулирующим входом модулятора 7. Информационный вход модулятора 7 соединен с выходом кодера 1, причем вход кодера 1 является входом радиолинии. Выход модулятора 7 соединен с входом усилителя мощности 8. Выход усилителя мощности 8 подключен к передающей антенне 9. Радиоприемник канала обратной связи 26 подключен к приемной антенне 10, а выход - к управляющему входу преобразователя псевдослучайной последовательности 4. Приемная часть содержит приемную антенну 10, входной усилитель 11, смеситель-гетеродин 12, детектор 13, блок АРУ 14, решающее устройство 15, декодер 16, блок синхронизации 17, генератор ПСП 18, блок управления 19, преобразователь ПСП 20, анализатор помех 21, делитель 22, БВМУПиС 23, вычислитель 24, передатчик канала обратной связи 25, передающую антенну 9. Причем выход декодера 16 является выходом радиолинии, а вход подключен к выходу решающего устройства 15 и входу блока синхронизации приемной части радиолинии 17. Управляющий вход решающего устройства 16 подключен к первому управляющему выходу блока управления 19, а информационный вход - к первому информационному выходу детектора 13. Второй информационный выход детектора 13 подключен к входу блока автоматической регулировки усиления 14. Вход детектора 13 подключен к выходу смеситель-гетеродина 12. Информационный и управляющий входы смеситель-гетеродина 12 подключены соответственно к выходу входного усилителя 11 и второму управляющему выходу блока управления 19. Информационный вход блока управления 19 подключен к выходу блока автоматической регулировки усиления 14 и к управляющему входу входного усилителя 11. Информационный вход входного усилителя 11 подключен к выходу приемной антенны 10. Управляющий вход блока управления 19 подключен к выходу преобразователя псевдослучайной последовательности 20. Синхро и информационный входы преобразователя псевдослучайной последовательности 20 подключены соответственно к выходу блока синхронизации 17 и выходу генератора псевдослучайной последовательности 18. Выход блока синхронизации 17 подключен к входу генератора псевдослучайной последовательности 18. Передатчик канала обратной связи 25 подключен к передающей антенне 9. Вход делителя 22 подключен к выходу блока синхронизации 17. Первый и второй синхровыходы делителя 22 подключены соответственно к первым и вторым синхровходам анализатора помех 21 и блока вычисления минимального уровня помехи и сигнала 23. Второй синхровыход делителя 22 подключен к первому синхровходу вычислителя 24. Второй синхровход вычислителя 24 подключен к третьему синхровыходу делителя 22. Управляющий вход анализатора помех 21 подключен к выходу преобразователя псевдослучайной последовательности 20. Первый и второй информационные входы анализатора помех 21 подключены соответственно к выходу входного усилителя 11 и первому информационному выходу блока вычисления минимального уровня помехи и сигнала 23. Второй информационный выход блока вычисления минимального уровня помехи и сигнала 23 подключен к первому информационному входу вычислителя 24. N информационных и N управляющих выходов анализатора помех 21, где N≥2, подключены соответственно к N информационным и N управляющим входам блока вычисления минимального уровня помехи и сигнала 23. Первая и вторая группы по N информационных выходов блока вычисления минимального уровня помехи и сигнала 23 подключены соответственно к N информационным входам анализатора помех 21 и N информационным входам вычислителя 24. Управляющий и второй информационный входы вычислителя 24 подключены соответственно к выходам блока автоматической регулировки усиления 14 и анализатора помех 21. Информационный и управляющий выходы вычислителя 24 подключены соответственно к входу передатчика канала обратной связи 25 и управляющему входу преобразователя псевдослучайной последовательности 20.

Кодер 1 предназначен для преобразования входной информационной последовательности импульсов в выходную последовательность с дополнительной кодовой избыточностью, позволяющей в декодере 16, служащем для восстановления исходной информационной последовательности, исправлять ошибки, появляющиеся из-за помех в переключаемых частотных каналах. Варианты реализации кодера 1 и декодера 16 известны и приведены, например, в /6, стр. 323-330, рис.8.9, 8.11, 8.16/.

Блок синхронизации 2 предназначен для формирования тактовой последовательности с периодом следования Т/2, где Т - длительность работы радиолинии на одной частоте. В радиолиниях с медленной псевдослучайной перестройкой рабочих частот величина Т должна быть не меньше, чем период τ=1/V следования импульсов на входе модулятора 7, где V - скорость манипуляции информационной составляющей сигнала, т.е. Т>τ. Вариант реализации блока синхронизации 2 известен и описан, например, в /18, стр.193, рис.5-19/.

Генераторы псевдослучайной последовательности 3 и 18 предназначены для формирования одинаковых на передающей и приемной сторонах радиолинии последовательностей равновероятных номеров частот в диапазоне i=1, …, N, поступающих на выход в параллельном двоичном коде разрядностью n=[log2N]. Пример реализации генератора ПСП 3(18) при N=2n на базе генератора двоичной ПСП и других типовых логических элементов известен и описан в патенте РФ №2185029 С1 (фиг.6).

Преобразователи ПСП 4 и 20 предназначены для формирования неравновероятной последовательности номеров перестраиваемых частот из равновероятной последовательности, формируемой генераторами ПСП 3 и 18. Вариант реализации преобразователя для формирования заданных вероятностных распределений дискретизируемых аналоговых уровней сигнала представлен на фиг.7.

Преобразователь псевдослучайной последовательности 4(20) состоит из триггера 4.1, первого 4.2 и второго 4.3 ключей, первого 4.4 и второго 4.5 регистров хранения, а также дешифратора 4.6. При этом управляющий вход первого регистра хранения 4.4 и первый вход дешифратора 4.6 являются управляющими входами преобразователя псевдослучайной последовательности 4(20). Выход первого регистра хранения 4.4 подключен к второму входу дешифратора 4.6, выход которого подключен к управляющему входу второго регистра хранения 4.5, выход которого является выходом преобразователя псевдослучайной последовательности 4(20), тактовые входы первого 4.2 и второго 4.3 ключей объединены с входом триггера 4.1 и являются тактовым входом преобразователя псевдослучайной последовательности 4(20), управляющие входы первого 4.2 и второго 4.3 ключей подключены, соответственно, к первому и второму выходу триггера 4.1, а выходы первого 4.2 и второго 4.3 ключей подключены, соответственно, к тактовым входам первого 4.4 и второго 4.5 регистров хранения.

Триггер 4.1 предназначен для поочередного противофазного открытия и закрытия первого и второго ключей 4.2 и 4.3 с периодом Т/2. Вариант реализации триггера 4.1 известен и описан, например, в /18, стр.165, рис.4-29/.

Первый ключ 4.2 предназначен для пропускания нечетных тактирующих импульсов, обеспечивающих считывание очередного входного n-разрядного двоичного равновероятного псевдослучайного числа в первый регистр хранения 4.4.

Второй ключ 4.3 предназначен для пропускания четных тактирующих импульсов, обеспечивающих считывание с выхода дешифратора 4.6 очередного выходного n-разрядного двоичного неравновероятного псевдослучайного числа во второй регистр хранения 4.5.

Варианты реализации первого ключа 4.2 и второго ключа 4.3 известны и описаны, например, в /18, стр.176 рис.5.2/.

Первый регистр хранения 4.4 предназначен для удержания параллельного n-разрядного двоичного кода очередного равновероятного псевдослучайного числа в течение длительности Т между нечетными тактовыми импульсами с периодом Т/2, поступающими на тактовый вход преобразователя ПСП.

Второй регистр хранения 4.5 предназначен для удержания параллельного n-разрядного двоичного кода очередного неравновероятного псевдослучайного числа в течение длительности Т между четными тактовыми импульсами с периодом Т/2, поступающими на тактовый вход преобразователя ПСП.

Варианты реализации первого регистра хранения 4.4 и второго регистра хранения 4.5 известны и представлены, например, в /16, стр.208-210, рис.5.4/.

Дешифратор 4.6 предназначен для преобразования 2n-разрядных двоичных псевдослучайных чисел с равномерным распределением в n-разрядные двоичные псевдослучайные числа с заданным распределением x*={xi}N в соответствии с используемым в прототипе алгоритмом неравновероятного ППРЧ и управляющим воздействием, поступающим от анализатора помех 21. Вариант реализации дешифратора 4.6 на базе арифметического логического устройства (АЛУ) известен и описан, например, в /10, стр.178, рис.1.130/.

Блок управления 5 предназначен для преобразования двоичных номеров частот в соответствующие управляющие сигналы, обеспечивающие перестройку синтезатора частот 6 на соответствующие частоты. Реализация данного блока зависит от способа управления частотами в синтезаторе 6. Если синтезатор 6 выполнен на базе опорного генератора и делителей с переменным коэффициентом деления, то блок управления 5 может представлять собой дешифратор, преобразующий двоичный номер очередной частоты в соответствующий двоичный код коэффициента деления. Вариант реализации блока управления 5 в виде дешифратора известен и описан, например, в /10, стр.178, рис.1.130/.

Если синтезатор 6 представляет собой генератор, управляемый напряжением, то в роли блока управления 5 может выступать цифроаналоговый преобразователь (ЦАП). Вариант реализации ЦАП известен и описан в /18, стр.185-193/.

Синтезатор частот 6 предназначен для формирования несущего колебания на каждой очередной псевдослучайно перестраиваемой частоте. Вариант реализации синтезатора частот 6 известен и представлен, например, в /8, стр.214, рис.7.7(а)/.

Модулятор 7 предназначен для преобразования последовательности импульсов, поступающих на сигнальный вход модулятора с выхода кодера 1, в модулированный высокочастотный сигнал на частоте несущей, поступающей на задающий вход модулятора с выхода синтезатора частот 6. При этом могут использоваться различные способы модуляции, что для заявляемого устройства не является принципиальным. Пример реализации модулятора 7 известен и описан, например, в /7, стр.273-274, рис.11.3 и рис.11.4/.

Усилитель мощности 8 предназначен для усиления высокочастотного сигнала до величины, необходимой для компенсации потерь в среде распространения радиоволн. Вариант реализации усилителя мощности 8 известен и описан, например, в /17, стр.374, рис.11.24/.

Антенные устройства 9, 10 предназначены для преобразования высокочастотного радиосигнала в радиоволны при передаче (9) и обратно при приеме (10). Варианты реализации антенных устройств 9, 10 известны и описаны, например, в /7, стр.169-172, рис.7.2 и рис.7.4/.

Входной усилитель 11 предназначен для предварительного усиления принимаемых высокочастотных сигналов во всем частотном диапазоне до уровня, необходимого для нормальной работы следующих блоков приемного тракта. При этом для регулирования усиления используется управляющий сигнал, поступающий с выхода блока АРУ 14 на управляющий вход входного усилителя 11. Вариант реализации входного усилителя 11 известен и описан, например, в /18, стр.30, рис.2.2(а)/.

Смеситель-гетеродин 12 предназначен для перенесения радиосигналов, принимаемых на различных псевдослучайно перестраиваемых частотах, на общую промежуточную частоту. Вариант реализации смесителя-гетеродина 12 приведен в патенте РФ №2185029 С1 (фиг.5).

Восстановление исходной последовательности импульсов из модулированного высокочастотного сигнала осуществляется в приемной части радиолинии путем снятия высокочастотного заполнения в детекторе 13 и потактового стробирования полученного сигнала в решающем устройстве 15. Сигнал на дополнительном выходе детектора 13 используется для оценки среднего уровня сигнала (огибающей) в блоке АРУ 14. При этом для усреднения уровня принимаемого сигнала может использоваться фильтр нижних частот (ФНЧ) с частотой среза F0<<V, где V - скорость манипуляции несущей информационной последовательностью импульсов. В состав детектора 13 могут входить два блока детектирования - детектор сигнала (амплитудный, частотный или фазовый) и детектор огибающей (амплитудный детектор) с разными ФНЧ (перед сигнальным и дополнительным выходами), отличающимися частотами среза Fc≈V и F0<<V, соответственно, где V - скорость манипуляции информационной составляющей сигнала.

Детектор 13 предназначен для выделения сообщения из принятого колебания. Вариант реализации детектора 13 известен и приведен в патенте РФ №2185029 С1 (фиг.4).

Блок АРУ 14 предназначен для автоматической регулировки усиления принимаемого сигнала. Пример реализации блока АРУ 14 известен и описан, например, в /8, стр.31, рис.2.2(a)/.

Решающее устройство 15 предназначено для регистрации очередного принятого двоичного информационного разряда. Вариант реализации решающего устройства 15 известен и показан, например, в /16, стр.363-371/.

Блок синхронизации 17, как и блок синхронизации 2, служит для формирования тактовой последовательности импульсов с периодом следования Т/2. Отличие заключается в том, что в блоке синхронизации 17 указанный период следования может корректироваться по сигналам управления, выделяемым из принимаемой последовательности импульсов, поступающих с выхода решающего устройства 15 на вход блока синхронизации приемной части радиолинии 17. При этом реализуется процедура согласования по задержке псевдослучайной последовательности, формируемой генератором ПСП 18 относительно ПСП, формируемой генератором ПСП 3. Вариант реализации блока синхронизации 17, обеспечивающего синхронизацию по задержке ПСП, известен и описан, например, в /19, стр.266-328/.

Блок управления 19, как и блок управления 5, предназначен в основном для преобразования двоичных номеров частот в соответствующие управляющие сигналы, обеспечивающие перестройку смесителя-гетеродина 12 на соответствующие частоты. Дополнительными функциями блока управления 19 в приемной части радиолинии с ППРЧ является коррекция управляющих сигналов, перестраивающих частоты в смесителе-гетеродине 12, и тактовых импульсов, стробирующих принимаемый сигнал с периодом τ=1/ν в решающем устройстве 15, по управляющим сигналам, поступающим на подстроечный вход блока управлений 19 с выхода блока АРУ 14. Подстройка может выполняться по разным алгоритмам, отличающимся скоростью, точностью, а также устойчивостью работы в различных условиях, вариант реализации блока управления 19 известен и приведен в патенте РФ №2185029 С1 (фиг.7).

Предлагаемый вариант реализации анализатора помех 21, составляющий часть формулы изобретения, показан на фиг.2.

Анализатор помех 21 предназначен для определения уровня суммарной нестационарной составляющей помех на всех частотных позициях, уровня смеси сигнала и помехи на каждой частотной позиции, а так же выработке управляющих воздействий для обеспечения работы БВМУПиС 23.

Анализатор помех 21 состоит из N смеситель-гетеродинов 21.1, N детекторов 21.2, N измерителей 21.3, N интеграторов 21.4, первого сумматора 21.5, вычитателя 21.6, N постоянно запоминающих устройств 21.7, N блоков сравнения 21.8, N элементов переключения 21.9, второго сумматора 21.10. Причем информационные входы N смеситель-гетеродинов 21.1 объединены и являются первым информационным входом анализатора помех 21. Управляющий вход i-го смеситель-гетеродина 21.1 соединен с выходом i-го постоянно запоминающего устройства 21.7 и с входом i-го блока сравнения 21.8. Управляющие входы N блоков сравнения 21.8 объединены и являются управляющим входом анализатора помех 21. Выход i-го блока сравнения 21.8 соединен с информационным входом i-го элемента переключения 21.9. Синхровходы N элементов переключения 21.9, N измерителей 21.3 и N интеграторов 21.4 объединены и являются первым синхровходом анализатора помех 21. Управляющие выходы N элементов переключения 21.9 и информационные выходы N измерителей 21.3 являются соответственно N управляющими и N информационными выходами анализатора помех 21. Информационные входы N интеграторов 21.4 подключены к информационным выходам соответствующих N измерителей 21.3. Выход i-го смеситель-гетеродина 21.1 соединен с входом i-го детектора 21.2. Информационный вход i-го измерителя 21.3 соединен с выходом i-го детектора 21.2. Выходы N интеграторов 21.4 объединены с входами соответствующих N информационных входов первого сумматора 21.5. Синхровход первого сумматора 21.5, вычитателя 21.6 и синхровходы N интеграторов 21.4 объединены и являются вторым синхровходом анализатора помех 21. Информационный выход первого сумматора 21.5 соединен с первым информационным входом вычитателя 21.6. Второй информационный вход вычитателя 21.6 является вторым информационным входом анализатора помех 21. Третий информационный вход вычитателя 21.6 подключен к выходу второго сумматора 21.10. Выход вычитателя 21.6 является выходом анализатора помех 21. N информационных входов второго сумматора 21.10 являются соответствующими N информационными входами анализатора помех 21.

Смеситель-гетеродин 21.1 предназначен для переноса входного сигнала в низкочастотную область для его последующей обработки. Вариант реализации смесителя известен и приведен, например, в /8, стр.153, рис.5.12/.

Детектор 21.2 предназначен для выделения уровня принимаемого сигнала (колебания) на всех частотных позициях ППРЧ. Вариант реализации детектора известен и приведен, например, в /патенте РФ №2185029 С1, фиг.4/.

Измеритель 21.3 предназначен для определения среднего уровня колебания на всех частотных позициях ППРЧ за интервал времени τ=n/fT, где n - целое положительное число. Вариант реализации измерителя приведен на фиг. 5.

Интегратор 21.4 предназначен для определения среднего уровня колебания на всех частотных позициях ППРЧ за интервал времени Т=к·τ, где к - целое положительное число. Вариант реализации интегратора аналогичен реализации измерителя, приведенной на фиг. 5.

Первый сумматор 21.5 предназначен для определения суммарного уровня смеси сигнала, стационарных и нестационарных помех во всем диапазоне используемых частот за время Т=к·τ, где к - целое положительное число. Вариант реализации первого сумматора известен и приведен, например, в /12, стр.115, рис.8.23, 8.38/.

Вычитатель 21.6 предназначен для выделения уровня нестационарных помех из смеси сигнала, стационарных и нестационарных помех. Вариант реализации блока вычитания известен и приведен, например, в /10, стр.156, рис.119(a)/.

Постоянный запоминающий элемент 21.7 хранит n-разрядный двоичный код частоты каждой частотной позиции ППРЧ. Вариант реализации детектора известен и приведен, например, в /13, стр.83, ПЗУ Cypress/

Блок сравнения 21.8 сравнивает n-разрядное двоичное псевдослучайное число, вырабатываемое преобразователем ППРЧ, с хранящимся в постоянном запоминающем элементе. При совпадении этих чисел блок сравнения вырабатывает управляющее воздействие, которое открывает соответствующий элемент переключения 21.9. Вариант реализации блока сравнения известен и приведен, например, в /12, стр.116, рис.8.39/.

Элемент переключения 21.9 предназначен для обеспечения работы блока вычисления минимального уровня помехи и сигнала 23 в соответствующих частотных позициях ППРЧ. Вариант реализации элемента переключения известен и приведен, например, в /11, стр.161, рис.3.56, 3.57/.

Второй сумматор 21.10 предназначен для определения среднего уровня нестационарных помех во всем диапазоне используемых частот за время Т=к·т, где к - целое положительное число. Вариант реализации второго сумматора известен и приведен, например, в /12, стр.115, рис.8.23, 8.38/.

Предлагаемый вариант реализации делителя 22, составляющий часть формулы изобретения, показан на фиг.3.

Делитель 22 предназначен для выработки тактовых последовательностей с частотами следования  ;

;  .

.

Делитель 22 состоит из первого делителя частоты 22.1, второго делителя частоты 22.2 и линии задержки 22.3. Причем синхровход первого делителя частоты 22.1, второй синхровход второго делителя частоты 22.2 и второй синхровход линии задержки 22.3 объединены и являются синхровходом делителя 22. Первые синхровыходы первого 22.1 и второго 22.2 делителей частоты, а так же синхровход линии задержки 22.3 являются соответственно первым, вторым и третьим синхровходами делителя 22. Второй синхровыход первого делителя частоты 22.1 подключен к первому синхровходу второго делителя частоты 22.2. Второй синхровыход второго делителя частоты 22.2 подключен к первому синхровходу линии задержки 22.3.

Делители частоты 22.1 и 22.2 предназначены для формирования тактовых последовательностей с частотами f=1/τ и F=1/T соответственно, необходимых для работы анализатора помех. Вариант реализации делителя частоты известен и приведен, например, в /14, стр.190, рис.8.3/.

Линия задержки 22.3 предназначена для задержки n-разрядного двоичного кода на время nτ, необходимое для передачи воздействия от приемника к передатчику по каналу обратной связи. Вариант реализации линии задержки известен и приведен, например, в /16, стр.208-210, рис.5.4(а)/.

Предлагаемый вариант реализации блока вычисления минимального уровня помехи и сигнала 23, составляющий часть формулы изобретения, показан на фиг.4.

БВМУПиС 23 предназначен для определения суммарного минимального уровня помех на всех частотных позициях, а так же минимального уровня сигнала на каждой частотной позиции.

БВМУПиС 23 состоит из переключателя входов 23.1, N первых компараторов 23.2, N первых регистров хранения 23.3, N вторых компараторов 23.4, N вторых регистров хранения 23.5, N счетчиков 23.6, N вычитателей 23.7 и сумматора 23.8. Причем N информационных входов переключателя входов 23.1 являются N информационными входами блока вычисления минимального уровня помехи и сигнала 23. Входы N счетчиков 23.6 соединены с соответствующими N управляющими входами переключателя входов 23.1 и являются N управляющими входами блока вычисления минимального уровня помехи и сигнала 23. Синхровходы N счетчиков 23.6, N первых 23.3 и N вторых 23.5 регистров хранения объединены и являются вторым синхровходом блока вычисления минимального уровня помехи и сигнала 23. Синхровходы N первых 23.2 и N вторых 23.4 компараторов объединены и являются первым синхровходом блока вычисления минимального уровня помехи и сигнала 23. Выходы N счетчиков 23.6 соединены с соответствующими N управляющими входами сумматора 23.8. Вторые информационные выходы N первых регистров хранения 23.3 соединены со вторыми информационными входами соответствующих N вторых регистров хранения 23.5, первыми информационными входами N вычитателей 23.7 и являются соответствующими информационными выходами в первой и второй группах информационных выходов блока вычисления минимального уровня помехи и сигнала 23. Первые информационные входы N первых компараторов 23.2 подключены к соответствующим N информационным выходам первой группы N информационных выходов переключателя входов 23.1. Первые информационные входы N вторых компараторов 23.4 подключены к соответствующим информационным выходам второй группы из N информационных выходов переключателя входов 23.1. Вторые информационные входы N первых компараторов 23.2 подключены к соответствующим первым информационным выходам N первых регистров хранения 23.3. Вторые информационные входы N вторых компараторов 23.4 подключены к соответствующим первым информационным выходам N вторых регистров хранения 23.5. N информационных выходов первого компаратора 23.2 подключены к соответствующим N информационным входам N первого регистра хранения 23.3. Информационные выходы N вторых компараторов 23.4 подключены к соответствующим первым информационным входам N вторых регистров хранения 23.5. Вторые информационные выходы N вторых регистров хранения 23.5 подключены к вторым информационным входам соответствующих N вычитателей 23.7. Выходы N вычитателей 23.7 соединены с соответствующими N информационными входами сумматора 23.8. Информационный выход сумматора 23.8 является первым и вторым информационными выходами блока вычисления минимального уровня помехи и сигнала 23.

Переключатель входов 23.1 предназначен для определения частотной позиции сигнала из всех частотных позиций и переключения соответствующих линия для дальнейшего определения уровня сигнала и уровня помех на соответствующих частотных позициях. Вариант реализации переключателя входов известен и приведен, например, в /10, стр.305, рис.3.21/

Первый компаратор 23.2 предназначен для определения минимального уровня сигнала на каждой из частотных позиций за время τ. Вариант реализации первого компаратора 23.2 известен и приведен, например в /12, стр.198, табл.9.3/.

Первый регистр хранения 23.3 предназначен для хранения значений минимального уровня сигнала за время Т. Вариант реализации первого регистра хранения 23.3 известен и приведен, например, в /16, стр.208-210, рис.5.4(а)/.

Второй компаратор 23.4 предназначен для определения минимального уровня помех на каждой из частотных позиций за время τ. Вариант реализации второго компаратора 23.4 известен и приведен, например, в /12, стр.198, табл.9.3/.

Второй регистр хранения 23.5 предназначен для хранения значений минимального уровня помех за время Т. Вариант реализации второго регистра хранения 23.5 известен и приведен, например, в /16, стр.208-210, рис.5.4(а)/.

Счетчик 23.6 предназначен для определения количества раз нахождения сигнала соответствующих частотных позиций за время Т. Вариант реализации счетчика 23.6 известен и приведен, например, в /12 стр.141/.

Вычитатель 23.7 предназначен для определения минимального уровня помех на каждой частотной позиции. Вариант реализации вычитателя 23.7 известен и приведен, например, в /10, стр.156, рис.119(а)/.

Сумматор 23.8 предназначен для определения суммарного минимального уровня помех на всех частотных позициях. Вариант реализации сумматора 23.8 известен и приведен, например, в /12, стр.115, рис.8.23, 8.38/.

Предлагаемый вариант реализации вычислителя 24, составляющий часть формулы изобретения, показан на фиг.6.

Вычислитель 24 состоит из компаратора 24.1, первого делителя 24.2, первого постоянно запоминающего устройства 24.3, N умножителей 24.4, второго постоянно запоминающего устройства 24.5, второго делителя 24.6, дешифратора 24.7, первого регистра хранения 24.8, второго регистра хранения 24.9. Причем управляющий вход компаратора 24.1 является управляющим входом вычислителя 24. Выход компаратора 24.1 подключен к управляющему входу первого делителя 24.2. Первый и второй информационные входы первого делителя 24.2 являются соответственно вторым и первым информационным входами вычислителя 24. Второй информационный вход первого делителя 24.2 подключен к информационному входу второго делителя 24.6. Выход первого постоянно запоминающего устройства 24.3 подключен к третьему информационному входу первого делителя 24.2. Вторые информационные входы N умножителей 24.4 являются соответствующими N информационными входами вычислителя 24. Первые информационные входы N умножителей 24.4 объединены и подключены к выходу второго постоянно запоминающего устройства 24.5. Выходы N умножителей 24.4 подключены к соответствующим N информационным входам второго делителя 24.6. N информационных выходов второго делителя 24.6 соединены с соответствующими N информационными входами дешифратора 24.7. Дополнительный информационный вход дешифратора 24.7 подключен к выходу первого делителя 24.2. N выходов дешифратора 24.7 подключены к соответствующим N входам первого регистра хранения 24.8. Выход первого регистра хранения 24.8 подключен к информационному входу второго регистра хранения 24.9 и является информационным выходом вычислителя 24. Синхровходы первого 24.8 и второго 24.9 регистров хранения являются соответственно первым и вторым синхровходами вычислителя 24. Выход второго регистра хранения 24.9 является управляющим выходом вычислителя 24.

Вычислитель 24 предназначен для формирования второго n-разрядного двоичного числа с учетом оцененной сигнально-помеховой обстановки, которое используется при формировании 2n-разрядного двоичного псевдослучайного числа преобразователем ППРЧ 4 (20). Вычислитель может быть реализован на базе программируемой логической микросхемы ЕП1С4 семейства CYCLONE FPGA компании Altera.

Радиолиния канала обратной связи служит для передачи управляющего воздействия от вычислителя 24 к преобразователю ПСП передающей части 4. В качестве канала обратной связи может применяться радиолиния, построенная с использованием передатчика 25 и радиоприемника 26 канала обратной связи. Вариант реализации радиолинии канала обратной связи с использованием передатчика канала обратной связи 25 и радиоприемника канала обратной связи 26 известен и приведен, например, в /патенте RU 2185029 С1, (фиг.1).

Заявляемое устройство работает следующим образом.

Входная информационная последовательность импульсов с входа радиолинии поступает на вход кодера 1, который преобразует ее в выходную последовательность импульсов с дополнительной кодовой избыточностью, следующих с тактовой скоростью V=1/τ. Данная последовательность закодированных информационных импульсов поступает на сигнальный вход модулятора 7, который преобразует их в модулированный высокочастотный сигнал на текущей псевдослучайной частоте несущей, поступающей на задающий вход модулятора с выхода синтезатора частот 6. Далее высокочастотный сигнал усиливается в усилителе мощности 8 и излучается антенной 9 в сторону приемной части радиолинии. Текущая несущая частота формируется в синтезаторе частот 6 в соответствии с управляющими сигналами, поступающими на вход синтезатора 6 с выхода блока управления 5, на вход которого с выхода преобразователя ПСП 4 поступают n-разрядные двоичные номера частот, где n=[log2N], N - количество частотных позиций. Преобразователь ПСП 4 преобразует последовательность 2n-разрядных двоичных чисел с выхода n-разрядного генератора ПСП 3, в последовательность n-разрядных двоичных номеров частот. Тактирование генератора ПСП 3 и преобразователя ПСП 4 осуществляется блоком синхронизации 2.

Используемый алгоритм преобразования ПСП в целом опирается на известный метод геометрической интерпретации вероятностей n событий {xi}n, как n участков соответствующей длины, укладывающихся на отрезке единичной длины. Особенностью предлагаемого преобразователя ПСП 4 является учет предопределенной дискретности множества n случайных чисел и сохранение в качестве источника входных равновероятных чисел типового n-разрядного двоичного генератора ПСП, где n=[log2N] (как в прототипе). При этом проблемой реализации неравновероятной ПСП (на базе указанного выше принципа геометрической интерпретации вероятностей) является невозможность получения ненулевых вероятностей отдельных частотных позиций меньших чем 1/n, т.е. меньших, чем в случае равновероятного выбора отдельных частотных позиций. Одним из способов решения указанной проблемы является увеличение разрядности входных двоичных псевдослучайных чисел. Однако в заявляемом изобретении с целью повышения эффективности формирования ПСП на базе типового n-разрядного двоичного генератора равновероятной ПСП для увеличения разрядности исходных равновероятных псевдослучайных чисел используются два последовательно генерируемых n-разрядных двоичных псевдослучайных числа, причем второе n-разрядное двоичное число формируется с учетом результатов определения помеховой обстановки, образующих в совокупности одно 2n-разрядного двоичное псевдослучайное число, что обеспечивает возможность задания ненулевых вероятностей выбора отдельных частот с минимальным значением 1/(n2).

Радиосигнал, принятый антенной 10, после усиления во входном усилителе 11 поступает на сигнальный вход смесителя-гетеродина 12, который переносит данный радиосигнал, принимаемый на различных псевдослучайно перестраиваемых частотах, на общую промежуточную частоту. С выхода смесителя-гетеродина 12 высокочастотный сигнал поступает на вход детектора 13, который выделяет низкочастотную огибающую информационного сигнала и подает ее на вход решающего устройства, который после стробирования импульсами с тактовой скоростью V=1/τ, поступающими с выхода блока управления 19, восстанавливает исходную закодированную последовательность импульсов и подает ее на вход декодера 16, в котором исправляются ошибки и восстанавливается исходная информационная последовательность, поступающая затем на выход радиолинии.

Для регулирования усиления входного усилителя 11 на его управляющий вход с выхода блока АРУ 14 поступает управляющий сигнал, формируемый на основании оценки среднего уровня (огибающей) сигнала, поступающей на вход блока АРУ 14 с дополнительного выхода детектора 13.

Перестройка смесителя-гетеродина 12 на очередные псевдослучайные частоты осуществляется с помощью управляющих сигналов, поступающих на управляющий вход смесителя-гетеродина 12 с управляющего выхода блока управления 19, который формирует данные сигналы в соответствии с номерами частотных позиций, поступающими на управляющий вход блока управления 19 с выхода преобразователя ПСП 20. Кроме того, блок управления 19 корректирует управляющие сигналы, перестраивающие частоты в смесителе-гетеродине 12, и тактовые импульсы, стробирующие принимаемый сигнал в решающем устройстве 15, по управляющим сигналам, поступающим на подстроечный вход блока управления 19 с выхода блока АРУ 14.

Формирование номера текущей частоты в приемной части радиолинии осуществляется с помощью блока синхронизации 17, генератора ПСП 18 и преобразователя ПСП 20, выполняющих функции, аналогичные описанным выше функциям блока синхронизации 2, генератора ПСП 3 и преобразователя ПСП 4 в передающей части радиолинии. Дополнительной функцией блока синхронизации 17 является подстройка последовательности тактовых импульсов для синхронизации по задержке формируемой псевдослучайной последовательности номеров частот и моментов их смены. Причем формирование второго n-разрядного двоичного числа, которое используется при формировании 2n-разрядного двоичного псевдослучайного числа преобразователем ППРЧ 4 (20), осуществляется вычислителем 24 на основании определенных в БВМУПиС 23 суммарного минимального уровня помех на всех частотных позициях, а также минимального уровня сигнала на каждой частотной позиции и уровня суммарной нестационарной составляющей помех на всех частотных позициях, вычисленного в анализаторе помех 21. Синхронность работы анализатора помех 21, БВМУПиС 23 и вычислителя 24 осуществляет делитель 22. Сформированное второе n-разрядное двоичное число передатчиком канала обратной связи 25 передается на приемник канала обратной связи 26, с которого поступает на преобразователь ППРЧ передающей части радиолинии 4.

Таким образом реализованный в заявляемом устройстве механизм формирования неравновероятной последовательности номеров перестраиваемых частот из равновероятной последовательности с учетом оценки сигнально-помеховой обстановки позволяет в худшем случае (при наличии периодических пульсаций и/или большой дисперсии уровня случайных помех) причислить все помехи к преднамеренным, и ППРЧ оказывается равномерным. В лучшем случае, устойчиво «плохие» из-за случайных помех частоты будут использоваться при ППРЧ с меньшей вероятностью вплоть до исключения их из используемого множества частот, что позволяет существенно повысить помехоустойчивость и достоверность в системах связи широкополосного радиодоступа с ППРЧ, функционирующих в условиях неопределенных помех.

Источники информации

1. Системы беспроводной связи европейского стандарта DECT // В кн. Громаков Ю.А. Стандарты и системы подвижной радиосвязи. - М.: ЭКО-ТРЕНДЗ, 2000. - С.209-212.

2. Системы с прыгающей частотой / В кн. Кларк Дж., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. - М.: Радио и связь, 1987. - С.352-356.

3. Адресные системы с псевдослучайной перестройкой рабочей частоты / В кн. Помехозащищенность радиосистем со сложными сигналами - М.: Радио и связь, 1985. - С.86-87.

4. Frequency Hopping Data Communication System // US Patent №4653068, 1987.

5. Одоевский С.М., Ерышов В.Г. Адаптивно-игровой алгоритм переключения каналов передачи информации / Сети связи и системы коммутации. Сборник научных трудов. Выпуск 1. - СПб: "Тема", 2000. - С.91-98.

6. Кларк Дж., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. - М.: Радио и связь, 1987. - 392 с.

7. Дж. Спилкер. Цифровая спутниковая связь. М.: Связь, 1979. - 592 с.

8. Радиоприемные устройства / Под ред. Л.Г.Барулина. М.: Радио и связь, 1984. - 272 с.

9. Полупроводниковые приемно-усилительные устройства: Справочник радиолюбителя / P.M.Терещук, К.М.Терещук, С.А.Седов. - Киев: Наукова думка, 1989. - 800 с.

10. Шило В.Л. Популярные цифровые микросхемы. М.: Радио и связь, 1989. - 352 с.

11. П.Хорвиц, У.Хилл. Искусство схемотехники. Изд. 4-е, Том 1. М.: Мир, 1993. - 416 с.

12. П.Хорвиц, У.Хилл. Искусство схемотехники. Изд. 4-е, Том 2. М.: Мир, 1993. - 376 с.

13. П.Хорвиц, У.Хилл. Искусство схемотехники. Изд. 4-е, Том 2. М.: Мир, 1993. - 368 с.

14. Гольденберг Л.М., Матюшкин Б.Д., Поляк М.Н. Цифровая обработка сигналов. М.: Радио и связь, 1989. - 256 с.

15. У.Титце, К.Шенк. Полупроводниковая схемотехника: Справочное руководство. М.: Мир, 1982. - 512 с.

16. Алексеенко А.Г., Шагурин И.И. Микросхемотехника. М.: Радио и связь, 1982. - 414 с.

17. Каганов В.И. СВЧ полупроводниковые передатчики. М.: Радио и связь, 1981. - 400 с.

18. Батушев В.А. Микросхемы и их применение. М.: Радио с связь, 1983. - 271 с.

19. Варакин Л.Е. Системы связи с шумоподобными сигналами. М.: Радио и связь, 1985. - 384 с.

20. Дискриминатор для синхронизации по задержке псевдослучайной последовательности // АС СССР №647875, 1979.

21. Радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами // АС СССР №1635275, 1990.

22. Радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами // Патент РФ №2101871, 1996.

23. Радиолиния с амплитудно-фазоманипулированными шумоподобными сигналами // Патент РФ №2144272, 1999.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛИНИЯ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2004 |

|

RU2273099C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2178237C2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2099886C1 |

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1996 |

|

RU2101871C1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ ФАЗЫ СИГНАЛА | 2017 |

|

RU2646602C1 |

| СИСТЕМА СВЯЗИ НАЗЕМНОГО ПУНКТА УПРАВЛЕНИЯ С БЕСПИЛОТНЫМ ЛЕТАТЕЛЬНЫМ АППАРАТОМ | 2024 |

|

RU2825035C1 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

| Когерентная радиолиния | 2019 |

|

RU2735923C1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

Изобретение относится к области радиотехники и может быть использовано в системах связи широкополосного радиодоступа, функционирующих в условиях неопределенных помех. Достигаемый технический результат - повышение помехоустойчивости. В радиолинии с псевдослучайной перестройкой рабочей частоты (ПСП) осуществляется учет предопределенной дискретности множества n случайных чисел и сохранение в качестве источника входных равновероятных чисел типового n-разрядного двоичного генератора ПСП, где n=log2N, для увеличения разрядности исходных равновероятных псевдослучайных чисел используются два последовательно генерируемых n-разрядных двоичных псевдослучайных числа, причем второе n-разрядное двоичное число формируется с учетом результатов определения сигнально-помеховой обстановки, образующих в совокупности одно 2n-разрядное двоичное псевдослучайное число, что обеспечивает возможность задания ненулевых вероятностей выбора отдельных частот с минимальным значением 1/n2. 4 з.п. ф-лы, 7 ил.

1. Радиолиния с псевдослучайной перестройкой рабочей частоты, состоящая из приемной и передающей частей, при этом передающая часть содержит блок синхронизации передающей части радиолинии, выход которого соединен с входом генератора псевдослучайной последовательности и синхровходом преобразователя псевдослучайной последовательности передающей части радиолинии, информационный вход которого соединен с выходом генератора псевдослучайной последовательности, блок управления, вход которого соединен с выходом преобразователя псевдослучайной последовательности передающей части радиолинии, а выход - с входом синтезатора частот, выход которого соединен с модулирующим входом модулятора, информационный вход которого соединен с выходом кодера, причем вход кодера является входом радиолинии, выход модулятора соединен с входом усилителя мощности, выход которого подключен к передающей антенне, а приемная часть содержит декодер, выход которого является выходом радиолинии, а вход подключен к выходу решающего устройства и входу блока синхронизации приемной части радиолинии, управляющий вход решающего устройства подключен к первому управляющему выходу блока управления, а информационный вход - к первому информационному выходу детектора, второй информационный выход которого подключен к входу блока автоматической регулировки усиления, вход детектора подключен к выходу смесителя-гетеродина, информационный и управляющий входы которого подключены соответственно к выходу входного усилителя и второму управляющему выходу блока управления, информационный вход которого подключен к выходу блока автоматической регулировки усиления и к управляющему входу входного усилителя, информационный вход которого подключен к выходу приемной антенны, управляющий вход блока управления подключен к выходу преобразователя псевдослучайной последовательности приемной части радиолинии, синхро и информационный входы которого подключены соответственно к выходу блока синхронизации приемной части радиолинии и выходу генератора псевдослучайной последовательности, а выход блока синхронизации приемной части радиолинии подключен к входу генератора псевдослучайной последовательности, отличающаяся тем, что в передающей части дополнительно введен радиоприемник канала обратной связи, вход которого подключен к приемной антенне, а выход - к управляющему входу преобразователя псевдослучайной последовательности передающей части радиолинии, а в приемной части дополнительно введены анализатор помех, делитель, предназначенный для формирования двоичного числа с учетом сигнально-помеховой обстановки, блок вычисления минимального уровня помехи и сигнала, вычислитель, предназначенный для выработки тактовых частотных последовательностей, передатчик канала обратной связи, выход которого подключен к передающей антенне, вход делителя подключен к выходу блока синхронизации приемной части радиолинии, а первый и второй синхровыходы подключены соответственно к первым и вторым синхровходам анализатора помех и блока вычисления минимального уровня помехи и сигнала, второй синхровыход делителя подключен к первому синхровходу вычислителя, второй синхровход которого подключен к третьему синхровыходу делителя, управляющий вход анализатора помех подключен к выходу преобразователя псевдослучайной последовательности приемной части радиолинии, а первый и второй информационные входы анализатора помех подключены соответственно к выходу входного усилителя и первому информационному выходу блока вычисления минимального уровня помехи и сигнала, второй информационный выход которого подключен к первому информационному входу вычислителя, N информационных и N управляющих выходов анализатора помех, где N≥2, подключены соответственно к N информационным и N управляющим входам блока вычисления минимального уровня помехи и сигнала, а первая и вторая группы по N информационных выходов блока вычисления минимального уровня помехи и сигнала подключены соответственно к N информационным входам анализатора помех и N информационным входам вычислителя, управляющий и второй информационный входы которого подключены соответственно к выходам блока автоматической регулировки усиления и анализатора помех, информационный и управляющий выходы вычислителя подключены соответственно к входу передатчика канала обратной связи и управляющему входу преобразователя псевдослучайной последовательности приемной части радиолинии.

2. Радиолиния по п.1, отличающаяся тем, что анализатор помех состоит из N смесителей-гетеродинов, N детекторов, N измерителей, N интеграторов, первого сумматора, вычитателя, N постоянно запоминающих устройств, N блоков сравнения, N элементов переключения, второго сумматора, информационные входы N смесителей-гетеродинов объединены и являются первым информационным входом анализатора помех, управляющий вход i-го смесителя-гетеродина соединен с выходом i-го постоянно запоминающего устройства и с входом i-го блока сравнения, управляющие входы N блоков сравнения объединены и являются управляющим входом анализатора помех, выход i-го блока сравнения соединен с информационным входом i-го элемента переключения, синхровходы N элементов переключения, N измерителей и N интеграторов объединены и являются первым синхровходом анализатора помех, управляющие выходы N элементов переключения и информационные выходы N измерителей являются соответственно N управляющими и N информационными выходами анализатора помех, информационные входы N интеграторов подключены к информационным выходам соответствующих N измерителей, выход i-го смесителя-гетеродина соединен с входом i-го детектора, информационный вход i-го измерителя соединен с выходом i-го детектора, выходы N интеграторов объединены с входами соответствующих N информационных входов первого сумматора, синхронизирующий вход первого сумматора, вычитателя и синхровходы N интеграторов объединены и являются вторым синхровходом анализатора помех, информационный выход первого сумматора соединен с первым информационным входом вычитателя, второй информационный вход которого является вторым информационным входом анализатора помех, а третий информационный вход вычитателя подключен к выходу второго сумматора, выход вычитателя является выходом анализатора помех, N информационных входов второго сумматора являются соответствующими N информационными входами анализатора помех.

3. Радиолиния по п.1, отличающаяся тем, что делитель состоит из первого делителя частоты, второго делителя частоты и линии задержки, причем синхровход первого делителя частоты, второй синхровход второго делителя частоты и второй синхровход линии задержки объединены и являются синхровходом делителя, первые синхровыходы первого и второго делителей частоты, а также синхровыход линии задержки являются соответственно первым, вторым и третьим синхровыходами делителя, второй синхровыход первого делителя частоты подключен к первому синхровходу второго делителя частоты, второй синхровыход которого подключен к первому синхровходу линии задержки.

4. Радиолиния по п.1, отличающаяся тем, что блок вычисления минимального уровня помехи и сигнала состоит из переключателя входов, N первых компараторов, N первых регистров хранения, N вторых компараторов, N вторых регистров хранения, N счетчиков, N вычитателей и сумматора, причем N информационных входов переключателя входов являются N информационными входами блока вычисления минимального уровня помехи и сигнала, входы N счетчиков соединены с соответствующими N управляющими входами переключателя входов и являются N управляющими входами блока вычисления минимального уровня помехи и сигнала, синхровходы N счетчиков, N первых и N вторых регистров хранения объединены и являются вторым синхровходом блока вычисления минимального уровня помехи и сигнала, синхровходы N первых и N вторых компараторов объединены и являются первым синхровходом блока вычисления минимального уровня помехи и сигнала, выходы N счетчиков соединены с соответствующими N управляющими входами сумматора, вторые информационные выходы N первых регистров хранения соединены со вторыми информационными входами соответствующих N вторых регистров хранения, первыми информационными входами N вычитателей и являются соответствующими информационными выходами в первой и второй группах информационных выходов блока вычисления минимального уровня помехи и сигнала, первые информационные входы N первых компараторов подключены к соответствующим N информационным выходам первой группы N информационных выходов переключателя входов, первые информационные входы N вторых компараторов подключены к соответствующим информационным выходам второй группы из N информационных выходов переключателя входов, вторые информационные входы N первых компараторов подключены к соответствующим первым информационным выходам N первых регистров хранения, вторые информационные входы N вторых компараторов подключены к соответствующим первым информационным выходам N вторых регистров хранения, N информационных выходов первого компаратора подключены к соответствующим N информационным входам N первого регистра хранения, информационные выходы N вторых компараторов подключены к соответствующим первым информационным входам N вторых регистров хранения, вторые информационные выходы N вторых регистров хранения подключены к вторым информационным входам соответствующих N вычитателей, выходы N вычитателей соединены с соответствующими N информационными входами сумматора, информационный выход которого является первым и вторым информационными выходами блока вычисления минимального уровня помехи и сигнала.

5. Радиолиния по п.1, отличающаяся тем, что вычислитель состоит из компаратора, первого делителя, первого постоянно запоминающего устройства, N умножителей, второго постоянно запоминающего устройства, второго делителя, дешифратора, первого регистра хранения, второго регистра хранения, причем управляющий вход компаратора является управляющим входом вычислителя, выход компаратора подключен к управляющему входу первого делителя, первый и второй информационные входы которого являются соответственно вторым и первым информационным входами вычислителя, второй информационный вход первого делителя подключен к информационному входу второго делителя, выход первого постоянно запоминающего устройства подключен к третьему информационному входу первого делителя, вторые информационные входы N умножителей являются соответствующими N информационными входами вычислителя, первые информационные входы N умножителей объединены и подключены к выходу второго постоянно запоминающего устройства, выходы N умножителей подключены к соответствующим N информационным входам второго делителя, N информационных выходов которого соединены с соответствующими N информационными входами дешифратора, дополнительный информационный вход которого подключен к выходу первого делителя, N выходов дешифратора подключены к соответствующим N входам первого регистра хранения, выход которого подключен к информационному входу второго регистра хранения и является информационным выходом вычислителя, синхровходы первого и второго регистров хранения являются соответственно первым и вторым синхровходами вычислителя, причем выход второго регистра хранения является управляющим выходом вычислителя.

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2004 |

|

RU2273954C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ СО СКАЧКООБРАЗНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2005 |

|

RU2290758C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2099886C1 |

| US 4653068, 24.03.1987 | |||

| US 4328581, 04.05.1982. | |||

Авторы

Даты

2011-02-10—Публикация

2009-05-25—Подача