Настоящее изобретение относится к полупроводниковому устройству и к способу формирования полупроводникового устройства.

Настоящее изобретение, в частности, относится к полупроводниковым устройствам, рассчитанным на высокое напряжение/мощность, которые могут использоваться в качестве дискретных устройств в гибридных цепях и в мощных интегральных схемах, и, в частности, относится к полевым транзисторам, таким как мощные MOSFET структуры (полевые транзисторы со структурой металл-оксид-полупроводник), к биполярным транзисторам с изолированным затвором (IGBT) и к мощным устройствам других типов, таким как диоды, транзисторы и тиристоры.

Для устройств, разработанных для использования в интегральных схемах, предпочтительно, чтобы основные выводы (называемые анодом/катодом, истоком/стоком и эмиттером/коллектором) и управляющие выводы (называемые затвором или базой) были размещены на поверхности устройства для упрощения доступа к ним. Основной ток протекает между основными выводами, и поэтому он преимущественно протекает в поперечном направлении. Такие устройства, поэтому, обычно называют устройствами с поперечным протеканием тока. Такие устройства часто интегрируют с устройствами, рассчитанными на низкое напряжение, или цепями, построенными с использованием технологий комплементарных металло-оксидных полупроводников (CMOS) или других стандартных планарных технологий, для формирования мощных интегральных схем. В одной микросхеме могут быть интегрированы несколько устройств, рассчитанных на работу с высоким напряжением/мощностью. Между устройствами высокой мощности и низкой мощности, а также между расположенными рядом друг с другом мощными устройствами устанавливают изоляцию. При этом используются две основные технологии изолирования, а именно способ изолирования р-n-переходом (JI) и технология с использованием структуры типа "кремний на диэлектрике" (SOI (КНД)).

При использовании технологии изоляции р-n-переходом для изоляции соседних устройств используется полупроводниковый переход с обратным смещением. Однако эта технология во многих случаях не удовлетворяет требованиям применения в мощных интегральных схемах, поскольку при ее использовании может возникать электропроводность, образуемая не основными носителями, через полупроводниковую подложку (на которой сформирована активная часть устройства) и, поэтому, трудно устранить взаимные помехи между соседними устройствами. Кроме того, биполярные устройства с изоляцией на основе p-n-перехода (такие, как биполярные транзисторы с изолированным затвором с поперечным протеканием тока) также подвержены влиянию паразитной плазмы подвижных носителей в полупроводниковой подложке в открытом состоянии, которые требуется удалять при выключении. Это существенно снижает скорость переключения устройства.

В технологии КНД используется заглубленный изолирующий слой для изоляции по вертикали верхнего полупроводникового слоя от нижнего полупроводникового слоя и, соответственно, проводимость тока, в основном, ограничена верхним слоем полупроводника, и ток в нижнем полупроводниковом слое практически отсутствует при любом режиме работы. Горизонтальная или поперечная изоляция в КНД структуре обычно осуществляется с использованием канавок, заполненных окисью кремния или, благодаря использованию известной технологии изоляции LOCOS ("местное окисление кремния"). Технология КНД обеспечивает лучшую изоляцию, чем технология с использованием изоляции p-n-переходом, поскольку заглубленный изолирующий слой устраняет проводимость тока и предотвращает формирование плазмы в подложке.

В массе высоковольтного полупроводникового устройства формируют высоковольтный полупроводниковый переход, который предназначен для блокирования напряжения. Такой переход содержит слой полупроводника с относительно низким уровнем примесей, который противостоит большей части напряжения, прикладываемого к основным выводам, когда устройство находится в закрытом состоянии и работает в режиме блокирования высокого напряжения. Этот слой обычно называют областью или слоем дрейфа, которая в этом режиме работы частично или полностью истощена в отношении не основных носителей. В идеале, потенциал должен равномерно распределяться вдоль области дрейфа между двумя концевыми участками области дрейфа. Однако из уравнения 1-D Пуассона следует, что при заданном уровне легирования примесями области дрейфа, распределение электрического поля имеет треугольную форму, или, при полностью обедненном состоянии, форму трапеции. Поскольку область ниже значения электрического поля приблизительно может рассматриваться как напряжение пробоя, когда пик электрического поля достигает критического значения для полупроводника, очевидно, что для 1-D перехода, чем ниже уровень легирования примесями слоя дрейфа, тем выше напряжение пробоя. Однако в устройствах с переносом тока основными носителями, такими как устройство типа MOSFET, известное как LDMOSFET, сопротивление слоя дрейфа в открытом состоянии обратно пропорционально степени легирования примесями слоя дрейфа. Поскольку для высоковольтного переключателя требуется обеспечить низкий уровень сопротивления в открытом состоянии, низкий уровень концентрации легирования примесями влияет на рабочие характеристики устройства в открытом состоянии. Кроме того, для полупроводниковых устройств с поперечным протеканием тока значение критического электрического поля на поверхности меньше, чем в массе полупроводника, что дополнительно повышает трудности при построении высоковольтных полупроводниковых устройств с поперечным протеканием тока.

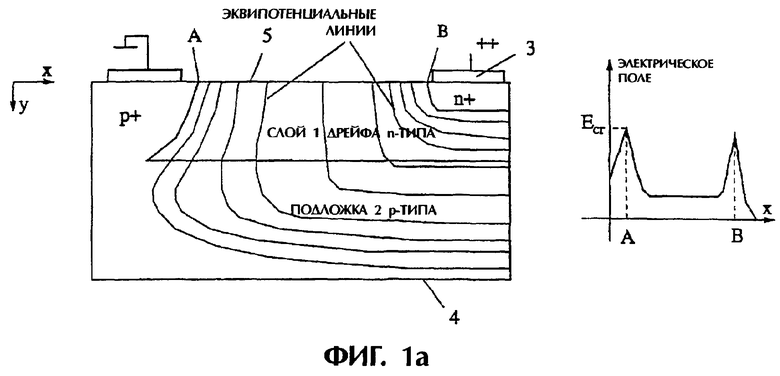

Использование технологии RESURF (пониженное влияние поверхностного поля) для устройств с изоляцией p-n-переходом позволяет повысить напряжения пробоя полупроводниковых устройств с поперечным протеканием тока, благодаря использованию дополнительного вертикального p-n-перехода, формируемого между областью дрейфа и полупроводниковой подложкой. На фиг.1а схематично показан обычный диод с изоляцией p-n-переходом, в котором используется эффект RESURF. Такой диод используется как часть обычного полупроводникового устройства с вертикальной структурой высокой мощности, такого, как транзистор с поперечным протеканием тока, LDMOSFET или LIGBT. На фиг.1а также показано распределение эквипотенциальных линий, и кромка обедненного слоя в режиме блокирования высокого напряжения. Следует отметить, что слой 1 дрейфа является полностью обедненным, но полупроводниковая подложка 2 остается не полностью обедненной. Эквипотенциальные линии изгибаются, по мере того как они проходят внутрь подложки, от вертикального направления к горизонтальному направлению, так, что ниже высоковольтного вывода 3 эквипотенциальные линии проходят практически параллельно нижней поверхности 4 подложки 2. Это происходит из-за того, что толщина полупроводниковой подложки 2 относительно велика (обычно 300 мкм) по сравнению с вертикальной протяженностью обедненного слоя от верхней поверхности 5 вглубь подложки 2 (обычно 60 мкм для устройств, рассчитанных на работу с напряжением 600 В). Следовательно, полупроводниковая подложка 2 остается не полностью обедненной, когда происходит пробой устройства. Известно, что в полупроводниковом диоде с поперечным протеканием тока с изоляцией p-n-переходом можно достичь напряжений пробоя, эквивалентных вертикальным диодам, несмотря на пониженное поверхностное критическое электрическое поле. Тем не менее, как показано на фиг.1а, даже оптимизированное распределение электрического поля, с использованием концепции RESURF, далеко от идеального (то есть имеющего прямоугольную форму). Кроме того, как уже было указано выше, устройства изоляцией p-n-переходом имеет недостаток, состоящий в высоком значении токов утечки и очень плохой изоляции, что сильно затрудняет их интеграцию в мощных интегральных схемах.

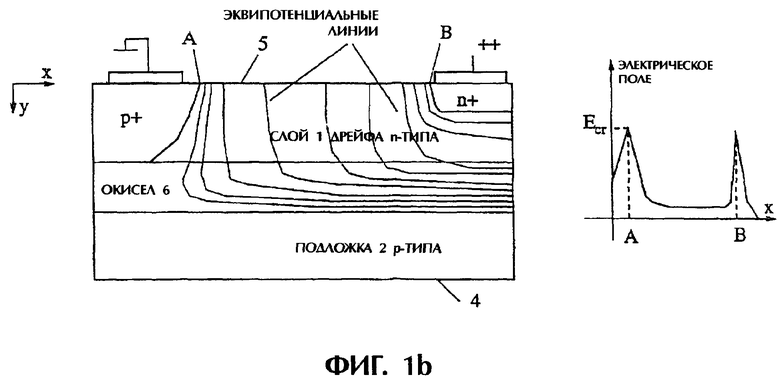

На фиг.1b показан обычный диод с КНД структурой, который обычно используется как часть высоковольтного устройства с КНД структурой с поперечным протеканием тока. Такая структура может быть построена с использованием известного соединения полупроводниковых пластин по технологии Unibond или SIMOX SOI. Также известны другие технологии, такие как кремний-на-алмазе (SOD). На фиг.1b, кроме того, показано распределение эквипотенциальных линий в режиме блокирования напряжения. Можно видеть, что прижим эквипотенциальных линий к кромке слоя 1 дрейфа приводит к плохому эффекту RESURF. Увеличение толщины заглубленного оксида 6 позволяет более равномерно перераспределить эквипотенциальные линии на верхней поверхности 5. Однако, в общем, напряжение пробоя все еще будет не больше, чем у устройства с изоляцией p-n-переходом или диода с изоляцией p-n-переходом, который показан на фиг.1а. И снова, эквипотенциальные линии слоя 1 дрейфа и заглубленного изолирующего слоя 6 окисла кремния под высоковольтным выводом практически выровнены вдоль горизонтальной поверхности. Это происходит из-за того, что полупроводниковая подложка 2 остается не полностью обедненной. В результате этого, все эквипотенциальные линии должны быть сжаты в слой 1 дрейфа и изолирующий слой 6 в случае КНД структуры и, более того, должны выравниваться параллельно поверхности раздела слоя 6 изоляции/полупроводниковой подложки 2. Это создает неравномерное распределение эквипотенциальных линий на верхней поверхности 5, в результате чего образуются высокие пики электрического поля и, поэтому, снижается напряжение пробоя. Кроме того, для устройств с КНД структурой сохранение перпендикулярного элемента плотности D=∈Е силовых линий электрического поля выше поверхности раздела полупроводникового слоя 1 /заглубленного окисла 6 ограничивает максимальное напряжение, которому может противостоять заглубленный окисел 6 до достижения критической величины электрического поля в слое 1 полупроводника на поверхности раздела. Такой вертикальный пробой приводит к очень сильному ограничению максимального напряжения, достижимого для данной толщины заглубленного окисла.

Таким образом, в общем, как в устройствах с изоляцией p-n-переходом, так и в устройствах с КНД структурой эквипотенциальные линии должны отклоняться от вертикальной ориентации в горизонтальную или поперечную ориентацию, и при этом в слое дрейфа получается далекое от идеального распределение потенциала.

Кроме того, когда мощная интегральная схема, выполненная с использованием тонкой технологии КНД структуры, содержит, по меньшей мере, полумостовую конфигурацию, которая включает два мощных устройства, работающих в различных режимах, на устройство, работающее на стороне режима высокого напряжения, может влиять отсечка области дрейфа в открытом состоянии. Это происходит из-за высокого значения электрического поля в области дрейфа, создаваемого высоким отрицательным потенциалом, образующимся в полупроводниковой подложке, по отношению к потенциалу одного из основных выводов устройства на стороне высокого напряжения.

Таким образом, очевидно, что полупроводниковая подложка в технологии с использованием КНД структуры не остается пассивной во всех режимах работы, и ее наличие приводит к плохому распределению эквипотенциальных линий во время режима блокирования напряжения, что может привести к преждевременному пробою, обычно на поверхности полупроводника или поверхности раздела заглубленного окисла/верхнего полупроводника из-за пробоя по вертикали. Недостаток технологии с использованием изоляции p-n-переходом состоит в очень плохой изоляции внутри мощной интегральной схемы и низком напряжении пробоя, которое, однако, обычно выше, чем в устройствах с использованием КНД структуры, но тем не менее ниже, чем было бы желательно.

Для дискретных устройств или гибридных схем, используемых в электронных цепях, рассчитанных на высокое напряжение или большую мощность, предпочтительно, чтобы основные выводы имели вертикальную ориентацию и были расположены на противоположных сторонах полупроводниковой пластины (например, с расположением низковольтного вывода сверху и высоковольтного вывода снизу). Эти устройства называются устройствами с вертикальной структурой, и они рассчитаны на высокое напряжение/большую мощность. По сравнению с устройствами с поперечным протеканием тока поток тока, проходящий между основными выводами, в этих устройствах направлен преимущественно вертикально, и это позволяет обеспечить более высокое номинальное значение тока и более высокое напряжение пробоя. Однако такие устройства трудно использовать в интегральных схемах. Примеры известных устройств, рассчитанных на высокое напряжение/большую мощность, представляют устройства DMOS & Trench MOSFET, DMOS & Trench IGBT и Cool MOS.

Для достижения оптимизированного компромисса между рабочими характеристиками в открытом состоянии, характеристиками переключения/напряжения пробоя, в устройствах с вертикальной структурой требуется использовать узкую область дрейфа, которая предпочтительно является полностью обедненной при полном блокировании напряжения. Такой слой может иметь толщину от 6 мкм до 180 мкм для устройств, предназначенных для работы в диапазоне напряжений от 50 В до 1,2 кВ. Обычно слой дрейфа располагают на полупроводниковой подложке с высоким уровнем легирования примесями. Полупроводниковая подложка, однако, оказывает отрицательное влияние на общие рабочие характеристики устройства. Прежде всего, она вводит паразитное сопротивление, что приводит к повышению потерь энергии в открытом состоянии. Во-вторых, для биполярных устройств с анодной инжекцией таких, как IGBT, поскольку подложка имеет высокую степень легирования примесями, для снижения потерь энергии на сопротивление подложки, инжекция со стороны подложки, которая действует как анод (эмиттер) устройства, в большинстве случаев будет слишком велико, что приводит к высоким потерям промежуточного переключения и длительному отключению из-за большого количества плазмы, накапливаемой внутри области дрейфа во время открытого состояния. В-третьих, подложка создает тепловое сопротивление, которое не позволяет эффективно рассеивать тепло через внешний теплоотвод, установленный снизу устройства. Наконец, если вертикальные устройства должны использоваться в интегральных схемах, наличие толстой полупроводниковой подложки существенно затрудняет изоляцию между соседними устройствами.

К настоящему времени было выдвинуто множество предложений по повышению напряжения пробоя полупроводниковых устройств, в частности, мощных полупроводниковых устройств. Их примеры описаны в публикациях US-A-5241210, US-A-5373183, US-A-5378920, US-A-5430316, US-A-5434444, US-A-5463243, US-A-5468982, US-A-5631491, US-A-6040617 и US-A- 6069396. Однако ни в одном из этих предложений известного уровня техники не была решена проблема повышения напряжения пробоя на основе подробного анализа распределения линий равного электрического потенциала в области дрейфа.

В публикации WO-A-98/32009 описано чувствительное к газу полупроводниковое устройство. Чувствительный к газу слой сформирован поверх нагревателя MOSFET, который используется для нагрева чувствительного к газу слоя. Подложка, на которой сформировано устройство, была подвергнута травлению с обратной стороны для формирования тонкой мембраны в чувствительной области. Следует отметить, что нагреватель MOSFET представляет собой низковольтное устройство (и как таковое не содержит область дрейфа) и, кроме того, тонкая мембрана сформирована ниже нагревателя MOSFET исключительно для обеспечения нагрева чувствительной области до очень высоких температур и не предназначена для оказания воздействия на поле или эквипотенциальные линии в устройстве.

В публикации US-A-5895972 описаны способ и устройство для охлаждения полупроводникового устройства во время фаз тестирования и отладки при разработке устройства. Вместо обычных тепловых стержней, выполненных, например, из меди, на устройстве закреплен тепловой стержень из прозрачного для инфракрасных лучей материала. В качестве предпочтительного описан тепловой стержень из алмаза. В публикации описано, что подложка, на которой сформировано устройство, может быть утончена перед установкой на устройстве стержня, прозрачного к инфракрасным лучам. Такое утончение подложки требуется для уменьшения потерь передачи, которая производится при оптических испытаниях и отладке устройства с использованием лучей света инфракрасного диапазона. В публикации не описан тип полупроводникового устройства, на который нанесен тепловой стержень, и в нем не содержится указание на то, что устройство представляет собой мощное устройство, содержащее область дрейфа. Кроме того, как указано в публикации, утончение подложки и нанесение теплового стержня предназначены исключительно для упрощения тестирования устройства с использованием оптического тестирования и отладки. Этот процесс осуществляется во время разработки устройства. Тепловой стержень не используется при нормальной работе устройства.

В публикациях известного уровня техники, направленных на полупроводниковые устройства, описан ряд предложений с использованием так называемой мембраны. Эти примеры включают публикации US-A-5420458, WO-A-94/22167, US-A-3689992 и US-A-6008126. В случае каждого из предложений известного уровня техники полупроводниковое устройство не является мощным устройством и, таким образом, не содержит область дрейфа. В каждом случае компоновка в виде мембраны используется для создания изоляции между полупроводниковыми устройствами и интегральной схемой или между областями в структуре полупроводникового устройства и/или для устранения или снижения паразитных емкостных связей. В каждом случае, поскольку описаны низковольтные устройства, структура мембраны практически не влияет на напряжение пробоя.

В соответствии с первым аспектом настоящее изобретение направлено на мощное полупроводниковое устройство, содержащее активную область, которая включает область дрейфа, по меньшей мере, часть области дрейфа, расположена в пределах мембраны, содержащей расположенные друг напротив друга верхнюю и нижнюю поверхности, причем верхняя поверхность мембраны содержит электрические выводы, подключенные непосредственно или опосредованно к ней, которые позволяют прикладывать напряжение в поперечном направлении через область дрейфа, причем рядом с нижней поверхностью мембраны полупроводниковая подложка отсутствует.

В соответствии со вторым аспектом настоящее изобретение направлено на мощное полупроводниковое устройство, содержащее активную область, которая включает область дрейфа, расположенную в слое, слой сформирован на полупроводниковой подложке, причем, по меньшей мере, часть полупроводниковой подложки ниже, по меньшей мере, части области дрейфа, удалена так, что указанная, по меньшей мере, часть области дрейфа сформирована в мембране, определяемой той частью слоя, ниже которого была удалена полупроводниковая подложка, к верхней поверхности мембраны прямо или - опосредованно подключены электрические выводы, позволяющие подавать напряжение в поперечном направлении через область дрейфа.

В соответствии с третьим аспектом настоящее изобретение направлено на мощное полупроводниковое устройство, содержащее активную область, которая включает область дрейфа, по меньшей мере, часть области дрейфа расположена в мембране, содержащей расположенные друг напротив друга верхнюю и нижнюю поверхности, по меньшей мере, один электрический вывод подключен непосредственно или опосредованно к верхней поверхности и, по меньшей мере, один электрический вывод подключен непосредственно или опосредованно к нижней поверхности, что позволяет прикладывать напряжение вертикально через область дрейфа, причем рядом с нижней поверхностью мембраны полупроводниковая подложка отсутствует.

В соответствии с четвертым аспектом настоящее изобретение направлено на мощное полупроводниковое устройство, содержащее активную область, которая включает область дрейфа, расположенную в слое, слой сформирован на полупроводниковой подложке, по меньшей мере, часть полупроводниковой подложки ниже, по меньшей мере, части области дрейфа удалена так, что указанная, по меньшей мере, часть области дрейфа сформирована в мембране, определенной указанной частью слоя, ниже которого полупроводниковая подложка была удалена, и, по меньшей мере, один электрический вывод подключен непосредственно или опосредованно к верхней поверхности и, по меньшей мере, один электрический вывод подключен непосредственно или опосредованно к нижней поверхности, что позволяет прикладывать напряжение вертикально через область дрейфа.

Указанная, по меньшей мере, часть области дрейфа полностью или, по существу, полностью обеднена в отношении подвижных носителей заряда, когда к выводам устройства прикладывают напряжение. В первом и втором аспектах настоящего изобретения эквипотенциальные линии в указанной, по меньшей мере, части области дрейфа располагаются, по существу, перпендикулярно к верхней и нижней поверхностям мембраны, и, по существу, равномерно распределяются в поперечном направлении по указанной, по меньшей мере, части области дрейфа. Это, в свою очередь, приводит к повышению напряжения пробоя, которое может приближаться к идеальному или теоретическому пределу. В третьем и четвертом аспектах эквипотенциальные линии в указанной, по меньшей мере, части области дрейфа располагаются, по существу, параллельно верхней и нижней поверхностям мембраны и, по существу, равномерно распределяются по вертикали через указанную, по меньшей мере, часть области дрейфа.

Таким образом, в предпочтительных вариантах воплощения отсутствие полупроводниковой подложки, по меньшей мере, под частью обедненной области в устройствах с поперечным протеканием тока приводит к улучшению способности противостоять напряжению пробоя, благодаря более благоприятному распределению электрического поля и потенциала в области дрейфа мощного устройства. Для устройств с вертикальной структурой отсутствие полупроводниковой подложки позволяет сформировать тонкую область дрейфа и устранить паразитные явления, такие как паразитное последовательное электрическое сопротивление и тепловое сопротивление подложки.

Мощные устройства обычно работают с напряжением в диапазоне от 30 В до 1,2 кВ и с токами в диапазоне от 100 мА до 50 А. Они могут использоваться в диапазоне от домашних электрических приборов, электрических автомобилей, систем управления двигателями и систем питания электроэнергией до радиочастотных и сверхвысокочастотных цепей и систем передачи данных.

Следует понимать, что термины "верх" и "низ", "выше" и "ниже", и "поперечный" и "вертикальный" используются в настоящем описании условно и что по отношению к устройству в целом невозможно использовать какие-либо характеристики физической ориентации.

Так называемое мембранное мощное устройство в соответствии с настоящим изобретением может представлять собой любое устройство из множества различных типов, включая, например, диод, транзистор, тиристор, управляемое устройство MOS (МОП), такое как MOSFET, биполярной транзистор с изолированным затвором (IGBT), устройство с двумя затворами и т.д.

Предпочтительные варианты воплощения, дополнительно описанные ниже, направлены на высоковольтное мощное устройство, которое способно противостоять высокому напряжению пробоя, в котором обеспечена исключительная изоляция и которое обладает пониженным самонагревом.

Может использоваться такая компоновка, в которой только часть области дрейфа расположена в мембране.

В первом и втором аспектах, где только часть области дрейфа расположена в мембране, предпочтительно, сторона вывода высокого напряжения области дрейфа находится в пределах мембраны; при этом остальная часть области дрейфа, включая сторону вывода низкого напряжения, может располагаться за пределами мембраны.

В третьем и четвертом аспектах боковые стороны устройства могут быть расположены за пределами мембраны, в то время как активная область, которая включает часть области дрейфа, расположена в пределах мембраны.

В любом аспекте область дрейфа может быть полностью расположена в мембране.

По меньшей мере, один изолирующий слой может окружать область дрейфа. По меньшей мере, один изолирующий слой может быть расположен в указанной мембране или в отдельной мембране так, что он проходит от верхней поверхности мембраны до нижней поверхности мембраны.

По меньшей мере, один изолирующий слой может окружать область дрейфа и может быть расположен за пределами мембраны.

Один изолирующий слой или, по меньшей мере, один изолирующий слой может состоять из электроизолирующего материала. Один изолирующий слой или, по меньшей мере, один изолирующий слой может представлять собой слой полупроводника с высокой степенью легирования примесями, на который при использовании подают смещение для создания полупроводникового перехода с обратным смещением или со смещением ниже уровня смещения в прямом направлении.

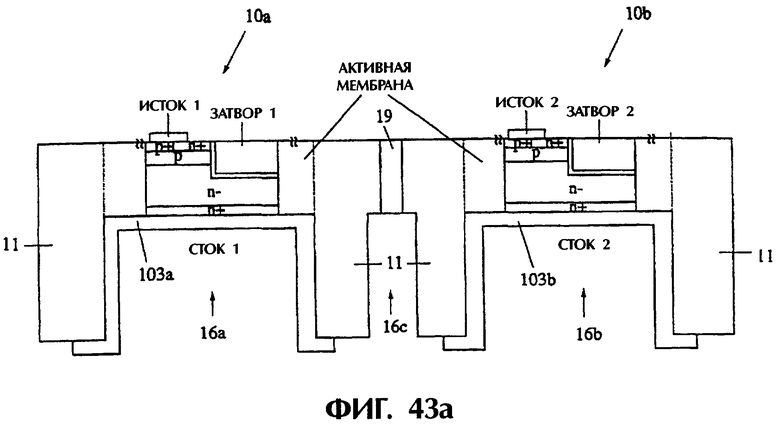

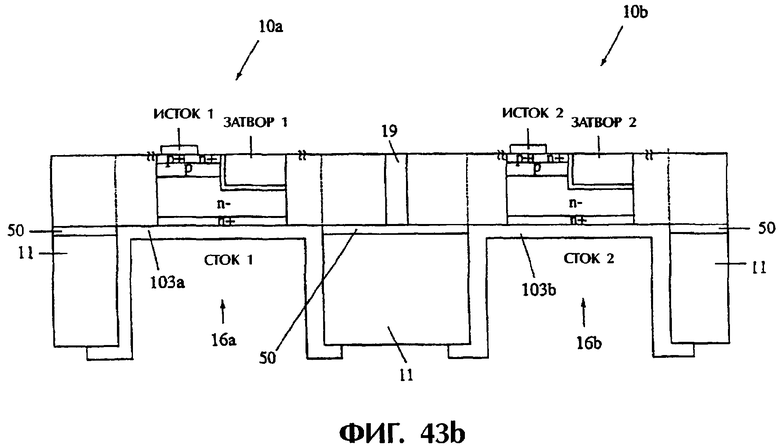

Может использоваться, по меньшей мере, одно дополнительное мощное устройство, содержащее область дрейфа, по меньшей мере, часть которой расположена на указанной мембране или на отдельной мембране. Отдельная мембрана, предпочтительно, сформирована поверх той же исходной подложки и, предпочтительно, на том же этапе изготовления, на котором другая мембрана или каждая другая мембрана сформирована в устройстве.

Может быть сформировано, по меньшей мере, одно низковольтное устройство. Указанное, по меньшей мере, одно низковольтное устройство может быть расположено в указанной мембране. В качестве альтернативы, указанное, по меньшей мере, одно низковольтное устройство может быть расположено за пределами указанной мембраны. В этом случае указанное, по меньшей мере, одно низковольтное устройство может содержать дополнительную мембрану, причем указанная дополнительная мембрана, предпочтительно, сформирована поверх той же исходной подложки и, предпочтительно, на том же этапе изготовления, на котором в устройстве были сформированы другие мембраны. В любом случае такая компоновка позволяет сформировать мощную интегральную микросхему. При этом низковольтное устройство (или устройства) может представлять собой, например, биполярную цепь или цепь CMOS. В таком низковольтном мощном устройстве могут быть сформированы цепи управления, защитные цепи или цепи обработки. В предпочтительных вариантах воплощения, описанных ниже, такие низковольтные устройства хорошо изолированы от мембранных мощных устройств как по вертикали, так и в поперечном направлении. Вертикальная изоляция получается, благодаря отсутствию паразитной подложки под активной областью мощного устройства. Поперечная изоляция обеспечивается, как кратко описано выше, с помощью одного или нескольких изолирующих слоев, сформированных предпочтительно в мембране, от верхней до нижней поверхности мембраны или за пределами мембраны.

Между соседними устройствами может быть установлен, по меньшей мере, один изолирующий слой, обеспечивающий электрическую изоляцию между ними. Указанный изолирующий слой может быть расположен на другой мембране, причем указанная дополнительная мембрана, предпочтительно, может быть сформирована поверх той же исходной подложки и, предпочтительно, на одном этапе изготовления с другой мембраной или с каждой другой мембраной, установленной в устройстве.

В первом и втором аспекте настоящего изобретения устройство может содержать электроизолирующий и теплопроводный слой, расположенный рядом с нижней поверхностью мембраны. Электроизолирующий теплопроводный слой используется для облегчения отвода большей части тепла, которое, в противном случае, может накапливаться в мембране при работе мощного устройства. Этот слой может быть изготовлен из любого подходящего материала, такого как, например, поликристаллический алмаз, аморфный алмаз, нитрид бора, окисел алюминия и т.д. Материал, предпочтительно, сформирован путем нанесения на необработанную подложку в виде слоя, с использованием способа напыления или осаждения из паров химического реагента или с использованием любой другой подходящей технологии. Слой может полностью заполнять пространство под мембраной или может быть сформирован как тонкий слой под мембраной, который располагается на боковых стенках и на нижней поверхности остающихся частей подложки. Этот слой, предпочтительно, находится в тепловом контакте с теплоотводом.

В третьем и четвертом аспектах нижний вывод может быть электро- и теплопроводным. Нижний вывод может быть изготовлен из металла или из комбинации металлов, таких как алюминий, медь и т.д. Нижний вывод может заполнять пространство под мембраной. В предпочтительном варианте воплощения нижний вывод сформирован как тонкий слой под мембраной, который следует конфигурации боковых стенок остающихся частей подложки и под основной нижней поверхностью устройства. Этот слой, предпочтительно, находится в тепловом контакте с внешним теплоотводом. В качестве альтернативы, на нижней стороне одной или отдельной мембраны, помимо одного нижнего вывода, могут быть расположены дополнительные выводы, которые выполнены в форме тонких слоев, изолированных друг от друга.

Мембрана может содержать полупроводниковый слой, сформированный на электроизолирующем слое. Электроизолирующий слой может представлять собой слой окисла, сформированный с использованием, например, известной технологии КНД. Когда подложку вытравливают для формирования мембраны, такой слой окисла обычно действует как ограничитель вытравливания, который помогает сформировать мембрану. В третьем и четвертом аспектах, этот слой удаляют для обеспечения доступа для слоя вывода, который должен быть сформирован с нижней стороны.

В первом и втором аспектах устройство может содержать механически прочный и электроизолирующий слой, сформированный под мембраной. Механически прочный и электроизолирующий слой обеспечивает структурную прочность мембраны, а также минимизирует риск разрушения мембраны.

В любом аспекте область дрейфа может иметь неравномерный профиль легирования примесями. Это позволяет обеспечить, по существу, равномерное распределение эквипотенциальных линий в области дрейфа. Это, в свою очередь, приводит к повышению напряжения пробоя, которое может приближаться к идеальному или теоретическому пределу. Концентрация легирования примесями в области дрейфа на стороне высоковольтного вывода устройства, предпочтительно, относительно высокая, и концентрация легирования примесями в области дрейфа на стороне низковольтного вывода устройства, предпочтительно, относительно низкая. Концентрация легирования примесями в области дрейфа может изменяться линейно от одной стороны области дрейфа к другой. Это позволяет дополнительно улучшить возможности устройства противостоять напряжению пробоя.

В первом и втором аспектах область дрейфа может содержать, по меньшей мере, два полупроводниковых слоя с чередующимся типом проводимости, сформированных один на другом и находящихся в контакте друг с другом. При использовании эти два или несколько полупроводниковых слоя с чередующимся типом проводимости формируют полупроводниковый переход в вертикальном направлении так, что область дрейфа может быть полностью обедненной в отношении подвижных носителей заряда, когда к выводам устройства прикладывают напряжение. Это, в свою очередь, позволяет обеспечить, по существу, перпендикулярное расположение эквипотенциальных линий по отношению к указанной верхней и нижней поверхностям мембраны, по меньшей мере, в части области дрейфа и, по существу, равномерное распределение в поперечном направлении вдоль, по меньшей мере, части области дрейфа. Это, в свою очередь, обеспечивает более высокое напряжение пробоя, которое может приближаться к идеальному или теоретическому пределу.

В любом аспекте область дрейфа может содержать множество расположенных рядом друг с другом в поперечном направлении полупроводниковых областей с чередующимся типом проводимости. Эти расположенные рядом друг с другом в поперечном направлении полупроводниковые области с чередующимся типом проводимости формируют множество расположенных в поперечном направлении переходов в направлении "z" устройства, что, в свою очередь, позволяет обеспечить, по существу, равномерное распределение эквипотенциальных линий в указанной, по меньшей мере, части области дрейфа в пределах указанной, по меньшей мере, части области дрейфа. Это, в свою очередь, повышает напряжение пробоя, которое может приближаться к идеальному или теоретическому пределу.

В любом аспекте область дрейфа может содержать множество расположенных рядом друг с другом в поперечном направлении полупроводниковых ячеек с чередующимся типом проводимости, расположенных в плоскости устройства. Эти ячейки могут быть расположены в правильном или неправильном порядке. Каждая компоновка, в свою очередь, позволяет обеспечить, по существу, равномерное распределение эквипотенциальных линий в указанной, по меньшей мере, части области дрейфа. Это, в свою очередь, приводит к повышению напряжения пробоя, которое может приближаться к идеальному или теоретическому пределу.

Устройство может содержать концевую область, расположенную в непосредственной близости и находящуюся в контакте с областью дрейфа, причем указанная концевая область может быть сформирована для снижения вероятности преждевременного пробоя на кромке области дрейфа. По меньшей мере, часть указанной концевой области может быть расположена внутри мембраны. По меньшей мере, часть указанной концевой области может быть расположена за пределами мембраны и выше любой полупроводниковой подложки. Область дрейфа может быть в большей степени легирована примесями, чем, по меньшей мере, часть концевой области. Область дрейфа может быть в большей степени легирована примесями, чем полупроводниковая подложка.

В соответствии с этим пятый аспект настоящего изобретения направлен на способ формирования мощного полупроводникового устройства, содержащего активную область, которая включает область дрейфа, способ содержит следующие этапы: формирование в слое, сформированном на полупроводниковой подложке, мощного полупроводникового устройства, включающего активную область, которая содержит область дрейфа; и удаление, по меньшей мере, части полупроводниковой подложки ниже, по меньшей мере, части области дрейфа так, чтобы указанная, по меньшей мере, часть области дрейфа была сформирована в мембране, определяемой этой частью слоя, ниже которой полупроводниковая подложка была удалена.

Предпочтительно, чтобы подложка была удалена, по меньшей мере, на последнем или на одном из последних этапов процесса изготовления устройства. При этом подложка обеспечивает поддержку для устройства в течение как можно большего времени в ходе процесса изготовления.

Указанная, по меньшей мере, часть полупроводниковой подложки может быть удалена способом жидкостного вытравливания.

Указанная, по меньшей мере, часть полупроводниковой подложки может быть удалена способом сухого вытравливания.

Указанная, по меньшей мере, часть полупроводниковой подложки может быть удалена с использованием заглубленного изолирующего слоя в качестве ограничителя вытравливания. Заглубленный слой может представлять собой часть структуры "кремний на диэлектрике" (КНД).

По меньшей мере, один полупроводниковый слой может быть введен способом имплантации, диффузии или осаждения с обратной стороны устройства после формирования мембраны.

Нижний слой вывода может быть нанесен на нижнюю сторону мембраны, причем указанный нижний слой вывода находится в контакте, по меньшей мере, с одним полупроводниковым слоем, расположенным в мембране.

Способ может содержать этап нанесения электроизолирующего и теплопроводного слоя, расположенного вблизи к поверхности мембраны. Электроизолирующий и теплопроводный слой может быть нанесен с помощью процесса осаждения (предпочтительно на необработанную подложку).

В качестве альтернативы, способ может содержать этап нанесения электро- и теплопроводного слоя, который действует как электрод (вывод), расположенный вблизи к нижней поверхности мембраны. Указанный слой может быть нанесен способом осаждения на необработанную подложку.

При формировании устройств и в способах, описанных выше, могут использоваться одна или несколько известных технологий формирования биполярных CMOS, BI-CMOS, DMOS, КНД структур, а также технология формирования канавок на соответствующих этапах изготовления интегральных схем.

В устройствах и способах, описанных выше, область дрейфа может содержать, по меньшей мере, один из материалов кремний, карбид кремния, алмаз, нитрид галлия и арсенид галлия.

В случае, когда сформирован, по меньшей мере, один изолирующий слой, он может состоять из одного из материалов, таких как двуокись кремния, нитрид, алмаз, окись алюминия, нитрид алюминия и нитрид бора.

Варианты настоящего изобретения будут описаны ниже на примере, со ссылкой на прилагаемые чертежи, на которых:

на фиг.1а схематично показан вид в поперечном сечении мощного диода с изоляцией p-n-переходом известного уровня техники;

на фиг.1b схематично показан вид в поперечном сечении мощного диода с КНД структурой известного уровня техники;

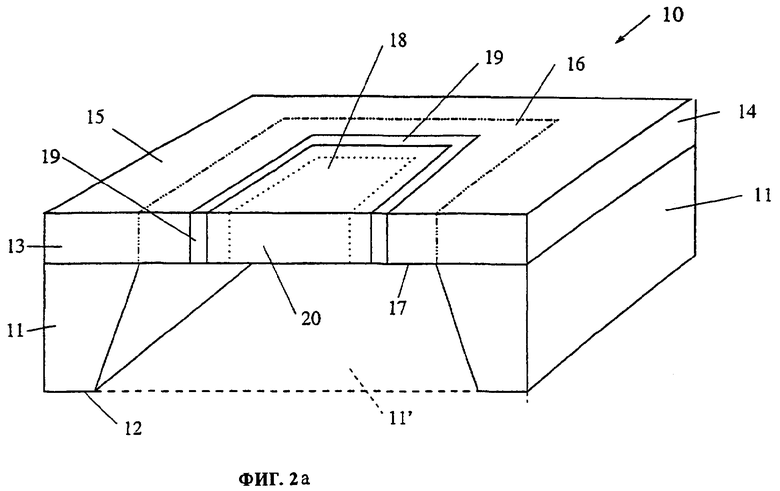

на фиг.2а схематично показан вид в перспективе первого примера устройства в соответствии с настоящим изобретением;

на фиг.2b схематично показан вид в перспективе второго примера устройства в соответствии с настоящим изобретением;

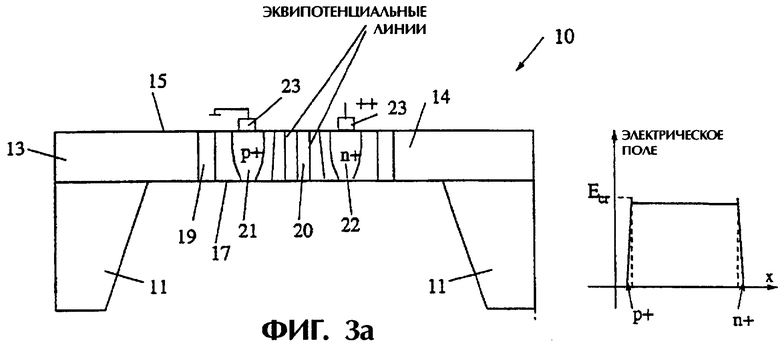

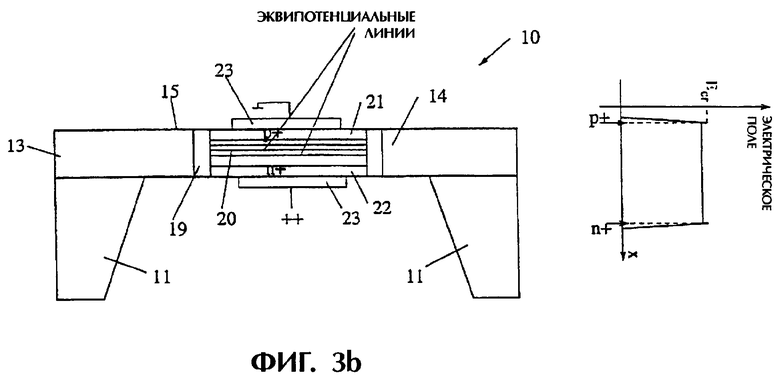

на фиг.3 схематично показан вид в поперечном сечении другого примера устройства в соответствии с настоящим изобретением, в котором показаны эквипотенциальные линии; и,

на фигурах 4-43 схематично показаны виды в поперечном сечении или виды в перспективе других примеров устройств в соответствии с настоящим изобретением.

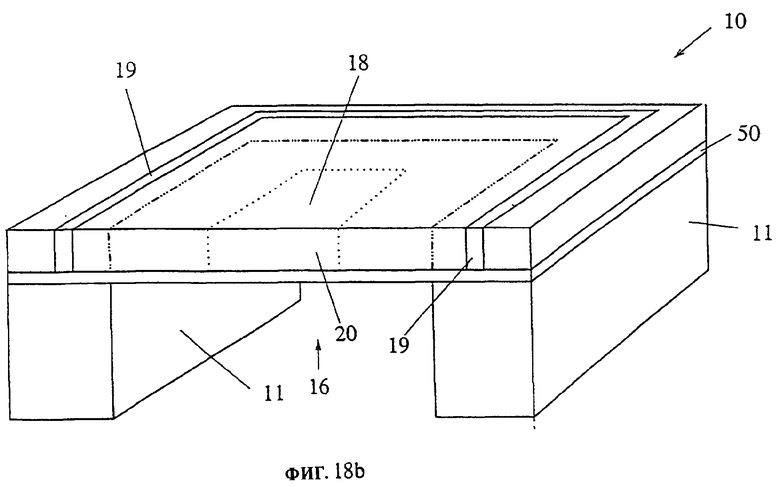

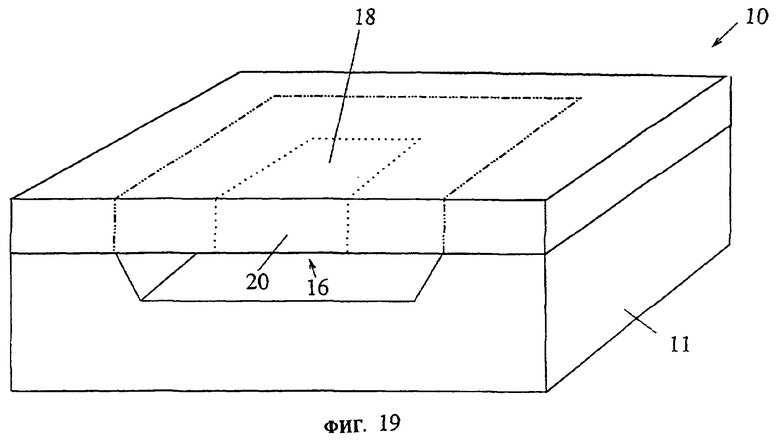

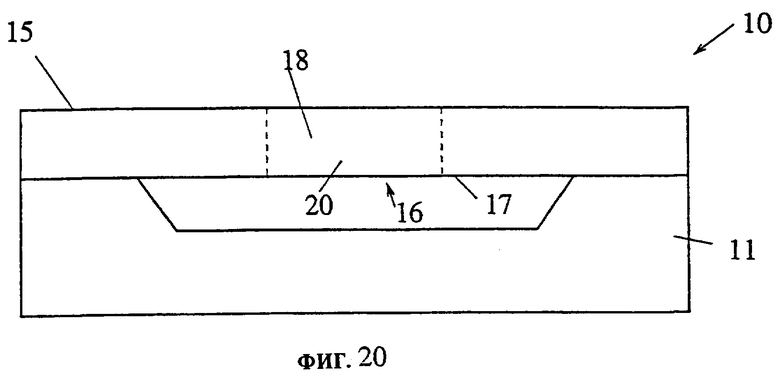

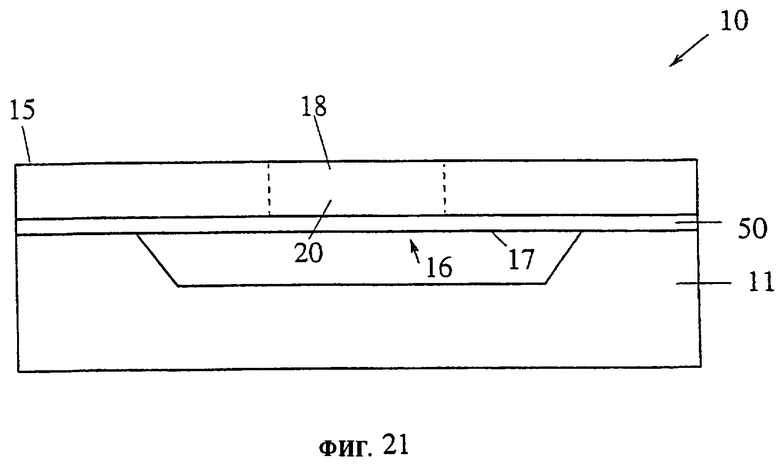

Как показано на фиг.2а и 2b, первый и второй примеры мембранного мощного полупроводникового устройства 10 в соответствии с настоящим изобретением содержат полупроводниковую подложку 11, имеющую нижнюю поверхность 12, которая формирует основную нижнюю поверхность устройства 10. Первый тонкий слой 13, который в этих примерах содержит полупроводниковый слой 14, сформирован на подложке 11 и имеет верхнюю поверхность 15, которая представляет собой основную верхнюю поверхность 5 устройства 10. Исходная полная протяженность подложки 11 обозначена на фигурах 2а и 2b пунктирными линиями. При изготовлении часть 11' подложки 11 ниже тонкого слоя 13 полностью удаляют до тонкого слоя 13 с тем, чтобы оставить область тонкого слоя 13, ниже которой отсутствует подложка 11, причем эта область называется здесь мембраной 16 (показана в пределах штрихпунктирных линий). Оставшиеся части подложки 11 формируют опорные ножки. Мембрана 16 имеет нижнюю поверхность 17. Активная структура 18 мощного устройства 10 (обозначена линиями из точек) в этих примерах расположена полностью в пределах мембраны 16. В примере, показанном на фигуре 2а, активная структура 18 электрически изолирована от других устройств или цепей изолирующим слоем 19, сформированным в мембране 16 между верхней поверхностью 15 и нижней поверхностью 17 мембраны, так, что изолирующий слой 19 окружает активную структуру 18 мощного устройства 10. В примере, показанном на фигуре 2b, изолирующий слой 19 расположен за пределами мембраны 16 в пределах тонкого слоя 13 так, что он окружает активную структуру 18 мощного устройства 10. В примерах, показанных на фигурах 2а и 2b, мощное устройство 10 содержит слой 20 дрейфа, который расположен в полупроводниковом слое 14 внутри первого тонкого слоя 13 и полностью находится в пределах мембраны 16. Слой 20 дрейфа выдерживает высокое напряжение, прикладываемое к основным выводам (не показаны) мощного устройства 10, когда мощное устройство 10 находится в закрытом состоянии и блокирует напряжение через основные выводы. Во время такого режима работы слой 20 дрейфа становится частично или в идеале полностью обедненным в отношении подвижных носителей заряда. В соответствии с вариантом воплощения настоящего изобретения, если основные выводы расположены на верхней поверхности 15 устройства и в пределах мембраны 16, эквипотенциальные линии в поперечном сечении устройства вдоль слоя 20 дрейфа будут располагаться практически перпендикулярно основной верхней поверхности 15 и нижней поверхности 17 мембраны. В соответствии с другим вариантом воплощения настоящего изобретения, если первый основной вывод будет расположен на поверхности 15 и в пределах мембраны 16, и второй основной вывод будет расположен рядом с нижней стороной мембраны и в пределах мембраны 16, эквипотенциальные линии будут практически параллельны как верхней, так и нижней поверхностям 15, 17.

Предпочтительно, чтобы часть 11' подложки была удалена в ходе последнего или одного из последних этапов изготовления, и, в частности, после завершения формирования всех или, по существу, всех структур на тонком слое 13 и выше него, так, что вся подложка 11 может поддерживать полностью тонкий слой 13 в ходе этих этапов изготовления.

Здесь следует отметить разницу в двумерном распределении потенциала высоковольтных устройств известного уровня техники, таких как обычное высоковольтное устройство с изоляцией полупроводниковым переходом (JI) или устройство типа "кремний на диэлектрике" (КНД), и мембранных мощных устройств в соответствии с настоящим изобретением. Как можно видеть на фигурах 1а и 1b, на которых показаны обычные устройства, эквипотенциальные линии практически перпендикулярны поверхности 5, но по мере их углубления в массу устройства они выравниваются параллельно нижней поверхности 4 подложки. Такое распределение эквипотенциальных линий может привести к преждевременному пробою. На фигурах 3а и 3b показано двумерное распределение эквипотенциальных линий в примере простой структуры мощного устройства в соответствии с настоящим изобретением, сформированного с использованием одного высоковольтного полупроводникового перехода. В примере, показанном на фигуре 3а, основные выводы 23 установлены на верхней поверхности 15, и область 20 дрейфа содержит для простоты только один слой полупроводника, который в меньшей степени легирован примесями, чем область 21 р+ анода и область 22 n+ катода. Область 20 дрейфа становится полностью обедненной в режиме блокирования напряжения и перед возникновением пробоя. Как показано на фигуре 3а, по сравнению с фигурой 1а и 1b, можно видеть, что эквипотенциальные линии располагаются перпендикулярно или практически перпендикулярно, как к верхней поверхности 15, так и к нижней поверхности 17 мембраны 16, и распределяются, по существу, равномерно от области 21 анода до области 22 катода внутри области 20 дрейфа так, что значение напряжения пробоя приближается к его идеальному пределу. В примере, показанном на фигуре 3b, основные выводы 23 расположены на верхней поверхности 15 и нижней поверхности 17 соответственно так, что эквипотенциальные линии располагаются параллельно или практически параллельно как к верхней поверхности 15, так и к нижней поверхности 17, и распределяются, по существу, равномерно от области 21 анода до области 22 катода внутри области 20 дрейфа так, что напряжение пробоя будет идеальным для данной толщины слоя 20 дрейфа.

Предпочтительные варианты воплощения высоковольтных мощных устройств в соответствии с настоящим изобретением также отличаются от устройств известного уровня техники способом формирования изоляции. Изоляция в предпочтительных мембранных мощных устройствах реализована вертикально и является идеальной, благодаря отсутствию подложки ниже активной структуры 18 мембранного мощного устройства 10, а также формируется поперечно с использованием изолирующего слоя 19, который окружает активную структуру 18 мощного устройства 10.

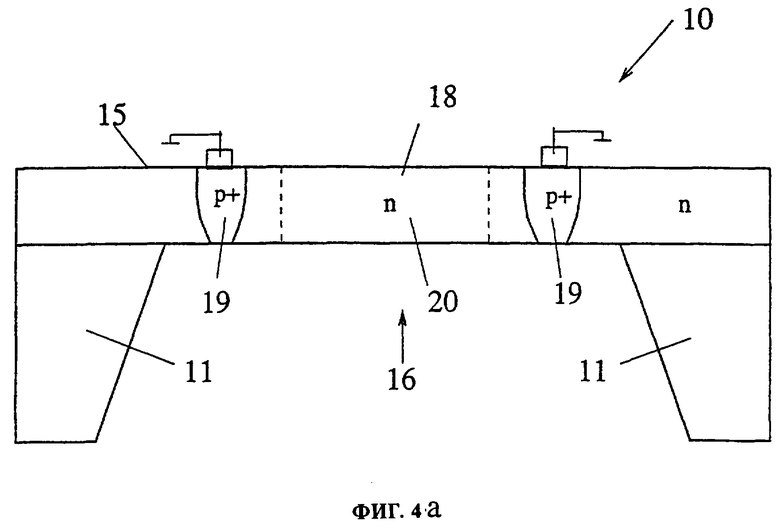

Там, где он установлен, изолирующий слой 19 может быть выполнен в форме полупроводникового слоя с высокой степенью легирования примесями, к которому подключено соответствующее напряжение смещения так, что все полупроводниковые переходы, связанные с указанным изолирующим слоем, находятся под обратным смещением или под нулевым смещением. В этом случае, изолирующий слой действует, как эффективный барьер для электропроводности. На фигурах 4а и 4b показан пример мембранного мощного устройства 10, содержащего р+ изолирующий слой 19, который проходит от верхней поверхности 15 до нижней поверхности 17 мембраны и который окружает активную структуру 18. Р+ изолирующий слой 19 соединен с землей и ее потенциал в данном примере является наименьшим доступным потенциалом в мощной интегральной схеме. В примере, показанном на фигуре 4а, изолирующий слой 19 расположен в пределах мембраны 16. В примере по фигуре 4b изолирующий слой 19 расположен за пределами мембраны 16.

Изолирующий слой может, в качестве альтернативы, быть выполнен в виде изолирующего слоя, например, окисла кремния и может быть выполнен в форме канавки или слоя LOCOS (технология изготовления интегральной схемы МОП с толстым защитным слоем окисла кремния). В дополнительном альтернативном варианте изоляция может быть обеспечена с помощью канавок, заполненных слоями окисла и поликристаллического кремния. Также могут использоваться другие изолирующие материалы. Другая альтернатива состоит в использовании воздушных зазоров (так называемая изоляция "MESA" или изоляция "канавками").

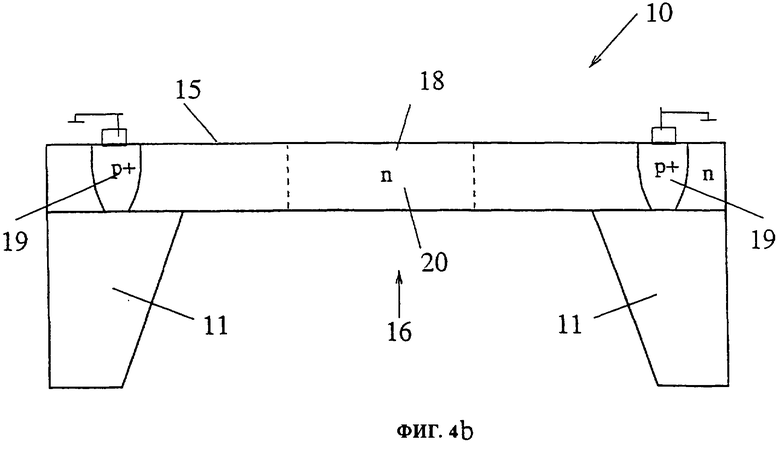

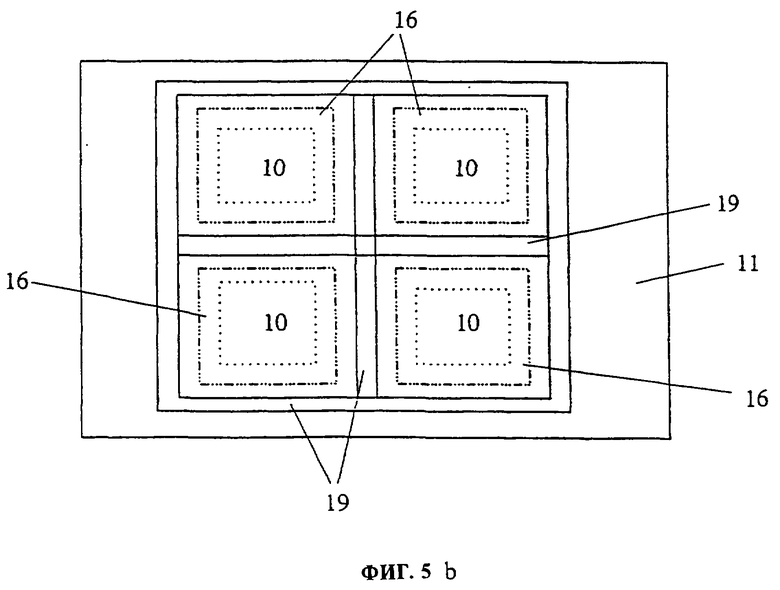

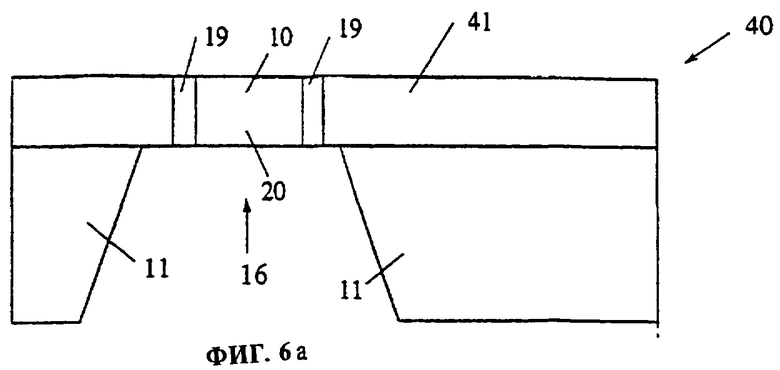

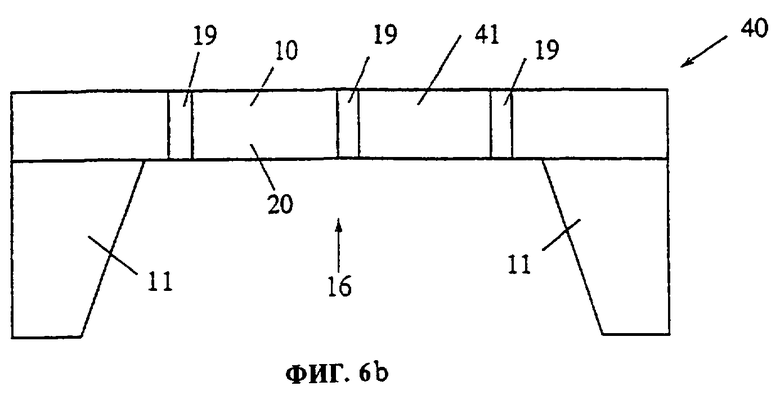

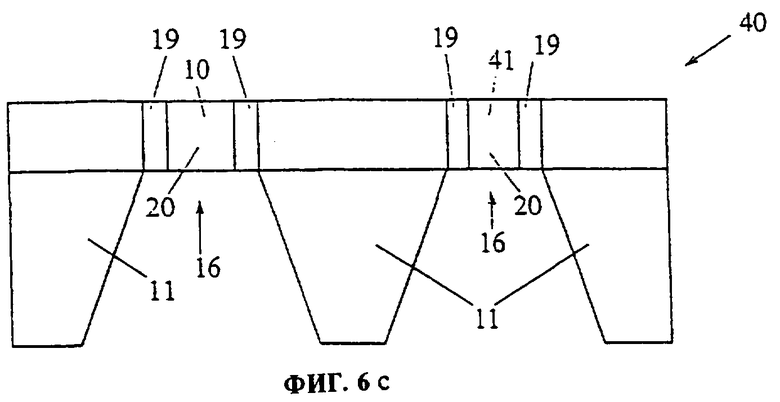

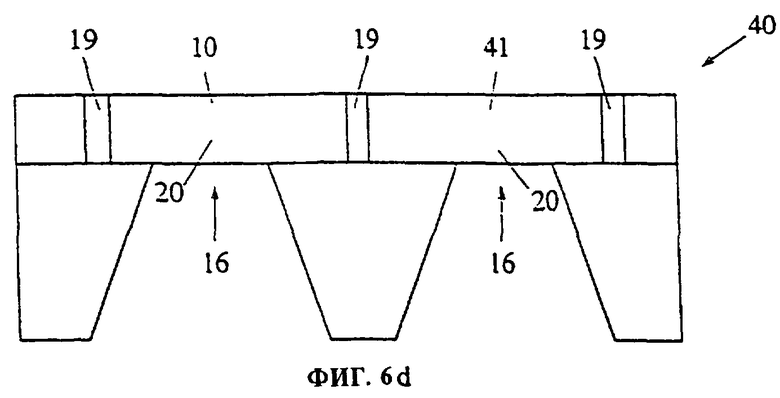

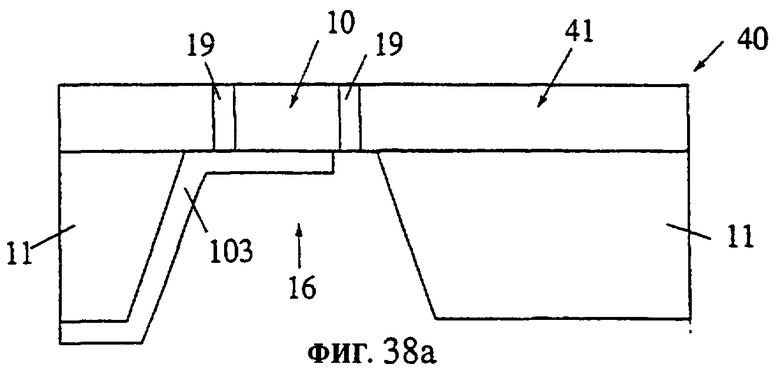

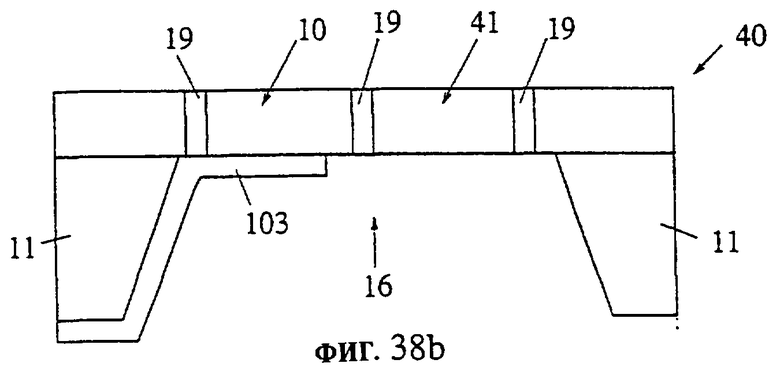

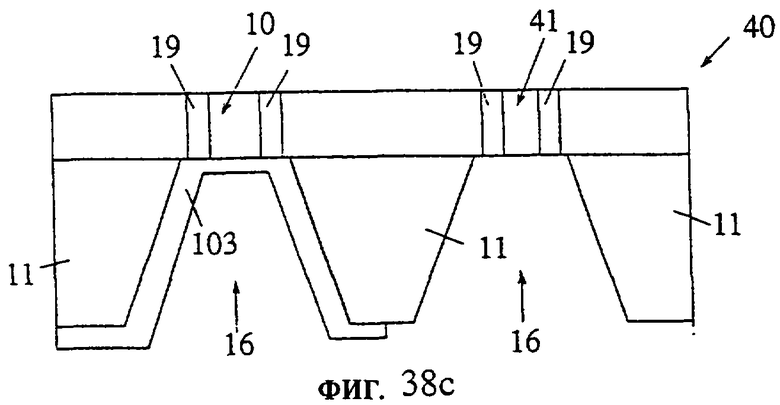

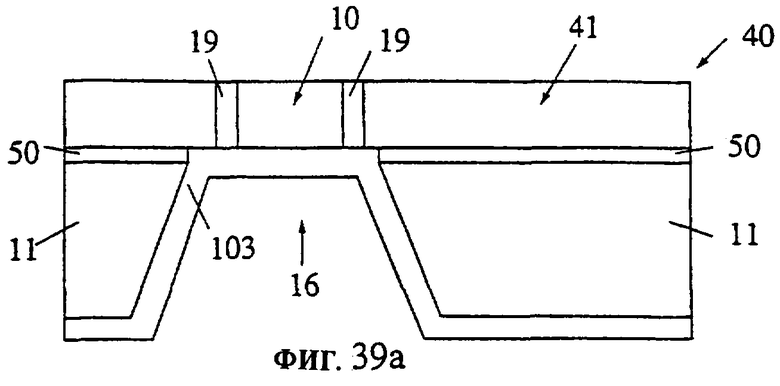

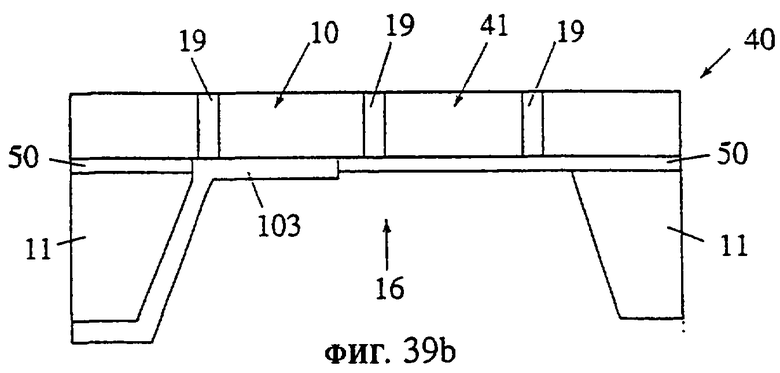

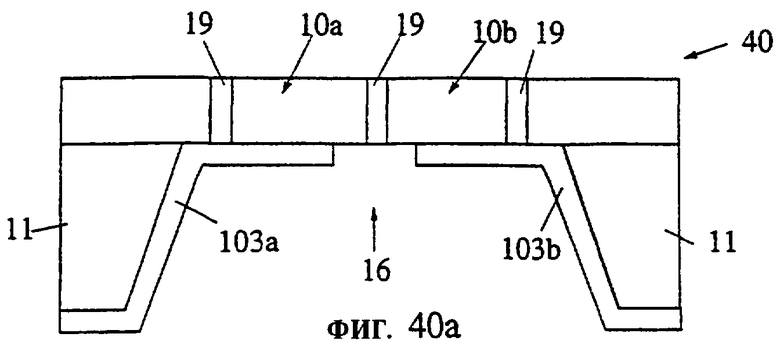

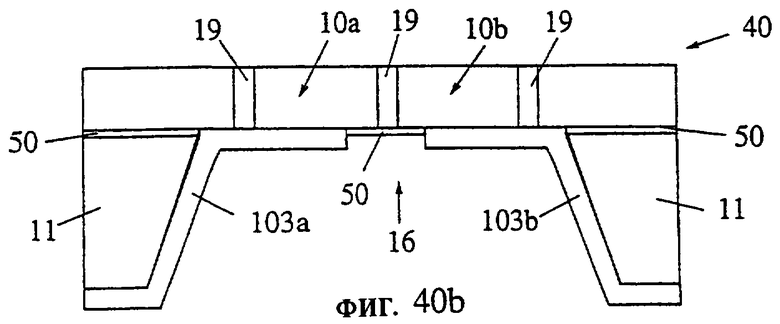

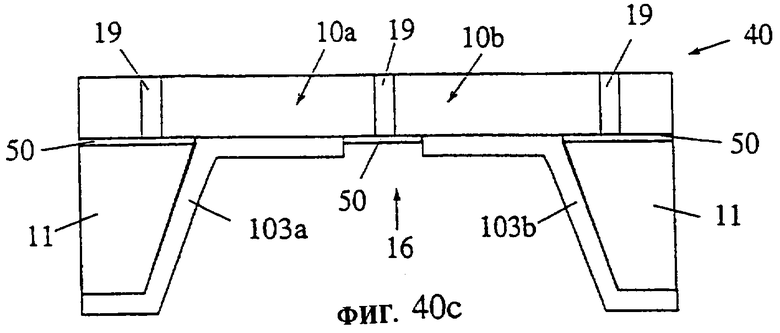

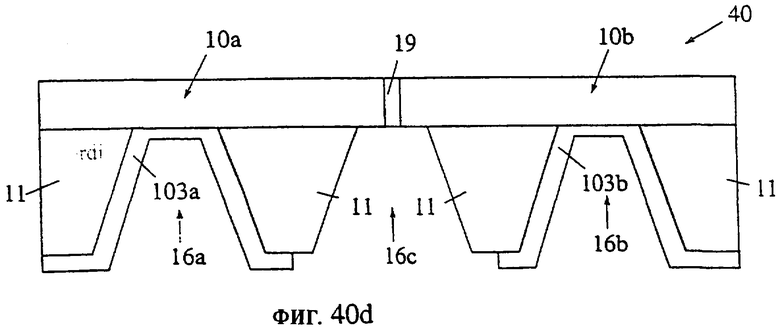

Несколько изолирующих слоев 19 могут использоваться в пределах одной мембраны 16 для разделения множества мощных устройств 10, расположенных в пределах одной мембраны 16, или для отделения биполярных низковольтных устройств или низковольтных устройств CMOS от мощных устройств 10. На фигуре 5а показан пример из четырех таких мощных устройств 10, расположенных в пределах одной мембраны 16, изолированных друг от друга с помощью изолирующих слоев, размещенных в пределах мембраны 16. На фигуре 5b показан вид сверху примера из четырех мощных устройств 10, расположенных на отдельных соответствующих мембранах 16, изолированных друг от друга с использованием изолирующих слоев 19, помещенных за пределами мембраны 16. На фигуре 6а схематично изображен двумерный вид в поперечном сечении мощной интегральной схемы 40, которая содержит одно мембранное мощное устройство 10, и CMOS, а также биполярные устройства 41, расположенные за пределами мембраны 16. В качестве альтернативы, CMOS и биполярные устройства 41 также могут быть расположены на мембране 16 вместе с мощными устройствами 10, как показано на фигуре 6b, или на других мембранах 16, сформированных поверх той же исходной подложки 11, как показано на фигуре 6с. Пример на фигуре 6d отличается от примера по фигуре 6с тем, что изолирующий слой 19 расположен за пределами мембраны 16. Очевидно, что использование мембран 16 и изолирующих слоев 19 позволяет обеспечить очень эффективную электрическую изоляцию между мощными устройствами 10 и маломощными цепями 41, а также между соседними мощными устройствами 10.

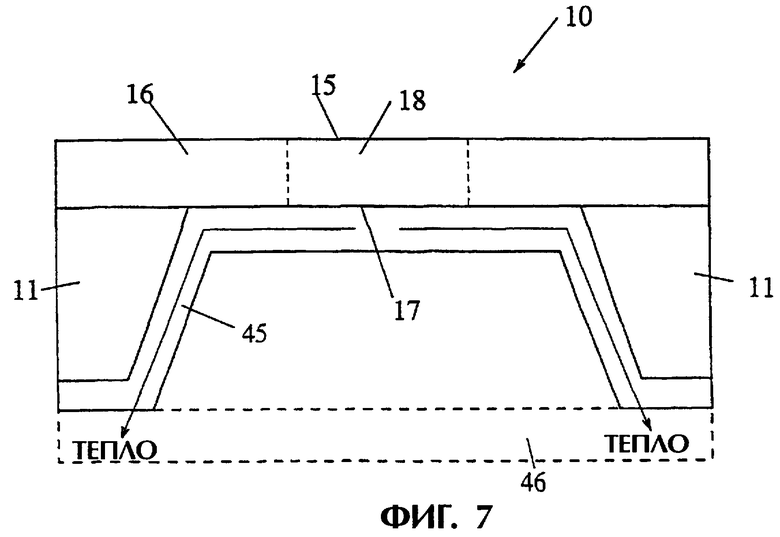

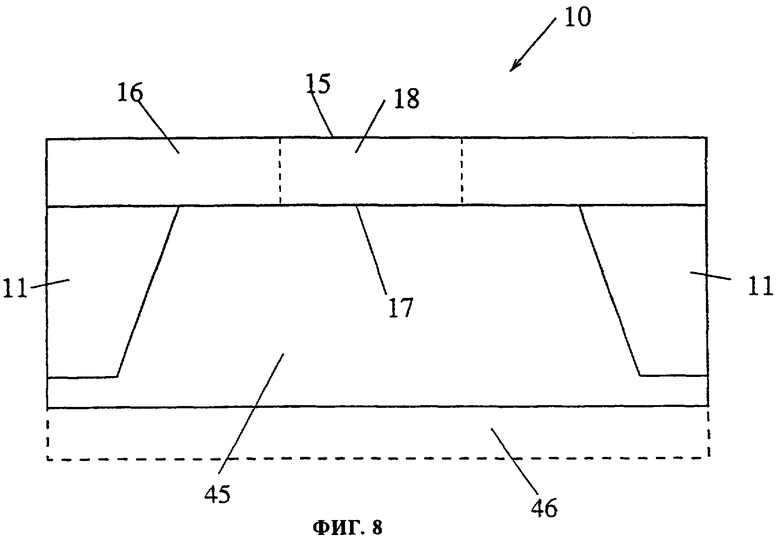

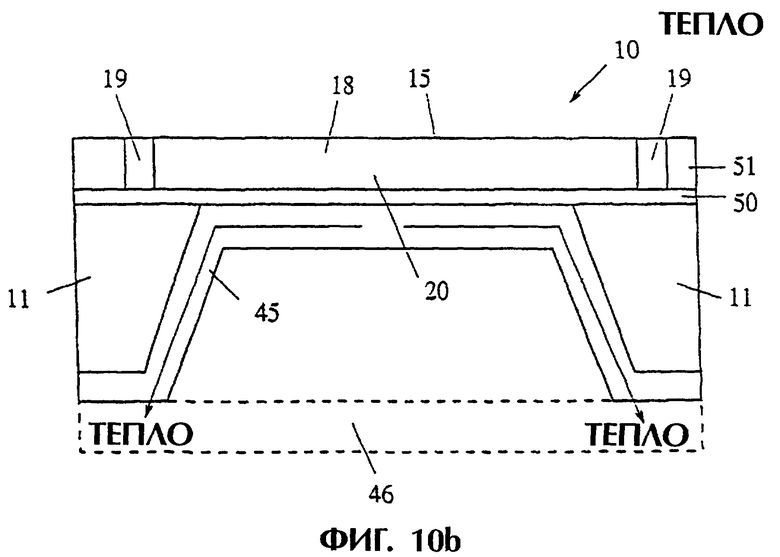

На фигуре 7 все выводы расположены на верхней поверхности 15, в данном примере слой 45, который выполнен электроизолирующим, но который имеет относительно высокую теплопроводность, может быть расположен вблизи к нижней поверхности 17 мембраны 16, что позволяет отводить большую часть тепла, которое в противном случае накапливалось бы внутри мембраны 16 при работе мощного устройства. В предпочтительном варианте воплощения этот слой 45 сформирован после однократного вытравливания нижней стороны полупроводниковой подложки 11 и может быть сформирован путем осаждения на необработанную подложку диэлектрического материала с высокой теплопроводностью. Такие материалы могут быть, например, основаны на алмазе. Также могут использоваться другие материалы, такие как нитрид бора, нитрид алюминия и окисел алюминия. Как показано на фигуре 8, изолирующий слой 45 может заполнять весь зазор в подложке 11, остающейся после формирования мембраны. В любом случае, теплоотвод 46 может находиться в тепловом контакте с изолирующим слоем 45 для отвода тепла.

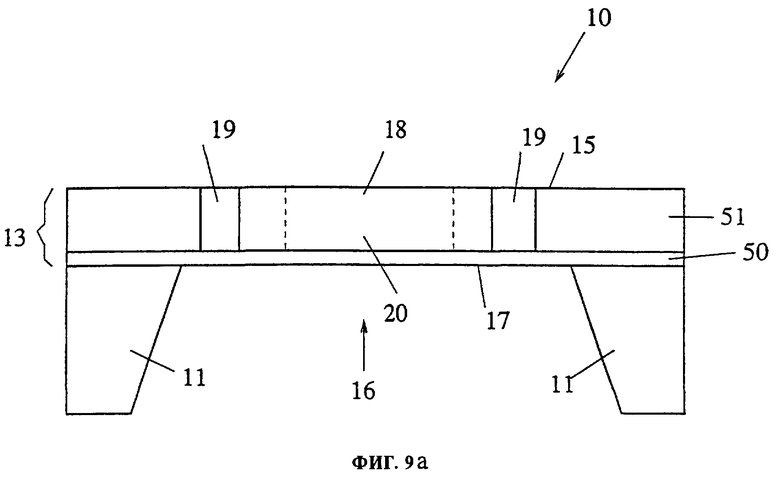

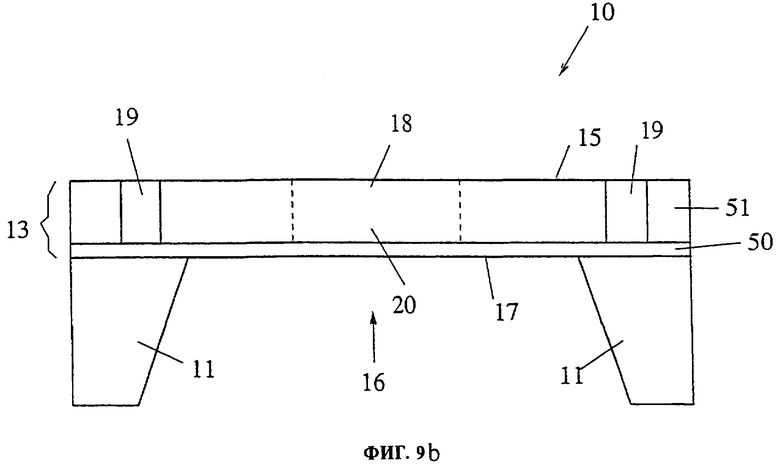

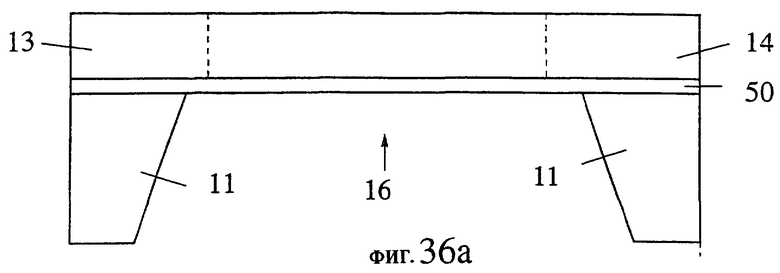

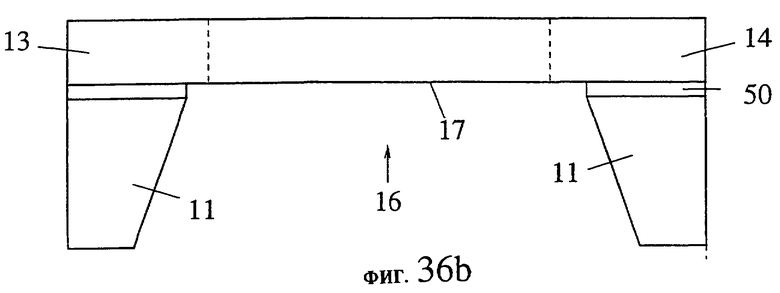

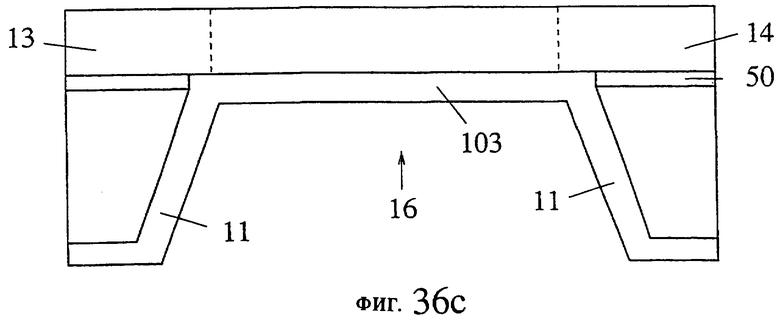

Как показано на фигурах 9а и 9b, первый тонкий слой 13 может содержать тонкий изолирующий слой 50, нижняя сторона которого, по существу, формирует нижнюю поверхность 17 мембраны, и, по меньшей мере, один полупроводниковый слой 51 расположен поверх тонкого изолирующего слоя 50, как например при использовании технологии "кремний на диэлектрике" (КНД) известного уровня техники. В этом случае при производстве мощных интегральных схем может использоваться технология КНД, такая как соединенные слои, SIMOX или Unibond. В качестве альтернативы, может использоваться технология "кремний на алмазе". На одном из последних этапов изготовления высоковольтной КНД структуры и в соответствии с вышеописанными примерами полупроводниковая подложка 11 под заглубленным изолирующим слоем 50 может быть частично удалена с использованием обычного формирования рисунка с однократным вытравливанием с задней стороны. В этом примере заглубленный изолирующий слой 50 действует как эффективный ограничитель вытравливания для мембраны 16. Важно отметить, что основные выводы расположены на верхней поверхности 15 в пределах мембраны 16, заглубленный изолирующий слой 50 также позволяет обеспечить равномерное распределение эквипотенциальных линий внутри слоя 20 дрейфа так, что напряжение пробоя мембранного мощного устройства 10 будет близко к его идеальному значению. В примере, показанном на фигуре 9а, изолирующий слой 19 расположен в пределах мембраны 16. В примере, показанном на фигуре 9b, изолирующий слой 19 расположен за пределами мембраны 16.

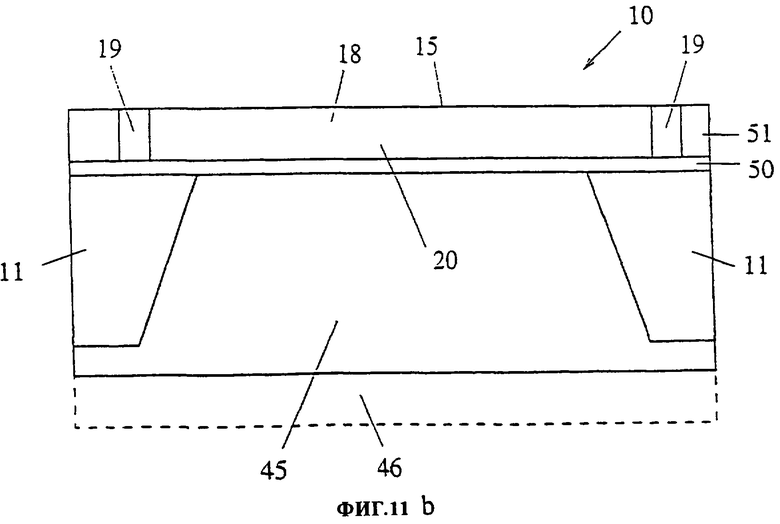

Повторим, что изолирующий слой 45 с относительно высокой теплопроводностью может быть сформирован под мембраной 16, как показано на фигурах 10 и 11, который позволяет отводить тепло в поперечном направлении на подложку 11 и/или непосредственно на внешний теплоотвод 46. В примерах, показанных на фигурах 10a и 11а, изолирующий слой 19 расположен в пределах мембраны 16, в то время как в примерах, показанных на фигурах 10b и 11b, изолирующий слой расположен за пределами мембраны 16.

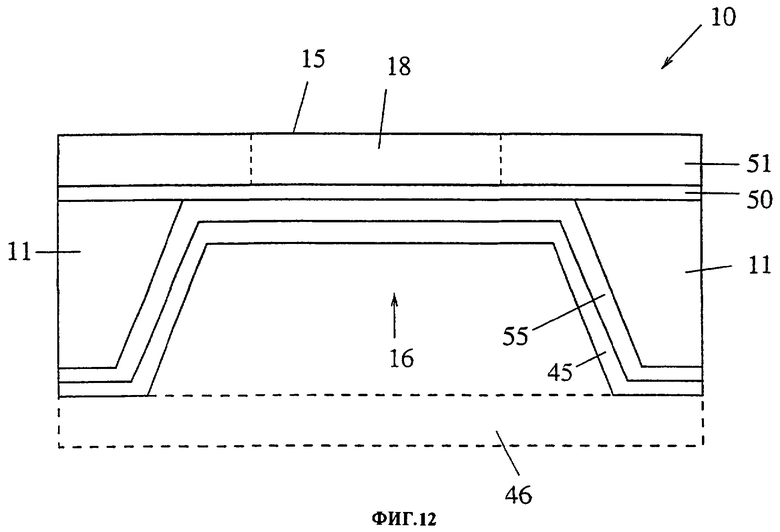

В примере, показанном на фигуре 12, дополнительный электроизолирующий слой 55, который обладает улучшенными механическими свойствами, расположен между заглубленным изолирующим слоем 50 и электроизолирующим, но теплопроводным слоем 45 в области мембраны 16, для усиления структуры мембраны 16 и для минимизации риска механического разрыва мембраны 16. Этот дополнительный изолирующий слой также позволяет скомпенсировать общее механическое напряжение в мембране 16 и также может улучшить сцепление электроизолирующего, но теплопроводного слоя 45 с заглубленным изолирующим слоем 50. Следует понимать, что такой механически прочный слой 55 также может быть размещен под мембраной 16 в любом из других примеров, описанных в данном описании, которые не содержат заглубленный изолирующий слой 50, причем такая компоновка улучшает электрическую пассивацию и/или механические свойства структуры, включая, в частности, сопротивление разрыву. Несколько таких механически прочных изолирующих слоев могут быть нанесены на заднюю сторону мембраны 16 для улучшения рассеивания тепла, электрической пассивации и/или механического упрочнения мембраны 16 и/или для действия в качестве буферных слоев для обеспечения хорошего сцепления между одним слоем и другим. Изолирующие слои 21 и буферный слой могут быть выполнены из нитридов, оксидов, аморфных материалов или поликристаллических материалов.

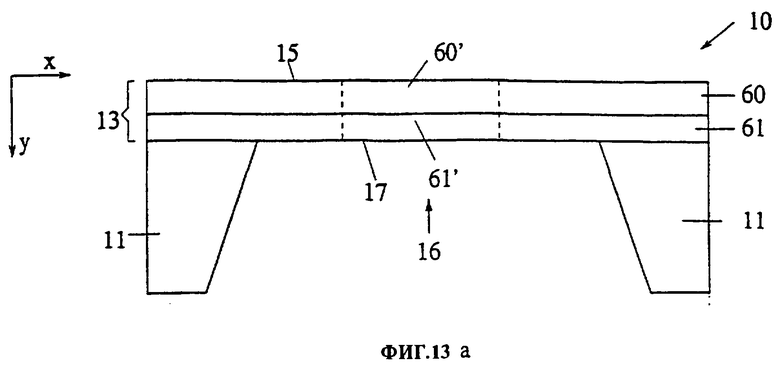

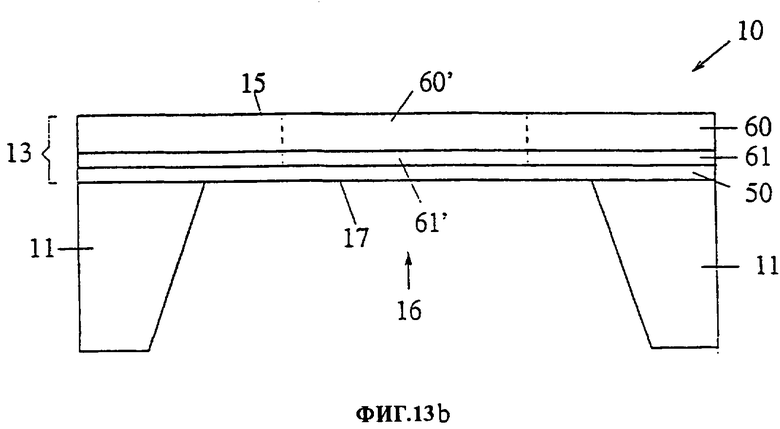

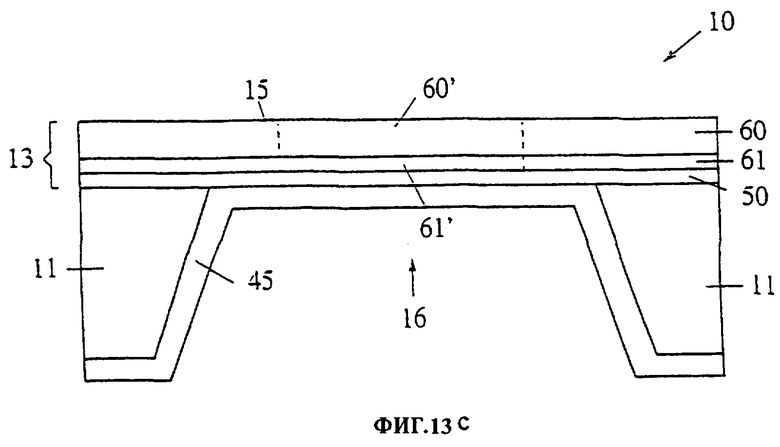

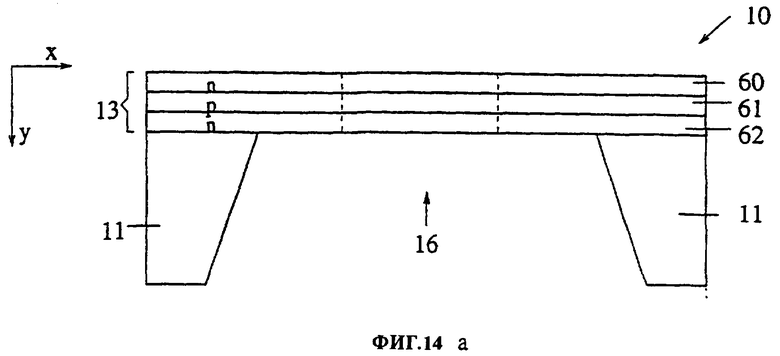

В примерах, показанных на фигурах 13а-13с, когда основные выводы устройства расположены на верхней поверхности 15, в пределах мембраны 16, первый тонкий слой 13 в каждом случае содержит два полупроводниковых слоя 60, 61 противоположного типа проводимости так, что область дрейфа в мощном устройстве 10 теперь состоит из двух полупроводниковых областей 60', 61' противоположного типа проводимости, расположенных друг над другом и находящихся в прямом контакте друг с другом так, что формируется полупроводниковый переход. Наличие этих двух полупроводниковых областей 60', 61' различного типа проводимости, находящихся в прямом контакте друг с другом, позволяет существенно повысить напряжение пробоя устройства. Это происходит, благодаря горизонтальному полупроводниковому переходу, сформированному в вертикальном направлении между полупроводниковыми слоями 60, 61, что позволяет обеспечить обеднение всей области дрейфа при намного меньшем напряжении, чем напряжение пробоя. Это означает, что область дрейфа физически действует как слой с собственной электропроводностью в режиме блокирования напряжения, и эквипотенциальные линии в вертикальном поперечном сечении устройства располагаются перпендикулярно верхней поверхности 15 и нижней поверхности 17 мембраны и более равномерно распределяются вдоль области дрейфа в поперечном направлении. В этих структурах, таким образом, формируется практически равномерное электрическое поле вдоль области дрейфа в поперечном направлении или в направлении х. Если электрическое поле достигает критического значения, происходит лавинный пробой. Поскольку электрическое поле в этот момент распределяется, по существу, равномерно, напряжение пробоя, которое графически представлено областью под кривой электрического поля в направлении х, между основными выводами устройства, будет максимальным. Следует понимать, что концентрация легирования примесями и толщина двух полупроводниковых слоев 60, 61 играют важную роль для достижения максимально возможного напряжения пробоя, и их предпочтительно выбирают такими, чтобы вся область дрейфа была обедненной при относительно низком напряжении по сравнению с номинальным напряжением пробоя. На выбор концентрации легирования примесями и толщины двух полупроводниковых слоев 60, 61 также влияет тип используемого мощного устройства и соответствующий процесс изготовления.

Пример, показанный на фигуре 13b, представляет собой КНД структуру, содержащую изолирующий слой 50 из окисла кремния. Пример, показанный на фигуре 13с, также представляет собой КНД структуру, содержащую изолирующий слой 50 из окисла кремния и электроизолирующий, но теплопроводный слой 45, нанесенный на заднюю сторону изолирующего слоя 50. Следует понимать, что электроизолирующий, но теплопроводный слой может также быть нанесен на нижнюю поверхность 17 мембраны 16 в примере структуры с изоляцией p-n-переходом, показанной на фигуре 13а.

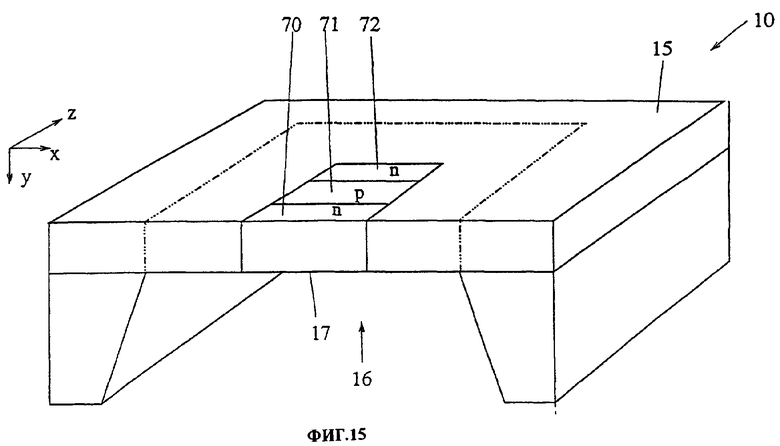

В примерах, показанных на фигурах 14а-14с, которые, в общем, соответствуют примерам, показанным на фигурах 13а-13с, область дрейфа в каждом случае сформирована с помощью нескольких полупроводниковых слоев чередующегося типа проводимости, построенных поверх друг друга, в направлении у так, что вся область дрейфа становится полностью обедненной при относительно низком напряжении по сравнению с номинальным напряжением пробоя. И снова, следует понимать, что в любом из этих примеров электроизолирующий, но теплопроводный слой 45 может быть нанесен на нижнюю поверхность 17 мембраны 16.

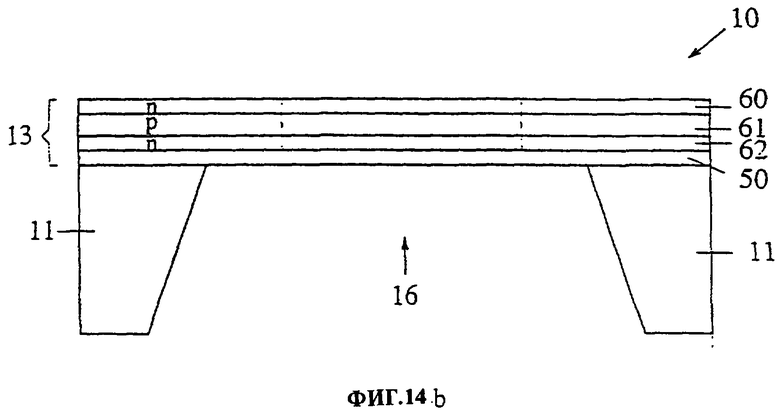

В примере, показанном на фигуре 15, в котором основные выводы снова расположены на верхней поверхности 15 в пределах мембраны 16, область дрейфа мембранного мощного устройства 10 содержит множество расположенных рядом друг с другом слоев 70, 71, 72 чередующегося типа проводимости, сформированных в третьем направлении z. Такие расположенные рядом друг с другом полупроводниковые области в направлении z формируют полупроводниковые переходы, расположенные поперечно в направлении z, так, что вся область дрейфа становится полностью обедненной при относительно низком напряжении по сравнению с номинальным напряжением пробоя. Наличие вертикальных плоскостей переходов в направлении z мембраны 16 обеспечивает равномерное распределение эквипотенциальных линий вдоль области дрейфа в направлении х, что повышает напряжение пробоя до значения, близкого к идеальной величине. Как и в примерах, описанных выше, эквипотенциальные линии в вертикальном поперечном сечении (х, у) устройства располагаются перпендикулярно верхней поверхности 15 и нижней поверхности 17 мембраны и, таким образом, выравниваются по оси у. Степень легирования примесями и толщину располагающихся рядом друг с другом полупроводниковых слоев 70, 71, 72 различного типа проводимости выбирают таким образом, чтобы область дрейфа полностью обеднялась в режиме блокирования напряжения, при относительно низком напряжении по сравнению с номинальным напряжением пробоя, что, таким образом, повышает напряжение пробоя до величины, близкой к идеальному значению. Следует понимать, что, хотя в направлении z показаны три полупроводниковых слоя 70, 71, 72, может использоваться только два слоя или больше трех слоев. Кроме того, следует понимать, что электроизолирующий, но теплопроводный слой может быть нанесен на нижнюю поверхность 17 мембраны 16 для отвода тепла от устройства 10.

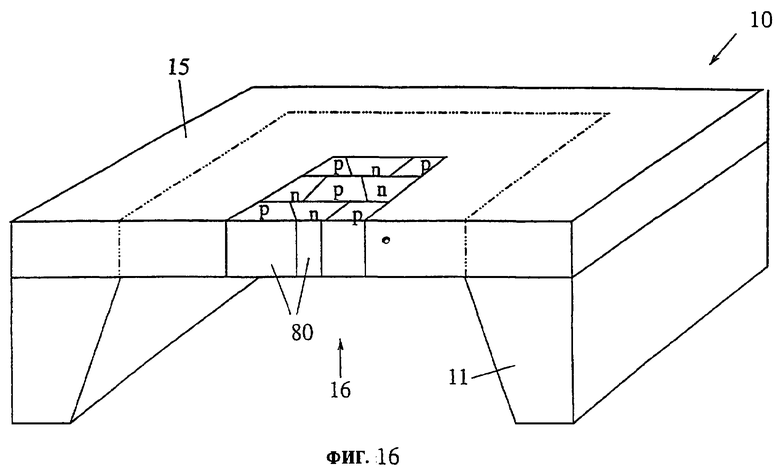

В примере, показанном в фигуре 16, область дрейфа сформирована из множества ячеек 80 различного типа проводимости, расположенных с чередованием по отношению друг к другу для формирования на верхней поверхности 15 и в плоскости х, z правильной структуры так, что снова вся область дрейфа становится полностью обедненной в режиме блокирования напряжения так, что потенциал равномерно распределяется по области дрейфа. Ячейки различного типа проводимости могут быть сформированы в виде правильной структуры или в виде беспорядочной структуры (не показана) в плоскости х, у.

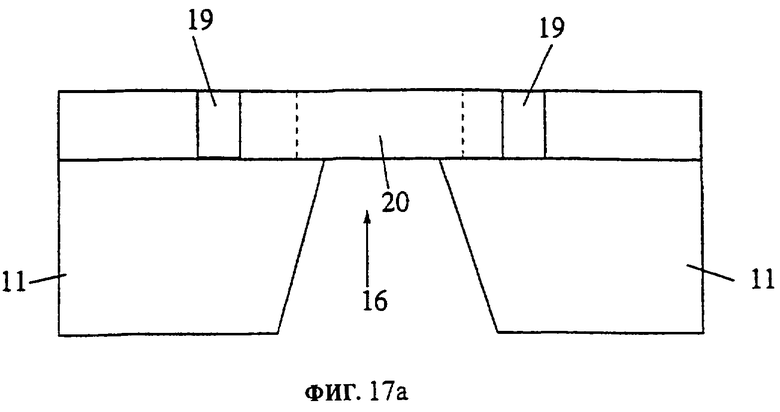

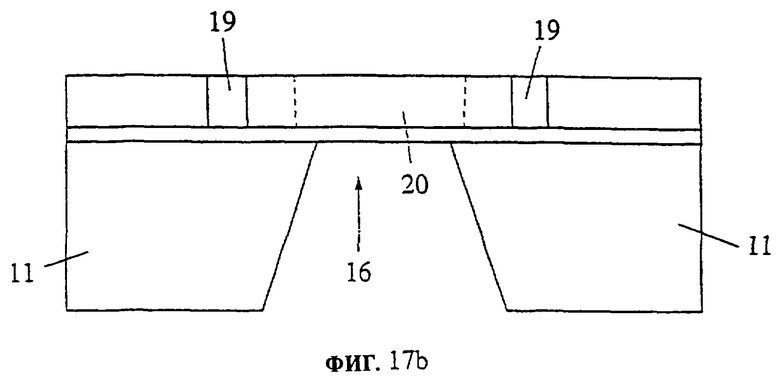

В примерах, показанных на фигурах 17а-17с (на которых, соответственно, изображено устройство с изоляцией p-n-переходом, устройство с КНД структурой, и устройство с КНД структурой, включающее электроизолирующий, но теплопроводный слой 45, нанесенный на заднюю сторону мембраны 16), подложка 11 удалена таким образом, что только часть области 20 дрейфа расположена в пределах мембраны 16. При этом часть области 20 дрейфа остается за пределами мембраны 16 (и поэтому располагается над остающимися частями подложки 11). Основные выводы располагаются на верхней поверхности 15, но предпочтительно высоковольтный контактный край области 20 дрейфа расположен в пределах мембраны 16, в то время как низковольтный контактный край области 20 дрейфа может оставаться за пределами мембраны 16. И снова, следует понимать, что электроизолирующий, но теплопроводный слой 45 может быть нанесен на нижнюю поверхность 17 мембраны 16 в любом из этих примеров.

Во всех примерах, описанных выше и представленных на фигурах 2-17, стенки подложки 11 расположены под углом к плоскости х, z устройства с поперечным протеканием тока. Это происходит из-за того, что наиболее часто используется жидкостное анизотропное вытравливание задней стороны, которое обычно выполняется с использованием раствора КОН. Кремниевая подложка 11 представляет собой монокристалл, и скорость вытравливания анизотропных травильных растворов зависит от ориентации кристалла. Плоскости ограничения травления обычно представляют собой (111) плоскости. Устройства типа КНД структуры, которые содержат заглубленный оксидный слой, имеют преимущество, состоящее в том, что вытравливание задней стороны автоматически прекращается при достижении заглубленного оксидного слоя, поскольку вытравливание окиси для многих травильных растворов (включая КОН) происходит намного медленнее, чем вытравливание кремния. В качестве альтернативы для устройств, сформированных в массиве кремния (то есть для устройств, в которых не используется КНД структура), вытравливание задней стороны может контролироваться по времени или электрохимическим способом.

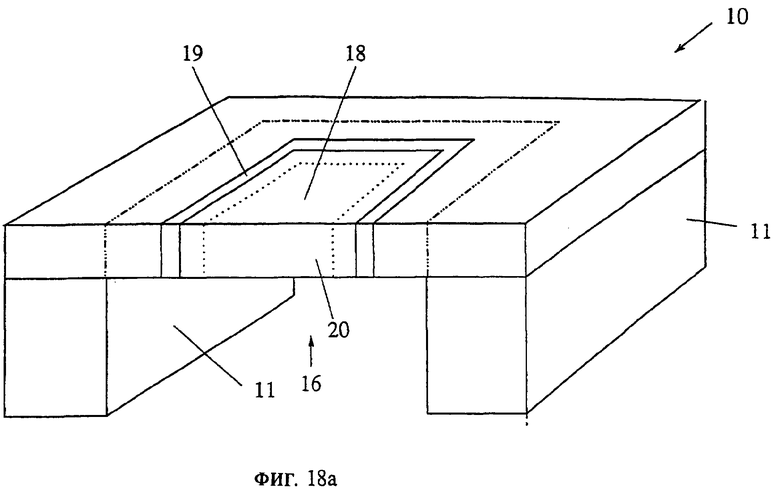

Вместо жидкостного анизотропного вытравливания может использоваться сухое вытравливание задней стороны для получения любого из мембранных мощных устройств, в соответствии с настоящим изобретением. Сухое вытравливание задней стороны имеет преимущество, состоящее в том, что при этом стенки подложки 11 получаются вертикальными, как показано на примере, представленном на фигурах 18 и 18b. Это означает, что объем, занимаемый зазором в подложке 11 ниже мембраны 16, больше не будет зависеть от толщины подложки 11, и, таким образом, более просто может быть получено множество мембран 16 с уменьшенным поперечным промежутком между ними в одном кристалле или интегральной схеме. В примере, показанном на фигуре 18а, изолирующий слой 19 расположен в пределах мембраны 16, в то время как в примере, показанном на фигуре 18b, изолирующий слой 19 расположен за пределами мембраны 16.

В примере, показанном на фигуре 19, мембрана 16 сформирована способом вытравливания передней стороны (то есть микромеханической обработки поверхности) подложки 11. В представленном примере подложка 11 частично удалена под активной областью 18 устройства 10 так, что в подложке 11 остается зазор под активной структурой 18, который позволяет повысить возможности устройства противостоять напряжению пробоя. На фигуре 20 показан вид в поперечном сечении примера, изображенного на фигуре 19. На фигуре 21 показан вариант КНД структуры для примера, показанного на фигурах 19 и 20. Поскольку во всех примерах, описанных выше, наличие зазора в подложке 11 под активной областью 18 (то есть формирование мембраны 16) означает, что эквипотенциальные линии в области 20 дрейфа располагаются перпендикулярно как к верхней поверхности 15 устройства, так и к нижней поверхности 7 мембраны и, по существу, равномерно распределяются внутри области 20 дрейфа так, что напряжение пробоя приближается к его идеальному пределу.

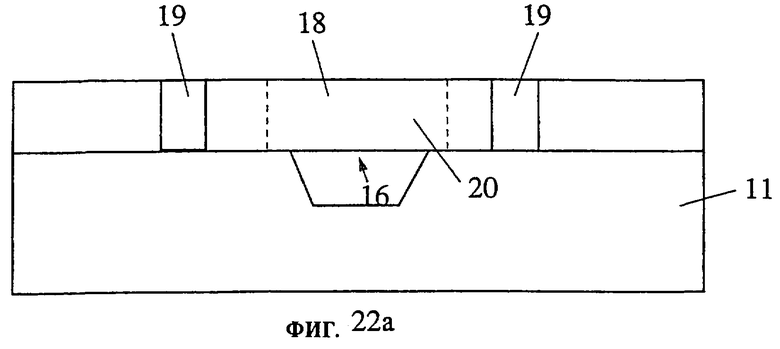

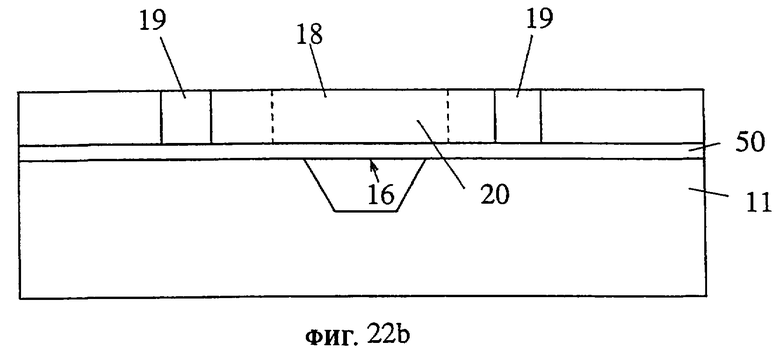

В примерах, показанных на фигурах 22а и 22b, на которых изображены соответственно варианты с использованием изоляции p-n-переходом и КНД структуры, зазор в подложке 11 сформирован только частично под областью 20 дрейфа так, что только часть области 20 дрейфа сформирована в мембране 16. И снова, основные выводы расположены на верхней поверхности 15, но предпочтительно контактный край высокого напряжения области 20 дрейфа расположен в пределах мембраны 16, в то время как контактный край низкого напряжения может располагаться за пределами мембраны 16.

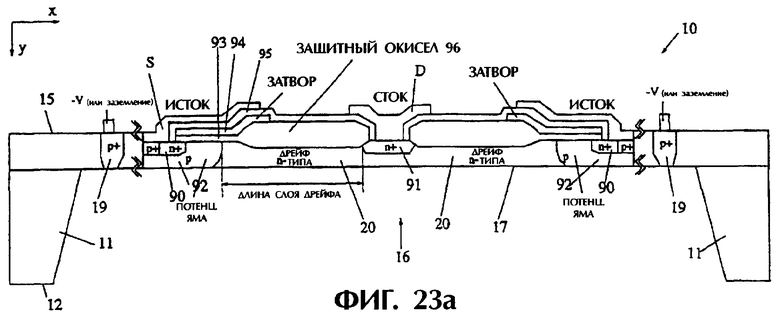

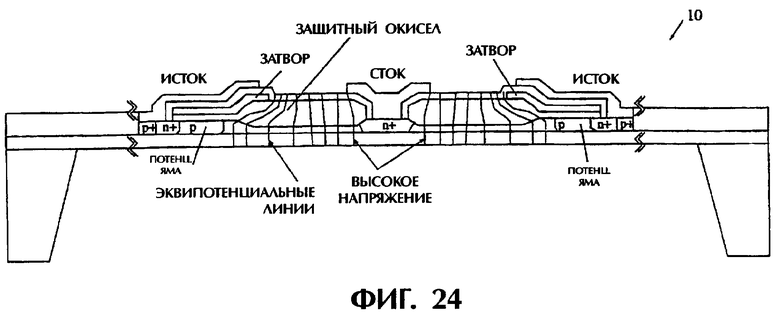

На фигуре 23а подробно показан пример мембранного высоковольтного DMOSFET (LDMOSFET) 10 с поперечным протеканием тока в соответствии с настоящим изобретением, в котором область 20 дрейфа имеет n тип проводимости, область 90 истока и область 91 стока представляют собой области n типа проводимости и очень хорошо легированы донорными примесями для формирования хорошего омического контакта, и потенциальная яма 92 имеет р тип проводимости. Обычный изолированный затвор, сформированный тонким изолирующим слоем 93 и слоем 94 из поликристаллического кремния и/или металла, расположен над потенциальной ямой 92 и изолирован от металлического слоя S истока изолирующим слоем 95. Более толстый изолирующий слой 96, обозначенный на чертеже как защитный слой окисла, может присутствовать поверх слоя 20 дрейфа между изолированным затвором и областью стока. Слой 94 из поликристаллического кремния/металла может проходить на короткое расстояние поверх защитного окисла 96. В открытом состоянии ток протекает между выводом D стока, который контактирует с n+ областью 91 стока, и выводом истока, который контактирует с n+ областью 90 истока. Этот ток управляется потенциалом, прикладываемым к выводу G затвора, который находится в контакте с изолированным затвором. Когда к выводу затвора приложен более высокий потенциал по отношению к выводу истока, на поверхности потенциальной ямы 92 формируется канал электронов под изолированным затвором, который позволяет протекать потоку электронов из области истока через канал, через область 20 дрейфа к стоку. Устройство может быть открыто и закрыто при приложении соответствующего потенциала на вывод затвора. Высоковольтная структура LDMOSFET расположена на мембране 16, определяемой верхней поверхностью 15 и нижней поверхностью 17 мембраны. Нижняя поверхность 17 мембраны расположена в направлении поперечного сечения между верхней поверхностью 15 и поверхностью 12 полупроводниковой подложки. Мембрана 16, таким образом, выполнена тонкой по сравнению с полупроводниковой подложкой 11 так, что, когда устройство работает в режиме блокирования напряжения, область 20 дрейфа становится полностью обедненной в отношении подвижных носителей заряда, и эквипотенциальные линии располагаются практически перпендикулярно по отношению к верхней поверхности 15 и нижней поверхности 17 мембраны, как показано на фигуре 24. Это отличается от структуры LDMOSFET с изоляцией p-n-переходом известного уровня техники, в которой область дрейфа обычно располагают поверх толстой полупроводниковой подложки, которая в закрытом состоянии является не полностью обедненной, и поэтому эквипотенциальные линии изгибаются от исходного вертикального направления в области дрейфа так, что они выравниваются по отношению к горизонтальному направлению (оси X) в подложке. Преимущество высоковольтного мембранного LDMOSFET состоит в способности противостоять более высокому напряжению пробоя, в более равномерном распределении эквипотенциальных линий на поверхности и в обеспечении лучшей изоляции, благодаря использованию вертикального изолирующего слоя 19 в мембране 16. В данном примере изолирующий слой 19 изготовлен из р+ слоя с высокой степенью легирования примесями и соединен с выводом истока. Следует понимать, что устройство, показанное на фигуре 23а, обычно может содержать несколько полосок/элементов/ячеек так, чтобы такое устройство соответствовало техническим требованиям по уровню тока и мощности. Для устройства, рассчитанного на 600 В, концентрация легирования в области дрейфа обычно может составлять 1016/см3, толщина области 20 дрейфа составляет от 0,2 до 20 мкм, и длина области дрейфа составляет 30-50 мкм. Степень легирования примесями области 20 дрейфа не обязательно должна быть постоянной, и может изменяться от края истока до края стока. Например, на краю истока степень легирования примесями может составлять 8×1015/см3 при линейном увеличении до величины 3×1016/см3 на краю стока.

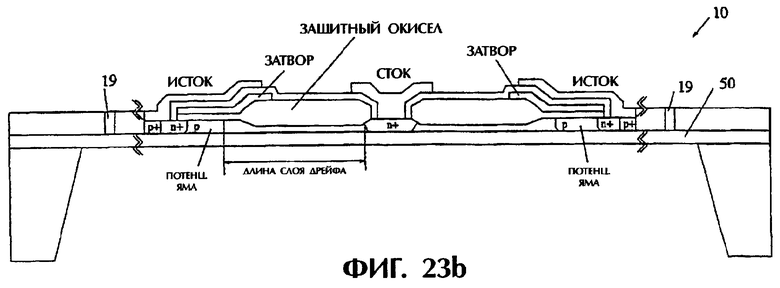

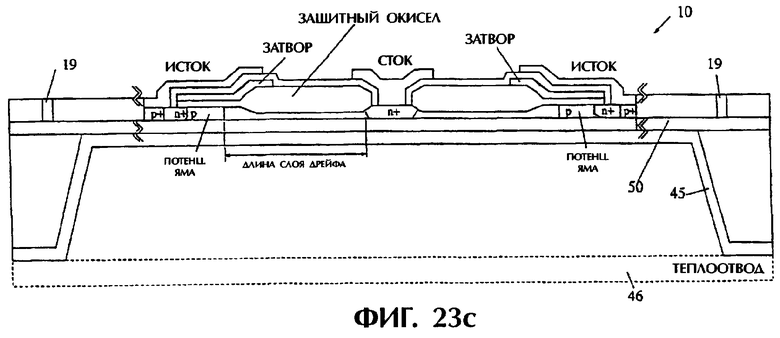

На фигуре 23b показан вариант с использованием КНД структуры для примера, представленного на фигуре 23а, в котором изолирующий слой 50 расположен снизу области 20 дрейфа, которая составляет часть мембраны 16. Этот изолирующий слой 50 не обязательно должен быть толстым, как в случае высоковольтных устройств с использованием КНД структуры известного уровня техники, но вместо этого может быть выполнен очень тонким, поскольку потенциал в режиме блокирования напряжения (когда устройство закрыто), не сосредотачивается на нем в направлении у (как в случае использования обычных высоковольтных устройств с КНД структурой), но вместо этого проходит вдоль него, в направлении х. Изоляция в этом случае выполнена с использованием оксидных канавок 19, но могут использоваться также другие типы изоляции, такие как р+ слой. На фигуре 23с показан вариант примера, представленного на фигуре 23b, в котором электроизолирующий слой 45 с хорошей теплопроводностью расположен под мембраной для облегчения отвода тепла к теплоотводу 46, который, таким образом, устраняет избыточный нагрев. В этом примере изолирующий слой 19 расположен за пределами мембраны 16.

И снова следует понимать, что электроизолирующий, но теплопроводный слой 45 может быть нанесен на нижнюю поверхность 17 мембраны 16 в любом из приведенных примеров.

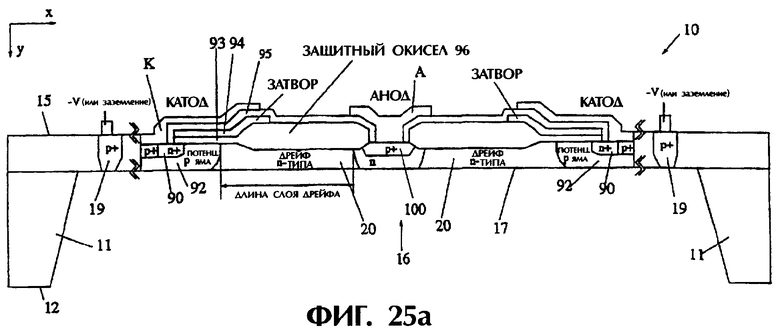

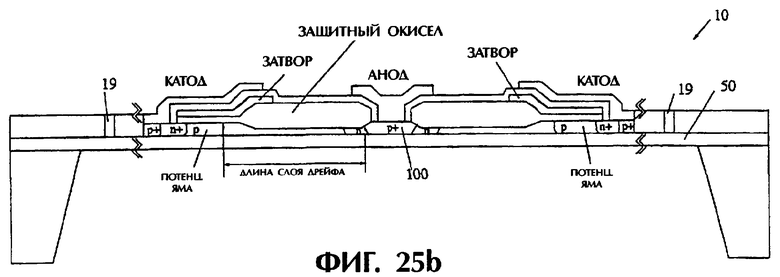

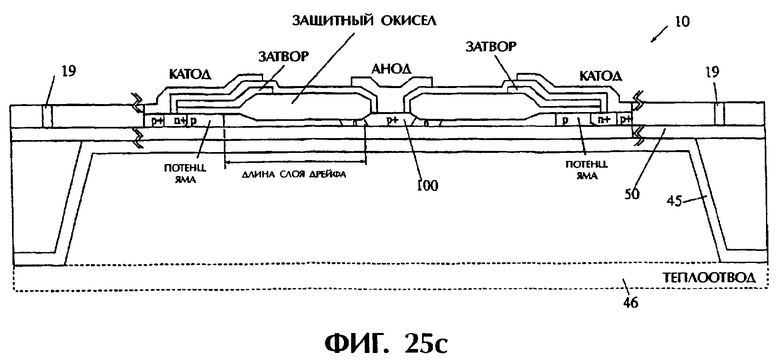

На фигурах 25а - 25с подробно представлены примеры мембранных мощных устройств, построенных на биполярных транзисторах с изолированным затвором со структурой с поперечным протеканием тока (LIGBT), в которых используется биполярная проводимость тока в области 20 дрейфа, подвешенной на мембране 16, и которые, в общем, соответствуют структурам LDMOSFET, показанным на фигурах 23а-23с. Основное отличие между мембранными мощными устройствами LIGBT и мощными устройствами LDMOSFET, показанными на фигурах 23а - 23с, состоит в использовании на аноде дырочного инжектирующего слоя 100 с высокой степенью легирования примесями. Биполярная проводимость устройств типа LIGBT отличается модуляцией проводимости в области дрейфа для снижения сопротивления в открытом состоянии. И снова понятно, что электроизолирующий, но теплопроводный слой 45 может быть нанесен на нижнюю поверхность 17 мембраны 16 в любом из этих примеров.

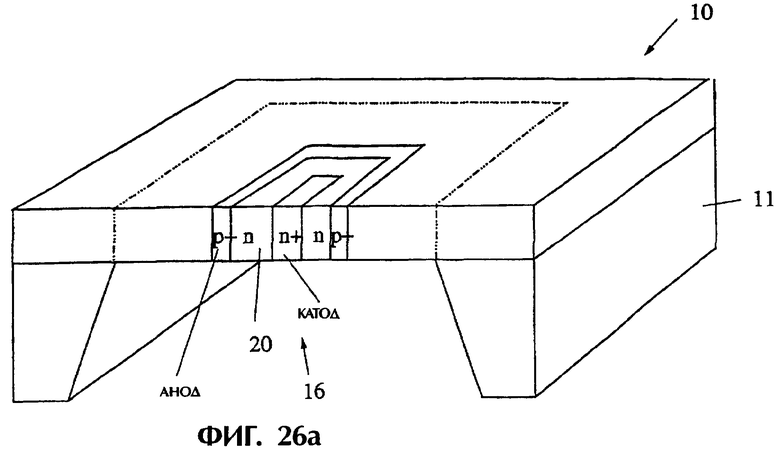

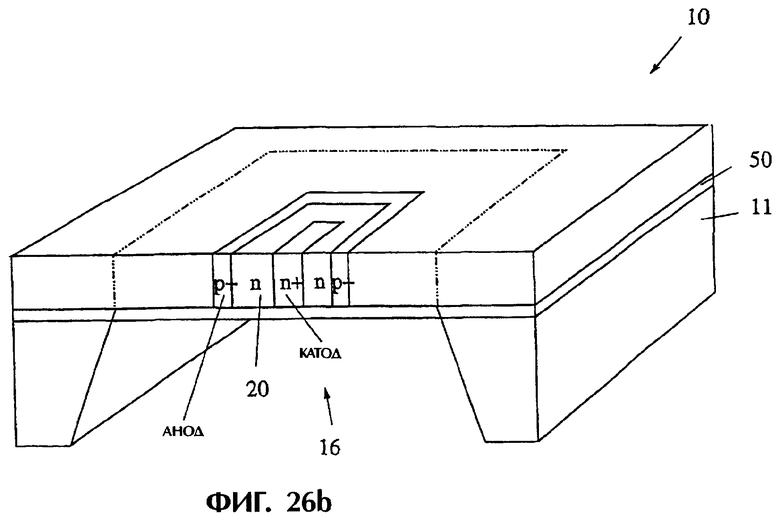

На фигуре 26а схематично показан вид в перспективе примера мембранного устройства, выполненного в виде мощного диода. Для мощного диода, рассчитанного на напряжение 600 В, концентрацию легирования примесями n области 20 дрейфа выбирают в диапазоне от 3×1015/см3 до 1016/см3 и длину от 30 до 50 мкм. Толщина области 20 дрейфа может составлять от 0,2 мкм до 20 мкм. Степень легирования области 20 дрейфа не обязательно должна быть постоянной и может изменяться от края истока до края стока. Например, на краю истока степень легирования примесями может составлять 8×1015/см3 при линейном повышении до величины 3×1016/см3 на краю стока. Для простоты на чертеже показана только одна ячейка диода. На фигуре 26b схематично показана версия с КНД структурой мощного диода, изображенного на фигуре 26а, в которой изолирующий слой 50 сформирован под областью 20 дрейфа, что обеспечивает более равномерное распределение эквипотенциальных линий в области 20 дрейфа и, таким образом, повышает способность диода противостоять напряжению пробоя. Кроме того, изолирующий слой 50 действует как очень хороший ограничитель вытравливания и, следовательно, облегчает формирование мембраны 16. Для облегчения отвода тепла при работе мощного устройства в высокой степени теплопроводный, но электроизолирующий слой 45 (не показан) также может быть расположен на задней стороне мембраны 16 устройств, показанных на фигурах 26а и 26b. Этот слой 45 может быть сформирован путем напыления или с использованием других способов нанесения на одном из последних этапов обработки при изготовлении мощной интегральной схемы, как описано выше.

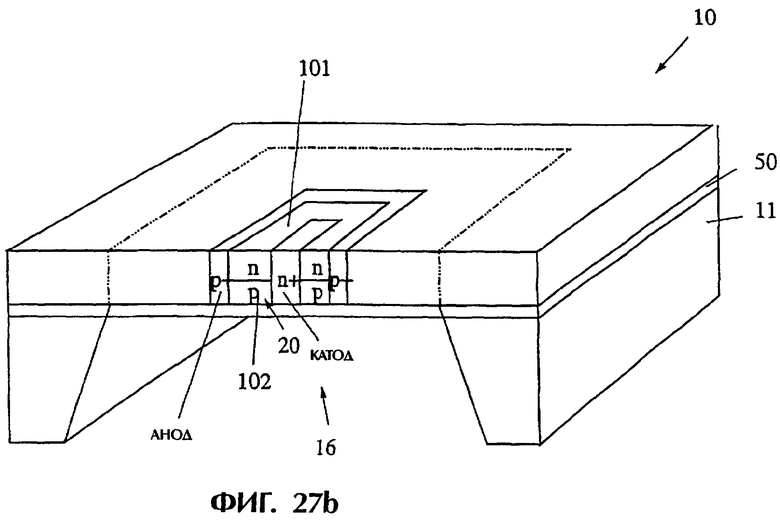

На фигуре 27а схематично показан пример мембранного мощного диода, который содержит область 20 дрейфа, сформированную двумя слоями 100, 101 различного типа проводимости n, р, расположенных вертикально друг над другом. Эти слои 100, 101 могут быть сформированы с помощью эпитаксиального выращивания или, предпочтительно, способом имплантации одного слоя 101 в другом слое 102. Для мощного диода, рассчитанного на напряжение 600 В, концентрация легирования примесями двух полупроводниковых слоев 101, 102, сформированных в области 20 дрейфа, может составлять от 1016/см3 до 5×1016/см3 при длине 30-40 мкм. Толщина двух полупроводниковых слоев 101, 102 составляет от 0,1 мкм до 20 мкм. Если верхний полупроводниковый слой 101 сформирован с помощью имплантации, то концентрация легирования примесями верхнего слоя 101 будет более высокой, чем у нижнего полупроводникового слоя 102, и, следовательно, для поддержания пространственного равновесия заряда, при обеднении слоя области 20 дрейфа 20, толщина верхнего слоя 101, предпочтительно, должна быть меньше, чем у нижнего слоя 102. На фигуре 27b схематично показана версия с использованием КНД структуры мощного диода, представленного на фигуре 27а, в которой изолирующий слой 50 сформирован под областью 101, 102 дрейфа. Дополнительный в высокой степени теплопроводный, но электроизолирующий слой 45 (не показан) также может быть расположен под мембраной для облегчения отвода тепла, как описано выше.

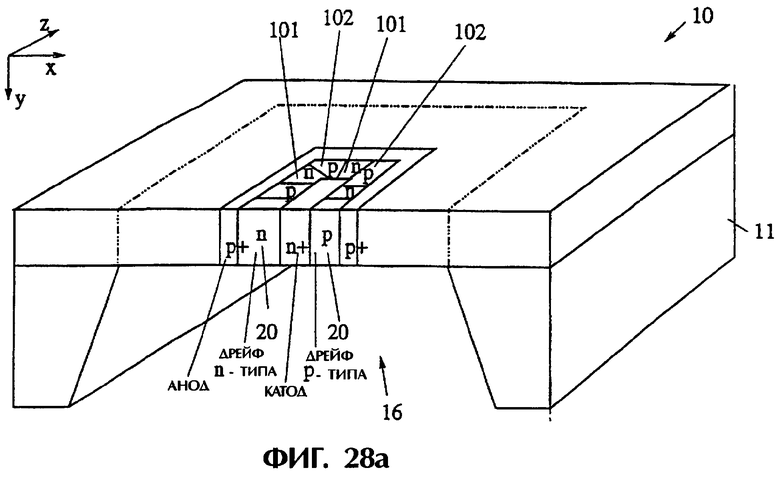

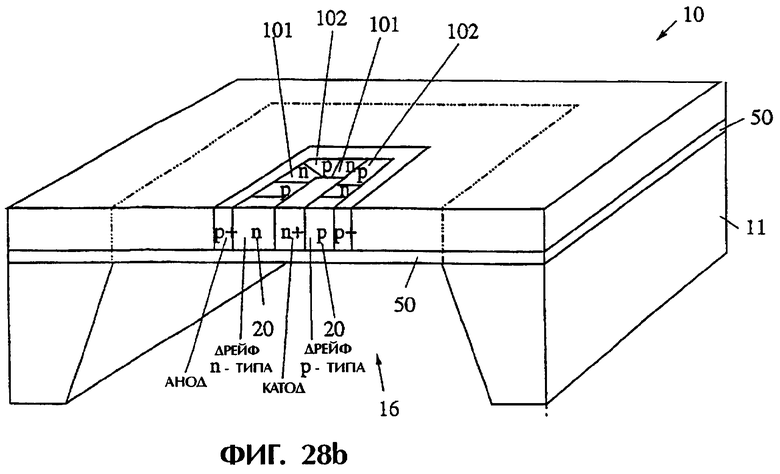

На фигуре 28а схематично показан пример трехмерного мембранного мощного диода. Область дрейфа трехмерного мощного диода состоит из нескольких пар n, p областей 110, 111, расположенных в плоскости х, z так, что они формируют поперечные полупроводниковые переходы в направлении z. Ширина этих n, р слоев 110, 111 обычно может составлять от 0,2 мкм до 5 мкм, что составляет небольшую часть их обычной длины. Это обеспечивает то, что область 20 дрейфа будет обедняться быстрее в направлении z, чем в направлении х, и, таким образом, будет вести себя аналогично слою с собственной электропроводностью в режиме блокирования напряжения. Для устройства, рассчитанного на работу с напряжением 600 В, длина областей 20 дрейфа (в направлении х) приблизительно может составлять 30 мкм. Степень легирования примесями n, р областей 110, 111 может составлять от 1015 /см3 до 6×1016 /см3. Предпочтительно, n, р области 110, 111 сформированы путем имплантации одного слоя (например, n слоя) 110 в другой слой (например, в р слой) 14. Следовательно, концентрация легирования примесями имплантированного слоя 110 будет выше, чем у фонового слоя 111, и, следовательно, для поддержания равновесия зарядов ширина имплантированного слоя 110, предпочтительно, должна быть меньше, чем у фонового слоя 111. На фигуре 28b схематично показан вариант с использованием КНД структуры примера, представленного на фигуре 28а. И снова, в каждом случае, электроизолирующий, но теплопроводный слой 45 (не показан) может быть нанесен для отвода тепла.

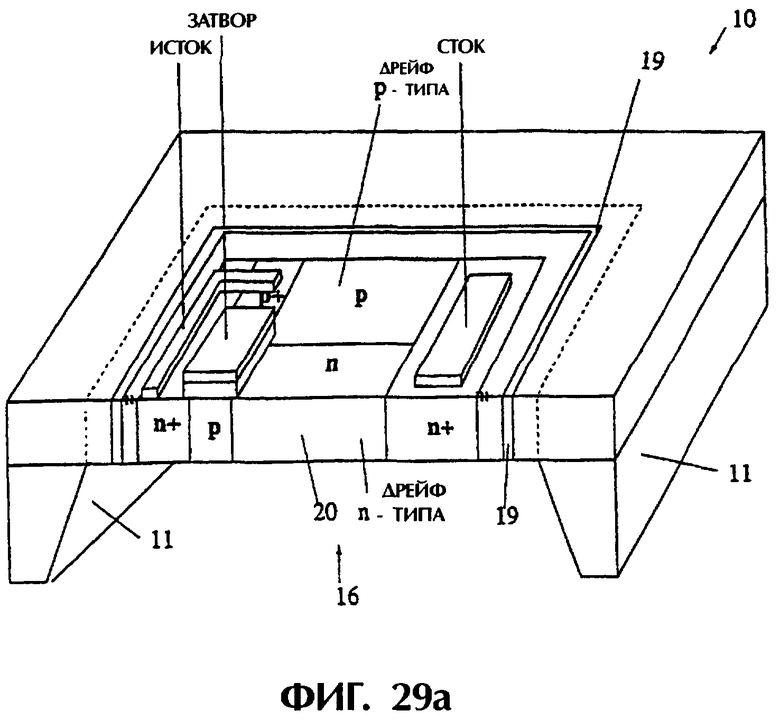

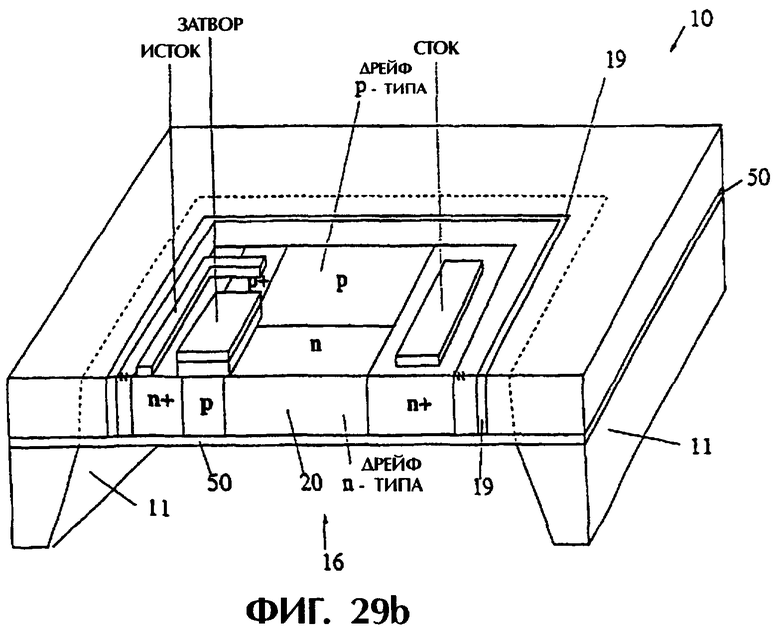

На фигуре 29а схематично показан пример мембранной трехмерной LDMOSFET структуры с одним затвором. В этом устройстве используется концепция, описанная выше, для трехмерного мембранного мощного диода, для поддержания очень высокого напряжения выводами истока и стока в режиме блокирования напряжения, в то время как в режиме электропроводности устройство аналогично обычному LDMOSFET и устройству, представленному на фигуре 23а. На фигуре 29b схематично показан вариант с использованием КНД структуры для примера, изображенного на фигуре 28а. И снова, в каждом случае, электроизолирующий, но теплопроводный слой 45 (не показан) может быть нанесен для отвода тепла.

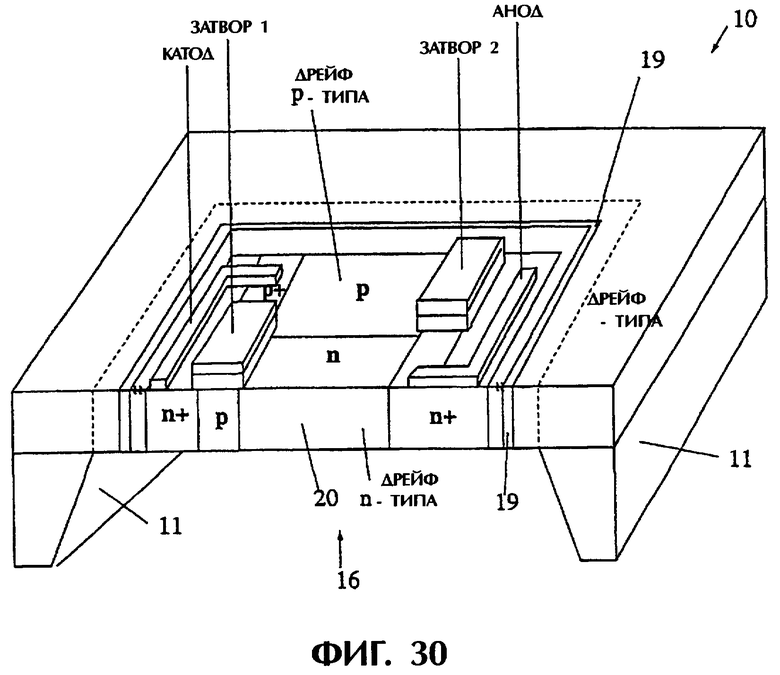

На фигуре 30 схематично показан пример мембранного трехмерного LDMOSFET с двойным затвором. В этом устройстве снова используется концепция, описанная выше, для трехмерного мембранного мощного диода, для поддержания очень высокого напряжения между выводами истока и стока. В режиме электропроводности устройство управляется с помощью затвора как n-канала, так и затвора р-канала, так что может быть обеспечена униполярная параллельная электропроводимость через n и p полоски. Биполярная электропроводимость также может происходить при инжекции электронов в р слой дрейфа и дырок в n слой дрейфа.

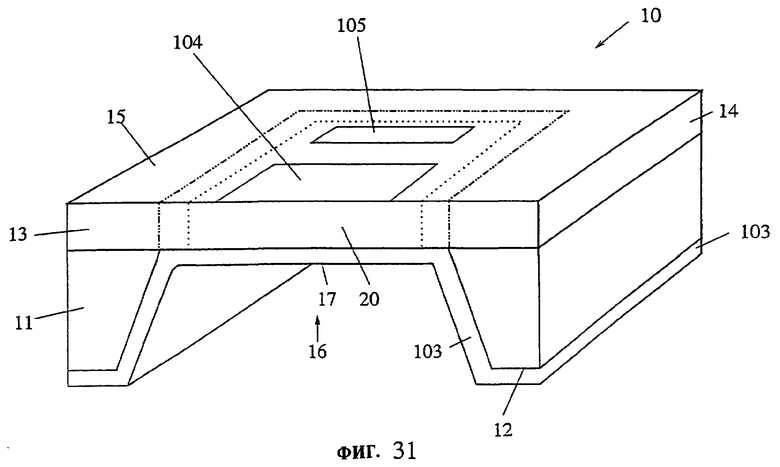

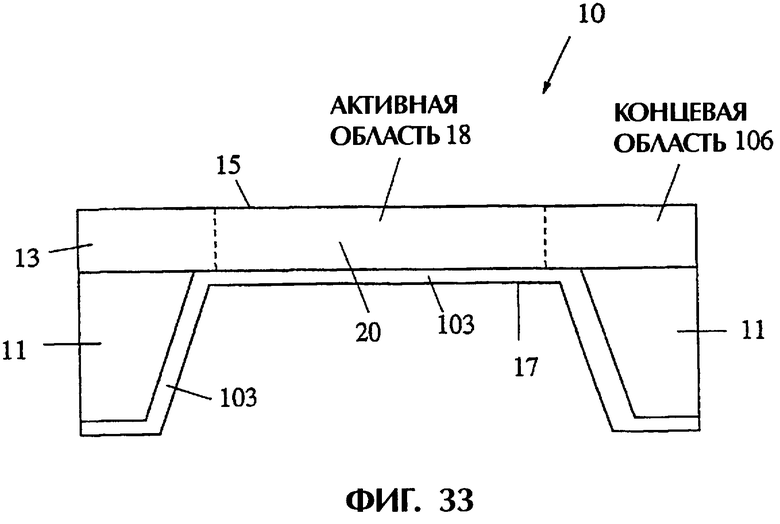

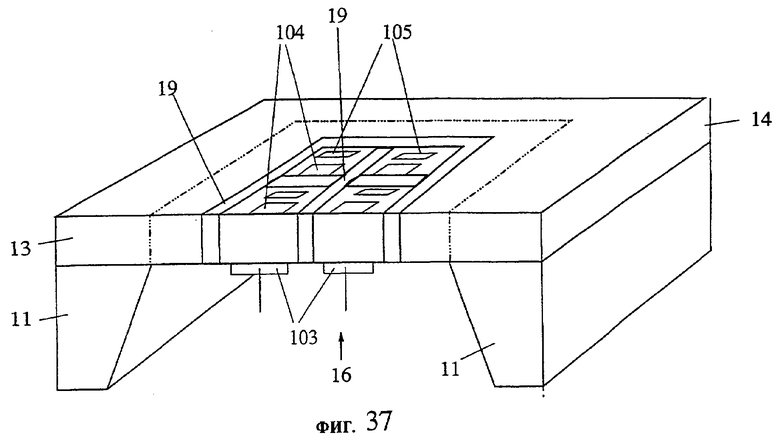

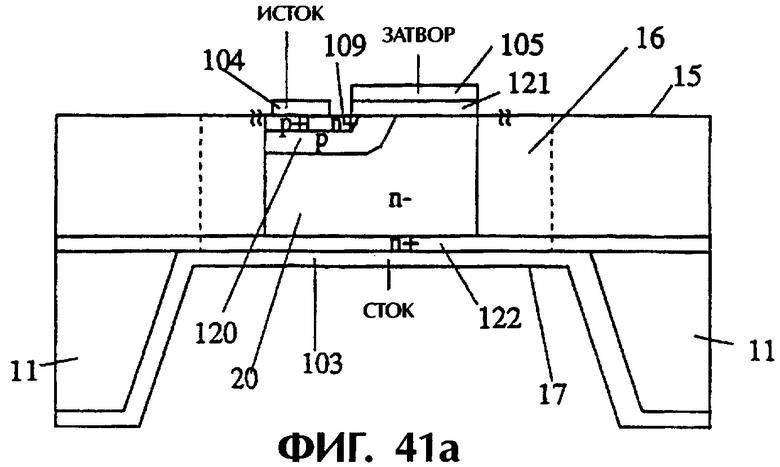

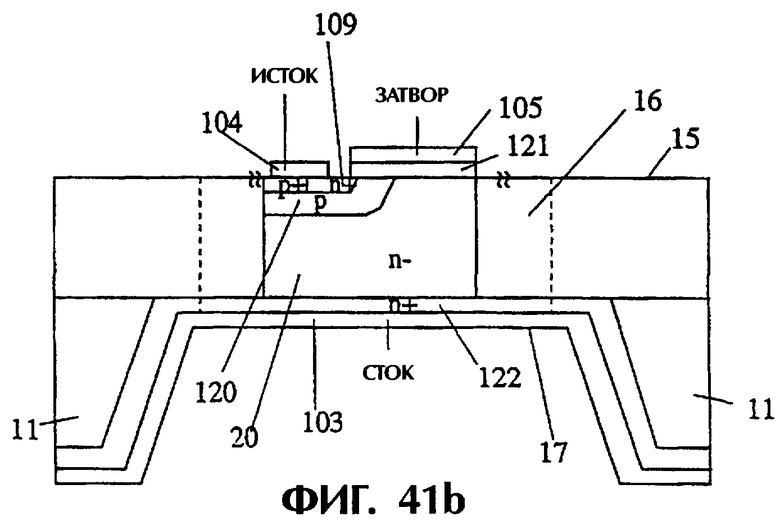

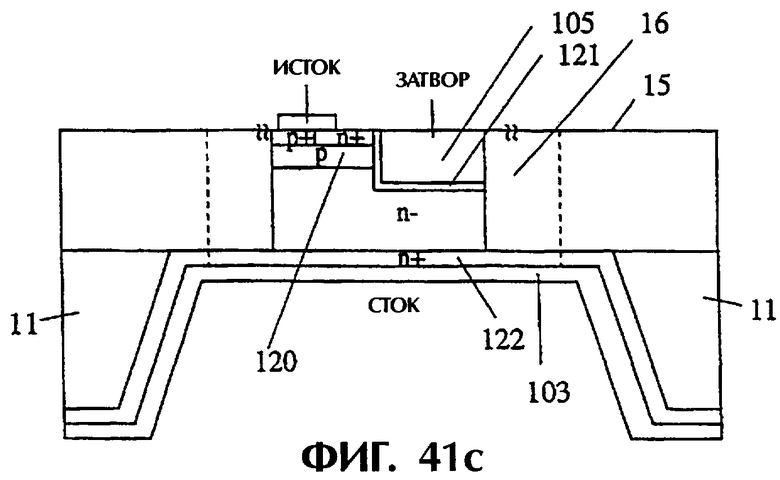

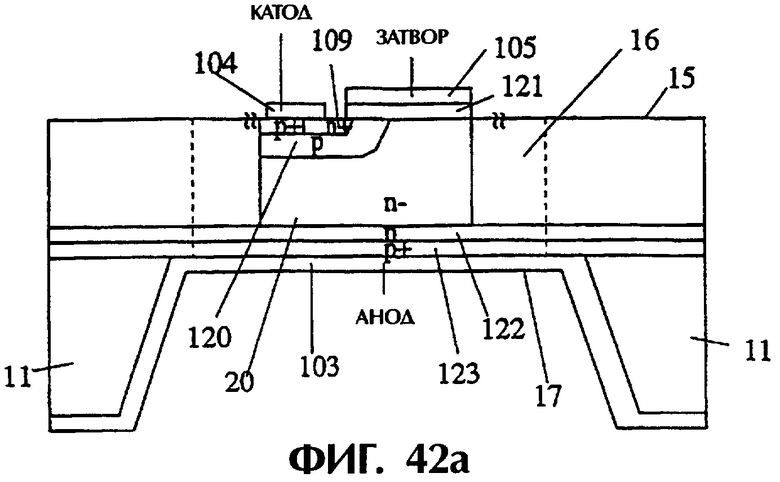

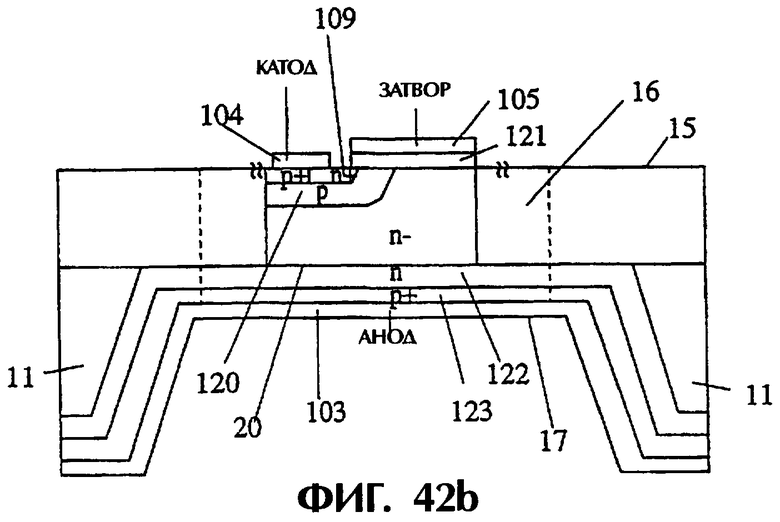

На фигуре 31 показан другой пример мембранного мощного полупроводникового устройства 10 в соответствии с настоящим изобретением, которое содержит полупроводниковую подложку 11 и тонкий слой 13, который включает, по меньшей мере, один полупроводниковый слой 14, и содержит верхнюю поверхность 15. Подложка 11 имеет нижнюю поверхность 12, которая формирует основную нижнюю поверхность устройства. В ходе производства часть подложки 11 ниже тонкого слоя 13 удаляют до тонкого слоя 13 для формирования мембраны 16 с верхней поверхностью 15 и нижней поверхностью 17. По меньшей мере, один контактный слой 103 присоединен к нижней поверхности 17 и находится в контакте с полупроводниковым слоем 14. В предпочтительном варианте воплощения указанный контактный слой 103 может быть выполнен в форме металлического слоя, нанесенного на обратную сторону устройства 10 после того, как мембрана 16 будет сформирована в ходе однократного вытравливания задней стороны. Металлический слой 103 может проходить от нижней поверхности 17 мембраны до основной нижней поверхности 12 устройства 10 и, предпочтительно, находится в контакте с внешним теплоотводом. Устройство содержит, по меньшей мере, один дополнительный основной вывод 104, закрепленный на верхней поверхности 15, находящейся в контакте с полупроводниковым слоем 14, и, предпочтительно, расположенный в пределах мембраны 16 так, что в открытом состоянии электропроводности между основным верхним выводом 104 и основным нижним выводом 103 он располагается, по существу, вертикально и перпендикулярно верхней поверхности 15 и нижней поверхности 17 мембраны. Устройство может содержать управляющий вывод 105, расположенный на поверхности 15, для управления током между основными выводами 103, 104. Мощное устройство 10 содержит слой 20 дрейфа, расположенный внутри первого тонкого слоя 13, в пределах полупроводникового слоя 14. По меньшей мере, часть слоя 20 дрейфа расположена в пределах мембраны 16.

Слой 20 дрейфа поддерживает высокие напряжения, прикладываемые к основным выводам 103, 104, в то время как мощное устройство 10 находится в закрытом состоянии и блокирует напряжение, приложенное к основным выводам 103 и 104. В таком режиме работы слой 20 дрейфа становится частично или полностью обедненным в отношении подвижных носителей заряда, и эквипотенциальные линии в поперечном сечении устройства 10 располагаются параллельно по отношению к верхней поверхности 15 и нижней поверхности 17 мембраны, и, по существу, равномерно распределяется между верхним краем слоя 20 дрейфа и нижним краем слоя 20 дрейфа.

Удаление подложки 11 под частью тонкого слоя 13 позволяет достичь лучший компромисс между сопротивлением в открытом состоянии и рабочими характеристиками в отношении напряжения пробоя. Равномерное распределение эквипотенциальных линий внутри области дрейфа в мембране 16 приводит к достижению идеального напряжения пробоя для заданной толщины области 20 дрейфа. Поскольку подложка 11 под частью тонкого слоя 13 удалена, отсутствует паразитное электрическое и тепловое сопротивление подложки и более просто достигается изоляция (не показана) от других устройств и цепей, сформированных на кристалле. Слой 103 вывода, предпочтительно, является в высокой степени теплопроводным для облегчения рассеивания тепла из области 11 мембраны на внешний теплоотвод (не показан).

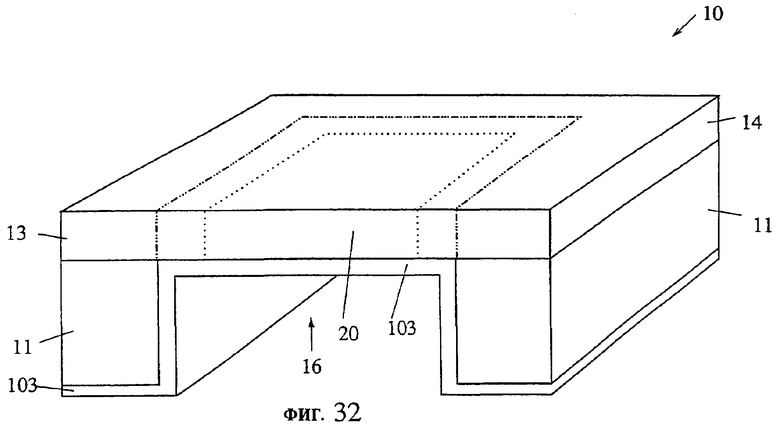

На фигуре 32 схематично показан пример мембранного мощного устройства 10 в соответствии с настоящим изобретением, в котором использовали сухое вытравливание нижней стороны для формирования мембраны 16. Стенки остающихся частей подложки 11 сформированы вертикальными, как показано на фигуре 32. После формирования мембраны способом сухого вытравливания слой 103 вывода наносят на нижнюю поверхность 17 мембраны для формирования одного из основных выводов устройства 10. Как было описано выше, сухое вытравливание имеет преимущество, состоящее в том, что объем, занимаемый зазором подложки 11, больше не зависит от толщины подложки 11, и, следовательно, проще контролировать площадь мембраны 16.