Изобретение относится к аппаратным устройствам компьютерного оборудования и может использоваться для расширения функций персонального компьютера (PC).

Аналогами являются проекционные устройства, приведенные в [1 с.517-536], построенные на основе ЖК-панелей, являющиеся внешним модулятором, и мультимедийные проекторы со встроенным модулятором. Изображение создается с помощью мощной проекционной лампы и встроенного в проектор электронно-оптического модулятора, управляемого сигналами с видеоадаптера PC, и проецируемое оптической системой на внешний экран. Недостатками аналогов являются: применение мощной проекционной лампы требует принудительного охлаждения ЖК-матрицы, неравномерная освещенность поверхности матрицы дает неравномерную яркость изображения на внешнем экране, в полисиликоновых проекторах используется три монохромных матрицы, процесс совмещения их изображений требует исключительно точной пространственной юстировки всех зеркал оптической системы, в них слишком объемна оптическая часть проектора, цветоделительная система, оптическая система и конвертер поляризации вместе с матрицами поглащают до 50% мощности светового потока лампы; проекторы технологии ILA имеют массу 120-500 кг и высокую стоимость 250000 USД, и работают только с аналоговым видеосигналом, проекторы технологии ДLP требуют 3-кратного увеличения частоты кадров и имеют сложную схему управления тремя ДМД-матрицами. Прототипом принят телевизионный проектор [2], содержащий три видеоусилителя, три канала управления лучами цветности R, G, В, каждый из которых включает АЦП, дешифратор, излучатель и оптическую систему, зеркальный сумматор цветовых лучей, последовательно соединенные усилитель строчной развертки и первый пьезодефлектор с отражателем на торце, последовательно соединенные усилитель кадровой развертки и второй пьезодефлектор с отражателем на торце, последовательно соединенные генератор импульсов и ключ, и экран. Недостатком прототипа является невозможность использования его как периферийное устройство для РС.

Цель изобретения - применение проектора периферийным аппаратным устройством для РС.

Техническим результатом является расширение рабочих возможностей РС отображением видеоинформации видеоадаптера на большом внешнем экране, достигаемый использованием с видеоадаптера PC видеорежима 800×600×85, преобразованием его в заявляемом устройстве в режим 1600×1200×85, и электронно-оптической разверткой на большом внешнем экране. Заявляемый цифровой проектор использует видеоинформацию с цифрового выхода (ДVI) видеоадаптера, который имеют большинство современных видеоадаптеров, например на основе чипсетов Ge Force 3, Ge Force 3 Ti 500 [1, c.651], Ge Force 4 Ti 4400, Ge Force 4 MX420, Ge Force MX460 [1, c.654], G 550 [1, c.659], Radeon 7500, 9000, 9500 [1, c.670]. Принимая видеоинформацию с разрешением 800×600 при 85 Гц, цифровой проектор увеличивает разряжение в 4 раза (1600×1200) и производит электронно-оптическую развертку изображения на большом внешнем экране. Информационными входами проектора являются 1-3 раздельные входы цифровых видеосигналов R, G, В, на которые коды поступают в последовательном виде, управляющими входами являются 1-3 входы: тактовой рабочей частоты, строчных синхроимпульсов и кадровых синхроимпульсов. Цифровой проектор выполняет следующие процессы: прием управляющих сигналов и кодов сигналов R, G, В, заполнение кодами первой строки трех первых накопителей кодов, заполнение кодами второй строки вторых трех накопителей кодов, удвоение числа отсчетов в каждой строке, удвоение числа строк в кадре и электронно-оптическую развертку изображения на внешнем экране.

Сущность заявляемого изобретения в том, что в цифровой проектор, содержащий последовательно соединенные усилитель строчной развертки и первый пьезодефлектор с отражателем на торце, последовательно соединенные усилитель кадровой развертки и второй пьезодефлектор с отражателем на торце, и экран, введены элемент И, делитель частоты, десять ключей, триггер, три первых и три вторых накопителей кодов, три блока удвоения строк, 1-6 блоки импульсных усилителей, блок модуляции излучения, блоки строчной и кадровой развертки, 1-4 блоки опорных напряжений и проекционная оптическая система.

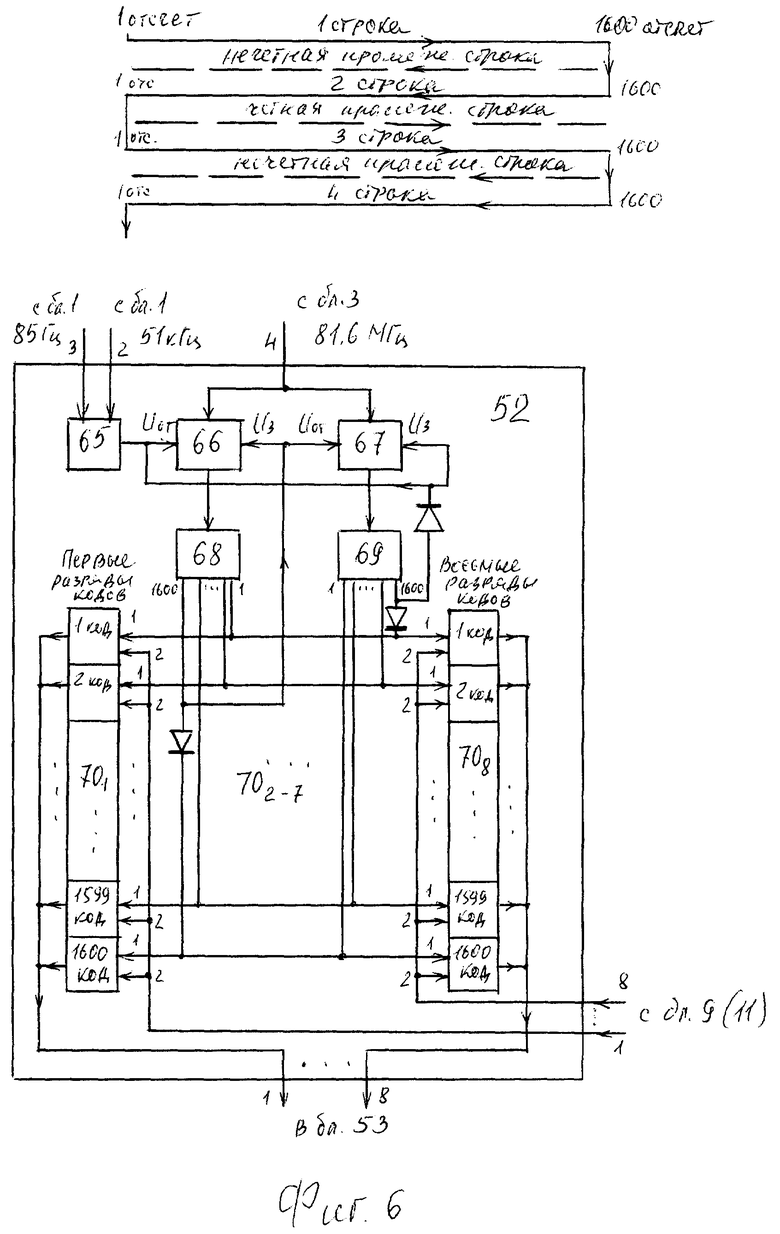

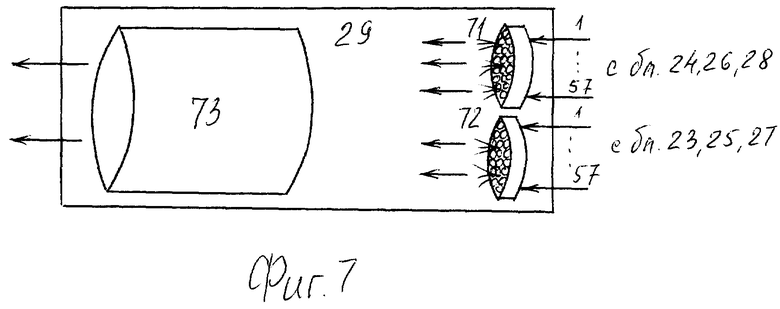

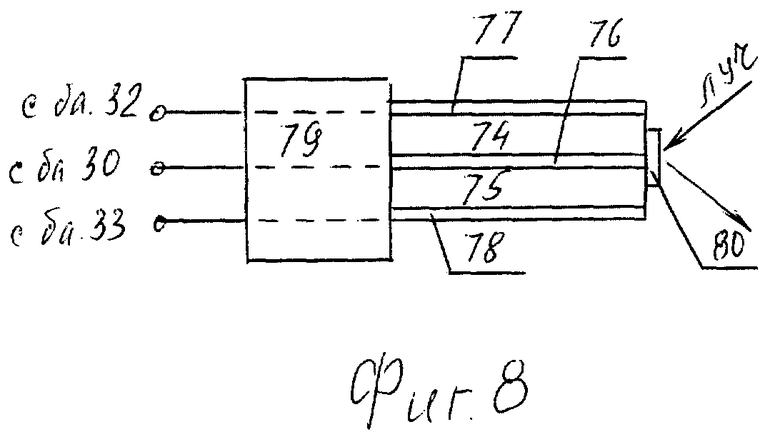

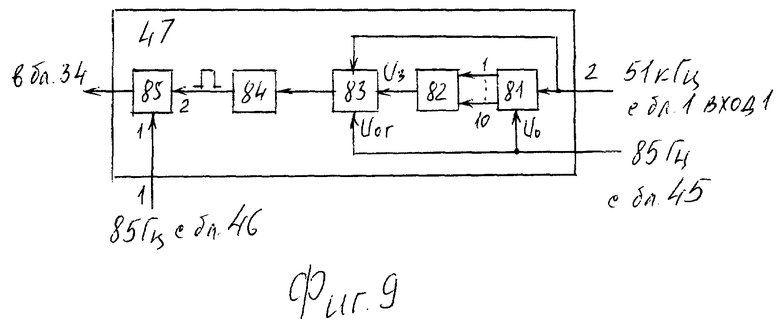

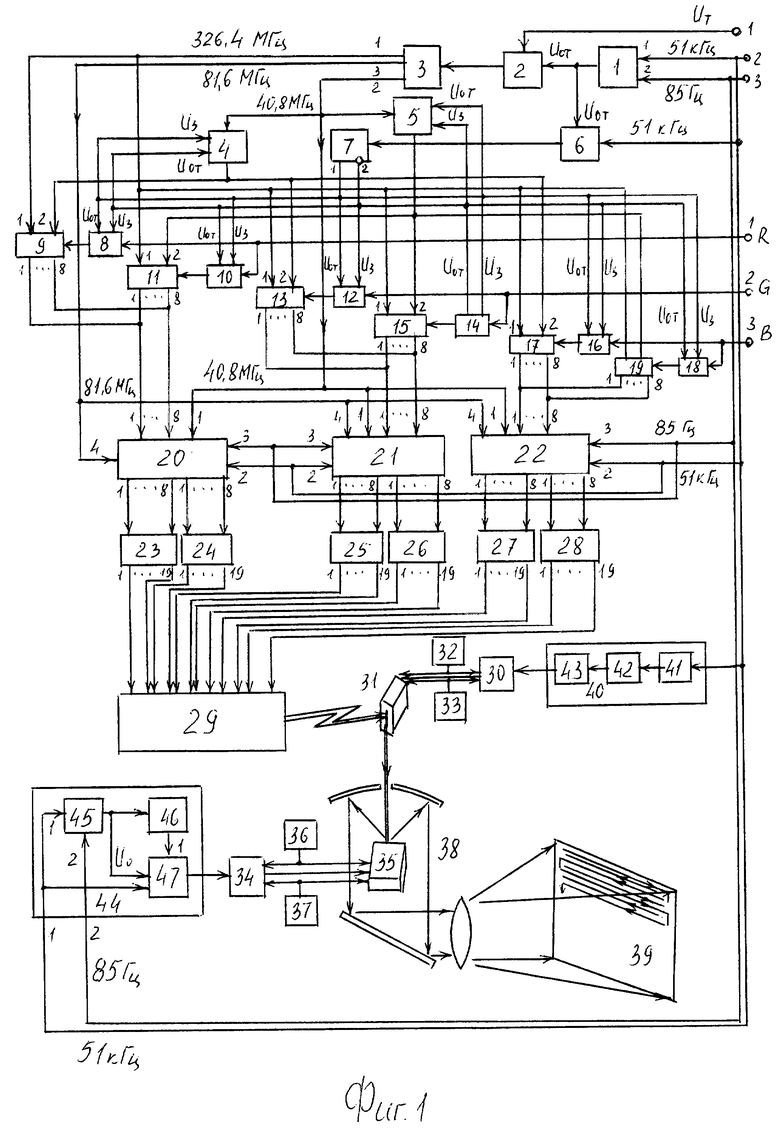

Функциональная схема цифрового проектора на фиг.1, построчная развертка растра и формы управляющих напряжений разверток на фиг.2, функциональная схема первого и второго накопителей кодов на фиг.3, блок удвоения строк на фиг.4, блок удвоения отсчетов на фиг.5, первый блок задержек на фиг.6, блок модуляции излучения на фиг.7, конструкция пьезодефлектора на фиг.8, суммирующий усилитель на фиг.9.

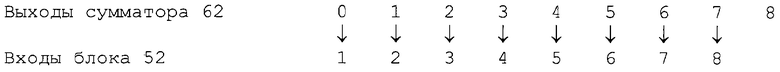

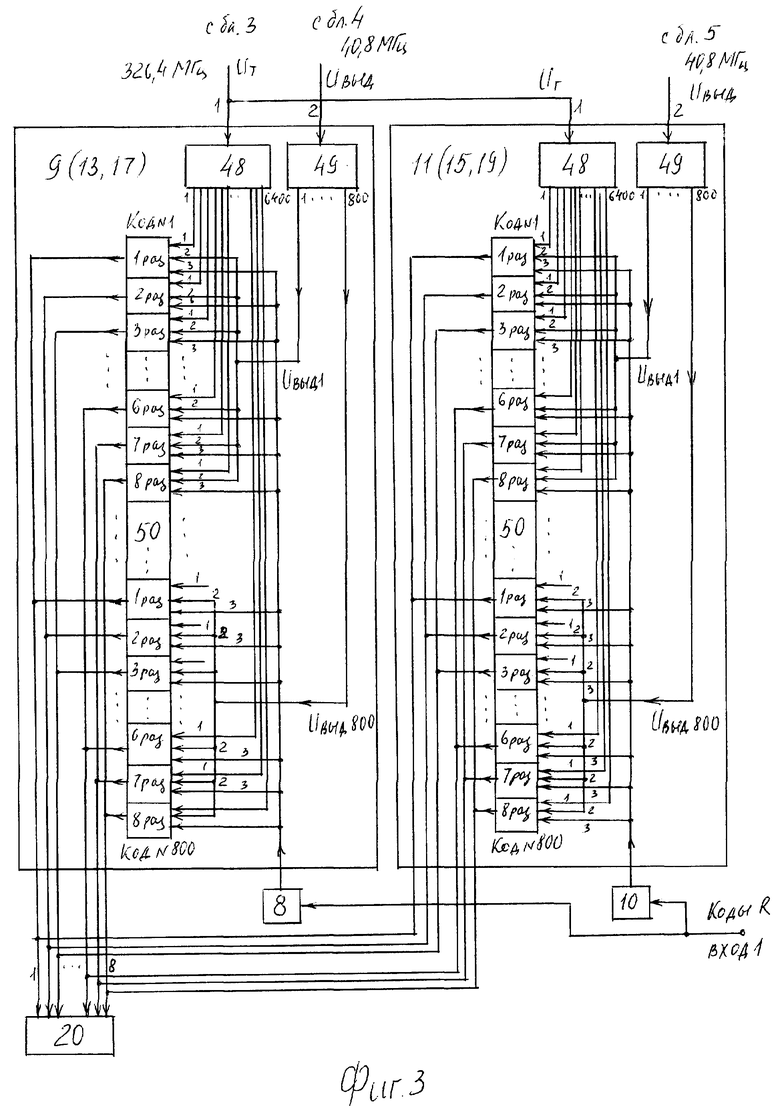

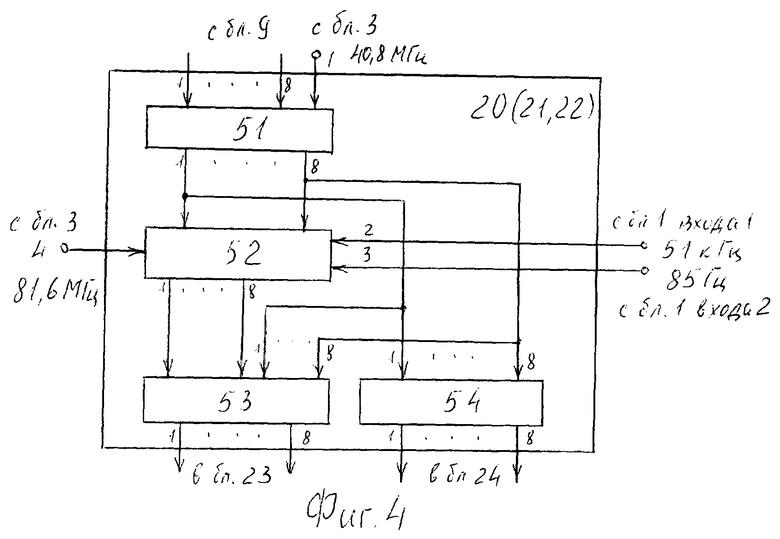

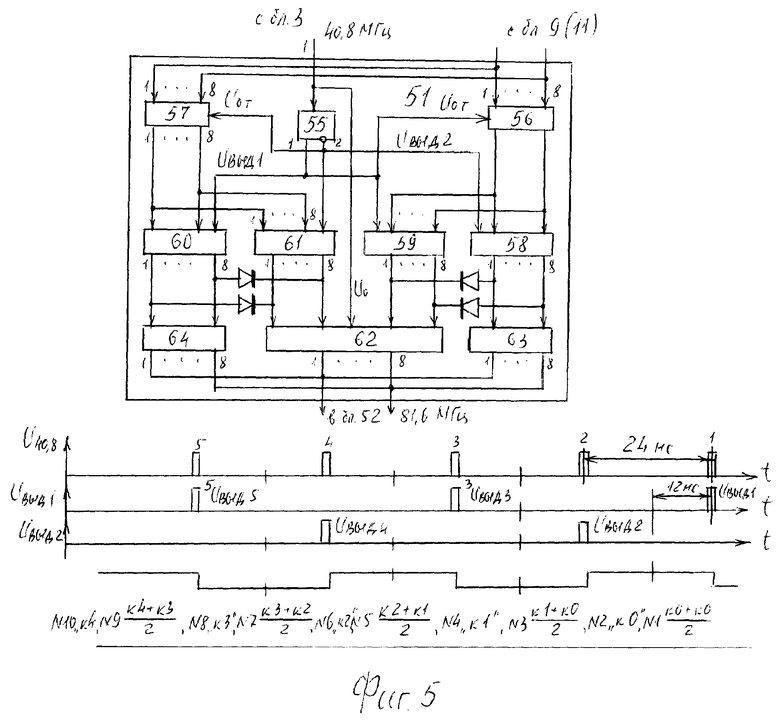

Цифровой проектор включает (фиг.1) последовательно соединенные элемент И 1, первый ключ 2, делитель 3 частоты и второй ключ 4, третий ключ 5, четвертый ключ 6, триггер 7, пятый ключ 8 и первый накопитель 9 кодов R, шестой ключ 10 и второй накопитель 11 кодов R, седьмой ключ 12 и первый накопитель 13 кодов G, восьмой ключ 14 и второй накопитель 15 кода G, девятый ключ 16 и первый накопитель 17 кодов В; десятый ключ 18 и второй накопитель 19 кодов В, первый 20, второй 21, третий 22 блоки удвоения строк, 1-6 блоки 23-28 импульсных усилителей, блок 29 модуляции излучения, последовательно соединенные усилитель 30 строчной развертки и порами пьезодефлектор 31 с отражателем на торце, первый источник 32 положительного опорного напряжения, второй источник 33 отрицательного опорного напряжения, последовательно соединенные усилитель 34 кадровой развертки и второй пьезодефлектор 35 с отражателем на торце, третий источник 36 положительного опорного напряжения, четвертый источник 37 отрицательного опорного напряжения, проекционную оптическую систему 38, во внешней фокальной плоскости которой расположен экран 39, блок 40 строчной развертки из последовательно соединенных делителя 41 частоты (2:1), задающего генератора 42 и выходного каскада 43, блок 44 кадровой развертки из элемента И 45, задающего генератора 46 и суммирующего усилителя 47. Первые накопители 9, 13, 17 кодов и вторые накопители 11, 15, 19 кодов идентичны (фиг.3), каждый включает первый распределитель 48 импульсов, второй распределитель 49 импульсов и регистр 50 на 800 кодов (800 байт). Блоки 20, 21, 22 удвоения строк (фиг.4) идентичны, каждый включает последовательно соединенные блок 51 удвоения отсчетов, первый блок 52 задержек и сумматор 53 и второй блок 54 задержек. Блок 51 удвоения отсчетов (фиг.5) содержит триггер 55, первый 56, второй 57 блоки ключей, первый 58, второй 59, третий 60, четвертый 61 регистры, сумматор 62, первый 63 и второй 64 блоки задержек, каждый из которых выполняет задержку кода на 24 нс. Первый блок 52 задержек (фиг.6) включает последовательно соединенные элемент И 65, первый 66 и второй 67 ключи, первый 68, второй 69 распределители импульсов и восемь регистров 701-708. Блок 52 производит задержку кодов на длительность строки 19,6 мкс (1000 мкс: 51 кГц). Блок 29 модуляции излучения (фиг.7) включает первый излучатель 71 трех основных цветов, второй излучатель 72 трех основных цветов (R, G, В) и оптическую систему 73. Излучающие плоскости излучателей расположены в вертикальной плоскости один над другим и в задней фокальной плоскости оптической системы 73, в передней фокальной плоскости которой расположен отражатель первого пьезодефлектора 31. Излучающие стороны излучателей 71, 72 оптически соединены через отражатели первого 31 и второго 35 пьезодефлекторов и проекционную оптическую систему 38 с внешним экраном 39. Входы первого излучателя 71 подключены к выходам блоков 24, 26, 28 импульсных усилителей, входы второго излучателя 72 подключены к выходам блоков 23, 25, 27 импульсных усилителей. Проекционная оптическая система 38 представлена зеркально-линзовой системой [3 с.370] и включает (фиг.1) сферическое зеркало, плоское зеркало с наклоном 45° относительно оптической оси сферического зеркала и корректирующую линзу. Плоское зеркало сокращает расстояние по прямой от сферического зеркала до экрана 39 и позволяет изменить направление лучей в нужном направлении. Кратность увеличения проекционной системы 38 задается требуемой величиной изображения на экране 39. Пьезодефлекторы 31 и 35 являются (фиг.8) торцевыми биморфными пьезоэлементами со световым отражателем на свободном торце. Конструктивно выполнены [4 c.118] из первой 74 и второй 75 пьезопластин, внутреннего электрода 76, первого 77 и второго 78 внешних электродов. Один конец пьезопластин жестко закреплен в держателе 79, на свободном торце расположен световой отражатель 80.

Суммирующий усилитель 47 включает (фиг.9) последовательно соединенные счетчик 81 импульсов, дешифратор 82, ключ 83, формирователь 84 импульсов и выходной усилитель 85. Первым входом суммирующего усилителя является первый вход выходного усилителя 85, вторым - счетный вход счетчика 81, управляющим входом являются объединенные входы управляющего входа счетчика 81 Uо первый управляющий вход ключа 83.

Цифровой проектор воспроизводит изображение на внешнем экране без преобразования кодов в аналоговые сигналы электронно-оптической разверткой одновременно двух строк. С приходом на первый вход элемента И 1 синхроимпульса строчной развертки 51 кГц и на второй его вход кадрового синхроимпульса 85 Гц сигнал с элемента И 1 открывает первый ключ 2 и четвертый ключ 6. Ключ 2 пропускает рабочую тактовую частоту с первого управляющего входа на вход делителя 3 частоты. Делитель 3 частоты выдает с первого выхода тактовую частоту 326,4 МГц, используемую при заполнении сигналами последовательных кодов разрядов регистров в накопителях кодов, со второго выхода импульсы дискретизации 40,8 МГц, с третьего выхода двойную частоту дискретизации 81,6 МГц. Коды видеосигналов R, G, В в последовательном виде с цифрового выхода PC поступают на 1-3 информационные входы цифрового проектора. Открытый ключ 6 пропускает синхроимпульсы строчной развертки на вход триггера 7, импульс с первого выхода триггера открывает ключи 8, 12, 16. Коды R первой строки через открытый ключ 8 поступают в первый накопитель 9 кодов R, коды G через открытый ключ 12 поступают в первый накопитель 13 кодов G, коды В через открытый ключ 16 поступают в первый накопитель 17 кодов В. За время первой строки 800 кодов R, G, В заполняют первые три накопителя 9, 13, 17 кодов. С приходом следующего синхроимпульса строчной развертки импульс со второго выхода триггера 7 закрывает ключи 8, 12, 16, открывает ключи 10, 14, 18 и открывает второй ключ 4, с выхода которого на вторые управляющие входы первых накопителей 9, 13, 17 кодов поступают сигналы Uвыд, выдающие последовательно с 1-го по 800-й коды первой строки в параллельном виде в блоки 20, 21, 22 удвоения строк. Через открытые ключи 10, 14, 18 коды R, G, В второй строки заполняют три вторых накопителя 11, 16, 19. С приходом третьего синхроимпульса строки коды третьей строки заполняют три первых накопителя 9, 13, 17, а коды второй строки в параллельном виде выдаются сигналами 40,8 МГц в блоки 20, 21, 22 удвоения строк. Частота сигналов выдачи (частота дискретизации): 600сторк×85 Гц ×800отс=40,8 МГц.

Частота строк: 600строк×85 Гц = 51 кГц.

Тактовая частота: 40,8 МГц ×8разр=326,4 МГц.

В блоках удвоения строк 20, 21, 22 коды поступают в блоки 51 удвоения отсчетов (фиг.4).

Процесс удвоения отсчетов в блоке 51 (фиг.5).

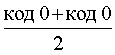

Период следования кодов на вход блока 51 составляет 24 нс, (1000 нс: 40,8 МГц), на выходе блока 51 составляет 12 нс, 1000 нс: 51,6 МГц. Каждый код используется дважды: первый раз как последующий, второй раз как предыдущий. Для этого блок 51 имеет четыре регистра 58, 59, 60, 61. Сумматор 62 выполняет сложение двух 8-разрядных кодов за 12 нс и выполнен из микросхем ИС ИМ180 [5, с.440]. При поступлении первого импульса 40,8 МГц на вход триггера 55 с его первого выхода сигнал Uвыд1 выдает одновременно "код 0" с регистра 59 и "код 0" с регистра 60, при выдаче содержимого регистры обнуляются. Код с регистра 59 поступает на первые входы сумматора 62, "код 0" с регистра 60 поступает на входы блока 64 задержек, а через диоды на вторые входы сумматора 62.

Блок 64 задерживает код на 24 нс. Сигнал Uвыд1 также открывает ключи в блоке 56, через которые первый код "код 1" поступает в регистры 58, 59. В это время сумматор 62 выполняет сложение кодов (код 0 + код 0) и деление на два. Деление кода суммы выполняется без затрат времени отбрасыванием младшего разряда кода суммы, как при делении десятичных чисел на 10. Для этого выходы сумматора 62 подключаются к входам блока 52 (53, 54) следующим образом:

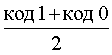

Разряд 0 означает разряд переноса при сумме кодов. При удвоении частоты следования кодов в 81,6 МГц период следования составляет 12 нс, поэтому время выполнения сложения кодов сумматором 62 оптимально подходит для удвоения числа отсчетов в строке, после сложения кодов (код 0 + код 0) сумматором 62 на его выходе появляется код №1  . Второй код №2 "код 0" следует на выход с блока 64 задержек через 12 нс. Блок 64 производит задержку кода на 24 нс, но первая половина времени задержки (12 нс) приходится на выполнение сложения в сумматоре 62, отсюда код №2 следует за кодом с сумматора через 12 нс. С приходом второго импульса в триггер 55 сигнал Uвыд2 со второго выхода выдает из регистра 58 "код 1" через диоды в сумматор 62 и напрямую в блок 63 задержек, задерживающий код на 24 нс. Из регистра 61 сигнал Uвыд2 выдает код "код 0" в сумматор 62, идет сложение (код 1 + код 0), при выходе деление на два, и код №3

. Второй код №2 "код 0" следует на выход с блока 64 задержек через 12 нс. Блок 64 производит задержку кода на 24 нс, но первая половина времени задержки (12 нс) приходится на выполнение сложения в сумматоре 62, отсюда код №2 следует за кодом с сумматора через 12 нс. С приходом второго импульса в триггер 55 сигнал Uвыд2 со второго выхода выдает из регистра 58 "код 1" через диоды в сумматор 62 и напрямую в блок 63 задержек, задерживающий код на 24 нс. Из регистра 61 сигнал Uвыд2 выдает код "код 0" в сумматор 62, идет сложение (код 1 + код 0), при выходе деление на два, и код №3  следует на выход блока 51. Через 12 нс с блока 63 следует на выход код №4 "код 1". Сигнал Uвыд2 открывает и ключи в блоке 57, и следующий "код 2" заполняет регистры 60, 61. С приходом третьего импульса в триггер 55 сигнал Uвыд3 с первого его выхода выдает о регистра 60 "код 2" в блок 64 задержек и через диоды в сумматор 62. Uвыд3 выдает с регистра 59 "код 1" в сумматор 62. Идет сложение (код 2 + код 1), деление на два, и с выхода блока 51 следует код №5

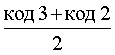

следует на выход блока 51. Через 12 нс с блока 63 следует на выход код №4 "код 1". Сигнал Uвыд2 открывает и ключи в блоке 57, и следующий "код 2" заполняет регистры 60, 61. С приходом третьего импульса в триггер 55 сигнал Uвыд3 с первого его выхода выдает о регистра 60 "код 2" в блок 64 задержек и через диоды в сумматор 62. Uвыд3 выдает с регистра 59 "код 1" в сумматор 62. Идет сложение (код 2 + код 1), деление на два, и с выхода блока 51 следует код №5  , через 12 нс за ним с блока 64 следует код №6 "код 2". Сигнал Uвыд3 открывает ключи в блоке 56, и код "код 3" поступает в регистры 58, 59. С приходом на вход триггера 55 четвертого импульса сигнал Uвыд4 с его второго выхода выдает с регистра 58 "код 3" в блок 63 и через диоды в сумматор 62 и выдает "код 2" с регистра 61. Идет сложение (код 3 + код 2), деление на 2, с выхода блока 51 следует код №7

, через 12 нс за ним с блока 64 следует код №6 "код 2". Сигнал Uвыд3 открывает ключи в блоке 56, и код "код 3" поступает в регистры 58, 59. С приходом на вход триггера 55 четвертого импульса сигнал Uвыд4 с его второго выхода выдает с регистра 58 "код 3" в блок 63 и через диоды в сумматор 62 и выдает "код 2" с регистра 61. Идет сложение (код 3 + код 2), деление на 2, с выхода блока 51 следует код №7  . Через 12 нс за ним с блока 63 следует код №8 "код 3". Сигнал Uвыд4 открывает ключи в блоке 57, и "код 4" поступает в регистры 60, 61. Далее процессы повторяются. Удвоенное число отсчетов в строке 1600 (800×2) поступает с блока 51 в первый блок 52 задержек, на вторые входы сумматора 53 и на входы второго блока 54 задержек (фиг.4). Коды текущей строки, поступая во второй блок 54 задержек, задерживаются на длительность сложения кодов в сумматоре 53 на 12 нс, затем поступают в параллельном виде в свой блок 24 импульсных усилителей, первый блок 52 задержек производит задержку кодов текущей строки на длительность 19,6 мкс. Сумматор 53 выполняет сложение кодов текущей строки с кодами тех же отсчетов строки, задержанными на 19,6 мкс, прошедшей строки. Код суммы делится на 2 отбрасыванием последнего разряда кода суммы. На входы блока 23 импульсных усилителей поступают в параллельном виде коды образованной промежуточной строки. На входы блоков 23, 25, 27 поступают коды промежуточных строк. Идентичные процессы идут в блоках 21 и 22 удвоения строк. В результате число активных строк удваивается с 591 до 1182. С трех блоков 54 задержек коды поступают в импульсные усилители блоков 24, 26, 28 (фиг.1), усиленные в них до необходимой величины сигналы кодов поступают для запитывания светодиодов в первом излучателе 71 блока 29 модуляции излучения. Излучение с первого излучателя 71 воспроизводит 591 строку изображения. Коды с трех блоков 53 поступают в импульсные усилители блоков 23, 25, 27, сигналы кодов, усиленные в них, запитывают светодиоды в излучателе 72. Его излучение воспроизводит 591 промежуточных строк изображения. Импульсные усилители представляются микросхемами 1533АП3 [5, с.128] с временем срабатывания до 12 нс. Каждый из блоков 23-28 содержит импульсные усилители по числу обслуживаемых светодиодов (по 19 штук). Развертка строк выполняется построчно без обратных ходов (фиг.2). Кадровая развертка выполняется с обратным ходом, 1,5% от длительности кадра 0,176 мкс (занимает 9 строк). Строчная развертка активных 1182 строк выполняется блоком 40 строчной развертки. На его вход поступает строчная частота 51 кГц, делитель 41 делит частоту 2:1, на вход задающего генератора 42 поступает 25,5 кГц. Выходной каскад 43 усиливает сигналы, которые поступают на вход усилителя 30 строчной развертки, а с него на внутренний электрод 76 первого пьезодефлектора (фиг.8). На внешние электроды 77, 78 поступают соответствующие напряжения с первого 32 и второго 33 источников опорных напряжений. C подачей управляющего сигнала с блока 30 происходит деформация пьезопластин [4 c.122], торец со световым отражателем 80 приходит в колебательное движение и производит развертку одновременно двух строк по горизонтали на отражателе второго пьезодефлектора 35 (фиг.1). Торец с отражателем пьезодефлектора 31 колеблется с частотой 25,5 кГц. Ширина отражателя пьезодефлектора 31 принята 0,04 мм (0,02 мм на одну строку), длина 3 мм для облегчения юстировки. Кадровую развертку выполняет блок 44, формируя управляющее напряжение на выходе блока 47 (фиг.2). Период развертки кадра 11,764 мс (85 Гц), развертка имеет обратный ход 0,176 мс. Задающий генератор 46 формирует пилообразное линейно изменяющееся напряжение, поступающее на первый вход суммирующего усилителя 47. На вход генератора 46 поступают импульсы с элемента И 45 в момент прихода на его входы строчного и кадрового синхроимпульсов. Суммирующий усилитель 47 производит суммирование линейно изменяющегося напряжения с импульсами частоты строк. Каждый импульс строки перемещает строку в конце ее хода на шаг в две строки. Назначение блоков 81-84 подавать на второй вход выходного усилителя 85 в нужное время импульсы соответствующей амплитуды и длительности. Счетчик 81 10-разрядный производит счет строчных импульсов 51 кГц, цикл счета 591 импульс. При поступлении 591-го импульса дешифратор 82 выдает сигнал U3, закрывающий ключ 83.

. Через 12 нс за ним с блока 63 следует код №8 "код 3". Сигнал Uвыд4 открывает ключи в блоке 57, и "код 4" поступает в регистры 60, 61. Далее процессы повторяются. Удвоенное число отсчетов в строке 1600 (800×2) поступает с блока 51 в первый блок 52 задержек, на вторые входы сумматора 53 и на входы второго блока 54 задержек (фиг.4). Коды текущей строки, поступая во второй блок 54 задержек, задерживаются на длительность сложения кодов в сумматоре 53 на 12 нс, затем поступают в параллельном виде в свой блок 24 импульсных усилителей, первый блок 52 задержек производит задержку кодов текущей строки на длительность 19,6 мкс. Сумматор 53 выполняет сложение кодов текущей строки с кодами тех же отсчетов строки, задержанными на 19,6 мкс, прошедшей строки. Код суммы делится на 2 отбрасыванием последнего разряда кода суммы. На входы блока 23 импульсных усилителей поступают в параллельном виде коды образованной промежуточной строки. На входы блоков 23, 25, 27 поступают коды промежуточных строк. Идентичные процессы идут в блоках 21 и 22 удвоения строк. В результате число активных строк удваивается с 591 до 1182. С трех блоков 54 задержек коды поступают в импульсные усилители блоков 24, 26, 28 (фиг.1), усиленные в них до необходимой величины сигналы кодов поступают для запитывания светодиодов в первом излучателе 71 блока 29 модуляции излучения. Излучение с первого излучателя 71 воспроизводит 591 строку изображения. Коды с трех блоков 53 поступают в импульсные усилители блоков 23, 25, 27, сигналы кодов, усиленные в них, запитывают светодиоды в излучателе 72. Его излучение воспроизводит 591 промежуточных строк изображения. Импульсные усилители представляются микросхемами 1533АП3 [5, с.128] с временем срабатывания до 12 нс. Каждый из блоков 23-28 содержит импульсные усилители по числу обслуживаемых светодиодов (по 19 штук). Развертка строк выполняется построчно без обратных ходов (фиг.2). Кадровая развертка выполняется с обратным ходом, 1,5% от длительности кадра 0,176 мкс (занимает 9 строк). Строчная развертка активных 1182 строк выполняется блоком 40 строчной развертки. На его вход поступает строчная частота 51 кГц, делитель 41 делит частоту 2:1, на вход задающего генератора 42 поступает 25,5 кГц. Выходной каскад 43 усиливает сигналы, которые поступают на вход усилителя 30 строчной развертки, а с него на внутренний электрод 76 первого пьезодефлектора (фиг.8). На внешние электроды 77, 78 поступают соответствующие напряжения с первого 32 и второго 33 источников опорных напряжений. C подачей управляющего сигнала с блока 30 происходит деформация пьезопластин [4 c.122], торец со световым отражателем 80 приходит в колебательное движение и производит развертку одновременно двух строк по горизонтали на отражателе второго пьезодефлектора 35 (фиг.1). Торец с отражателем пьезодефлектора 31 колеблется с частотой 25,5 кГц. Ширина отражателя пьезодефлектора 31 принята 0,04 мм (0,02 мм на одну строку), длина 3 мм для облегчения юстировки. Кадровую развертку выполняет блок 44, формируя управляющее напряжение на выходе блока 47 (фиг.2). Период развертки кадра 11,764 мс (85 Гц), развертка имеет обратный ход 0,176 мс. Задающий генератор 46 формирует пилообразное линейно изменяющееся напряжение, поступающее на первый вход суммирующего усилителя 47. На вход генератора 46 поступают импульсы с элемента И 45 в момент прихода на его входы строчного и кадрового синхроимпульсов. Суммирующий усилитель 47 производит суммирование линейно изменяющегося напряжения с импульсами частоты строк. Каждый импульс строки перемещает строку в конце ее хода на шаг в две строки. Назначение блоков 81-84 подавать на второй вход выходного усилителя 85 в нужное время импульсы соответствующей амплитуды и длительности. Счетчик 81 10-разрядный производит счет строчных импульсов 51 кГц, цикл счета 591 импульс. При поступлении 591-го импульса дешифратор 82 выдает сигнал U3, закрывающий ключ 83.

Развертка кадра прекращается, следует обратный ход. На вход усилителя 34 поступает управляющее линейно изменяющееся ступенчатое напряжение, усиливаемое усилителем 34 до необходимой величины. Отражатель пьезодефлектора 35 отклоняет развертываемые строки вниз, затем обратный ход вверх (фиг.2). Во время обратного хода коды цветных сигналов из накопителей 9, 11, 13, 15, 17, 19 кодов не выдаются, закрыты ключи 8, 10, 12, 14, 16, 18. Излучение с блока 29 отсутствует. Ширина отражателя второго пьезодефлектора 35 принята 0,04 мм (две строки по 0,02 мм), длина составляет 32 мм (1600отсч×0,02 мм). Разрешающий элемент одной строки на отражателе пьезодефлектора 35 0,02×0,02 мм. С приходом первого синхроимпульса строки в триггер 7 сигнал с его первого выхода открывает ключи 8, 12, 16, и первые накопители 9, 13, 17 заполняют коды сигналов R, G, В. С приходом 2-го синхроимпульса строки в триггер 7 сигнал со второго его выхода закрывает ключи 8, 12, 16, открывает ключи 10, 14, 18. Вторые накопители 11, 15, 19 заполняются кодами цветовых сигналов. Сигналы Uвыд дискретизации 40,8 МГц выдают коды с первых накопителей кодов в последовательности с 1-го по 800-й в блоки 20, 21, 22 удвоения строк. С приходом третьего ССИ в триггер 7 процесс заполнения первых трех накопителей кодов повторяется, выдаются коды с вторых накопителей в блоки 20-22 в последовательности о 1-го по 800-й. Схемы первого и второго накопителей кодов на фиг.3. Заполнение регистров 50 кодами 800 отсчетов строки производится в последовательности с 1-го 800-й отсчет. В каждом регистре размещается по 800 байт.

Выдача кодов с регистров 50 идет в последовательности с 1-го отсчета по 800-й. Блоки 52 участвуют в формировании промежуточных строк задержкой кодов каждой строки на длительность строки. В связи с тем, что развертка строк в растре идет встречно (фиг.6), то при формировании четных промежуточных строк коды с блока 52 в сумматор 53 выдаются последовательно с 1-го отсчета по 1600-й, а при формировании нечетных промежуточных строк коды с блока 52 выдаются в обратной последовательности, т.е. с 1600-го отсчета к первому. Коды 1600 отсчетов с блока 9 (13) в параллельном виде поступают в восемь регистров 701-708 блока 52. Первые разряды кодов поступают в регистр 701, вторые разряды - в регистр 702... восьмые разряды кодов поступают в регистр 708. Каждый из регистров 701-8 включает по 1600 разрядов. Заполнение разрядов регистров идет последовательно с 1-го по 1600 коды. Выдача кодов сигналами с распределителя 68 импульсов при формировании четных промежуточных строк идет в прямой последовательности с 1-го по 1600, а выдача кодов при формировании нечетных промежуточных строк сигналами с распределителя 69 импульсов идет в обратной последовательности: начинается с 1600-го кода к первому. Сумматоры 53 идентичны, представлены микросхемами ИМ180 [5, с.440], формируют промежуточные строки выполнением сложения кодов одних и тех же отсчетов предыдущей и последующей строк и делением кода суммы на два. Сигналы разрядов кодов в импульсных усилителях блоков 23-28 усиливаются до необходимой величины и запитывают свои светодиоды на излучение в излучателях 71, 72 блока 29 модуляции излучения. Яркостная модуляция выполняется включением на излучение светодиодов соответственно весам разрядов в кодах, приведенные в таблице 1. Промодулированное по яркости излучения первого 71 и второго 72 излучателей фокусируется оптической системой 73 (фиг.7) на отражателе первого пьезодефлектора 31, выполняющего строчную развертку двух лучей на отражателе второго пьезодефлектора 35. Каждый из излучателей 71, 72 содержит по 57 светодиодов: 19 красного, 19 зеленого и 19 синего излучения типа HLMP, выпускаемые компанией "Хьюлетт паккард" [6, c.71]. Распределение светодиодов одного цвета соответственно весам разрядов в коде в таблице 1.

Суммарное излучение светодиодов трех цветов от каждого излучателя смешивается оптической системой 73 при фокусировке в два цветовых пятна на отражателе первого пьезодефлектора 31. Яркость, насыщенность и цветовой тон результирующего цвета на экране 39 определяется суммарной энергией и взаимным соотношением трех цветов от излучателя. Для красного излучения приняты светодиоды HLMP-AL00 с силой света 0,4 кд, длиной волны 0,59 мкм и током 0,02 А, для зеленого излучения приняты светодиоды HLMP-АМ00 с силой света 0,8 кд, длиной волны 0,526 мкм и током 0,02 А, для синего излучения приняты светодиоды HLMP-АВ00 с силой света 0,3 кд, длиной волны 0,475 мкм и током 0,02 А.

Максимальная сила света от одного излучателя с учетом, что все светодиоды имеют силу света синего светодиода 0.3 кд, составляет:

В=3×0,3 кд (8+4+2+1+0,5+0,25+0,125+0,0625)=0,9 кд × 15,97=14,37 кд.

где 8-0,0625 - коэффициенты двоичного кода 1-8 разрядов.

При учете потерь силы излучения одного излучателя при проекции до экрана в 30 крат максимальная яркость одного развертывающего элемента (пикселя) площадью (при увеличении изображения проекционной системой в 100 раз) 2×2 мм, 4·10-6 м2 составляет:

где в числителе - суммарная сила излучения одного излучателя,

30 - кратность ослабления излучения при проекции,

4·10-6 м2 - площадь светового элемента (пикселя) на экране.

При увеличении изображения на экране в 100 раз его размеры составляют: по горизонтали 100×(0,02 мм × 1600)=3200 мм, по вертикали 100×(0,02 мм × 1182)=2364 мм, по диагонали 3,98 м.

Пьезодефлектор 31 производит строчную развертку двух строк одновременно на отражателе второго пьезодефлектора 35 (фиг.1), выполяющего кадровую развертку на экране 39. Развертка строк построчная в две строки без обратных ходов, развертка кадра с обратным ходом. Технические характеристики цифрового проектора в таблице 2.

Работа цифрового проектора.

Рабочая тактовая частота и синхроимпульсы строчной и кадровой разверток поступают на 1, 2, 3 управляющие входы проектора. Коды видеосигналов R, G, B в последовательном виде поступают с цифрового выхода видеоадаптера PC на 1-3 информационные входы проектора. Коды R, G, В при открытых ключах 8, 12, 16 заполняют первые три накопителя 9, 13, 17 кодов. По заполнении 800 кодами первой строки первых три накопителя кодов ключи 8, 12, 16 закрываются, открываются ключи 10, 14, 18. Коды второй строки заполняют вторые три накопителя кодов 11, 15, 19. А содержимое первых трех накопителей кодов последовательно код за кодом выдаются в блоки 20, 21, 22 удвоения строк. По заполнении вторых накопителей кодов их содержимое выдается в блоки 20, 21, 22, далее процесс непрерывно повторяется. Блоки 20-22 выполняют сначала удвоение отсчетов в строке, а затем и удвоение строк. Коды текущей 591 строки с выхода вторых блоков 54 задержек поступают в параллельном виде в блоки 24, 26, 28. Коды промежуточных строк 591 с выходов сумматоров 53 поступают в блоки 23, 28, 27 импульсных усилителей. Блоки 54, задерживая коды на 12 нс, обеспечивают параллельное поступление одних и тех же отсчетов двух строк на входы блока 29 модуляции излучения. Оптическая система 73 фокусирует промодулированные излучателями 71, 72 излучения по яркости на отражателе пьезодефлектора 31, выполняющего строчную развертку двух строк на отражателе пьезодефлектора 35, выполняющего кадровую развертку изображения. Проекционная оптическая система 38 проецирует развертываемое изображение на большом внешнем экране 39, который выполняется из матового стекла либо из другого высоко отражающего материала. Размер экрана при увеличении кадра в 100 раз составляет 3,2×2,364 м, размещается от проекционного объектива на расстоянии 11-12 метров. Заявляемый цифровой проектор расширяет рабочие возможности персонального компьютера отображением видеоинформации на большом экране для пользования ею более чем одним человеком.

Использованные источники

1. Колесниченко О.В, Шишигин И.В. Аппаратные средства PC. 5-е издание, СПб, 2004, с.517-536, 651, 654, 659, 660, 670.

2. Патент №2099902, кл. Н 04 N 9/31, бюл.35 за 1997, прототип.

3. Самойлов В.Ф, Хромой Б.И. Телевидение. М., 1975, с.370.

4. Фридлянд И.В, Сошников В.Г. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118, рис.5,5, с.122, рис.5.10.

5. Цифровые интегральные микросхемы. Минск, 1991, с.128, 440.

6. "Радио" №7, 1998, с.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2004 |

|

RU2270529C1 |

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2284672C1 |

| ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕР | 2004 |

|

RU2279708C1 |

| ЦИФРОВОЙ МОНИТОР | 2005 |

|

RU2292664C1 |

| СИСТЕМА ОБЪЕМНОЙ ВИДЕОЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ | 2006 |

|

RU2315439C1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2006 |

|

RU2310287C1 |

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2006 |

|

RU2303334C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2000 |

|

RU2194370C2 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2001 |

|

RU2214693C2 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

Изобретение относится к аппаратным устройствам компьютерного оборудования, может использоваться для расширения функций персонального компьютера (PC). Техническим результатом является расширение рабочих возможностей, достигаемое отображением видеоинформации с PC на большом внешнем экране, для чего в цифровой проектор, содержащий усилители строчной и кадровой разверток и два пьезодефлектора с отражателями на торцах, введены элемент И, делитель частоты, ключи, триггер, три первых и три вторых накопителя кодов, три блока удвоения строк, шесть блоков импульсных усилителей, блок модуляции излучения и проекционная оптическая система. Воспроизводимый видеорежим на внешнем экране 1600×1200×85. 9 ил., 2 табл.

Цифровой проектор, содержащий последовательно соединенные усилитель строчной развертки и первый пьезодефлектор с отражателем на торце, последовательно соединенные усилитель кадровой развертки и второй пьезодефлектор с отражателем на торце, оптически соединенный с отражателем первого пьезодефлектора, и экран, отличающийся тем, что в него введены последовательно соединенные элемент И, первый ключ и делитель частоты, сигнальный вход первого ключа является первый управляющим входом цифрового проектора, вторым и третьим управляющими входами которого являются первый и второй входы элемента, и введены второй, третий, четвертый ключи, входы второго и третьего ключей объединены и подключены к второму выходу делителя частоты, вход четвертого ключа подключен к первому входу элемента И, а управляющий вход его подключен к выходу элемента И, введен триггер, вход которого подключен к выходу четвертого ключа, последовательно соединенные пятый ключ и информационный вход первого накопителя кодов R, последовательно соединенные шестой ключ и информационный вход второго накопителя кодов R, последовательно соединенные седьмой ключ и информационный вход первого накопителя кодов G, последовательно соединенные восьмой ключ и информационный вход второго накопителя кодов G, последовательно соединенные девятый ключ и информационный вход первого накопителя кодов В, последовательно соединенные десятый ключ и информационный вход второго накопителя кодов В, первые (тактовые) управляющие входы первых и вторых накопителей кодов R, G, В подключены к первому выходу делителя частоты, вторые управляющие входы первых накопителей кодов R, G, В подключены к выходу второго ключа, вторые управляющие входы вторых накопителей кодов R, G, В подключены к выходу третьего ключа, первые управляющие входы пятого, седьмого, девятого ключей, вторые управляющие входы шестого, восьмого, десятого ключей, второй управляющий вход второго ключа и первый управляющий вход третьего ключа объединены и подключены к первому выходу триггера, вторые управляющие входы пятого, седьмого, девятого ключей, первые управляющие входы шестого, восьмого, десятого ключей, первый управляющий вход второго ключа и второй управляющий вход третьего ключа объединены и подключены к второму выходу триггера, сигнальные входы пятого и шестого ключей объединены и являются первым информационным входом цифрового проектора, сигнальные входы седьмого и восьмого ключей объединены и являются вторым информационным входом цифрового проектора, сигнальные входы девятого и десятого ключей объединены и являются третьим информационным входом цифрового проектора, введены первый, второй, третий блоки удвоения строк, информационные входы первого блока удвоения строк подключены к поразрядно объединенным выходам первого и второго накопителей кодов R, информационные входы второго блока удвоения строк подключены к поразрядно объединенным выходам первого и второго накопителей кодов G, информационные входы третьего блока удвоения строк подключены к поразрядно объединенным выходам первого и второго накопителей кодов В, первые управляющие входы блоков удвоения строк подключены к второму выходу делителя частоты, вторые управляющие входы блоков удвоения строк подключены к первому входу элемента И цифрового проектора, третьи управляющие входы блоков удвоения строк подключены к второму входу элемента И цифрового проектора, четвертые управляющие входы блоков удвоения строк подключены к третьему выходу делителя частоты, введены 1-6 блоки импульсных усилителей и блок модуляции излучения, входы первого, второго блоков импульсных усилителей подключены к выходам первого блока удвоения строк, входы третьего, четвертого блоков импульсных усилителей подключены к выходам второго блока удвоения строк, входы пятого, шестого блоков импульсных усилителей подключены к выходам третьего блока удвоения строк, выходы 1-6 блоков импульсных усилителей подключены к соответствующим входам блока модуляции излучения, введены блок строчной развертки из последовательно соединенных делителя частоты (2:1), задающего генератора и выходного каскада, входом блока строчной развертки является вход делителя частоты, подключенный к первому входу элемента И цифрового проектора, выходом является выход выходного каскада, подключенный к входу усилителя строчной развертки, блок кадровой развертки из последовательно соединенных элемента И, задающего генератора и суммирующего усилителя, первым входом блока кадровой развертки являются вход элемента И и второй вход суммирующего усилителя, которые объединены и подключены к первому входу элемента И цифрового проектора, вторым входом блока кадровой развертки является второй вход элемента И, подключенный к второму входу элемента И цифрового проектора, выход элемента И блока кадровой развертки подключен и к управляющему входу суммирующего усилителя, выход которого является выходом блока кадровой развертки, и подключен к входу усилителя кадровой развертки, введена проекционная оптическая система, содержащая последовательно расположенные сферическое зеркало, в фокальной плоскости которого расположен отражатель второго пьезодефлектора, плоское зеркало с наклоном 45° относительно оптической оси сферического зеркала и корректирующая линза, излучающая сторона блока модуляции излучения оптически соединена через отражатели первого и второго пьезодефлекторов и через проекционную оптическую систему с экраном цифрового проектора, введены первый источник положительного опорного напряжения, выход которого подключен к вторым входам усилителя строчной развертки и первого пьезодефлектора, второй источник отрицательного опорного напряжения, выход которого подключен к третьим входам усилителя строчной развертки и первого пьезодефлектора, третий источник положительного опорного напряжения, выход которого подключен к вторым входам усилителя кадровой развертки и второго пьезодефлектора, четвертый источник отрицательного опорного напряжения, выход которого подключен к третьим входам усилителя кадровой развертки и второго пьезодефлектора, первые три и вторые три накопителя кодов R, G, В идентичны, каждый включает первый и второй распределители импульсов и регистр с соответствующим числом разрядов, выходы первого распределителя импульсов последовательно с первого по последний выход подключены к первым управляющим входам разрядов в регистре, каждый выход второго распределителя импульсов последовательно от первого по последний выход подключен параллельно к восьми вторым управляющим входам регистра, третьи (информационные) входы разрядов регистра объединены и являются информационным входом в каждом накопителе кодов, выходы одноименных разрядов регистра объединены и являются 1-8 выходами в каждом накопителе кодов, первым и вторым управляющими входами в каждом накопителе кодов являются соответственно вход первого и вход второго распределителя импульсов, первый, второй, третий блоки удвоения строк идентичны, каждый включает последовательно соединенные блок удвоения отсчетов, первый блок задержек и сумматор, и второй блок задержек, информационные входы которого подключены к выходам блока удвоения отсчетов, первые информационные входы сумматора подключены к выходам первого блока задержек, вторые информационные входы сумматора подключены к выходам блока удвоения отсчетов, входы которого являются информационными входами блока удвоения строк, первым управляющим входом которого является управляющий вход блока удвоения отсчетов, вторым, третьим, четвертым управляющими входами являются соответственно второй, третий и четвертый управляющие входы первого блока задержек, выходами блока удвоения строк являются выходы второго блока задержек и выходы сумматора, первый, второй, третий блоки удвоения отсчетов идентичны, каждый включает триггер, первый и второй блоки ключей, 1-4 регистры, сумматор, первый и второй блоки задержек, информационным входом являются поразрядно объединенные входы блоков ключей, выходы первого блока ключей подключены параллельно к входам первого и второго регистров, выходы второго блока ключей подключены параллельно к входам третьего и четвертого регистров, выходы первого регистра подключены к входам первого блока задержки и через диоды к первым входам сумматора, выходы второго регистра подключены к первым входам сумматора, выходы третьего регистра подключены к входам второго блока задержек и через диоды к вторым входам сумматора, выходы четвертого регистра подключены к вторым входам сумматора, управляющим входом является вход триггера и объединенный с ним управляющий вход сумматора, первый выход триггера подключен к управляющим входам второго, третьего регистров и к управляющему входу первого блока ключей, второй выход триггера подключен к управляющим входам первого, четвертого регистров и к управляющему входу второго блока ключей, выходы сумматора, первого и второго блоков задержек поразрядно объединены и являются выходами блока удвоения отсчетов, первые блоки задержек идентичны, каждый содержит последовательно соединенные элемент И, первый, второй ключи, первый распределитель импульсов, второй распределитель импульсов и восемь регистров, 1-3 управляющими входами являются первый и второй входы элемента И и объединенные сигнальные входы первого и второго ключей, выход элемента И подключен к первому управляющему входу первого ключа и к второму управляющему входу второго ключа, выход первого ключа подключен к входу первого распределителя импульсов, выход второго ключа подключен к входу второго распределителя импульсов, выходы первого распределителя импульсов подключены к первым управляющим входам разрядов 1-8 регистров, начиная с первого разряда, последний выход подключен к второму управляющему входу первого и к первому управляющему входу второго ключей и через диод к первым управляющим входам последних разрядов 1-8 регистров, выходы второго распределителя импульсов подключены к первым управляющим входам разрядов 1-8 регистров в последовательности, начиная с последнего разряда регистра к первому разряду, последний разряд через диод подключен к первым управляющим входам первых разрядов 1-8 регистров и через диод подключен к второму управляющему входу второго ключа и к первому управляющему входу первого ключа, вторые (информационные) входы разрядов 1-8 регистров объединены и каждый подключен к своему из 1-8 информационных входов, выходы разрядов каждого из 1-8 регистров объединены и являются 1-8 выходами первого блока задержек, блок модуляции излучения включает первый и второй излучатели трех основных цветов из соответствующего числа светодиодов каждый и оптическую систему, входы первого излучателя подключены к выходам второго, четвертого, шестого блоков импульсных усилителей, входы второго излучателя подключены к выходам первого, третьего, пятого блоков импульсных усилителей, один излучатель расположен над другим и их излучающие плоскости находятся в задней фокальной плоскости оптической системы, в передней фокальной плоскости которой расположен отражатель первого пьезодефлектора, оптически соединенный с отражателем второго пьезодефлектора, суммирующий усилитель блока кадровой развертки содержит последовательно соединенные счетчик импульсов, дешифратор, ключ, формирователь импульсов и выходной усилитель, первым входом суммирующего усилителя является первый вход выходного усилителя, вторым входом является счетный вход счетчика импульсов, объединенный с сигнальным входом ключа, управляющим входом являются объединенные управляющий вход счетчика импульсов и первый управляющий вход ключа, выходом является выход выходного усилителя.

| ТЕЛЕВИЗИОННЫЙ ПРОЕКТОР | 1994 |

|

RU2099902C1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2003 |

|

RU2232481C1 |

| WO 9426065 A1, 10.11.1994 | |||

| US 6219110 A, 17.04.2001 | |||

| US 6057894 A, 05.05.2000. | |||

Авторы

Даты

2006-05-10—Публикация

2005-02-28—Подача