Изобретение относится к аппаратным устройствам компьютерного оборудования и используется для расширения функций персонального компьютера.

За прототип принят универсальный домашний персональный компьютер [1, с.26], содержащий системный блок, включающий платформу, объединяющую системную /материнскую/ плату, процессор и оперативную память [1, с.34], жесткий диск и контроллер [1, с.64], видеокарту [1, с.56], звуковую карту [1, с.72], дисковод, корпус с блоком питания и монитор на ЭЛТ [1, с.60], устройства ввода - клавиатуру и мышь, устройства вывода - модем и принтер. Для приема телевизионного сигнала и вывода его на монитор применяются встроенные в видеокарту TV-тюнеры, но они не отличаются хорошим качеством - изображение воспроизводится только в небольшом окне [2, с.54]. Помимо внутренних устройств для приема телесигнала существуют и внешние, которые подключаются к компьютеру через порт USB и воспроизводят телепередачи в "оконном" режиме [2, с.55]. Существуют и автономные внешние тюнеры, подключаемые не к компьютеру, а непосредственно между монитором и видеокартой. Компьютер им не нужен [2, с.55]. Автономные тюнеры обеспечивают лучшее качество изображения, их недостатком является невозможность ввода видеоизображения в компьютер. Недостатками прототипа являются: воспроизведение телепередач в "оконном" режиме /TV-тюнеры/ либо невозможность ввода телеизображения в компьютер /автономные внешние тюнеры/, к этим недостаткам добавляется невозможность приема встроенными и внешними тюнерами эфирного цифрового телесигнала [1, с. 496], а мониторы на ЭЛТ воспроизводят изображение только с аналового видеосигнала.

Цель изобретения - осуществление приема эфирного цифрового телесигнала и ввод видео и звуковой информации в компьютер для записи на жесткий диск и параллельно воспроизведение его на полном экране монитора.

Техническим результатом является прием эфирного цифрового телесигнала, воспроизведение его без потерь качества на полном экране монитора с параллельной записью в сжатой форме на жесткий диск. Результат достигается введением в компьютер цифрового монитора, телевизионной карты, расположенной в системном блоке, и запись на жесткий диск видеоинформации, сжатой отличным от существующих к настоящему времени способом. Вводимая телевизионная карта предназначается для совместной работы с цифровыми системами телевидения, а именно с цифровой системой телевидения высокой четкости по патенту №2194370 [3] либо аналогичными, выполняющей кодирование цветов 2:2:4 /R, G, B/ при частоте дискретизации видеосигналов 8, 75 МГц /ER, EG/, 17,5 МГц /EB/, информация о цветовых тонах производится верхней или нижней боковыми частотами и полярностью сигналов в коде, информация о яркости передается кодами амплитуд видеосигналов, число кодируемых отсчетов сигналов ER и EG в строке 700, EB - 1400, кодируемых строк в кадре 500, кадров 25, полей в кадре 2, коды видеосигналов 8-разрядные, коды звуковых сигналов 16-разрядные с частотой дискретизации 50 кГц, развертка растра чересстрочная, строчная и кадровая развертки без обратных ходов [3, с.2]. Телевизионная карта выполняет следующие функции: осуществляет прием одновременно двух радиосигналов, выделяет строчные /ССИ/ и кадровые /КСИ/ синхроимпульсы, отделяет коды двух звуковых сигналов стереосопровождения в звуковую карту компьютера, удваивает число отсчетов в строке видеосигналов ER и EG /1400/, удваивает число строк в кадре /1000/ и вводит коды видеосигналов одновременно двух строк в цифровой монитор, до соответствующей шине направляет сжатую цифровую видеоинформацию для записи на жесткий диск компьютера. Цифровой монитор выполняет электронно-оптическую развертку изображения по кодам с цифрового выхода видеокарты на матовом экране /без образования кодов в аналоговые видеосигналы/, удваивает число отсчетов в строке /800×2/ и число строк в кадре /600×2/, формирует построчный растр 1600×1200, производит развертку строк без обратных кодов. В режиме воспроизведения телевизионного изображения с телевизионной карты монитор выполняет электронно-оптическую развертку изображения на том же матовом экране, производит чересстрочную развертку кадра из двух полей /растр 1400×1000/, развертка строк и полей кадров без обратных ходов [3]. Запись видео и звуковой цифровой информации с телевизионной карты на жесткий диск компьютера выполняется с использованием интерфейса жесткого диска параллельного типа /IDE или SCSI/ после сжатия информации в блоке компрессии способом, отличным от MPEG-2. Сущность заявляемого изобретения в том, что в персональный компьютер, содержащий системный блок, включающий платформу, объединяющую системную плату, процессор и оперативную память, жесткий диск с контроллером, видеокарту, звуковую карту, дисковод, монитор, устройства ввода - клавиатуру и мышь, устройства вывода - модем и принтер, введены цифровой монитор, соответствующие входы которого подключены к соответствующим выходам видеокарты, телевизионная карта, расположенная в системном блоке, соответствующие выходы которой подключены к соответствующим входам цифрового монитора, звуковой карты, к входам контроллера жесткого диска, и блок компрессии, входы которого подключены к соответствующим выходам телевизионной карты, а выходы его подключены к соответствующим входам контроллера жесткого диска.

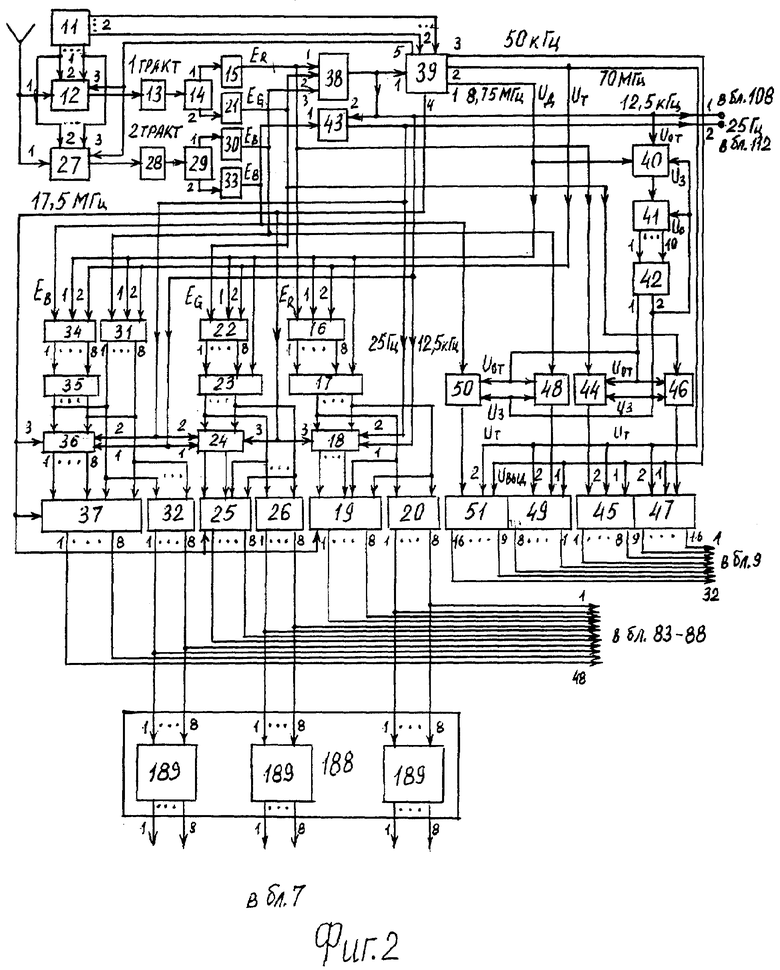

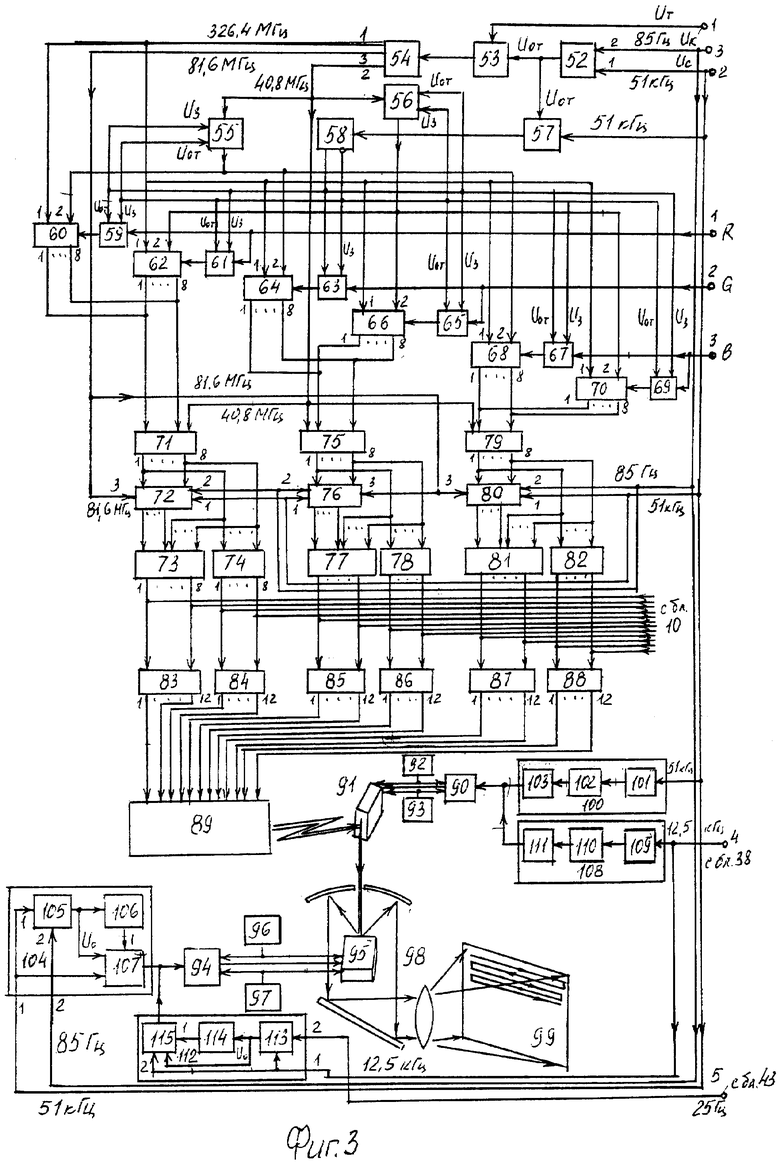

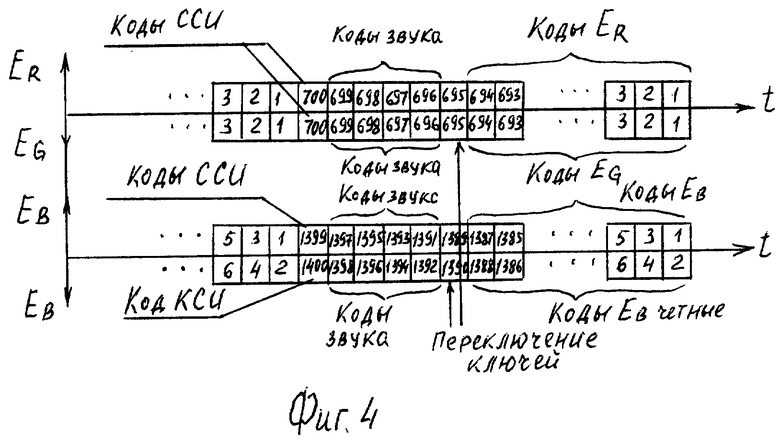

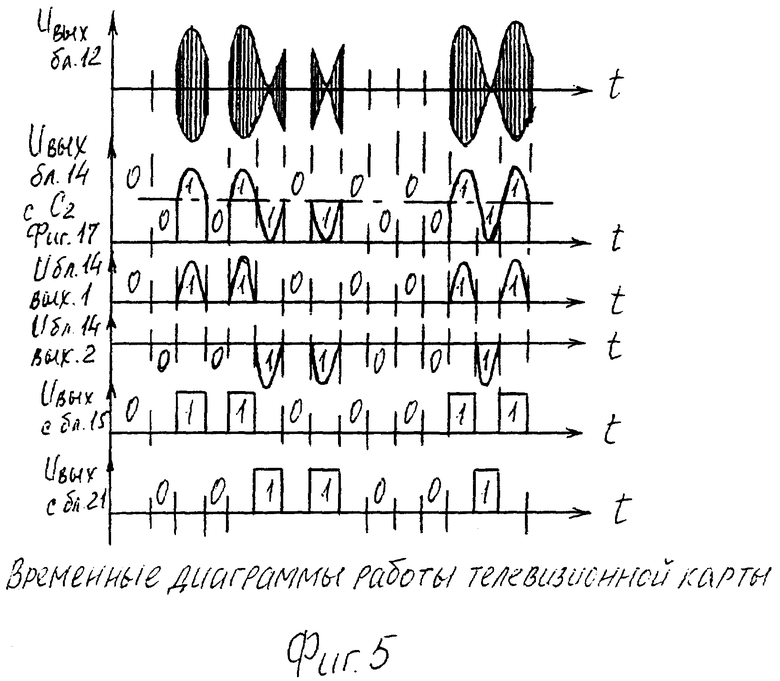

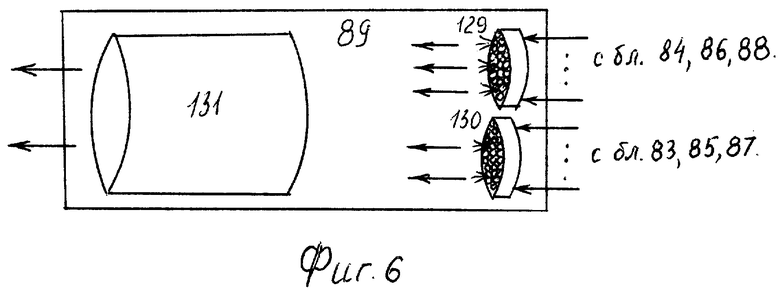

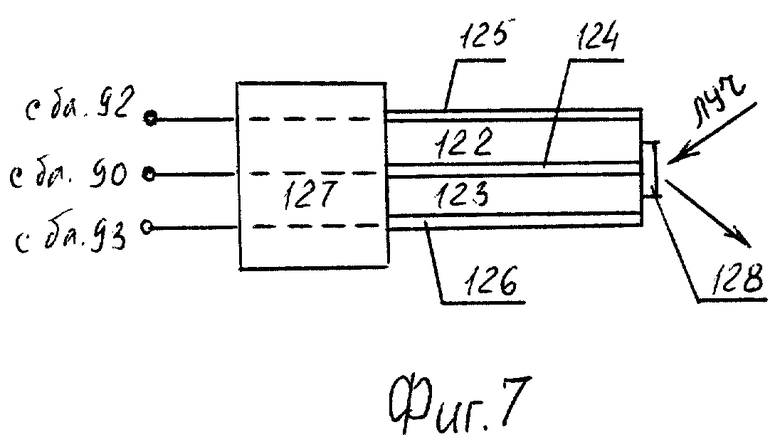

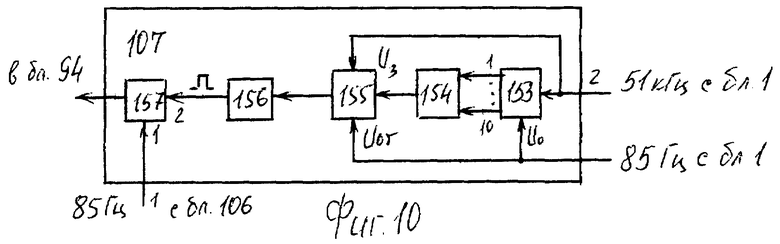

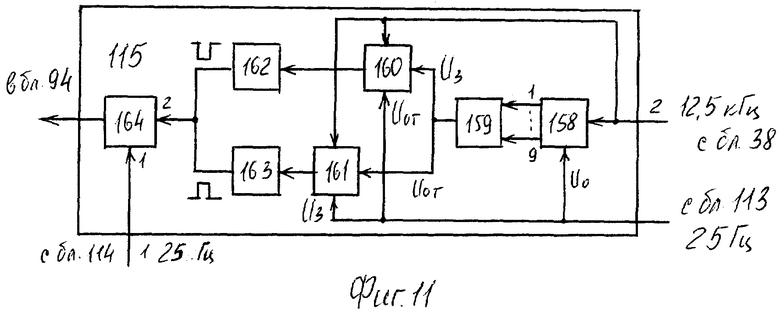

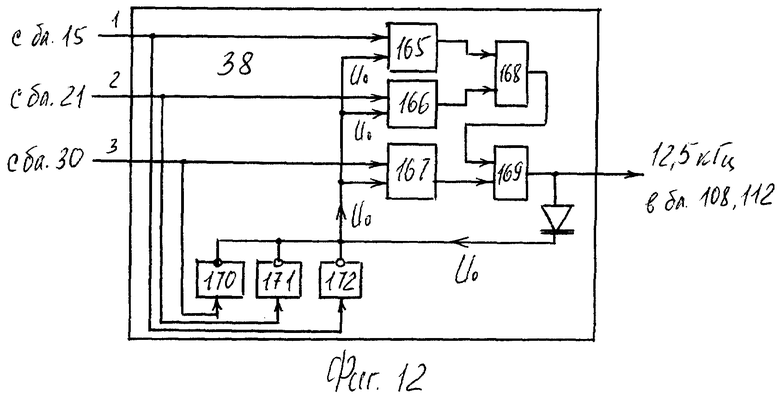

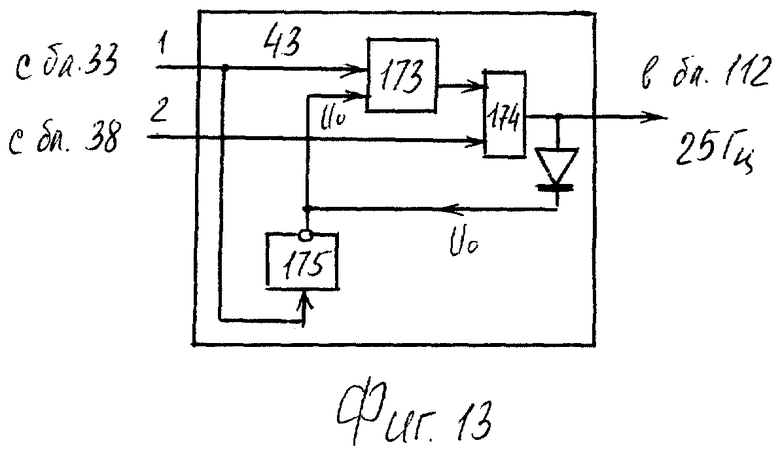

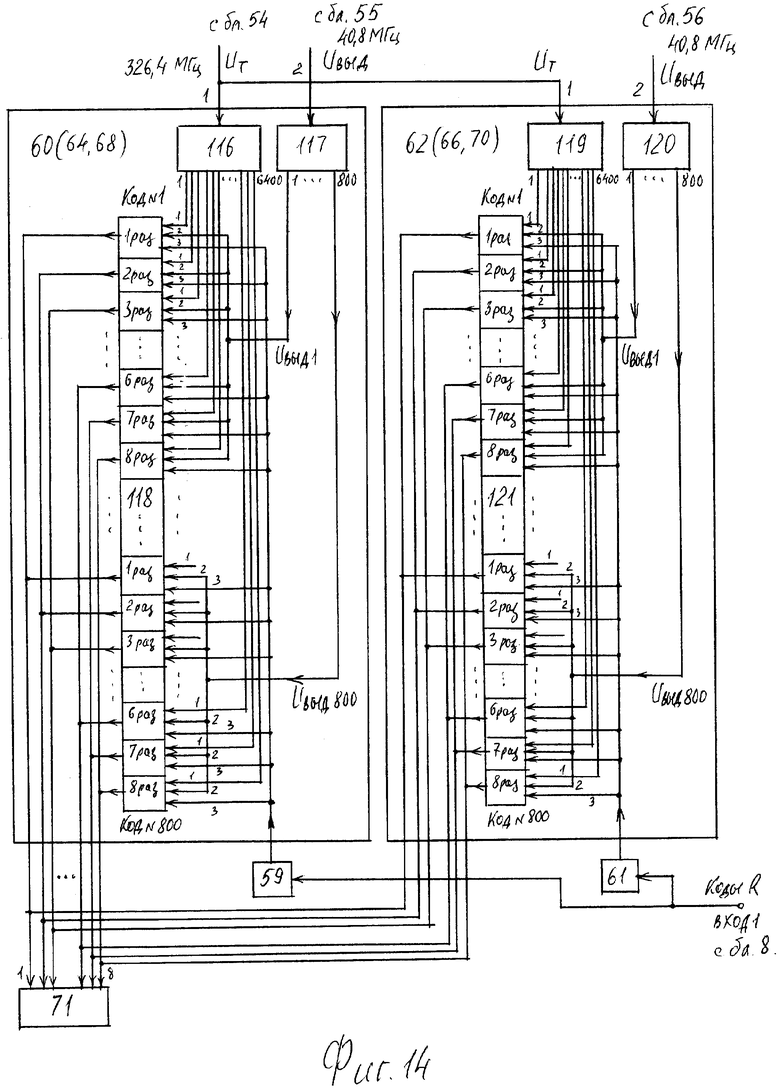

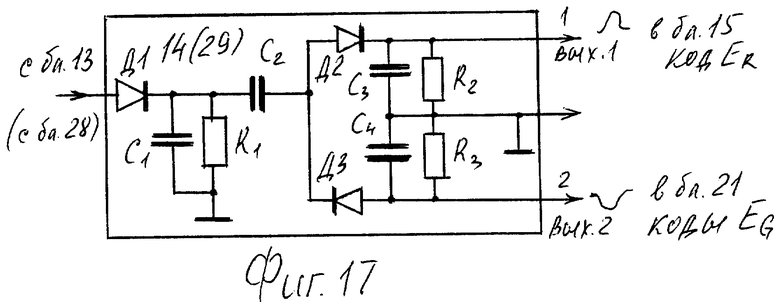

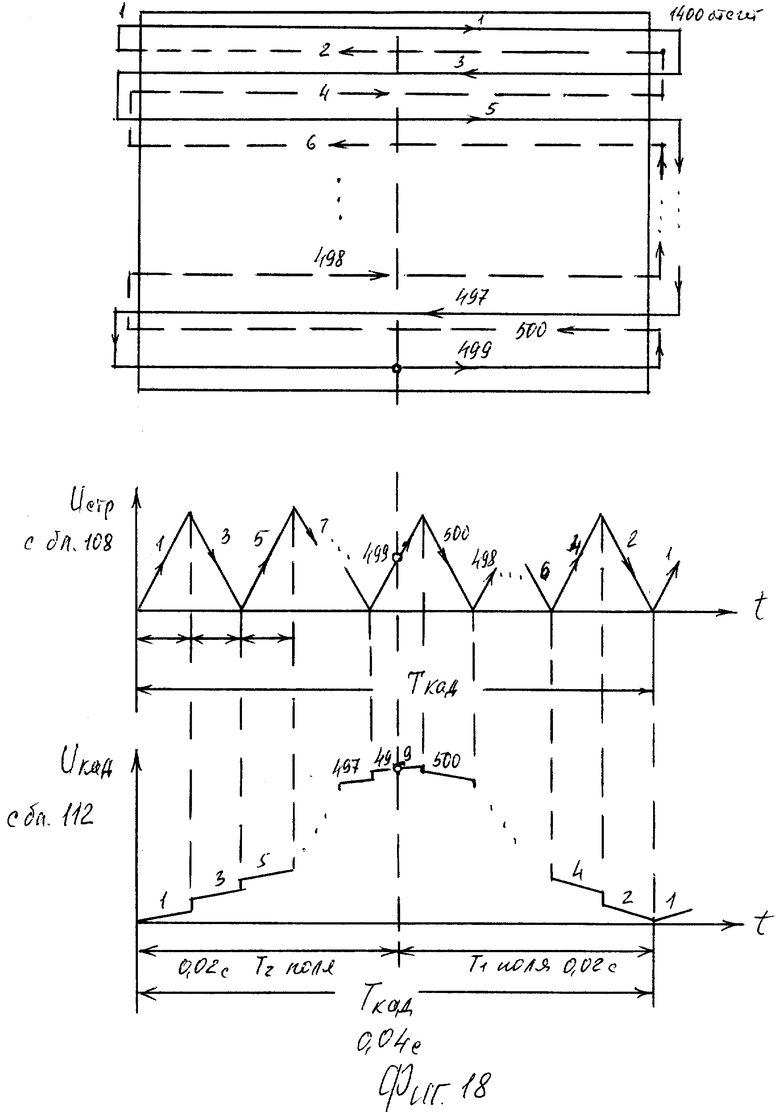

Структурная схема персонального компьютера представлена на фиг.1, функциональная схема телевизионной карты - на фиг.2, функциональная схема цифрового монитора - на фиг.3, порядок следования кодов в цифровом потоке в эфире - на фиг.4, временные диаграммы работы входного тракта телевизионной карты - на фиг.5, блок модуляции излучения - на фиг.6, конструкция пьезодефлектора - на фиг.7, блоки удвоения числа отсчетов - на фиг.8 и 9, суммирующие усилители - на фиг.10 и 11, схема выделения строчного синхроимпульса - на фиг.12, кадрового синхроимпульса - на фиг.13, первые и вторые накопители кодов - на фиг.14, первые блоки задержек - на фиг.15 и 16, принципиальная схема двухполярного амплитудного детектора - на фиг.17, развертка растра с телевизионной карты и виды управляющих напряжений - на фиг.18, развертка растра с видеокарты и виды управляющих напряжений - на фиг.19, кодер - на фиг.20, диаграммы сжатия цифрового потока - на фиг.21, функциональная схема декодера - на фиг.22.

Персональный компьютер включает /фиг.1/ системный блок 1, цифровой монитор 2, устройства ввода - клавиатуру 3 и мышь 4, устройства вывода - модем 5 и принтер 6, в системном блоке расположены контроллер 7 жесткого диска, управляющий всеми электромеханическими и электронными компонентами жесткого диска [1, с.302], видеокарта 8 с цифровым выходом на монитор, звуковая карта 9 [1, с.520] и телевизионная карта 10. Вводимая телевизионная карта 10 содержит /фиг.2/ антенну, блок 11 выбора программ телевещания, первый и второй тракты приема кодов видеосигналов, канал формирования управляющих сигналов и два канала выделения кодов звука. Первый тракт приема кодов видеосигналов включает блок 12 приема радиосигнала, усилитель 13 радиочастоты и двухполярный амплитудный детектор 14, канал видеосигнала ER, включающий последовательно соединенные первый формирователь 15 импульсов, регистр 16 видеосигнала ER, блок 17 удвоения отсчетов, первый блок 18 задержек и сумматор 19, и второй блок 20 задержек, канал видеосигнала EG, включающий второй формирователь 21 импульсов, регистр 22 видеосигнала EG, блок 23 удвоения отсчетов, первый блок 24 задержек и сумматор 25, и второй блок 26 задержек. Второй тракт приема кодов видеосигналов включает последовательно соединенные блок 27 приема радиосигнала, усилитель 28 радиочастоты и двухполярный амплитудный детектор 29, и два канала видеосигнала EB. Первый канал видеосигнала EB содержит третий формирователь 30 импульсов, первый регистр 31 видеосигнала ЕВ и второй блок 32 задержек, второй канал видеосигнала ЕВ включает четвертый формирователь 33 импульсов, второй регистр 34 видеосигнала ЕВ, блок 35 задержек, первый блок 36 задержек и сумматор 37. Канал формирования управляющих сигналов включает последовательно соединенные блок 38 выделения строчного синхроимпульса /ССИ/, синтезатор 39 частот, ключ 40, счетчик 41 импульсов и дешифратор 42, и блок 43 выделения кадрового синхроимпульса /КСИ/. Первый канал выделения кодов звука включает последовательно соединенные первый ключ 44 и первый блок 45 регистров звука, второй ключ 46 и второй блок 47 регистров звука, второй канал выделения кодов звука включает третий ключ 48 и третий блок 49 регистров звука, четвертый ключ 50 и четвертый блок 51 регистров звука. Цифровой монитор 2 включает /фиг.3/ последовательно соединенные элемент И 52, первый ключ 53, делитель 54 частоты и второй ключ 55, третий ключ 53, четвертый ключ 57 и триггер 58, пятый ключ 59 и первый накопитель 60 кодов R, шестой ключа 61 и второй накопитель 62 кодов R, седьмой ключ 63 и первый накопитель 64 кодов G, восьмой ключ 65 и второй накопитель 66 кодов G, девятый ключ 67 и первый накопитель 68 кодов В, десятый ключ 69 и второй накопитель 70 кодов В, последовательно соединенные блок 71 удвоения отсчетов видеосигнала ЕR, первый блок задержек 72 и первый сумматор 73, и второй блок 74 задержек, последовательно соединенные блок 75 удвоения отсчетов видеосигнала ЕG, первый блок 76 задержек и второй сумматор 77, и второй блок 78 задержек, последовательно соединенные блок 79 удвоения отсчетов видеосигнала ЕВ, первый блок 80 задержек и третий сумматор 81, и второй блок 82 задержек, первый 83, второй 84, третий 85, четвертый 86, пятый 87 и шестой 88 блоки импульсных усилителей, блок 89 модуляции излучения, последовательно соединенные первый усилитель 90 и первый пьезодефлектор 91 с отражателем на торце, первый источник 92 положительного опорного напряжения, второй источник 93 отрицательного опорного напряжения, последовательно соединенные второй усилитель 94 и второй пьезодефлектор 95 с отражателем на торце, третий источник 96 положительного опорного напряжения, четвертый источник 97 отрицательного опорного напряжения, проекционную оптическую систему 98, во внешней фокальной плоскости которой расположен матовый экран 99, первый блок 100 строчной развертки из последовательно соединенных делителя 101 частоты /2:1/, задающего генератора 102 и выходного каскада 103, первый блок 104 кадровой развертки из элемента И 105, задающего генератора 106 и суммирующего усилителя 107, второй блок 108 строчной развертки из последовательно соединенных делителя 109 частоты /2:1/, задающего генератора 110 и выходного каскада 111, второго блока 112 кадровой развертки из элемента И 113, задающего генератора 114 и суммирующего усилителя 115.

Первые накопители 60, 64, 68 кодов идентичны /фиг.14/, каждый включает первый распределитель 116 импульсов, второй распределитель 117 импульсов и регистр 118 на 800 кодов строки /800 байтов/, вторые накопители 62, 66, 70 кодов идентичны /фиг.14/, каждый включает первый распределитель 119 импульсов, второй распределитель 120 импульсов и регистр 121 на 800 кодов строки /800 байтов/. Информационные входы накопителей 60 и 62 кодов R через свои ключи 59, 61 объединены и являются 1-ым информационным входом цифрового монитора /фиг.3/, входы накопителей 64, 66 кодов G через ключи 63 и 65 объединены и являются 2-ым информационным входом монитора, входы накопителей 68, и 70 кодов В через ключи 67, 69 объединены и являются 3-им информационным входом монитора. Первые управляющие /тактовые/ входы всех накопителей кодов объединены и подключены к первому входу /326,4 МГц/ делителя 54 частоты, вторые управляющие входы накопителей 60, 64, 68 кодов объединены и подключены к выходу второго ключа 55, вторые управляющие входы накопителей 62, 66, 70 объединены и подключены к выходу третьего ключа 56. Пьезодефлекторы 91 и 95 являются /фиг.7/ торцевыми биморфными пьезоэлементами со световым отражателем на свободном торце. Конструктивно выполнены [5, с.118] из первой 122 и второй 123 пьезопластин, внутреннего электрода 124, первого 125 и второго 126 внешних электродов. Один конец пьезопластин закреплен в держателе 127, на свободн6ом торце расположен световой отражатель 128.

Блок 89 модуляции излучения /фиг.8/ включает первый излучатель 129 трех основных цветов, второй излучатель 130 трех основных цветов и оптическую систему 131. Один излучатель расположен над другим. Излучающая плоскость излучателей 129, 130 расположена в задней фокальной плоскости оптической системы, в передней фокальной плоскости которой распложен отражатель первого пьезодефлектора 91 /Фиг.3/. Излучающие стороны излучателей оптически соединены через отражатель первого 91 и второго 95 пьезодефлекторов и проекционную оптическую систему 98 с матовым экраном 99. Входы первого излучателя 129 подключены к выходам блоков 84, 86, 88 импульсных усилителей, входы второго излучателя 130 подключены к выходам блоков 83, 85, 87 импульсных усилителей. Проекционная оптическая система 98 представлена зеркально-линзовой системой [11, с.370] и включает /фиг.3/ сферическое зеркало, плоское зеркало с наклоном 45° относительно оптической оси сферического зеркала и корректирующую линзу. Плоское зеркало сокращает прямое расстояние до экрана 99 и позволяет изменить направление хода луча в нужном направлении. Кратность увеличения проекционной оптической системы задается требуемой величиной изображения на экране 99.

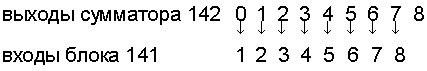

Блоки 17, 23 удвоения отсчетов идентичны и каждый /фиг.8/ включает триггер 132, первый 133 и второй 134 блоки ключей, первый 135, второй 136, третий 137, четвертый 138 регистры, первый 139, второй 140, третий 141 блоки задержек, каждый из которых включает по 8 элементов задержек, сумматор 142 и соответствующее число диодов. Информационным входом блока 17 /23/ являются объединенные поразрядно входы блоков 133, 134 ключей, управляющим входом является вход триггера 132. Выходом блока 17 являются объединенные поразрядно выходы блоков 139, 140, 141 задержек. Блоки 139, 140 выполняют задержку кодов на 114,28 нс  блок 141 выполняет задержку кодов на 33,14 нс /15,14-24/. Блоки 71, 75, 79 удвоения отсчетов идентичны /фиг.9/, каждый включает триггер 143, первый 144, второй 145 блоки ключей, первый 146, второй 147, третий 148, четвертый 149 регистры, сумматор 150, первый 151 и второй 152 блоки задержек, каждый из которых задерживает коды на 24,5 нс. Суммирующий усилитель 107 включает /фиг.10/ последовательно соединенные счетчик 153 импульсов, дешифратор 154, ключ 155, формирователь 156 импульсов и выходной усилитель 157. Первым информационным входом является первый вход выходного усилителя 157, вторым - счетный вход счетчика 153 импульсов, управляющим входом являются объединенные входы: управляющий вход счетчика 153 и первый управляющий вход ключа 155. Суммирующий усилитель 115 /фиг.11/ включает счетчик 158 импульсов, дешифратор 159, первый 160, второй 161 ключи, первый 162, второй 163 формирователи импульсов и выходной усилитель 164. Входами являются: первым - первый вход выходного усилителя 164, вторым - счетный вход счетчика 158 импульсов, управляющим входом являются объединенные входы управляющего входа счетчика 158, первого управляющего входа второго ключа. Блок 38 выделения строчного синхроимпульса /фиг.12/ включает первый 165, второй 166, третий 167 счетчики импульсов, первый 168 и второй 169 элементы И, первый - третий 170, 171, 172 элементы НЕ и диод. Входами являются счетные входы счетчиков импульсов, выходом - выход второго элемента И 169. Блок 43 выделения кадрового синхроимпульса /фиг.13/ включает счетчик 173 импульсов, элемент И 174, элемент НЕ 175 и диод. Входами являются вход счетчика 173 и второй вход элемента И 174. Выходом является выход элемента И 174.

блок 141 выполняет задержку кодов на 33,14 нс /15,14-24/. Блоки 71, 75, 79 удвоения отсчетов идентичны /фиг.9/, каждый включает триггер 143, первый 144, второй 145 блоки ключей, первый 146, второй 147, третий 148, четвертый 149 регистры, сумматор 150, первый 151 и второй 152 блоки задержек, каждый из которых задерживает коды на 24,5 нс. Суммирующий усилитель 107 включает /фиг.10/ последовательно соединенные счетчик 153 импульсов, дешифратор 154, ключ 155, формирователь 156 импульсов и выходной усилитель 157. Первым информационным входом является первый вход выходного усилителя 157, вторым - счетный вход счетчика 153 импульсов, управляющим входом являются объединенные входы: управляющий вход счетчика 153 и первый управляющий вход ключа 155. Суммирующий усилитель 115 /фиг.11/ включает счетчик 158 импульсов, дешифратор 159, первый 160, второй 161 ключи, первый 162, второй 163 формирователи импульсов и выходной усилитель 164. Входами являются: первым - первый вход выходного усилителя 164, вторым - счетный вход счетчика 158 импульсов, управляющим входом являются объединенные входы управляющего входа счетчика 158, первого управляющего входа второго ключа. Блок 38 выделения строчного синхроимпульса /фиг.12/ включает первый 165, второй 166, третий 167 счетчики импульсов, первый 168 и второй 169 элементы И, первый - третий 170, 171, 172 элементы НЕ и диод. Входами являются счетные входы счетчиков импульсов, выходом - выход второго элемента И 169. Блок 43 выделения кадрового синхроимпульса /фиг.13/ включает счетчик 173 импульсов, элемент И 174, элемент НЕ 175 и диод. Входами являются вход счетчика 173 и второй вход элемента И 174. Выходом является выход элемента И 174.

Первые блоки 18, 24, 36 задержек идентичны, каждый содержит /фиг.15/ элемент И 176, первый 177, второй 178 ключи, первый 179, второй 180 распределители импульсов и восемь регистров 1811-1818. Каждый из блоков принимает 1400 кодов строки и производит задержку их на длительность строки 80 мкс:  Первые блоки 72, 76, 80 задержек идентичны, каждый содержит /фиг.16/элемент И 182, первый 183, второй 184 ключи, первый 185, второй 186 распределители импульсов и восемь регистров 1871-1878. Каждый из блоков 72, 76, 80 производит задержку кодов на длительность строки 19,6 мкс:

Первые блоки 72, 76, 80 задержек идентичны, каждый содержит /фиг.16/элемент И 182, первый 183, второй 184 ключи, первый 185, второй 186 распределители импульсов и восемь регистров 1871-1878. Каждый из блоков 72, 76, 80 производит задержку кодов на длительность строки 19,6 мкс:  Передатчиком цифровой системы телевидения [3, с.19] в эфир излучаются два радиосигнала /фиг.5/. Первый радиосигнал содержит коды видеосигнала ER, символы единиц в которых представляются положительными полусинусоидами верхней боковой частоты, и коды видеосигнала EG, символы единиц в которых представляются отрицательными полусинусоидами той же верхней боковой частоты /700 МГц/. Второй радиосигнал содержит коды видеосигнала ЕВ, причем символы единиц в нечетных кодах сигнала ЕВ представляются положительными полусинусоидами нижней боковой частоты, символы единиц в четных кодах представляются полусинусоидами /фиг.4/ той же нижней боковой частоты /560 МГц/. Несущая частота одна 630 МГц. Порядок следования цифровых потоков при приеме радиосигналов на фиг.4. Оба радиосигнала принимаются блоками 12 и 27 приема радиосигнала /фиг.2/, которые являются селекторами дециметрового диапазона /СКД/ с электронной настройкой и выполняют прием радиосигналов в диапазоне 560-790 МГц. Каждый блок представляет собой первую половину СКД-24 [6, с.132] и включает входную цепь, усилитель радиочастоты, а из преобразователя частоты используется смеситель /на транзисторе VT2 [6, рис.4.2]/. Полосовой фильтр усилителя радиочастоты в каждом диапазоне перестраивается подачей напряжения смещения на варикапы с блока 11 выбора программ телевещания. Усиленный радиочастотный сигнал через петлю связи [6, с.132] поступает на эмиттер смесителя /VT2/, на который с синтезатора 39 частот /фиг.2/ подается несущая частота /630 МГц/, необходимая для детектирования однополосного сигнала [7, с.146], несущая данной программы. Сигнал с коллектора VT2, являющийся выходным сигналом блока 12 /27/, поступает на вход усилителя 13 /28/ радиочастоты, где усиливается до необходимой величины и поступает на вход двухполярного амплитудного детектора 14 /29/. Временные диаграммы работы входного тракта телевизионной карты на фиг.5. Вторые входы синтезатора 39 частот подключены к второй группе выходов блока 11. При включении программы передач сигналы со вторых выходов блока 11 определяют выход соответствующей несущей частоты с блока 39 /выход 5/ на третьи входы блоков 12 и 27. С переходом на другую программу передач на третьи входы блока 12 и 27 поступят синусоидальные колебания другой несущей частоты, соответственно несущей частоте в передатчике передающей стороны. Двухполярные амплитудные детекторы 14 и 29 выполнены по схеме [8, с.112] /фиг.17/. Диод Д1 выделяет положительную огибающую модулирующего синусоидального сигнала. Диод Д2 из модулирующей выделяет огибающие положительных полусинусоид - символы единиц кодов ER /фиг.17, выход 1/; диод Д3 из модулирующей выделяет огибающие отрицательных полусинусоид - символы единиц кодов EG /фиг.17, выход 2/. С первого выхода блока 14 продетектированные положительные полусинусоиды поступают на вход формирователя 15 импульсов. Продетектированные отрицательные полусинусоиды той же частоты поступают на вход второго формирователя 21 импульсов. Аналогичный процесс и в блоке 29. Формирователи 14, 21, 30, 33 импульсов идентичны, выполнены по схеме несимметричного триггера с эмиттерной связью [9, с.209], формирующие прямоугольные импульсы из гармонически изменяющихся сигналов. С блоков 15, 21, 30, 33 импульсы имеют одну полярность и длительность, равные по амплитуде и длительности импульсам, принятым на передающей стороне в системе телевидения.

Передатчиком цифровой системы телевидения [3, с.19] в эфир излучаются два радиосигнала /фиг.5/. Первый радиосигнал содержит коды видеосигнала ER, символы единиц в которых представляются положительными полусинусоидами верхней боковой частоты, и коды видеосигнала EG, символы единиц в которых представляются отрицательными полусинусоидами той же верхней боковой частоты /700 МГц/. Второй радиосигнал содержит коды видеосигнала ЕВ, причем символы единиц в нечетных кодах сигнала ЕВ представляются положительными полусинусоидами нижней боковой частоты, символы единиц в четных кодах представляются полусинусоидами /фиг.4/ той же нижней боковой частоты /560 МГц/. Несущая частота одна 630 МГц. Порядок следования цифровых потоков при приеме радиосигналов на фиг.4. Оба радиосигнала принимаются блоками 12 и 27 приема радиосигнала /фиг.2/, которые являются селекторами дециметрового диапазона /СКД/ с электронной настройкой и выполняют прием радиосигналов в диапазоне 560-790 МГц. Каждый блок представляет собой первую половину СКД-24 [6, с.132] и включает входную цепь, усилитель радиочастоты, а из преобразователя частоты используется смеситель /на транзисторе VT2 [6, рис.4.2]/. Полосовой фильтр усилителя радиочастоты в каждом диапазоне перестраивается подачей напряжения смещения на варикапы с блока 11 выбора программ телевещания. Усиленный радиочастотный сигнал через петлю связи [6, с.132] поступает на эмиттер смесителя /VT2/, на который с синтезатора 39 частот /фиг.2/ подается несущая частота /630 МГц/, необходимая для детектирования однополосного сигнала [7, с.146], несущая данной программы. Сигнал с коллектора VT2, являющийся выходным сигналом блока 12 /27/, поступает на вход усилителя 13 /28/ радиочастоты, где усиливается до необходимой величины и поступает на вход двухполярного амплитудного детектора 14 /29/. Временные диаграммы работы входного тракта телевизионной карты на фиг.5. Вторые входы синтезатора 39 частот подключены к второй группе выходов блока 11. При включении программы передач сигналы со вторых выходов блока 11 определяют выход соответствующей несущей частоты с блока 39 /выход 5/ на третьи входы блоков 12 и 27. С переходом на другую программу передач на третьи входы блока 12 и 27 поступят синусоидальные колебания другой несущей частоты, соответственно несущей частоте в передатчике передающей стороны. Двухполярные амплитудные детекторы 14 и 29 выполнены по схеме [8, с.112] /фиг.17/. Диод Д1 выделяет положительную огибающую модулирующего синусоидального сигнала. Диод Д2 из модулирующей выделяет огибающие положительных полусинусоид - символы единиц кодов ER /фиг.17, выход 1/; диод Д3 из модулирующей выделяет огибающие отрицательных полусинусоид - символы единиц кодов EG /фиг.17, выход 2/. С первого выхода блока 14 продетектированные положительные полусинусоиды поступают на вход формирователя 15 импульсов. Продетектированные отрицательные полусинусоиды той же частоты поступают на вход второго формирователя 21 импульсов. Аналогичный процесс и в блоке 29. Формирователи 14, 21, 30, 33 импульсов идентичны, выполнены по схеме несимметричного триггера с эмиттерной связью [9, с.209], формирующие прямоугольные импульсы из гармонически изменяющихся сигналов. С блоков 15, 21, 30, 33 импульсы имеют одну полярность и длительность, равные по амплитуде и длительности импульсам, принятым на передающей стороне в системе телевидения.

Единицы в кодах представлены наличием импульсов, нули - их отсутствием. Порядок работы телевизионной карты определяется сигналами управления, вырабатываемыми каналом формирования управляющих сигналов. Задающая роль принадлежит строчному синхроимпульсу /ССИ/, коды которых выделяются из потока кодов блоком 38 выделения строчного ССИ. Условием выдачи ССИ является одновременный приход с трех формирователей 15, 21, 30 импульсов кодов из восьми единиц 11111111 на входы блока 38. Во всех кодах строк, кроме кода ССИ - отсчеты 700 и 1399 /фиг.4/, всегда будет присутствовать хотя бы один нуль, тем более в кодах трех цветных сигналах одновременно. При наличии хотя бы одного нуля в трех кодах элемент НЕ /фиг.12/ обнулит счетчики в блоке 38. С приходом трех кодов 11111111 блок 38 выдает на выходе импульс, являющийся импульсом ССИ, частота их 12,5 кГц. ССИ открывает ключ 40, поступает на второй вход блока 43, поступает на первый вход синтезатора 39 частоты, являясь импульсом синхронизации частоты в синтезаторе 39 частот, по нему производится подстройка частоты синтезатора 39 под частоту и фазу задающего генератора передающей стороны и поступает в блок 108 строчной развертки и первый вход блока 112 кадровой развертки в цифровом мониторе /фиг.3/. Блок 43 выделяет кадровые синхроимпульсы /КСИ/ в момент прихода на 1-й его вход кода 11111111 с блока 33 и на 2-й вход импульса ССИ с блока 38. КСИ 25 Гц поступает на вторые входы блоков 18, 24, 36 и в блок 112 монитора 2. Синтезатор 39 выдает с первого выхода импульсы дискретизации 8,75 МГц, с второго - тактовые импульсы 70 МГц, с третьего - импульсы дискретизации 50 кГц сигнала звука, с четвертого - импульсы дискретизации /двойной/ кодов видеосигналов 17,5 МГц, с пятого - синусоидальные колебания требуемой несущей частоты. Коды видеосигнала ER с выхода формирователя 15 импульсов в последовательном виде поступают на вход регистра 16, заполняя разряды которого приобретают параллельный вид, в котором они выдаются импульсами 8,75 МГц на входы блока 17 удвоения отчетов. Блок 17 выполняет удвоение отсчетов видеосигнала ER в строке получением промежуточных /средних/ отсчетов между каждым прошедшим кодом и каждым следующим за ним. Частота дискретизации становится 17,5 МГц. В блоке 17 выполняется сложение предыдущего и последующего кодов и код суммы делится на два. С блока 17 коды уже с частотой 17,5 МГц поступают во второй блок 20 задержек, на первые входы сумматора 19 и в первый блок 18 задержек, который выполняет задержку каждого кода на длительность строки /80 мкс/. На вторые входы сумматора 19 поступают код, задержанный на 80 мкс, на первые входы поступает код текущей строки. Сумматор 19 выполняет сложение кодов, а код суммы делится попалам. Код суммы делится на два соответствующим подключением выходов сумматора 19 к входам следующего блока так, чтобы отбрасывался младший разряд кода суммы, как делится десятичное число на десять. Код с выхода блока 19 является промежуточным кодом /средним/ между прошедшим и следующим за ним кодом. Коды сигнала EG с выхода блока 21 проходят тот же процесс. Коды сигнала EB с формирователя 30 импульсов поступают в первый регистр 31 видеосигнала EB, с него в параллельном виде поступают на вход блока 36 для задержки на 80 мкс, а также на первые входы сумматора 37 и на входы блока 32 задержек /24 нс/. Коды с формирователя 33 импульсов поступают во второй регистр 34 видеосигнала EB и через блок 35 задержек, задерживающий код на 57,14 нс для восстановления следования четного кода за нечетным /в тракте они идут параллельно, фиг.4/, поступает в блок 36 задержек, задерживающий код на 80 мкс, поступает на вторые входы сумматора 37. После блока 35 коды с регистра 34 поступают и в блок 32 задержек, последовательность поступления кодов в который составляет 17,5 МГц /через 57,14 нс/. Блок 36 выполняет задержку поступающих кодов с блока 35 и блока 31 на 80 мкс. Сумматоры 19, 25, 37 идентичны и являются микросхемами К555ИМ6 с временем сложения 24 нс [10, с.258]. Для компенсации задержки кодов при сложении сумматорами применяются блоки 20, 26, 31 задержек, задерживающие коды на 24 нс /на длительность сложения/. Поэтому с выходов сумматоров и блоков 20, 26, 32 задержек коды одних отсчетов в строках следуют синхронно.

Работа блока 17 /23/ удвоения отсчетов, фиг.8.

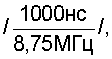

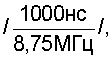

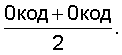

Блок 17 /23/ производит удвоение отсчетов в строке получением промежуточного кода между прошедшим и следующим за ним, увеличивая в 2 раза частоту следования кодов /17,5 МГц/. Период следования кодов на входе блока 17 составляет 114,28 нс  на выходе 57,14 нс

на выходе 57,14 нс  Каждый код используется два раза: первый раз как предыдущий, второй раз как последующий, поэтому блок 17 имеет четыре регистра 135, 136, 137, 138. С поступлением первого импульса /8,75 МГц/ на вход триггера 132 с его первого выхода сигнал Uвыд1 выдает одновременно "0 код" из регистра 136 и "0 код" из регистра 137, при выдаче регистры и обнуляются. Код с регистра 136 поступает прямо на первые входы сумматора 142, с регистра 137 поступает на входы блока 140 задержек, задерживающий код на 114, 28 нс, и через диоды поступает на вторые входы сумматора 142. Сигнал Uвыд1 также открывает ключи в блоке 133, через которые первый код "1 код" поступает в регистры 135, 136. В это время сумматор 142 за 24 нс выполняет сложение кодов 0 код+0 код. Код суммы выдается в блок 141 задержек, задерживающий код на 33,14 нс /57,14-24/. Выходы сумматора и входы блока 141 подключены так, что при переходе кода суммы в блок 141 опускается младший разряд, т.е. выполняется деление двоичного кода на два:

Каждый код используется два раза: первый раз как предыдущий, второй раз как последующий, поэтому блок 17 имеет четыре регистра 135, 136, 137, 138. С поступлением первого импульса /8,75 МГц/ на вход триггера 132 с его первого выхода сигнал Uвыд1 выдает одновременно "0 код" из регистра 136 и "0 код" из регистра 137, при выдаче регистры и обнуляются. Код с регистра 136 поступает прямо на первые входы сумматора 142, с регистра 137 поступает на входы блока 140 задержек, задерживающий код на 114, 28 нс, и через диоды поступает на вторые входы сумматора 142. Сигнал Uвыд1 также открывает ключи в блоке 133, через которые первый код "1 код" поступает в регистры 135, 136. В это время сумматор 142 за 24 нс выполняет сложение кодов 0 код+0 код. Код суммы выдается в блок 141 задержек, задерживающий код на 33,14 нс /57,14-24/. Выходы сумматора и входы блока 141 подключены так, что при переходе кода суммы в блок 141 опускается младший разряд, т.е. выполняется деление двоичного кода на два:

Разряд 0 означает разряд переноса при сумме кодов. Процесс получения промежуточных кодов на фиг.8. При удвоении частоты следования кодов в 17,5 МГц период их следования 57,14 нс. Сложение за 24 нс, поэтому блок 141 должен задержать код еще на 33,14 нс. По истечении этой задержки с выхода блока 141 следует код №1  Второй код №2 "0 код" следует с блока 140 задержек. Он задерживает код на 114, 28 нс, но первая половина задержки 57,14 нс приходится на сложение в сумматоре и задержку в блоке 141.

Второй код №2 "0 код" следует с блока 140 задержек. Он задерживает код на 114, 28 нс, но первая половина задержки 57,14 нс приходится на сложение в сумматоре и задержку в блоке 141.

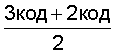

Поэтому код №2 "0 код" следует за кодом №1 через 57,14 нс. С приходом второго импульса в триггер 132 сигнал Uвыд2 с второго выхода выдает "1 код" из регистра 135 через диоды в сумматор 142 и напрямую в блок 139 задержки, задерживающий код на 114,28 нс. Из регистра 138 сигнал Uвыд2 выдает код "0 код" в сумматор 142. Идет сложение 1 код+0 код, код суммы выдается из сумматора, делится попалам и выдается с блока 141 код №3  Через 57,14 нс с блока 139 следует код №4 "1 код". Сигнал Uвыд2 также открывает ключи в блоке 134, и код "2 код" поступает в регистры 137, 138. С приходом 3-го импульса в триггер 132 сигнал Uвыд3 с первого выхода триггера выдает с регистра 137 "2 код" через диоды на вторые входы сумматора 142 и в блоки 140 задержки. Uвыд3 выдает с регистра 136 "1 код" в сумматор 142, идет сложение 2 код + 1 код, деление на 2, и с выхода блока 141 следует код №5

Через 57,14 нс с блока 139 следует код №4 "1 код". Сигнал Uвыд2 также открывает ключи в блоке 134, и код "2 код" поступает в регистры 137, 138. С приходом 3-го импульса в триггер 132 сигнал Uвыд3 с первого выхода триггера выдает с регистра 137 "2 код" через диоды на вторые входы сумматора 142 и в блоки 140 задержки. Uвыд3 выдает с регистра 136 "1 код" в сумматор 142, идет сложение 2 код + 1 код, деление на 2, и с выхода блока 141 следует код №5  а через 57,14 нс с блока 140 следует код №6 "2 код". Сигнал Uвыд3 открывает блок 133, и "3 код" поступает в регистры 135, 136. С приходом четвертого импульса в триггер 132 сигнал Uвыд4 с второго выхода триггера выдает "3 код" их регистра 138 "2 код" в сумматор 142. Следует сложение 3 код + 2 код, давление на 2, и код №7

а через 57,14 нс с блока 140 следует код №6 "2 код". Сигнал Uвыд3 открывает блок 133, и "3 код" поступает в регистры 135, 136. С приходом четвертого импульса в триггер 132 сигнал Uвыд4 с второго выхода триггера выдает "3 код" их регистра 138 "2 код" в сумматор 142. Следует сложение 3 код + 2 код, давление на 2, и код №7  следует с блока 141. За ним через 57,14 нс следует с блока 139 код №8 "3 код". Далее эти процессы повторяются. Сумматоры в блоках 17 и 23 представляются микросхемами К555ИМ6. Блоки 18, 24, 36 /фиг.15/ участвуют в формировании отсчетов промежуточных строк, задерживая коды на длительность строки, 80 мкс. А так как развертка строк в растре идет встречно, необходимо при развертке одних строк выдавать коды с сумматоры /19, 25, 37/ в последовательности с 1-го к 1400, а при развертке других строк, наоборот, с 1400 кода к 1-му. 1400 кодов с блока 17 /23, 35/ поступают последовательно в восемь регистров 1811-8. Каждый регистр 181 включает по 1400 разрядов. Причем коды по разрядам располагаются: первые разряды кодов в регистре 1811, вторые - в регистре 1812..., восьмые - в регистре 1818. Если смотреть на фиг.15, расположение идет как бы по горизонтали. При сложении в сумматоре кодов предыдущей строки с кодами последующей строки /фиг.15 вверху/, коды которой уже были задержаны на 80 мкс, выдача кодов из регистров 1811-8 идет не с 1-х разрядов, а с 1400-х, т.к. строка идет навстречу предыдущей. Это выполняется подключением выходов второго распределителя 180 импульсов к управляющим входам разрядов регистров в обратном порядке: к 1-му разрядам регистров 1400-го выхода, а к 1400-ым разрядам 1-го выхода. При сложении кодов 3 строки с кодами 5 строки выдача кодов в прямом порядке с распределителя 179 импульсов, выходы которого подключены к управляющим входам разрядов в прямом порядке. Коды с блоков 20, 26, 32 являются кодами текущих 500 строк и поступают в параллельном виде в блоки 84, 86, 88 импульсных усилителей в цифровом мониторе 2 /фиг.3/. Коды с блоков 19, 25, 37 являются кодами промежуточных /средних/ 500 строк и поступают в блоки 83, 85, 87 импульсных усилителей в цифровом мониторе.

следует с блока 141. За ним через 57,14 нс следует с блока 139 код №8 "3 код". Далее эти процессы повторяются. Сумматоры в блоках 17 и 23 представляются микросхемами К555ИМ6. Блоки 18, 24, 36 /фиг.15/ участвуют в формировании отсчетов промежуточных строк, задерживая коды на длительность строки, 80 мкс. А так как развертка строк в растре идет встречно, необходимо при развертке одних строк выдавать коды с сумматоры /19, 25, 37/ в последовательности с 1-го к 1400, а при развертке других строк, наоборот, с 1400 кода к 1-му. 1400 кодов с блока 17 /23, 35/ поступают последовательно в восемь регистров 1811-8. Каждый регистр 181 включает по 1400 разрядов. Причем коды по разрядам располагаются: первые разряды кодов в регистре 1811, вторые - в регистре 1812..., восьмые - в регистре 1818. Если смотреть на фиг.15, расположение идет как бы по горизонтали. При сложении в сумматоре кодов предыдущей строки с кодами последующей строки /фиг.15 вверху/, коды которой уже были задержаны на 80 мкс, выдача кодов из регистров 1811-8 идет не с 1-х разрядов, а с 1400-х, т.к. строка идет навстречу предыдущей. Это выполняется подключением выходов второго распределителя 180 импульсов к управляющим входам разрядов регистров в обратном порядке: к 1-му разрядам регистров 1400-го выхода, а к 1400-ым разрядам 1-го выхода. При сложении кодов 3 строки с кодами 5 строки выдача кодов в прямом порядке с распределителя 179 импульсов, выходы которого подключены к управляющим входам разрядов в прямом порядке. Коды с блоков 20, 26, 32 являются кодами текущих 500 строк и поступают в параллельном виде в блоки 84, 86, 88 импульсных усилителей в цифровом мониторе 2 /фиг.3/. Коды с блоков 19, 25, 37 являются кодами промежуточных /средних/ 500 строк и поступают в блоки 83, 85, 87 импульсных усилителей в цифровом мониторе.

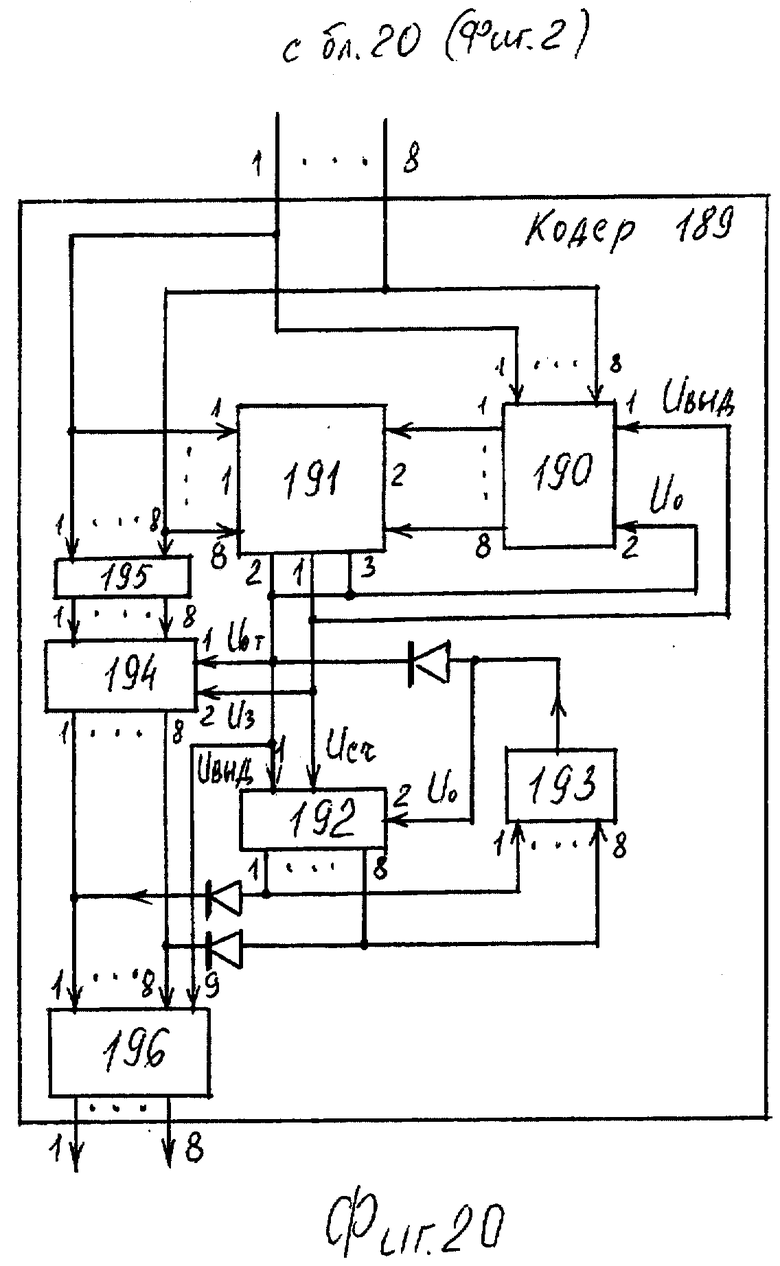

В монитор 2 на воспроизведение поступает кадр в 1000 строк с 1400 отсчетами в строке, скорость поступающей видеоинформации составляет: 1000стр×1400отсч×25 Гц=35 Мбайт/с. Это при условии, что сигналы цветов R, G, B идут параллельно, и коды следуют тоже в параллельном виде. С учетом трех цветов раздельно поток видеоинформации в три раза больше 105 Мбайт/с. Параллельно коды только текущих строк /с блоков 20, 26, 32/ поступают в блок 188 компрессии для сжатия видеоинформации перед записью на жестком диске компьютера /или ДД/. Блок 188 компрессии /фиг.2/ включает три идентичных кодера для сжатия потока каждого цветового сигнала раздельно.

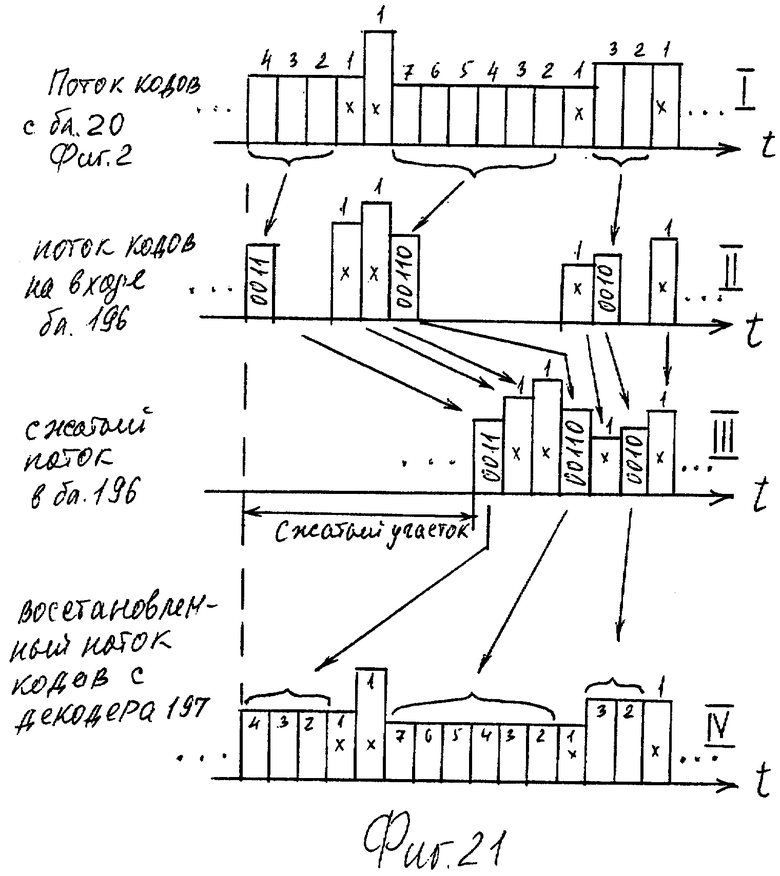

Способ сжатия цифровой видеоинформации перед записью состоит из следующих, последовательно выполняемых операций:

1. Сравнение значений кодов потока по величине для определения кодов, равных по величине и следующих друг за другом.

2. Подсчет числа кодов, равных по величине, начиная со второго кода последовательности, и формирование двоичного кода этого числа.

3. Введение кода числа в поток вслед за первым кодом своей последовательности.

4. Занесение сжатого потока видеоданных в буферную память перед выдачей их на запись в сжатом виде.

При восстановлении потока видеоданных при воспроизведении выполняются следующие операции:

5. Определение в сжатом потоке кода числа, равных по величине кодов /наличие сигнала в 9-м разряде кода/.

6. Дешифрация кода числа, равных кодов, и формирование числа сигналов выдачи первого кода соответственно количеству изъятых кодов.

7. Определение первого кода последовательности и выдача его соответственно числу изъятых кодов при сжатии. Диаграмма процесса сжатия потока данных и восстановление его перед воспроизведением на фиг.21. Число равных по величине кодов, идущих друг за другом, меняется, поэтому коэффициент сжатия будет плавающий. Чем больше равных кодов подряд, тем выше степень сжатия. Достоинство этого способа не снижает полноту восстановленного потока и не изменяет качество видеоинформации. Кодеры идентичны, каждый включает /фиг.20/ регистр 190, схему 191 сравнения /компаратор/, счетчик 192 импульсов, дешифратор 193, блок 194 ключей, блок 195 задержек и блок 196 буферной памяти /флэш-память/ [1, с.328]. На вход кодера /фиг.20/ поступают 8-разрядные коды /фиг.2/ с выхода блока 20 /26, 32/ задержек телевизионной карты. Код поступает на 1-8 разряды регистра 190, на первые входы 1-8 схемы 191 сравнения и на входы блока 165 задержек. Исходное состояние ключей в блоке 194 открытое. Поступающий в блок 195 код задерживается на 18 нс /время срабатывания схемы 191/ и поступает через открытые ключи блока 194 на 1-8 входы блока 196 буферной памяти, при этом на входе 9 сигнала нет. При следовании неравных кодов по величине ключи блока 194 остаются открытыми, коды идут на входы блока 196. Схема 191 сравнения производит сравнение по величине предыдущего и последующего кодов для выявления их равенства. В качестве схемы 191 применяются две микросхемы 530СП1 с временем срабатывания 18 нс [10 с.279]. Схема 191 при неравенстве кодов А>В выдает сигнал на выходе 2 /в микросхеме выход 5/ [10, с.272, рис.2, 190], при равенстве кодов А=В выдает сигнал с выхода 1 /в микросхеме выход 6/, а при А<В выдает сигнал с выхода 3 /выход 7 в микросхеме/. При равенстве кодов А=В сигнал с выхода 1 блока 191 закрывает ключи в блоке 194, он же поступает счетным сигналом на счетный вход счетчика 192 импульсов и на первый управляющий вход регистра 190 как сигнал Uвыд. Счетчик 192 производит счет импульсов, пока в потоке идут равные по величине коды. При неравенстве кодов /А>В или А<В/ со схемы 191 сравнения следует сигнал с выхода 2 или 3, которые объединены. Сигналы с них используются в качестве управляющих: для обнуления регистра 190 Uo, для открытия Uот ключей в блоке 194, для выдачи Uвыд кода со счетчика 192 и заполняет ряд 9, который определяет признак кода со счетчика 192. При равенстве кодов счетчик 192 /микросхема К531ИЕ17П с временем срабатывания 12 нс [10 c., 156]/ производит счет числа равных кодов. Счетчик 192 импульсов 8-разрядный, максимальный код в нем 11111111. При сравнении в схеме 191 неравных кодов появляется сигнал с выхода 2 /3/, который выдает код со счетчика 192, открывает ключи в блоке 194 и обнуляет регистр 190. Первый код из числа равных проходит в блок 196 и является первым кодом своей последовательности /диаграмма 11 на фиг.21/. Следующие за ним коды 2, 3, 4..., равные по величине, подсчитываются счетчиком 192 импульсов до появления сигнала со схемы 191 и исключаются из потока кодов.

За первым кодом последовательности следует код со счетчика 192 импульсов в блоке 196. Сам код 8-разрядный, а для его опознания в процессе восстановления /в декодере/ ему добавляется в 9-й разряд сигнал с выхода 2 /3/ со схемы 191 сравнения. В случае следования подряд 225 равных кодов и более дешифратор 193 при коде 11111111 выдает сигнал, который обнуляет регистр 190, выдает код из счетчика 192 и выдает импульс в 9-й разряд, открывает Uот ключи в блоке 194. На входе блока 196 поток кодов имеет вид диаграммы 11 /фиг.21/. Блок 196 производит накопление кодов, занося в память байт за байтом, и принимает вид диаграммы 111. С блока 196 сжатый поток подобранным соответственно драйвером через контроллер 7 переписывает содержание блока 196 на жесткий диск. Быстродействие кодера определяется временем срабатывания схемы 191 сравнения /18 нс/, обеспечивает пропускную способность кодера при кодах в параллельном виде 55 Мбайт/с. Объем потока, подлежащий сжатию, составляет 17,5 Мбайт/с /1400отсч×500стр×25кадр/. Пропускная способность кодера 189 с запасом обеспечивает поток сжимаемой информации. Ключ 40 открывается импульсом ССИ с блока 38, счетчик 41 импульсов 10-разрядный производит счет импульсов дискретизации 8,75 МГц, цикл счета 700 импульсов. С приходом 694 импульса дешифратор 42 дешифрирует код и выдает с первого выхода сигнал Uот ключей 44, 46 и 48, 50, которые пропускают четыре кода звука во время 696, 697, 698, 699 дискретных импульсов /фиг.4/. 695-й импульс приходится на срабатывание ключей при открытии. Коды стереозвука поступают в блоки 45, 47, 48, 51 регистров звука, каждый из которых включает по четыре 8-разрядных регистра. Регистры заполняются по мере поступления кодов, а выдаются сигналами 50 кГц с 3-го выхода синтезатора 39 частот. Коды звука поступают на соответствующие входы звуковой карты 9 /фиг.1/, где преобразуются в аналоговые сигналы и воспроизводятся громкоговорителями. Уровней квантования звука при кодировании 65536, т.е. 216 или 16 разрядов. С приходом в счетчик 699-го импульса дешифратор 42 сигналом со второго выхода закрывает ключи, обнуляет счетчик 41 и закрывает ключ40. Коды поступают и в видеоканалы телевизионной карты, но, начиная с 696 /1391/, лучи, воспроизводящие изображение на экране, находятся уже за краем экрана.

Работа цифрового монитора /фиг.3/

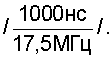

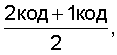

Цифровой монитор воспроизводит изображение без преобразования кодов видеосигналов в аналоговые видеосигналы, что необходимо в мониторах на ЭЛТ, и в нем ЭЛТ отсутствует. Цифровой монитор имеет плоский и легкий матовый экран, низковольтное питание, определяемое уровнем напряжения микросхем, имеет малое энергопотребление, что недоступно пламенным панелям /300 Вт «Радио» №9, 2004, с.9/, меняет режимы разрешения, что невозможно в ЖК-мониторах. Цветное изображение воспроизводится на матовом плоском экране электронно-оптической разверткой одновременно двух строк из трех цветных лучей R, G, B. Воспроизведение цветного изображения выполняется приемом кодов раздельно сигналов R, G, B с цифрового интерфейса видеокарты /выход ДV/. Используя режим видеокарты 800×600 и 85 кадр/с, поток кодов одного цвета 40,8 Мбайт/с, цифровой монитор воспроизводит на экране изображение 1600×1200 при 85 кадр/с при потоке кодов одного цвета 163,2 Мбайт/с, и параллельном потоке кодов трех цветов в 489,6 Мбайт/с. Управляющие сигналы ССИ и КСИ принимаются с видеокарты. Тактовые сигналы, импульсы дискретизации и импульсы двойной частоты дискретизации выдает делитель 54 частоты, соответственно 326,4 МГц, 40,8 МГц и 81,6 МГц. На вход делителя 54 частоты поступает рабочая частота с соответствующего выхода системного блока компьютера. Частота дискретизации определяется: 600строк×800отсч×85 Гц=40,8 МГц. Частота строк составляет: 600строк×85 Гц=51 кГц. Тактовая частота используется для заполнения кодами сигналов R, G, B, поступающим в последовательном виде, регистров в накопителях 60, 62, 64, 66, 68, 70 кодов и составляет: 40,8 МГц× 8разрядов=326,4 МГц. 1-3 управляющими входами цифрового монитора являются [1, c.485] соответственно сигнальный вход первого ключа 53 /фиг.3/, первый и второй входы элемента И 52. С приходом на входы элемента И импульс открывает первый ключ 53 и четвертый ключ 57, остающиеся открытыми весь кадр. Через открытый ключ 53 рабочая частота с системного блока поступает на вход делителя 54. Через открытый ключ 57 импульс ССИ поступает в триггер 58, сигнал с первого выхода которого открывает пятый ключ 59, седьмой ключ 63 и девятый 67. С 1-3 информационных входов монитора коды цветных сигналов R, G, В первой строки через открытые ключи 59, 63, 67 заполняют первые накопители 60, 64, 68 кодов. С приходом второго ССИ в триггер 58 сигнал с его второго выхода закрывает ключи 59, 63, 67 и открывает ключи 61, 65, 69 и 55. Коды цветных сигналов второй строки поступают во вторые накопители 62, 66, 70 кодов, а сигналы Uвыд с ключа 55 выдают последовательно с 1-го по 800-й коды сигналов в параллельном виде с первых накопителей 60, 64, 68 в блоки 71, 75, 79 удвоения отсчетов. Процесс удвоения отсчетов в блоках 71, 75, 79 аналогичен работе блока 17. Период следования кодов на входе блока 71 /75, 79/ составляет 24,5 нс /фиг.9/:  на выходе блока 12,2 нс:

на выходе блока 12,2 нс:  Каждый код используется два раза: первый раз как предыдущий, второй раз как последующий. Блок 71 имеет четыре регистра 146, 147, 148, 149. Сумматор 150 выполняет сложение двух 8-разрядных кода за время не более 12,2 нс, построен на быстродействующих микросхемах ИМ180 [10 с., 440]. С поступлением первого импульса на вход триггера 143 с его первого выхода сигнал Uвыд1 выдает одновременно «0 код» с регистра 147 и «0 код» с регистра 148, при выдаче регистры и обнуляются. Код с регистра 147 поступает на первые входы сумматора 150, «0 код» с регистра 148 поступает на вторые входы сумматора 150 через диоды и на входы блока задержек 152, задерживающий код на 24,5 нс. Сигнал Uвыд1 также открывает ключи в блоке 144, через которые первый код «1 код» поступает в регистры 146, 147.

Каждый код используется два раза: первый раз как предыдущий, второй раз как последующий. Блок 71 имеет четыре регистра 146, 147, 148, 149. Сумматор 150 выполняет сложение двух 8-разрядных кода за время не более 12,2 нс, построен на быстродействующих микросхемах ИМ180 [10 с., 440]. С поступлением первого импульса на вход триггера 143 с его первого выхода сигнал Uвыд1 выдает одновременно «0 код» с регистра 147 и «0 код» с регистра 148, при выдаче регистры и обнуляются. Код с регистра 147 поступает на первые входы сумматора 150, «0 код» с регистра 148 поступает на вторые входы сумматора 150 через диоды и на входы блока задержек 152, задерживающий код на 24,5 нс. Сигнал Uвыд1 также открывает ключи в блоке 144, через которые первый код «1 код» поступает в регистры 146, 147.

В это время сумматор 150 за 12,2 нс выполняет сложение кодов 0 код+0 код. В коде суммы на выходе сумматора 150 опускается младший разряд, чем выполняется деление двоичного кода на два:

Разряд 0 означает разряд переноса при сумме кодов. При удвоении частоты следования кодов в 81, 6 МГц период их следования составляет 12 нс, поэтому задержки после сумматора не нужно. После сложения 0 код + 0 код, код №1  следует с выхода сумматора 150. Второй код №2 «0 код» следует с блока 152 задержек, он задерживает код на 24 нс, но первая половина времени задержки кода 12 нс приходится на выполнение сложения в сумматоре. Поэтому вслед за кодом №1 через 12 нс следует код №2 «0 код». С приходом 2-го импульса на вход триггера 143 сигнал Uвыд2 со второго выхода выдает «1 код» из регистра 146 через диоды в сумматор 150 и в блок 151 задержек, задерживающий код на 12 нс. Из регистра 149 сигнал Uвыд2 выдает код «0 код» в сумматор 150. Идет сложение 1 код+0 код, при выходе кода суммы деление на 2, и следует код №3

следует с выхода сумматора 150. Второй код №2 «0 код» следует с блока 152 задержек, он задерживает код на 24 нс, но первая половина времени задержки кода 12 нс приходится на выполнение сложения в сумматоре. Поэтому вслед за кодом №1 через 12 нс следует код №2 «0 код». С приходом 2-го импульса на вход триггера 143 сигнал Uвыд2 со второго выхода выдает «1 код» из регистра 146 через диоды в сумматор 150 и в блок 151 задержек, задерживающий код на 12 нс. Из регистра 149 сигнал Uвыд2 выдает код «0 код» в сумматор 150. Идет сложение 1 код+0 код, при выходе кода суммы деление на 2, и следует код №3  через 12 нс с блока 151 следует код №4 «1 код». Сигнал Uвыд2 также открывает ключи в блоке 145, и код «2 код» заполняет регистры 148, 149. С приходом 3-го импульса в триггер 143 сигнал Uвыд3 первого выхода выдает с регистра 148 «2 код» через диоды на вход сумматора 150 и в блок 152 задержек. Uвыд3 выдает с регистра 147 «1 код» в сумматор 150, идет сложение 2 код + 1 код, деление на 2, и с выхода блока 150 код №5

через 12 нс с блока 151 следует код №4 «1 код». Сигнал Uвыд2 также открывает ключи в блоке 145, и код «2 код» заполняет регистры 148, 149. С приходом 3-го импульса в триггер 143 сигнал Uвыд3 первого выхода выдает с регистра 148 «2 код» через диоды на вход сумматора 150 и в блок 152 задержек. Uвыд3 выдает с регистра 147 «1 код» в сумматор 150, идет сложение 2 код + 1 код, деление на 2, и с выхода блока 150 код №5  затем через 12 нс следует с блока 152 код №6 «2 код». На вход триггера 143 поступает 4-й импульс и процессы повторяются. Коды удвоенной частоты следования 81,6 МГц /800×2=1600/ отсчетов поступают с блоков 71, 75, 79 через первые блоки 72, 76, 80 задержек на первые входы сумматоров 73, 77, 81, а также без задержек на вторые входы сумматоров 73, 77, 81 и на входы вторых блоков 74, 78, 82 задержек. Первые блоки 72, 76, 80 задержек выполняют задержку кодов на длительность 19,6 мкс строки

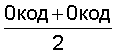

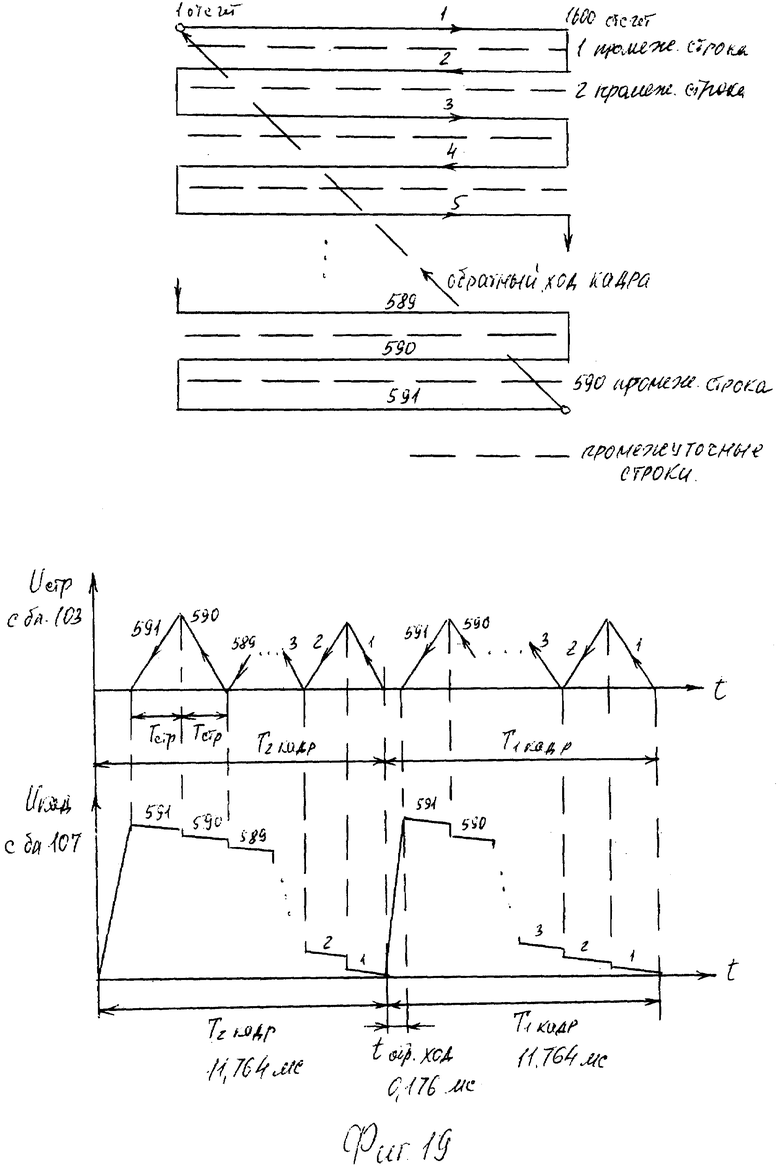

затем через 12 нс следует с блока 152 код №6 «2 код». На вход триггера 143 поступает 4-й импульс и процессы повторяются. Коды удвоенной частоты следования 81,6 МГц /800×2=1600/ отсчетов поступают с блоков 71, 75, 79 через первые блоки 72, 76, 80 задержек на первые входы сумматоров 73, 77, 81, а также без задержек на вторые входы сумматоров 73, 77, 81 и на входы вторых блоков 74, 78, 82 задержек. Первые блоки 72, 76, 80 задержек выполняют задержку кодов на длительность 19,6 мкс строки  Вторые блоки 74, 78, 82 задержек выполняют задержку кодов на время срабатывания сумматоров 73, 77, 81, т.е. на 12 нс, сумматоры на основе ИС ИМ180 [10, с.440]. Коды с блоков 74, 78, 82 представляют 600 строк промежуточных. В кадре получается 1200 строк с 1600 отсчетами в каждой. Развертка кадра на экране 99 выполняется одновременно двумя строками. Коды 600 строк с блоков 74, 78, 82 задержке поступают через импульсные усилители блоков 84, 86, 88 на входы первого излучателя 129 блока 89 /фиг.6/ модуляции излучения, его луч воспроизводит 600 строк изображения, коды которых представляются видеокартой. Коды 600 промежуточных строк с сумматоров 73, 77, 81 поступают через импульсные усилители блоков 83, 85, 81 на входы второго излучателя 130, луч с которого воспроизводит 600 промежуточных строк, коды которых представляются сумматорами 73, 77, 81. Импульсные усилители в блоках 83-88 представляются микросхемами 1536АП3 [10, с.128] с временем срабатывания не более 12 нс. С выходов видеокарты ССИ и КСИ и коды сигналов R, G, B раздельно поступают на 1-6 входы монитора. Развертка строк выполняется построчно /прогрессивная/ без обратных ходов /фиг.19/. Кадровая развертка с обратным ходом составляет 1,5% от длительности кадра 0,176 мс /занимает 9 строк/. Строчную развертку активных строк /591/ выполняет блок 100 строчной развертки /фиг.3/. На вход его поступает строчная частота 51 кГц, делитель 101 делит частоту 2:1, на вход задающего генератора 102 поступает частота 25,5 кГц. Выходной каскад усиливает сигналы до необходимой величины, которые поступают на внутренний электрод 124 /фиг.7/ первого пьезодефлектора 91. На внешние электроды 125, 126 поступают соответствующие напряжения с первого 92 и второго 93 источников опорного напряжения. С подачей управляющего сигнала с блока 103 происходит деформация пьезопластин [5, c.122], торец со световым отражателем 128 приходит в колебательное движение и производит развертку двух лучей по горизонтали на отражателе второго пьезодефлектора 95. Торец первого пьезодефлектора 91 колеблется с частотой 25,5 кГц, за один период колебания выполняя развертку двух строк. Ширина отражателя на торце пьезодефлектора 91 принята 0,02 мм, длина 3 мм /для облегчения юстировки/. Кадровую развертку выполняет блок 104, формируя управляющее напряжение на выходе блока 107 /фиг.19/. Период развертки кадра 11, 764 мс /85 Гц/, развертка имеет обратный ход в 0,176 мс /9 строк/. Задающий генератор 106 формирует пилообразное напряжение, линейно изменяющееся, поступающее на первый вход суммирующего усилителя 107.

Вторые блоки 74, 78, 82 задержек выполняют задержку кодов на время срабатывания сумматоров 73, 77, 81, т.е. на 12 нс, сумматоры на основе ИС ИМ180 [10, с.440]. Коды с блоков 74, 78, 82 представляют 600 строк промежуточных. В кадре получается 1200 строк с 1600 отсчетами в каждой. Развертка кадра на экране 99 выполняется одновременно двумя строками. Коды 600 строк с блоков 74, 78, 82 задержке поступают через импульсные усилители блоков 84, 86, 88 на входы первого излучателя 129 блока 89 /фиг.6/ модуляции излучения, его луч воспроизводит 600 строк изображения, коды которых представляются видеокартой. Коды 600 промежуточных строк с сумматоров 73, 77, 81 поступают через импульсные усилители блоков 83, 85, 81 на входы второго излучателя 130, луч с которого воспроизводит 600 промежуточных строк, коды которых представляются сумматорами 73, 77, 81. Импульсные усилители в блоках 83-88 представляются микросхемами 1536АП3 [10, с.128] с временем срабатывания не более 12 нс. С выходов видеокарты ССИ и КСИ и коды сигналов R, G, B раздельно поступают на 1-6 входы монитора. Развертка строк выполняется построчно /прогрессивная/ без обратных ходов /фиг.19/. Кадровая развертка с обратным ходом составляет 1,5% от длительности кадра 0,176 мс /занимает 9 строк/. Строчную развертку активных строк /591/ выполняет блок 100 строчной развертки /фиг.3/. На вход его поступает строчная частота 51 кГц, делитель 101 делит частоту 2:1, на вход задающего генератора 102 поступает частота 25,5 кГц. Выходной каскад усиливает сигналы до необходимой величины, которые поступают на внутренний электрод 124 /фиг.7/ первого пьезодефлектора 91. На внешние электроды 125, 126 поступают соответствующие напряжения с первого 92 и второго 93 источников опорного напряжения. С подачей управляющего сигнала с блока 103 происходит деформация пьезопластин [5, c.122], торец со световым отражателем 128 приходит в колебательное движение и производит развертку двух лучей по горизонтали на отражателе второго пьезодефлектора 95. Торец первого пьезодефлектора 91 колеблется с частотой 25,5 кГц, за один период колебания выполняя развертку двух строк. Ширина отражателя на торце пьезодефлектора 91 принята 0,02 мм, длина 3 мм /для облегчения юстировки/. Кадровую развертку выполняет блок 104, формируя управляющее напряжение на выходе блока 107 /фиг.19/. Период развертки кадра 11, 764 мс /85 Гц/, развертка имеет обратный ход в 0,176 мс /9 строк/. Задающий генератор 106 формирует пилообразное напряжение, линейно изменяющееся, поступающее на первый вход суммирующего усилителя 107.

На вход задающего генератора 106 поступают импульсы с элемента И 105 в момент прихода в элемент И импульсов ССИ, КСИ. Торец пьезодефлектора 95 выполняет кадровую развертку 85 Гц. Ширина отражателя пьезодефлектора принята 0,02 мм, длина составляет не менее 32 мм /1600×0,02 мм/. С выхода суммирующего усилителя 107 выдается линейно изменяющееся ступенчатое управляющее напряжение, усиливаемое выходным усилителем 157 /фиг.10/. Отражатель пьезодефлектора 95 отклоняет развертываемые строки вниз, затем обратный ход торца вверх. Во время обратного хода коды цветных сигналов из накопителей кодов 60, 62, 64, 66, 68, 70 не выдаются /закрыты ключи/, излучение с блока 89 отсутствует. Суммирующий усилитель 107 производит суммирование напряжения с задающего генератора 106 с импульсами частоты строк 51 кГц. Каждый импульс строки перемещает строку в конце ее хода на шаг в ширину строки. Назначение блоков 153-156 /фиг.10/ подавать на 2-й вход выходного усилителя 157 в нужное время импульсы соответствующей амплитуды и длительности. Счетчик 153 10-разрядный, производит счет строчных импульсов 51 кГц, цикл счета 591 импульс. При поступлении 591-го импульса дешифратор 154 выдает сигнал U3, закрывающий ключ 155. Развертка кадра вниз прекращается, следует обратные ход.

В первых накопителях 60, 64, 68 кодов накапливаются коды нечетных строк, во вторые накопителях 62, 66, 70 кодов накапливаются коды четных строк. Коды с них выдаются в порядке с 1-го по 800-й код. С приходом первого ССИ в триггер 58 сигнал с его 1-го выхода открывает ключи 59, 63, 67, коды первой строки с 1-го по 800-й /с 1-3 информационных входов/ заполняют первые накопители 60, 64, 68 кодов. С приходом второго ССИ в триггер 58 сигнал с второго выхода закрывает ключи 59, 63, 67, открывает ключи 61, 65, 69. Коды четной строки заполняют вторые накопители 62, 66, 70, а сигналы Uвыд /40,8 МГц/ с открытого ключа 55 выдают коды с первых накопителей кодов в последовательности с первого по 800-й коды в блоки 71, 75, 79, где число отсчетов в строке удваивается с 800-й по 1600-й, и через соответствующие блоки они поступают в блоки 83-88, в которых импульсные усилителя усиливают сигналы кодов для запитывания своих светодиодов в излучателях 129, 130. С приходом третьего ССИ в триггер 58 импульс с его первого выхода повторяет открытие ключей 59, 63, 67 и 56, закрывает ключа 61, 65, 69 и 55. Сигналы Uвыд /40,8 МГц/ с ключа 56 выдают коды в порядке с 1-го кода по 800-й со вторых накопителей 62, 66, 70 в блоки 71, 75, 79, затем в блок 89 модуляции излучения. С поступлением следующих ССИ в триггер 58 процессы повторяются. Схемы накопителей кодов на фиг.14. Заполнение регистров 118 и 121 кодами 800 отсчетов строки производятся в последовательности с 1-го по 800-й код. В каждой размещается по 800 байт /6400 бит/.

Блоки 72, 76, 80 задерживают коды строки перед сложением отсчетов для получения промежуточных строк на длительность отроки 19,6 мкс. А так как развертка в растре строк встречная, то при развертке нечетных строк 1, 3, 5... коды выдаются в последовательности с 1-го по 1600-й /фиг.16/, а при развертке четных строк 2, 4, 6... коды выдаются в сумматоры в последовательности с 1600-го к 1-му коду. Работа блоков 72, 76, 80 задержки идентична работе уже описанных блоков 18, 24, 36 (с.19).

Блок 89 модуляции излучения выполняет яркостную модуляцию трех цветов в двух излучателях одновременно. Первый 129 модулированным по яркости лучом при работе с видеокарты 8 воспроизводит 600 строк растра, кодируемых в видеокарте. Второй излучатель 130 воспроизводит еще 600 промежуточных строк, формируемых сумматорами 73, 77, 81 монитора. Активных строк в кадре 591×2=1182, 9×2=18 строк приходится на обратный ход кадра. Воспроизводимый растр содержит 1182 активных строк с 1600 отсчетами в каждой, что определяет 1891200 элементов разрешения в кадре, против 480000 элементов разрешения, выдаваемых видеокартой: 800×600. При работе от телевизионной карты 10 первый излучатель 129 воспроизводит 500 строк растра, принятых телевизионной картой из эфира, второй излучатель 130 воспроизводит еще 500 строк промежуточных, которые формируются сумматорами 20, 26, 37.

Воспроизводимый растр содержит 1000 строк /все активные/ с 1400 отсчетами в каждой. И строчная кадровая развертки не имеют обратных ходов /фиг.18/. Разрешающая способность 1400000 элементов. Развертка изображения на матовом экране 99 выполняется блоком 108 строчной развертки и блоком 112 кадровой развертки. На вход делителя 109 частоты /2:1/ с блока 38 /фиг.2/ поступают ССИ 12,5 кГц. Задающий генератор 110 принимает импульсы 6,25 кГц и формирует управляющие напряжения треугольной равнобедренной формы частотой 6,25 кГц и формирует управляющие напряжения треугольной равнобедренной формы частотой 6,25 кГц /фиг.18/. Усилитель выходного каскада III усиливает управляющее напряжение до необходимой величины и подает их на внутренний электрод первого пьезодефлектора 91, что приводит свободный торец в колебания с частотой 6,25 кГц, выполняя развертку двух строк с частотой 12,5 кГц на отражателе второго пьезодефлектора 95, выполняющего кадровую развертку по управляющим напряжениям с блока 112 кадровой развертки. Управляющие сигналы на фиг.18. Развертка чересстрочная и без обратных ходов. Пьезодефлектор 95 колеблется по управляющим напряжениям с блока 115 с частотой 25 Гц, 50 полей в секунду. С выхода суммирующего усилителя 115 выдается линейно изменяющееся ступенчатое напряжение, усиливаемое усилителем 164 /фиг.11/ и поступающее на внутренний электрод пьезодефлектора 95. Суммирующий усилитель 115 производит суммирование треугольного напряжения с задающего генератора 114 с импульсами 12,5 кГц, что дает линейно изменяющееся и ступенчатое напряжение для усилителя 164. Каждый импульс строки перемещает строку в конец ее хода на шаг в ширину двух строк в момент захода лучей за край экрана 99 с одной и другой сторон. Назначение блоков 158-163 подавать на второй вход усилителя 164 в нужное время положительные /или отрицательные/ импульсы соответствующей амплитуды и длительности. Счетчик 158 9-разрядный производит счет импульсов 12,5 кГц, цикл счета 500. В конце развертки 1-го поля кадра с приходом 250-го импульса строки /499 строка из нечетных строк/ счетчик 158 формирует код 11111010, который дешифрируется блоком 159 в сигнал, закрывающий первый ключ 160, открывающий второй ключ 161, который пропускает во втором поле кадра импульсы 12,5 кГц во второй формирователь 163 импульсов. Следует развертка второго поля кадра /вверх/. Блок 89 модуляции излучения выполняет яркостную модуляцию излучения трех цветов соответственно кодов каждого цветового сигнала в излучателе 129, 130. Каждый излучатель включает светодиоды красного излучения 12 шт., зеленого - 12 шт, синего - 12 шт. типа HL MP, выпускаемые компанией «Хьюлетт-паккард» [12, с.71]. Излучающие окна светодиодов расположены в задней фокальной плоскости оптической системы 131. Распределение светодиодов одного цвета по весам разрядов кода в таблице.

Для красного излучения приняты светодиоды HL MP-AL00 с силой света 0,4 кд [12, с.71] при токе 0,02 А с длиной волны 0,59 мкм, для зеленого - светодиоды HL MP-AM00 с силой света 0,8 кд с длиной волны 0,526 мкм и токе 0,02 А, для синего - светодиоды HL-AB00 с силой света 0,3 кд с длиной волны 0,475 мкм и токе 0,02 А. Суммарное излучение светодиодов трех цветов двух излучателей смешивается оптической системой 131 при фокусировке в два цветовых пятна на отражателе первого пьезодефлектора 91. Яркостная модуляция выполняется включением на излучение числа светодиодов в излучателе соответственно весам разрядов в коде. Яркость, насыщенность и цветовой тон результирующего цвета на экране 99 определяется суммарной энергией и взаимным соотношением трех цветов R, G, B в каждом излучателе. Суммарная сила света одного излучателя 129 /130/ с учетом, что светодиоды всех цветов имеют силу света синего светодиода 0,3 кд, составляет:

где 3 - число цветов в излучателе;

0,3 кд - сила света синего светодиода;

- коэффициенты двоичных разрядов с 4 по 8.

- коэффициенты двоичных разрядов с 4 по 8.

С учетом потерь силы излучения при прекции в 20 раз от излучателей до экрана 99 максимальная яркость одного развертывающего светового элемента с размером поперечного сечения 0,16 мм2 /0,4×0,4 мм/ составляет:

где 7,17 кд - суммарная сила света одного излучателя;

20 - кратность ослабления силы света при проекции;

0,16·10-6 м2 - площадь элемента разрешения на экране 99,

/0,4×0,4/ мм.

Кратность увеличения изображения проекционной оптической системой 98 принимаем в 20 раз. В этом варианте размеры изображения при растре 1600×1200 на экране 99 составляют:

по горизонтали 20×/0,02 мм × 1600/=640 мм,

по вертикали 20×/0,02 мм × 1200/=480 мм,

по диагонали 800 мм или 31″. 0,02 мм диаметр разрешающего светового элемента на отражателе второго пьезодефлектора 95.

При растре 1400×1000 /от телевизионной карты/ размеры изображения на экране 99 составляют:

по горизонтали 20×/0,02 мм × 1400/=560 мм,

по горизонтали 20×/0,02 мм × 1600/=400 мм,

по диагонали 688 мм или 27″.

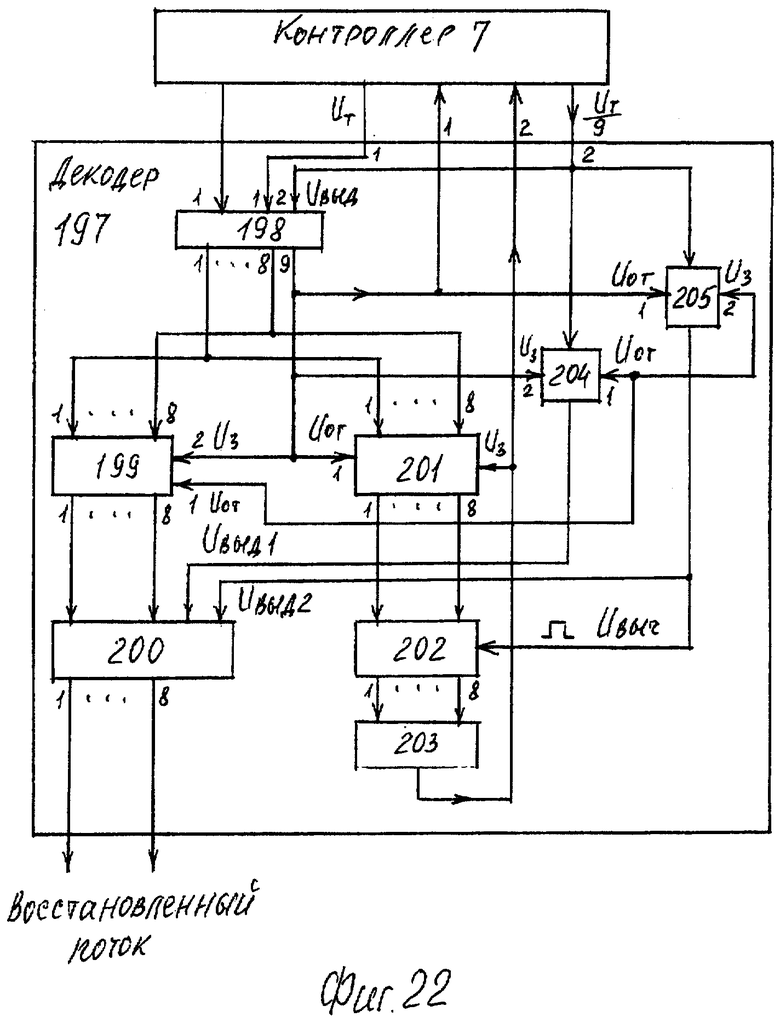

Для восстановления сжатой кодером 189 /фиг.20/ видеоинформации применяется декодер 197 /фиг.22/, включающий последовательно соединенные первый регистр 198, первый блок 199 ключей и второй регистр 200, последовательно соединенные второй блок 201 ключей, вычитающий счетчик 202 импульсов и дешифратор 203, а также первый 204 и второй 205 ключи. Для восстановления сжатой информации коды в последовательном виде с жесткого диска поступают на информационный вход декодера в первый регистр 198. При поступлении 8-разрядного кода в регистр 198 заполняется 1-8 разряды, тактовые импульсы поступают на первый управляющий вход декодера. Код с регистра 198 выдается сигналом дискретизации Uвыд, поступающим на второй управляющий вход декодера  на входы блоков 204, 205 ключей. Исходное состояние ключей в блоке 199 открытое, в блоке 201 закрытое. Код через открытые ключи в блоке 199 поступает в регистр 200, с которого выдается сигналом Uвыд1 на выход декодера и обнуляет регистр 200. Пока в регистр 198 поступают коды по 8 разрядов, такой процесс повторяется. С приходом в регистр 198 кода из 9 разрядов, означающий число равных кодов, сигнал с 9-го разряда регистра 198 закрывает ключи в блоке 199, открывает ключи в блоке 201, закрывает ключ 204, открывает ключ 205 и поступает на соответствующий вход контроллера 7 /фиг.1/ жесткого диска для очень кратковременного прекращения выдачи кодов в декодер 197 /пока идет выдача одного и того же кода с регистра 200/. Код числа равных кодов через открытые ключи блока 201 поступает в вычитающий счетчик 202 импульсов. Импульсы с ключа 205 поступают на счетный вход вычитающего 202 счетчика /микросхема 100ИЕ137 с временем срабатывания 10,5 нс [10, с.428]/ и одновременно поступает как сигнал Uвыд2 в регистр 200. Сигнал Uвыд2 выдает код из регистра 200, но не обнуляет его. Поэтому пока идет работа счетчика 202 на вычитание до появления в нем кода 00000000, с регистра 200 выдается один и тот же код. Он представляет коды, изъятые при сжатии информации. Восстановленный поток данных с деводера на диаграмме IY фиг.21. При поступлении в дешифратор 203 кода 00000000 он выдает сигнал, который закрывает ключ 205, открывает ключ 204 и со второго управляющего выхода декодера поступает в контроллер 7 на возобновление выдачи информации с жесткого диска в декодер. Далее процессы повторяются. Декодер включается в системный блок или три декодера, которые работают параллельно для декодирования трех цветовых сигналов раздельно. Они могут применяться и для считывания сжатой по этому способу видео- или звуковой информации с дисков КД и DVD.

на входы блоков 204, 205 ключей. Исходное состояние ключей в блоке 199 открытое, в блоке 201 закрытое. Код через открытые ключи в блоке 199 поступает в регистр 200, с которого выдается сигналом Uвыд1 на выход декодера и обнуляет регистр 200. Пока в регистр 198 поступают коды по 8 разрядов, такой процесс повторяется. С приходом в регистр 198 кода из 9 разрядов, означающий число равных кодов, сигнал с 9-го разряда регистра 198 закрывает ключи в блоке 199, открывает ключи в блоке 201, закрывает ключ 204, открывает ключ 205 и поступает на соответствующий вход контроллера 7 /фиг.1/ жесткого диска для очень кратковременного прекращения выдачи кодов в декодер 197 /пока идет выдача одного и того же кода с регистра 200/. Код числа равных кодов через открытые ключи блока 201 поступает в вычитающий счетчик 202 импульсов. Импульсы с ключа 205 поступают на счетный вход вычитающего 202 счетчика /микросхема 100ИЕ137 с временем срабатывания 10,5 нс [10, с.428]/ и одновременно поступает как сигнал Uвыд2 в регистр 200. Сигнал Uвыд2 выдает код из регистра 200, но не обнуляет его. Поэтому пока идет работа счетчика 202 на вычитание до появления в нем кода 00000000, с регистра 200 выдается один и тот же код. Он представляет коды, изъятые при сжатии информации. Восстановленный поток данных с деводера на диаграмме IY фиг.21. При поступлении в дешифратор 203 кода 00000000 он выдает сигнал, который закрывает ключ 205, открывает ключ 204 и со второго управляющего выхода декодера поступает в контроллер 7 на возобновление выдачи информации с жесткого диска в декодер. Далее процессы повторяются. Декодер включается в системный блок или три декодера, которые работают параллельно для декодирования трех цветовых сигналов раздельно. Они могут применяться и для считывания сжатой по этому способу видео- или звуковой информации с дисков КД и DVD.

Работа цифрового монитора и телевизионной карты

Информация кодов ER и EG передается в эфир верхней боковой частотой несущей, кодов ЕВ - нижней боковой частотой несущей. Оба радиосигнала принимаются блоками 12, 27 приема радиосигнала первого и второго трактов телевизионной карты. После детектирования радиосигналов коды видеосигналов ER, EG, ЕВ поступают в свои регистры 16, 22, 31, 34. Блоки 17, 23 выполняют удвоение числа отсчетов в 500 строках сигналов ER, EG. Сумматоры 19, 25, 37 формируют еще 500 промежуточных строк и блоков задержек 20, 26, 32, 500 строк поступают в цифровой монитор на входы блоков 83-88 импульсных усилителей. Кадр с телевизионной карты представляет 1400×100. Коды звуковых сигналов в телевизионной карте отделяются от кодов видеосигналов и поступают в звуковую карту компьютера, где преобразуются в аналоговые сигналы и воспроизводятся громкоговорителями. Импульсные усилители блоков 83-88 усиливают сигналы кодов и запитывают светодиоды в излучателях блока 89 модуляции излучения. Развертка кадра 1400×1000 выполняется одновременно двумя строками управляющими сигналами с блока 108 строчной и с блока 112 кадровой разверток. Первый пьезодефлектор 91 выполняет строчную развертку двух лучей, второй пьезодефлектор 95 выполняет кадровую развертку. Проекционная оптическая система 98 выполняет увеличение изображения в 20 раз, проецирует его на матовый экран 99.

Параллельно коды видеосигналов с телевизионной карты поступают в блок 188 компрессии, где потоки кодов сигналов R, G, B раздельно сжимаются тремя кодерами 189 /фиг.20/ и поступают по интерфейсу параллельного типа /IDE или SCSI/ через контроллер 7 на запись в жесткий диск. Коды видеосигналов с цифрового выхода видеокарты поступают на 1-3 информационные входы цифрового монитора в первые 60, 64, 68 накопители кодов, коды второй строки поступают во вторые накопители 62, 66, 70 кодов. А коды первой строки в это время выдаются в блоки 71, 75, 79 удвоения отсчетов. Удвоенные коды поступают в блоки 74, 78, 79 удвоения отсчетов. Удвоенные коды поступают в блоки 74, 78, 82 задержки и в свои сумматоры 73, 77, 81. С блоков задержек коды 600 строк, усиленные по амплитуде сигналов, через блоки 84, 86, 88 поступают в первый излучатель 129, с сумматоров коды 600 строк /промежуточных/ через блоки 83, 85, 87 импульсных усилителей поступают во второй излучатель 130. Развертка кадра 1600×1200 выполняется пьезодефлекторами 91 и 95 по управляющим напряжениям с блока 100 строчной и блока 104 кадровой разверток. Проекционная оптическая система проецирует изображение развертываемого кадра на матовый экран 99. Применение цифрового монитора снижает энергопотребление компьютера и максимально выполняет требования безопасности для пользователя /низковольтное питание, отсутствие вредных излучений, малый вес монитора/. Введение телевизионной карты в состав компьютера позволяет отказаться от телевизора и объединит желание всех членов семьи в приобретении компьютера. Сжатие цифровой информации с телевизионной карты и запись ее на жесткий диск расширяет функции в работе компьютера.

Использованные источники

1. Мураховский В.И. Устройство компьютера. М., 2003, с.26, 34, 56, 60, 72, 302, 485, 496, 328, 520, прототип.

2. В.П.Леонтьев. Новейшая энциклопедия персонального компютера. М., 2004, с.54, 55.

3. Патент РФ №2194370 кл. Н 04 N, бюл. №34, 2002.

4. С.Н.Липатов. Я люблю создавать и копировать видеодиски. М., 2004, с.22-24.

5. Фриндлянд И.В., Сошников В.Г. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118 рис.5.5, с.122, рис.5.10.

6. Бродский М.А. Телевизоры цветного изображения. Минск, 1988, с.86 рис.2.55, с.132 рис.4.2.

7. Радиосвязь, вещание, телевидение. По ред. А.Л.Фортушенко, М., 1984, с.146.

8. Справочник по радиовещанию. Под ред. А.В.Выходца, Киев, 1981, с.112 рис.81.

9. Баркан В.Ф., Жданов В.К. Усилительная и импульсная техника, М., 1981, с.209.

10. Цифровые интегральные микросхемы. Минск, 1991, с.128, 156, 231, 258, 272 рис.2.190, 279, 440.

11. Самойлов В.Ф., Хромой Б.П.Телевидение. М., 1975, с.370.

12. «Радио» №7, 1998, с.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2298297C1 |

| ВИДЕОКАМЕРА | 2005 |

|

RU2304361C1 |

| ЦИФРОВОЙ МОНИТОР | 2005 |

|

RU2292664C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2004 |

|

RU2270529C1 |

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2284672C1 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2292127C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2351094C1 |

| СИСТЕМА ОБЪЕМНОЙ ВИДЕОЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ | 2006 |

|

RU2315439C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2007 |

|

RU2339183C1 |

Изобретение относится к аппаратным устройствам компьютерного оборудования и используется для расширения функций персонального компьютера. Техническим результатом является обеспечение возможности приема персональным компьютером эфирного цифрового телевизионного сигнала, воспроизведение его без потерь качества на полном экране монитора с записью в сжатой форме на жесткий диск компьютера. Технический результат достигается тем, что в персональный компьютер, содержащий системный блок, включающий системную плату, процессор, оперативную память, жесткий диск с контроллером, видеокарту, звуковую карту, дисковод, монитор, клавиатуру и мышь, введены цифровой монитор, телевизионная карта, блок компрессии. 22 ил., 1 табл.