Изобретение относится к аппаратным устройствам компьютерного оборудования и используется совместно с персональным компьютером (PC) для формирования трехмерного изображения.

Прототипом принят кибершлем V8 фирмы Virtual Research Sistems [1, c.557], содержащий блок управления, два соединительных кабеля и шлем, включающий две ЖК-матрицы размером по диагонали 1,3'' (дюйма). В качестве входного сигнала используется выходной сигнал видеоадаптера VGA в режиме 640×480 при построчной развертке и частоте кадров 60 Гц. Сигнал подается на вход блока управления через 15-контактныи VGA-разъем. Блок управления выполняет функции коммутирующего устройства, имеет два входа для раздельного подключения левого и правого экранов. Оба сигнала поступают на экраны шлема независимо друг от друга. Шлем соединяется с блоком управления 50-контактным SCSI-разъемом. Каждая ЖК-матрица размером по диагонали 1,3'' с разрешением 307200 элементов. Недостатками прототипа являются: недостаточное разрешение ЖК-матриц [1, с.558], частота ограничена 60 Гц, высокая стоимость.

Цель изобретения - повышение разрешения изображений на экранах и увеличение частоты кадров.

Техническим результатом является увеличение разрешения изображения на экранах в 1,56 раза (480000/307200) и частоты кадров в 1,41 раза (85/60), достигаемое применением развертки растра двумя строками одновременно, преобразование двоичных кодов в яркостное излучение двух излучателей (для двух строк) и электронно-оптической разверткой растров.

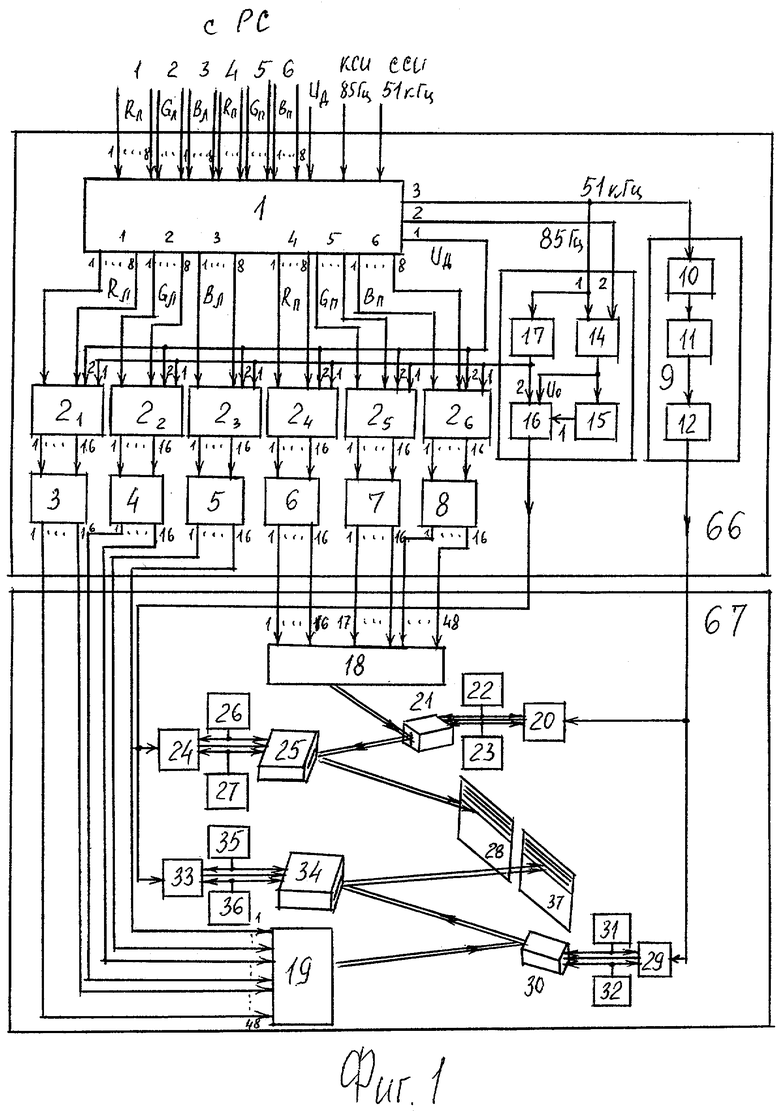

Сущность изобретения заключается в том, что в систему виртуальной реальности, содержащую блок управления, два соединительных кабеля и шлем, введены шесть строчных накопителей кодов, шесть блоков импульсных усилителей, два блока модуляции излучений, последовательно соединенные первый усилитель и первый пьезодефлектор с отражателем на торце, второй усилитель и второй пьезодефлектор с отражателем на торце, третий усилитель и третий пьезодефлектор с отражателем на торце, четвертый усилитель и четвертый пьезодефлектор с отражателем на торце, четыре источника опорных напряжений и два матовых экрана. Используется построчная развертка без обратных ходов. Стереокадр формируется видеоадаптером PC из левого и правого кадров стереопары. Используется видеорежим 800×600×85. С блока управления коды левого и правого кадров раздельно по цветам сигналов R, G, В поступают в строчные накопители кодов, усиливаются в 1-6 импульсных усилителях, поступают в первый и второй блоки модуляции излучений, лучи с которых развертываются пьезодефлекторами на левом и правом экранах.

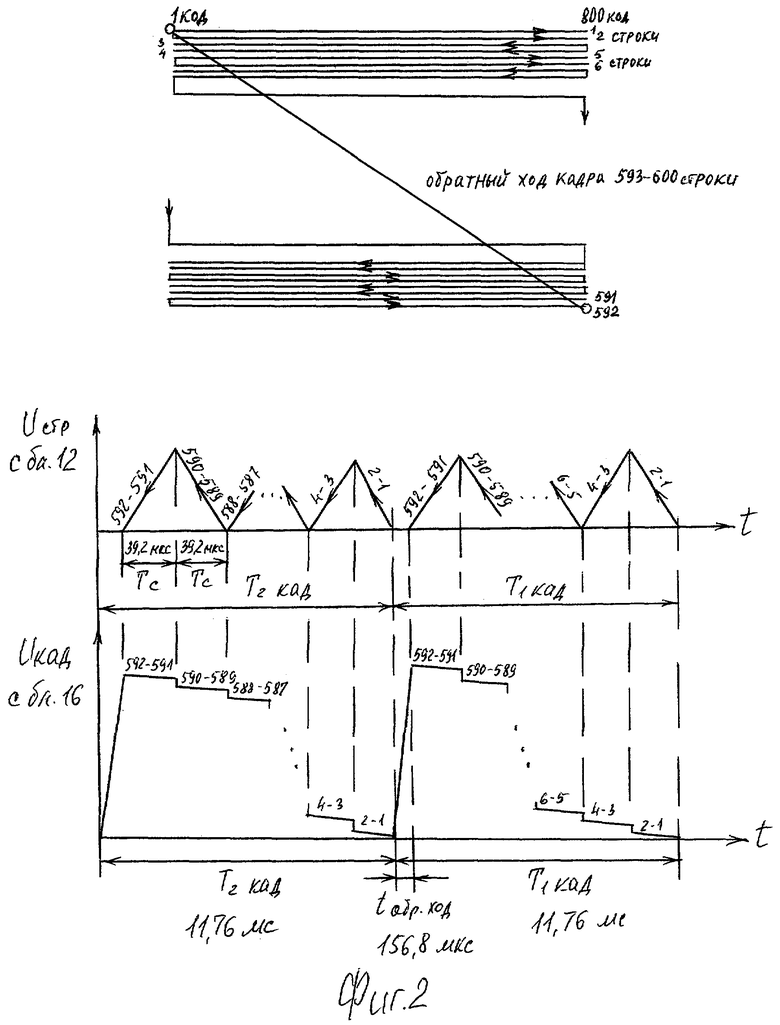

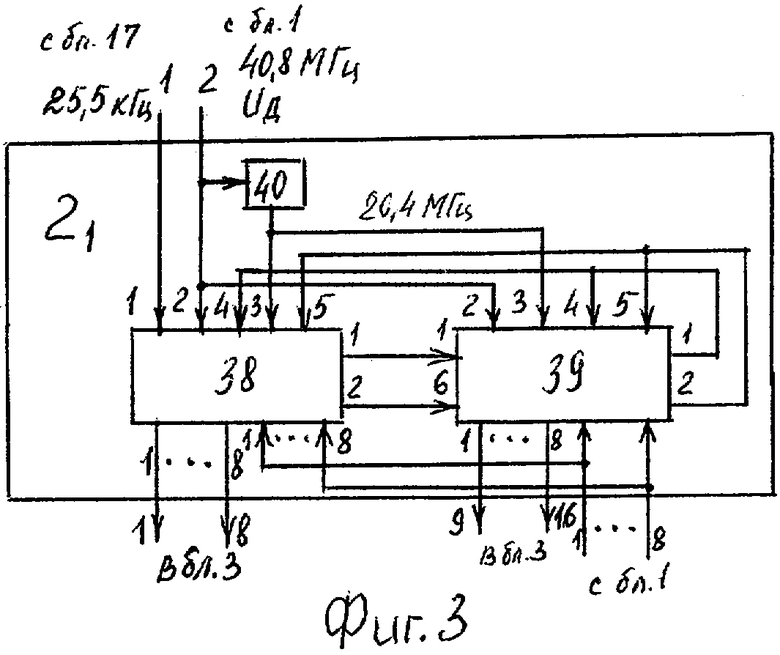

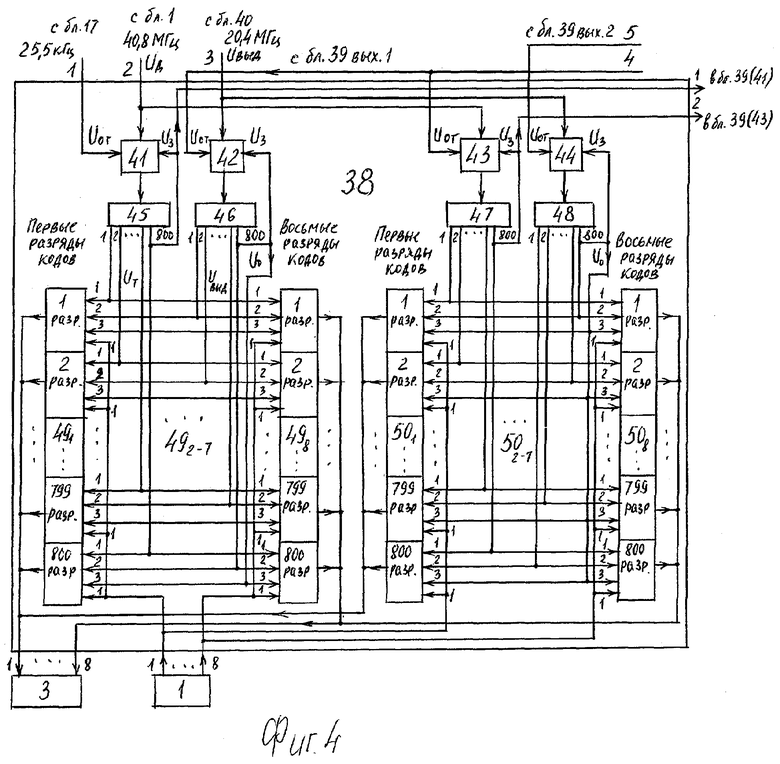

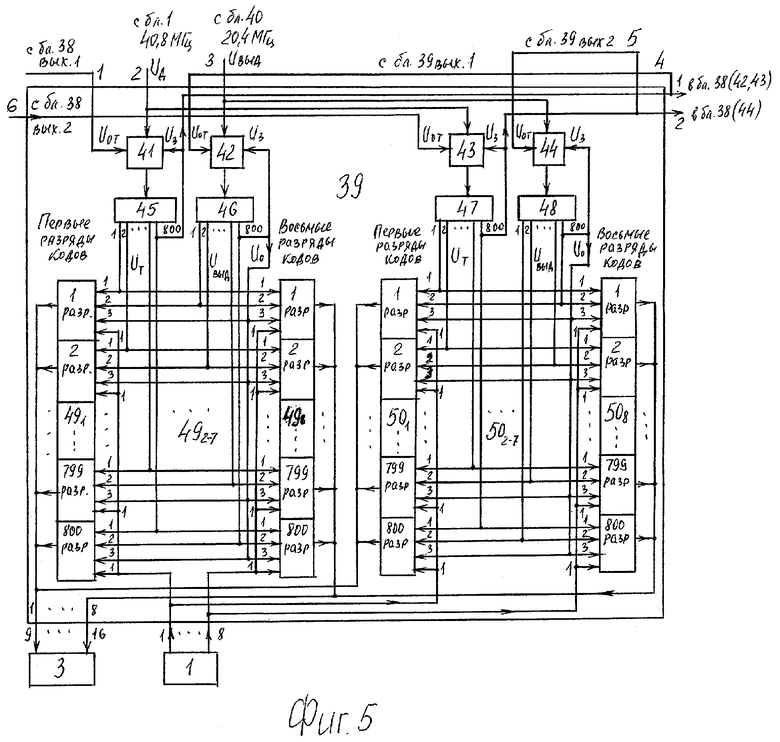

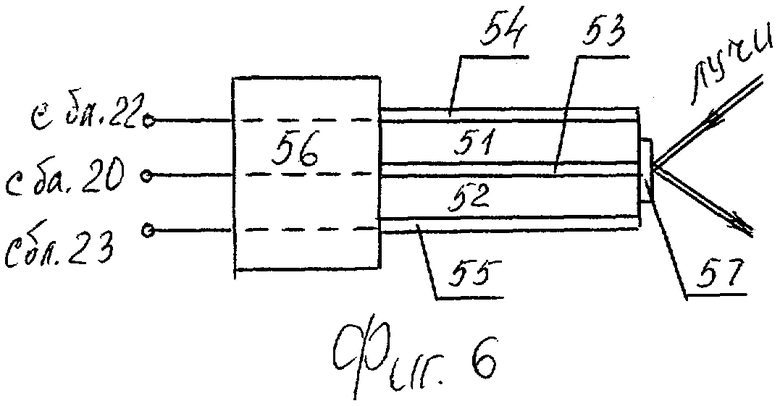

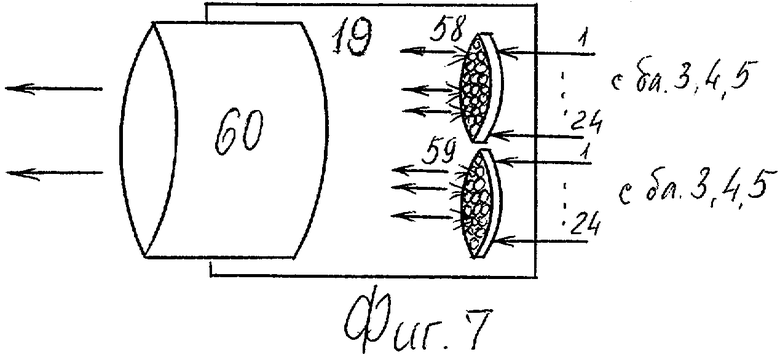

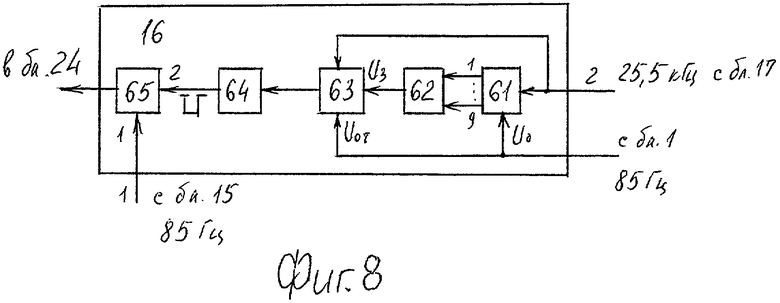

Функциональная схема системы представлена на фиг.1, блок-схема строчного накопителя кодов - на фиг.3, развертка растра и управляющие сигналы - на фиг.2, функциональные схемы первого и второго блоков регистров - на фиг.4 и 5, конструкция пьезодефлектора - на фиг.6, блок модуляции излучений - на фиг.7, суммирующий усилитель - на фиг.8.

Система виртуальной реальности включает (фиг.1) блок 1 управления, шесть идентичных строчных накопителя 21-6 кодов, шесть блоков 3-8 импульсных усилителей, блок 9 строчной развертки из последовательно соединенных делителя 10 частоты (4:1), задающего генератора 11 и выходного каскада 12, блок 13 кадровой развертки из последовательно соединенных элемента И 14, задающего генератора 15 и суммирующего усилителя 16 и делителя 17 частоты (2:1), первый блок 18 модуляции излучений, второй блок 19 модуляции излучений, последовательно соединенные первый усилитель 20 и первый пьезодефлектор 21 с отражателем на торце, первый источник 22 положительного опорного напряжения, второй источник 23 отрицательного опорного напряжения, второй усилитель 24 и второй пьезодефлектор 25 с отражателем на торце, третий источник 26 положительного опорного напряжения, четвертый источник 27 отрицательного опорного напряжения и первый матовый экран 28, последовательно соединенные третий усилитель 29 и третий пьезодефлектор 30 с отражателем на торце, пятый источник 31 положительного опорного напряжения, шестой источник 32 отрицательного опорного напряжения, четвертый усилитель 33 и четвертый пьезодефлектор 34 с отражателем на торце, седьмой источник 35 положительного опорного напряжения, восьмой источник 36 отрицательного опорного напряжения и второй матовый экран 37.

Строчные накопители 21-6 кодов идентичны, каждый включает (фиг.3) первый блок 38 регистров, второй блок 39 регистров и делитель 40 частоты (2:1). Блоки регистров 38 и 39 идентичны (фиг.4, 5), каждый включает первый 41, второй 42, третий 43 и четвертый 44 ключи, первый 45, второй 46, третий 47 и четвертый 48 распределители импульсов, первые восемь регистров 491-8 и вторые восемь регистров 501-8. Пьезодефлекторы 21, 25, 30 и 34 (фиг.6) являются торцевыми биморфными пьезоэлементами со световым отражателем на торце, конструктивно выполнены [2, c.118] из первой 51 и второй 52 пьезопластин, внутреннего электрода 53, первого 54 и второго 55 внешних электродов. Один конец пьезопластин жестко закреплен в держателе 56, на свободном торце расположен световой отражатель 57. Блоки 18, 19 модуляции излучений идентичны (фиг.7), каждый включает первый излучатель 58 трех основных цветов (R, G, В), второй излучатель 59 трех основных цветов и объектив 60. Входами блока являются входы излучателей 58, 59. Выходом являются излучения излучателей, фокусируемые объективом 60 в два цветовых пятна на отражателе своего пьезодефлектора 21, 30, каждый диаметром не более 0,02 мм. Плоскости излучения находятся в задней фокальной плоскости объектива 60, в передней фокальной плоскости которого расположен отражатель пьезодефлектора. Каждый излучатель включает 24 светодиода: 8 - красного цвета излучения, 8 - зеленого и 8 синего цвета излучения. Суммирующий усилитель 16 (фиг.8) включает последовательно соединенные счетчик 61 импульсов, дешифратор 62, ключ 63, формирователь 64 импульсов и выходной усилитель 65. Первым входом является первый вход выходного усилителя 65, вторым - счетный вход счетчика 61 импульсов, управляющим входом является управляющий вход счетчика 61 импульсов и объединенный с ним первый управляющий вход ключа 63.

На 1-6 информационные входы блока 1 управления (фиг.1) с соответствующих выходов видеоадаптера PC (поддерживающего выход на два дисплея) поступают два цифровых видеосигнала (левого и правого кадров), представляемые раздельно 8-разрядными цветовыми сигналами R, G, В. На управляющие 1-3 входы блока 1 с видеоадаптера поступают частота дискретизации 40,8 МГц, кадровые 85 Гц и строчные 51 кГц синхроимпульсы.

Частота дискретизации кодов цветовых сигналов составляет:

600строк×85 Гц×800отсчетов=40,8 МГц

Частота строчных синхросигналов: 600×85 Гц=51 кГц.

При развертке растра двумя строками одновременно частота строк составляет: 51 кГц:2=25,5 кГц. Длительность строки при этом составляет 39,2 мкс (1000 мкс/25,5 кГц).

Блок 9 строчной развертки выдает на входы усилителей 20, 29 линейно изменяющееся напряжение в виде равнобедренного треугольника (фиг.2). Напряжение сигнала сначала возрастает пропорционально времени, отражатели пьезодефлекторов 21, 30 с равномерной скоростью синхронно и синфазно поворачиваются слева направо, по достижении края растра напряжение развертки уменьшается пропорционально времени, отражатели с той же скоростью возвращаются обратно, период управляющего напряжения равен длительности двух строк, поэтому пьезодефлекторы колеблются с частотой 12,75 кГц. Так как развертка растра выполняется двумя строками одновременно за один период колебания пьезодефлектора 21 (30) развертываются четыре строки: две слева направо и две справа налево, развертка строк без обратных ходов и встречная, первая пара строк слева направо (фиг.2), вторая пара строк идет ей навстречу - справа налево. Выполнение такой развертки осуществляют блоки регистров 38, 39. Делитель 10 частоты выполняет деление 4:1, на вход задающего генератора 11 поступают импульсы 12,75 кГц. Задающий генератор 11 формирует управляющие прямоугольные импульсы с периодом 78,4 мкс, которые поступают в выходной каскад 12, формирующий управляющие треугольной формы сигналы с периодом 78,4 мкс. Сигнал с усилителя 12 поступает на внутренний электрод 53 (фиг.6) пьезодефлектора 21, 30, к внешнему электроду 54 приложено напряжение с источника 22 положительного опорного напряжения, к внешнему электроду 55 приложено напряжение с источника 23 опорного напряжения. При подаче управляющего напряжения на внутренний электрод происходит деформация пьезопластин [2 с.122], торец со световым отражателем приходит в колебательное движение и отклоняет луч излучения, выполняя строчную развертку одновременно двух лучей. Коды поступают с блоков 21-6 с в соответствующие блоки 3-8 импульсных усилителей, которых в каждом блоке по 16 штук, используются микросхемы 533АП6 [3, с.128]. Сигналы кодов, усиленные до необходимой величины, запитывают свои светодиоды в излучателях 58, 59. Объектив 60 фокусирует их излучение на отражателях пьезодефлекторов 21, 30, которые выполняют развертку двух строк на отражателях пьезодефлекторов 25, 34, которые выполняют кадровую развертку изображения на экранах 28, 37. Ширина отражателей пьезодефлекторов 21, 30 принимается 1 мм (для облегчения юстировки), длина до 3 мм. Ширина отражателей пьезодефлекторов 25, 34 принимается 2 мм, длина не менее 24 мм (0,03 мм×800). Кадровая развертка с обратным ходом (фиг.2), равным длительности 4-х парных строк: 39,2 мкс×4=156,8 мкс, 1,33% от длительности кадра. Форма управляющего напряжения кадровой развертки представлена на фиг.2. Период развертки 11,76 мс (1000 мс/85). Задающий генератор 15 формирует линейно изменяющееся пилообразное напряжение, поступающее на первый вход суммирующего усилителя 16. На вход задающего генератора 15 поступают импульсы с элемента И 14 в момент прихода на его входы синхронных импульсов строки и кадра. На второй вход суммирующего усилителя 16 поступают с делителя 17 частоты (2:1) импульсы частотой 25,5 кГц. Каждый импульс 25,5 кГц перемещает пару строк в конце растра на шаг в две строки. Назначение блоков с 61 по 64 подавать на второй вход выходного усилителя 65 в нужное время импульсы соответствующей амплитуды и длительности. Счетчик 6-19-разрядный, производит счет импульсов 25,5 кГц, цикл счета 300 импульсов, при поступлении 296-го импульса дешифратор 62 выдает сигнал U3, закрывающий ключ 63. Развертка кадра идет вниз, и следует обратный ход. Блок 1 управления, строчные накопители 21-6 кодов, блоки 3-8 импульсных усилителей, блок 9 строчной развертки и блок 13 кадровой развертки смонтированы совместно в корпусе внешнего блока 66. Блоки 18, 19 модуляции излучений, пьезодефлекторы 21, 25, 30, 34, усилители 20, 24, 29, 33 и источники опорных напряжений смонтированы соответствующим образом непосредственно в шлеме 67. Входы блоков 18, 19 соединены с выходами блоков 3-8 импульсных усилителей многожильным соединительным кабелем с 96-ю информационными линиями (16×6), плюс к ним две управляющие линии: от блока 9 к усилителям 20, 29 и от блока 13 к усилителям 24, 33. Каждый строчный накопитель 2 кодов (фиг.3) включает первый 38 и второй 39 блоки регистров и делитель 40 частоты (2:1). Блок 38 принимает нечетные строки кадра, блок 39 принимает четные строки кадра. Процесс накопления кодов строк начинает блок 38 регистров (фиг.4). Первый ключ 41 (вход 1) открывается импульсом 25,5 кГц с блока 17 и пропускает импульсы дискретизации 40,8 МГцд с блока 1 на вход распределителя 45 импульсов, выдающего с 800 выходов тактовые импульсы UТ. Первые восемь регистров 491-8 и вторые восемь регистров 501-8 включают по 800 разрядов каждый, по числу отсчетов в строке, при нечетных строках заполняются регистры 491-8 в блоке 38, при четных строках заполняются регистры 491-8 в блоке 39. При поступлении следующей пары строк коды нечетной строки заполняют регистры 501-8 в блоке 38, коды четной строки заполняют регистры 501-8 в блоке 39. В регистры 491 и 501 заносятся первые разряды кодов, в регистры 492 и 502 заносятся вторые разряды кодов,... в регистры 498 и 508 заносятся восьмые разряды кодов. Всего в каждый регистр заносятся 800 бит, в 8 регистров 800 байт (6400 бит), первый импульс UТ с блока 45 поступает параллельно на первые (тактовые) входы первых разрядов регистров 491-8, по которому сигналы разрядов первого кода строки поступают в первые разряды регистров 491-8, по второму UТ сигналы разрядов второго кода строки поступают во вторые разряды регистров 491-8 и т.д., при 800-тактовом импульсе сигналы разрядов 800-го кода строки поступают в 800-е разряды регистров 491-8. Сигнал с 800-го выхода блока 48 закрывает ключ 41 и открывает ключ 41 в блоке 39 (фиг.5). Тем же порядком 800 кодов четной строки заполняют регистры 491-8 в блоке 39. Тактовый сигнал с 800-го выхода блока 45 (в блоке 39) поступает на 4-е управляющие входы блоков 38, 39. В блоке 38 этот сигнал открывает ключ 42 и ключ 43. Ключ 42 пропускает сигналы UВЫД 20,4 МГц на вход распределителя 46 импульсов, а ключ 43 пропускает тактовые импульсы 40,8 МГЦ на вход распределителя 47 импульсов. В блоке 39 сигнал с 4-го управляющего входа открывает один ключ 42, пропускающий сигналы UВЫД 20,4 МГц на вход распределителя 46 импульсов. Сигналы UВЫД в блоке 38 выдают коды первой строки с регистров 491-8, а в блоке 39 выдают коды второй строки с регистров 491-8. Так как коды выдаются сигналами 20,4 МГц в два раза меньшей частоты, чем 40,8 МГЦ, то, следовательно, длительность выдаваемых строк увеличивается в два раза и составляет: 19,6 мкс×2=39,2 мкс. Одновременно в блоке 38 распределитель 47 импульсов выдает UТ тактовые импульсы 40,8 МГц на первые входы разрядов регистров 501-8 и коды 3-й строки заносятся в разряды регистров 501-8 Сигнал с 800-го выхода блока 47 в блоке 38 закрывает ключ 43 и открывает ключ 43 (вход) в блоке 39, пропускающий импульсы 40,8 МГЦ на вход распределителя 47 импульсов в блоке 39. В регистры 501-8 блока 39 поступают коды 4-й строки. Затем сигнал с 800-го выхода закрывает ключ 43 и открывает ключи 44 в блоках 38, 39, на входы которых поступают импульсы UВЫД 20,4 МГц, параллельно выдающие коды 3-й и 4-й строк в блоки импульсных усилителей. Коды следующей 5-й строки поступают в освободившиеся регистры 481-8 блока 38, а коды 6-й строки поступают в освободившиеся разряды регистров 491-8 блока 39, Пока коды 5-й и 6-й строк друг за другом заполняют регистры 491-8 в блоках 38 и 39, коды 3-й и 4-й строк выдаются из регистров 501-8 блоков 38, 39 и блоки импульсных усилителей. Так как развертка второй пары строк (3 и 4) выполняется встречно первой паре строк 1 и 2, то и выдача кодов этих строк начинается не с 1-го кода, а с 800-го кода к первому коду. Такой процесс выдачи выполняется сигналами UВЫД с выходов распределителя 48 импульсов, которые подключены к вторым управляющим входам регистров 501-8 в следующем порядке: первый выход подключен к 800-м разрядам регистров, а 800-й выход подключен к первым разрядам регистров. Сигналы кодов со строчных накопителей 21-6 кодов поступают соответственно в блоки 3-8 импульсных усилителей, где усиливаются и поступают с блоков 3, 4, 5 в блок 19 модуляции излучений (фиг.1), с блоков 6, 7, 8 - в блок 18 модуляции излучений. Каждый блок модуляции излучений выполняет яркостную модуляцию трех цветов (R, G, В) в двух излучателях одновременно. Яркостная модуляция выполняется включением на излучение числа светодиодов в излучателе соответственно весам разрядов в коде. Яркость, насыщенность и цветовой тон результирующего цвета с излучателя на экране определяется суммарной энергией и взаимным соотношением цветов в излучателе. Распределение светодиодов и нейтральных светофильтров по весам разрядов в коде приведено в таблице.

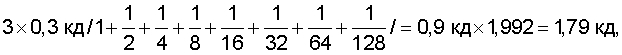

В излучателях применены светодиоды типа HLMP фирмы "Хьюлетт-Паккард" [4, c.71]. Для красного излучения приняты светодиоды HLMP-AL00 с силой света 0,4 кд [4, c.71], длиной волны 0,59 мкм при токе 0,02 А, для зеленого излучения - светодиоды HLMP-АМ00 с силой света 0,8 кд, длиной волны 0,526 мкм при токе 0,02 А, для синего излучения - светодиоды HLMP-АВ00 с силой света 0,3 кд, длиной волны 0,475 мкм при токе 0,02 А. Суммарное излучение светодиодов трех цветов излучателя смешивается объективом 60 при фокусировке в световое пятно диаметром не более 0,02 мм, которое и определяет разрешение изображения и размеры экрана. Суммарная сила света одного излучателя с учетом, что светодиоды всех цветов имеют силу света синего светодиода 0,3 кд, составляет:

где 3 - число цветов в излучателе,

0,3 кд - сила света синего светодиода,

коэффициенты двоичных разрядов с 2 по 8.

коэффициенты двоичных разрядов с 2 по 8.

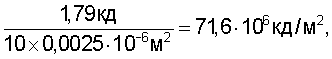

С учетом потерь силы излучения при проекции от излучателя до экрана в 10х раз максимальная яркость одного разрешающего элемента на экране с размером его поперечного сечения 0,5×0,5 мм (0,0025 мм2) составляет:

где 1,79 кд - сила света одного излучателя,

10 - кратность ослабления силы света при проекции,

0,0025·10-6 м2 - площадь разрешающего светового элемента на экране 0,5×0,5 мм.

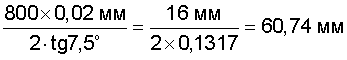

При диаметре сфокусированного пятна от излучателя 0,02 мм и угле 2α отклонения пьезодефлектором 21 в 15° [5, с.56] расстояние от отражателя пьезодефлектора 21 до отражателя пьезодефлектора 25 составляет:

где 800 - число отсчетов в строке,

0,02 мм - диаметр одного разрешающего элемента,

∠7,5° - отклонение луча отражателем пьезодефлектора 21 при колебании.

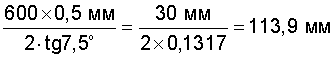

Учитывая расхождение луча при проекции от отражателя пьезодефлектора 25 до экрана 28, диаметр разрешающего элемента на экране принимается диаметром 0,05 мм и при угле 2α отклонения вторым пьезодефлектором 25 то же в 15° расстояние от отражателя пьезодефлектора 25 до экрана. 28 составляет:

где 600 - число строк в кадре,

0,05 мм - диаметр разрешающего элемента на экране,

∠7,5° - угловое отклонение луча отражателем пъезодефлектора 25 (34).

В этом варианте (пьезодефлекторов) размер каждого экрана составляет:

по горизонтали 0,05 мм×800=40 мм,

по вертикали 0,05 мм×600=30 мм,

по диагонали 50 мм или 1,97'' (дюймов).

Пьезодефлекторы 21, 30 по управляющим напряжениям с усилителей 20, 29 выполняют каждый строчную развертку двух строк параллельно на отражателях пьезодефлекторов соответственно 25, 34, выполняющих по управляющим напряжениям с блоков 24, 33 кадровую развертку соответственно на экранах 28, 37. Трехмерное изображение воспринимается зрителем раздельным наблюдением левого кадра стереопары левым глазом на левом экране 37, правого кадра стереопары правым глазом на правом экране 28.

Работа системы.

Для восприятия зрителем трехмерного пространства система виртуальной реальности используется совместно с PC. Блок 1 управления подключается к двум соответствующим цифровым выходам видеоадаптера. На 1-3 информационные входы блока 1 управления поступают коды цветовых сигналов левого кадра стереопары, на 4-6 информационные входы поступают коды цветовых сигналов правого кадра стереопары, на 1-3 управляющие входы поступают импульсы дискретизации UД 40,8 МГц, кадровые и строчные синхроимпульсы. Блок 1 управления выполняет функции коммутирующего устройства, распределяя выдачу кодов цветовых сигналов стереопары на входы шести строчных накопителей 21-6 кодов. Строчные накопители 21 и 24 принимают коды сигналов R соответственно левого и правого кадров, строчные накопители 22 и 25 принимают коды сигналов G левого и правого кадров, строчные накопители 23 и 26 принимают коды сигналов В. С началом кадра коды первой строки, затем второй строки код за кодом заполняют регистры 491-8 сначала в блоке 38, затем в блоке 39. По окончании занесения кодов второй строки коды 3-й строки заполняют регистры 501-8 в блоке 38, затем коды 4-й строки заполняют регистры 501-8 в блоке 39. В это же время коды 1-й и 2-й строк параллельно выдаются в блоки импульсных усилителей, а после усиления сигналов запитывают свои светодиоды для излучения в первом 58 и втором 59 излучателях блока 60 модуляции излучений. Первым излучатель 58 моделированным по яркости лучом воспроизводит первую (нечетную) строку, второй излучатель 59 модулированным по яркости лучом воспроизводит вторую (четную) строку. Развертка кадра параллельно двумя строками позволяет увеличить в 2 раза длительность развертываемых строк, и, следовательно, уменьшить в 2 раза частоту колебаний пьезодефлекторов 21, 30. Во время заполнения кодами 5-й и 6-й строк регистров в блоках 38, 39 на входы импульсных усилителей блоков 3-8 выдаются коды 3-й и 4-й строк и т.д. Коды сигналов R, G, В с блоков 3-5 импульсных усилителей поступают в блок 19 модуляции излучений, коды сигналов R, G, В с блоков 6-8 поступают в блок 18 модуляции излучений. Пьезодефлектор выполняет строчную развертку двух строк на отражателе пьезодефлектора 25, выполняющего кадровую развертку правого кадра на экране 28. Пьезодефлектор 30 выполняет строчную развертку двух строк на отражателе пьезодефлектора 34, выполняющего кадровую развертку левого кадра на экране 37. Для восприятия трехмерного пространства зритель надевает шлем 67 на голову и наблюдает левым глазом левое изображение стереопары и правым глазом правое изображение. Размер каждого экрана 40×30 мм, диагональ 50 мм (1,97''). Разрешение кадра 480000 элементов (800×600). Частота кадров 85 Гц. Входы блоков 18, 19 шлема 67 соединяются с выходами 3-8 блоков импульсных усилителей, смонтированных во внешнем блоке 66, многожильным соединительным кабелем с 96-ю информационными линиями.

Использованные источники.

1. Колесниченко О.В., Шишигин И.В. Аппаратные средства PC. 5-е изд, СПб, 2004, с.557, 558.

2. Фридлянд М.В., Сошников В.Г. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118 рис.5.5, с.122, рис.5.10.

3. Цифровые интегральные микросхемы. Минск, 1991, с.128.

4. "Радио", №7, 1998, с.71.

5. Днепровский Е.В. и др. Расчет элементов лазерных сканирующих систем. Минск, 1986, с.56, табл.2.3.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2304362C2 |

| ЦИФРОВОЙ ПРОЕКТОР | 2005 |

|

RU2292663C1 |

| ЦИФРОВОЙ ПРОЕКТОР | 2005 |

|

RU2276469C1 |

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2284672C1 |

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2004 |

|

RU2270529C1 |

| СТЕРЕОМОНИТОР | 2005 |

|

RU2279190C1 |

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2006 |

|

RU2303334C1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2003 |

|

RU2246796C1 |

| ЦИФРОВОЙ МОНИТОР | 2006 |

|

RU2306676C1 |

| ЦИФРОВОЙ МОНИТОР | 2004 |

|

RU2265286C1 |

Изобретение относится к аппаратным устройствам компьютерного оборудования и используется совместно с персональным компьютером для формирования трехмерного изображения. Технический результат заключается в повышении разрешения изображений на экранах и увеличении частоты кадров. Технический результат достигается тем, что система содержит блок управления, шесть строчных накопителей, шесть блоков импульсных усилителей, блок строчной развертки, блок кадровой развертки, два блока модуляции излучений, четыре усилителя, четыре пьезодефлектора, четыре источника положительного опорного напряжения, четыре источника отрицательного опорного напряжения и два матовых экрана. 8 ил., 1 табл.

Система виртуальной реальности, содержащая блок управления, два соединительных кабеля и шлем, отличающаяся тем, что в нее введены 1-6 строчные накопители кодов, 1-6 блоков импульсных усилителей, входы которых подключены к выходам соответствующих строчных накопителей кодов, блок строчной развертки из последовательно соединенных делителя частоты, вход которого подключен к третьему управляющему выходу блока управления, задающего генератора и выходного каскада, блок кадровой развертки из последовательно соединенных элемента И, первый и второй входы которого подключены к третьему и второму управляющим выходам блока управления, задающего генератора и суммирующего усилителя, и делителя частоты (2:1), вход которого подключен к первому входу элемента И, а выход подключен к второму входу суммирующего усилителя, управляющий вход которого подключен к выходу элемента И, 1-8 информационные входы каждого строчного накопителя кодов подключены к соответствующим 1-8 выходам блока управления, первые управляющие входы строчных накопителей кодов объединены и подключены к выходу делителя частоты в блоке кадровой развертки, вторые управляющие входы строчных накопителей кодов объединены и подключены к первому управляющему выходу блока управления, введены первый блок модуляции излучений, входы которого подключены к выходам 4-6 блоков импульсных усилителей, второй блок модуляции излучений, входы которого подключены к выходам 1-3 блоков импульсных усилителей, последовательно соединенные первый усилитель, вход которого подключен к выходу блока строчной развертки, и первый пьезодефлектор с отражателем на торце, первый источник положительного опорного напряжения, выход которого подключен к вторым входам первого усилителями первого пьезодефлектора, второй источник отрицательного опорного напряжения, выход которого подключен к третьим входам первого усилителя и первого пьезодефлектора, последовательно соединенные второй усилитель, вход которого подключен к выходу блока кадровой развертки, и второй пьезодефлектор с отражателем на торце, третий источник положительного опорного напряжения, выход которого подключен к вторым входам второго усилителя и второго пьезодефлектора, четвертый источник отрицательного опорного напряжения, выход которого подключен к третьим входам второго усилителя и второго пьезодефлектора, и первый матовым экран, оптически соединенный через отражатели второго и первого пьезодефлекторов с излучающей стороной первого блока модуляции излучений, последовательно соединенные третий усилитель, вход которого подключен к выходу блока строчной развертки, и третий пьезодефлектор с отражателем на торце, пятый источник положительного опорного напряжения, выход которого подключен к вторым входам третьего усилителя и третьего пьезодефлектора, шестой источник отрицательного опорного напряжения, выход которого подключен к третьим входам третьего усилителя и третьего пьезодефлектора, последовательно соединенные четвертый усилитель, вход которого подключен к выходу блока кадровой развертки, и четвертый пьезодефлектор с отражателем на торце, седьмой источник положительного опорного напряжения, выход которого подключен к вторым входам четвертого усилителя и четвертого пьезодефлектора, восьмой источник отрицательного опорного напряжения, выход которого подключен к третьим входам четвертого усилителя и четвертого пьезодефлектора, и второй матовый экран, оптически соединенный через отражатели четвертого и третьего пьезодефлекторов с излучающей стороной второго блока модуляции излучений, строчные накопители кодов идентичны, каждый включает последовательно соединенные первый блок регистров и второй блок регистров, и делитель частоты (2:1), первый управляющий вход строчного накопителя кодов является первым управляющим входом первого блока регистров, вторые управляющие входы первого и второго блоков регистров объединены и являются вторым управляющим входом строчного накопителя кодов, к которому подключен вход делителя частоты, выход которого подключен к третьим управляющим входам первого и второго блоков регистров, первый управляющий выход первого блока регистров является первым управляющим входом второго блока регистров, второй управляющий выход первого блока регистров является шестым управляющим входом второго блока регистров, четвертые управляющие входы первого и второго блоков регистров объединены и подключены к первому управляющему выходу второго блока регистров, пятые управляющие входы первого и второго блоков регистров объединены и подключены к второму управляющему выходу второго блока регистров, 1-8 информационные входы первого и второго блоков регистров поразрядно объединены и подключены к соответствующим 1-8 выходам блока управления, 1-8 выходы первого блока регистров подключены к 1-8 входам соответствующего блока импульсных усилителей, 9-16 выходы второго блока регистров подключены к 9-16 входам того же блока импульсных усилителей, первый и второй блоки регистров идентичны, каждый включает последовательно соединенные первый ключ и первый распределитель импульсов, второй ключ и второй распределитель импульсов, третий ключ и третий распрелитель импульсов, четвертый ключ и четвертый распределитель импульсов, первые восемь регистров и вторые восемь регистров, 1-5-м управляющими входами блока регистров являются соответственно первый управляющий вход первого ключа, объединенные сигнальные входы первого и третьего ключей, объединенные сигнальные входы второго и четвертого ключей, первый управляющий вход второго ключа и первый управляющий вход четвертого ключа, в первом блоке регистров первый управляющий вход третьего ключа подключен к первому управляющему входу второго ключа, во втором блоке регистров первый управляющий вход третьего ключа является шестым управляющим входом блока, 1-800 выходы первого распределителя импульсов подключены к первым (тактовым) управляющим входам в каждом регистре в последовательности с 1-го по 800-й разряды первых восьми регистров, 800-й выход первого распределителя импульсов в каждом блоке регистров подключен к второму управляющему входу первого ключа и является первым управляющим выходом блока, 1-800 выходы второго распределителя импульсов подключены к вторым управляющим входам в каждом разряде в последовательности с 1-го по 800-й разряды первых восьми регистров, 800-й выход второго распределителя импульсов подключен к третьим управляющим входам разрядов последовательно с 1-го по 800-й разряды первых восьми регистров и к второму управляющему входу второго ключа, информационные (первые) входы разрядов в каждом регистре первых восьми регистров объединены и являются 1-8 информационными входами блока регистров, выходы разрядов в каждом из первых восьми регистров объединены и являются 1-8 выходами первого блока регистров и 9-16 выходами во втором блоке регистров, 1-800 выходы третьего распределители импульсов подключены к первым (тактовым) управляющим входам разрядов последовательны с 1-го по 800-й разряды вторых восьми регистров, 800-й выход в каждом блоке регистров подключен к второму управляющему входу третьего ключа и является вторым управляющим выходом блока регистров, 1-800 выходы четвертого распределителя импульсов подключены к вторым управляющим входам в каждом разряде в последовательности от 800-го разряда к первому разряду вторых восьми регистров, 800-й выход четвертого распределителя импульсов подключен к второму управляющему входу четвертого ключа, информационные (первые) входы разрядов в каждом регистре вторых восьми регистров объединены и являются 1-8 информационными входами блока регистров, выходы разрядов каждого регистра вторых восьми регистров объединены и являются 1-8 выходами в первом блоке регистров и 9-16 выходами во втором блоке регистров, первый и второй блоки модуляции излучений идентичны, каждый включает первый и второй излучатели и объектив, входами блока модуляции являются входы первого и второго излучателей, входы первого блока модуляции излучений подключены к выходам 4-6 блоков импульсных усилителей, входы второго блока модуляции излучений подключены к выходам 1-3 блока импульсных усилителей, выходом каждого блока модуляции излучении являются излучения первого и второго излучателей, излучающие плоскости которых находятся в задней фокальной плоскости объектива, в передней фокальной плоскости которого находятся отражатели соответственно первого, третьего пьезодефлекторов, суммирующий усилитель блока кадровой развертки содержит последовательно соединенные счетчик импульсов, дешифратор, ключ, формирователь импульсов и выходной усилитель, выход которого является выходом суммирующего усилителя, первый вход выходного усилителя является первым входом суммирующего усилителя, вторым входом которого является вход счетчика импульсов, объединенный с сигнальным входом ключа, управляющим входом является управляющий вход счетчика импульсов, объединенный с первым управляющим входом ключа, блок управления, 1-6 строчные накопители кодов, 1-6 блоки импульсных усилителей, блок строчной развертки и блок кадровой развертки смонтированы совместно в корпусе внешнего блока, первый и второй блоки модуляции излучений, 1-4 усилители, 1-4 пьезодефлекторы, 1-8 источники опорных напряжении, первый и второй матовые экраны соответствующим образом расположены в шлеме, входы первого и второго блоков модуляции излучений с соответствующими выходами 1-6 блоков импульсных усилителей и входы 1-4 усилителей с выходами блока строчной развертки и блока кадровой развертки соединены многожильным кабелем.

| СИСТЕМА ИМИТАЦИИ ВИЗУАЛЬНОЙ ОРИЕНТИРОВКИ ЛЕТЧИКА | 1997 |

|

RU2128860C1 |

| US 6518939 В1, 11.02.2003 | |||

| JP 2000196975, 14.07.2000 | |||

| US 20010009410 А1, 26.07.2001 | |||

| JP 2000152125, 30.05.2000 | |||

| US 5734421 А, 31.05.1998. | |||

Авторы

Даты

2006-08-10—Публикация

2005-04-11—Подача