Изобретение относится к железнодорожному транспорту и может быть использовано в области железнодорожной автоматики и телемеханики, а именно в устройствах для регулирования движения поездов.

Система включает в себя микроЭВМ, обеспечивающую выполнение основных функций по контролю состояния объектов и управлению маршрутами, стрелками светофора и другими объектами станции и прилегающих перегонов с соблюдением требований безопасности движения поездов в соответствии с принципами, принятыми в существующих устройствах электрической централизации (ЭЦ), а также сбор данных о состоянии объекте управления и отдельных релейных схем путем циклического опроса датчиков.

Двухканальная система для регулирования движения железнодорожных транспортных средств, содержащая установленные на релейном пункте железнодорожной станции два процессорных комплекта, работающих синхронно по одинаковой программе, схему встроенного аппаратного контроля, к которой подключены указанные процессорные комплекты и которая предназначена для сравнения работы процессорных комплектов и воздействия на работу системы, если один из комплектов неисправен (Заявка Европейского Патентного Ведомства ЕР 148995). В данной заявке раскрыто устройство схемы для проверки последовательности запуска двухканальной отказоустойчивой системы последовательной логической микроЭВМ, преимущественно для железнодорожного оборудования защиты.

Схемное устройство содержит две микроЭВМ, которые синхронно обрабатывают одинаковую информацию по двум каналам. Сигналы, которыми микроЭВМ проверяются побитно компараторами. Отсутствие выключения (переход в состояние защитного отключения или отказа) происходит только в случае законченного, непрерывного правильного установления последовательности всех разрядных пар.

В блоках памяти содержатся тестирующие программы для использования по крайней мере в течение пуска системы микроЭВМ. Информация представляет собой фиксированное предопределенное число поочередных технологических операций в испытательную программу. Однако данная система имеет ограниченное применение при осуществлении контроля состояния объекта и самоконтроля. Она не может быть использована для сбора данных состояния большого количества объектов, что необходимо при контроле состояния объектов железнодорожной автоматики, которыми оборудованы станции и прилежащие к ним перегоны.

Техническим результатом, на достижение которого направлено данное изобретение, является расширение функциональных возможностей системы, то есть разработка отказоустойчивой системы контроля состояния большого количества объектов на станциях и перегонах с возможностью осуществления функций управления, а также повышение устойчивости ее работы путем использования перехода в состояние защитного отключения или защитного отказа в модулях, предназначенных для реализации ответственных команд, а также более рациональное конструктивное оформление системы в виде блока, в котором содержится несколько модулей.

Технический результат достигается тем, что двухканальная система для регулирования движения железнодорожных транспортных средств, содержащая установленные на релейном пункте железнодорожной станции два процессорных комплекта, работающих синхронно по одинаковой программе, схему встроенного аппаратного контроля, к которой подключены указанные процессорные комплекты и которая предназначена для сравнения работы процессорных комплектов и воздействия на работу системы, если один из комплектов неисправен, представляет собой моноблочную конструкцию и имеет многомодульную структуру, включающую в себя модуль центрального процессора, состоящего из упомянутых двух процессорных комплектов, по меньшей мере, один интерфейсный модуль сбора информации о состоянии объектов контроля железнодорожной станции и прилегающих перегонов, содержащий токовые входы и выходы, предназначенные для подключения к контактам реле объектов контроля, по меньшей мере, железнодорожной станции, интерфейсные модули формирования управляющих сигналов, воздействующих на исполнительные устройства электрической централизации, и интерфейсные модули передачи ответственных команд, причем модуль центрального процессора установлен в моноблоке на первом месте рядом с блоком питания, а упомянутые интерфейсные модули установлены за процессорным модулем, при этом все модули связаны между собой системной шиной, которая состоит из двух идентичных шин, каждая из которых подключена к соответствующему процессорному комплекту.

Система по п.1, отличающаяся тем, что интерфейсный модуль сбора информации о состоянии объектов контроля железнодорожной станции и прилегающих перегонов, связанный с токовыми выходами и входами, представляющий собой средство с возможностью подачи единичного сигнала на токовые выходы, каждый из которых подключен к параллельно соединенным свободным контактам соответствующей контактной группы объектов контроля, а токовые входы предназначены для восприятия параллельного кода, состоящего из нулей и единиц, соответствующих разомкнутым и замкнутым контактам опрашиваемой контактной группы.

Интерфейсный модуль формирования управляющих сигналов выполнен с возможностью сохранения управляющих сигналов на выходах в течение времени, необходимого для реализации команды управления.

Интерфейсный модуль для передачи ответственных команд выполнен с возможностью перехода в состояние защитного отключения или защитного отказа при возникновении внезапных одиночных неисправностей, а также при постепенных отказах.

Интерфейсный модуль сбора информации о состоянии объектов контроля железнодорожной станции и прилегающих перегонов содержит токовые входы и выходы, предназначенные для подключения к контактам реле объектов, прилегающих к железнодорожной станции перегонов.

Система выполнена с возможностью исключения передачи ответственных команд при отказе одного из комплектов.

Схема встроенного аппаратного контроля представляет собой схему сравнения, состоящую из двух каскадов, один из которых включает в себя: два оптрона, первые выводы излучающих элементов первого и второго оптронов подключены соответственно через первый и второй ключевые элементы к отрицательному полюсу источника питания, с которым связаны первые выводы приемных элементов первого и второго оптронов, первый диодный мост, третий ключевой элемент, выход которого через первый конденсатор подключен к соединенным между собой первым и вторым диодам первого диодного моста, к точке соединения первого и третьего диодов первого диодного моста подключен второй вывод излучающего элемента первого оптрона, а второй вывод приемного элемента первого оптрона через первый резистор связан с положительным полюсом источника питания, второй вывод излучающего элемента второго оптрона соединен с одним из выводов второго конденсатора, другим выводом подключенного к отрицательному полюсу источника питания и через диод с одним из выводов третьего конденсатора, причем параллельно цепи, образованной упомянутым диодом и вторым конденсатором, включен другой диод, а между точкой подключения второго вывода излучающего элемента к диодному мосту и отрицательным полюсом источника питания включен четвертый конденсатор, второй вывод приемного элемента второго оптрона через пятый конденсатор подключен к точке соединения третьего и четвертого диодов первого диодного моста и через второй резистор - к положительному полюсу источника питания. Второй каскад включает в себя: третий оптрон, первый вывод излучающего элемента которого подключен к отрицательному полюсу источника питания через четвертый ключевой элемент, вход которого связан со вторым выводом приемного элемента второго оптрона, второй диодный мост, пятый ключевой элемент, выход которого через шестой конденсатор подключен к точке соединения первого и второго диодов второго диодного моста, второй вывод излучающего элемента третьего оптрона подключен к точке соединения первого и третьего диодов второго диодного моста, а к точке соединения второго и четвертого диодов подключен отрицательный полюс источника питания, первый вывод приемного элемента третьего оптрона подключен к отрицательному выводу источника питания, второй вывод приемного элемента третьего оптрона через третий резистор связан с положительным полюсом источника питания, через седьмой конденсатор - с точкой соединения третьего и четвертого диодов второго диодного моста и через девятый диод - с входом шестого - выходного двухкаскадного ключевого элемента. Входы первого и второго ключевых элементов предназначены для подключения к соответствующим выходам контролируемых процессорных комплектов, входы третьего и пятого ключевых элементов являются входами запуска.

На фиг.1 представлена структурная схема двухканальной отказоустойчивой системы для контроля состояния объектов и управления объектами станции и прилегающих перегонов.

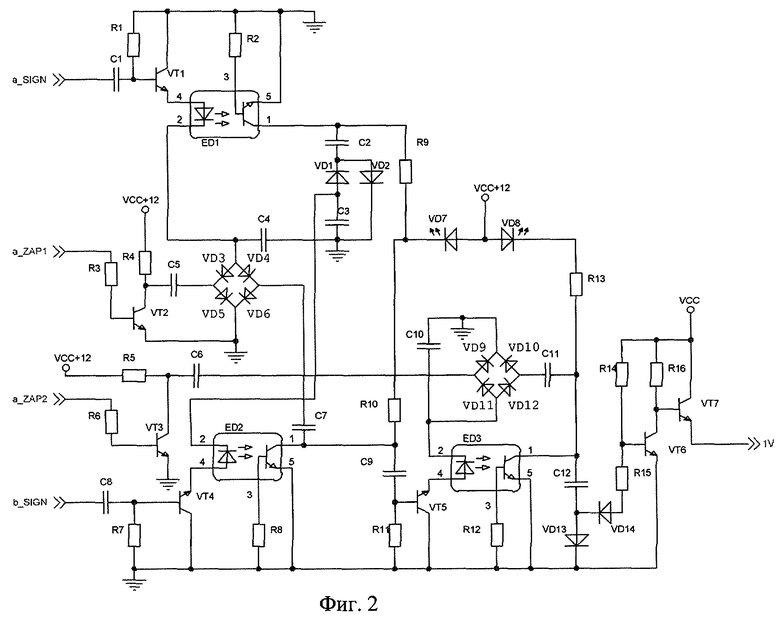

На фиг.2 показана схема встроенного аппаратного контроля.

Система содержит два процессорных комплекта 1 и 2, работающих синхронно по одинаковой программе, схему 3 встроенного аппаратного контроля, к которой подключены указанные процессорные комплекты 1 и 2 и которая предназначена для сравнения работы процессорных комплектов для исключения работы, если один из комплектов неисправен. Система представляет собой моноблочную конструкцию и имеет многомодульную структуру. Причем модуль 4 центрального процессора включает в себя упомянутые два процессорных комплекта. Имеется модуль 5 токовых выходов-входов, выходы которого подключены к параллельно соединенным контактам 6.1-6.п соответствующей контактной группы объектов контроля, образованной контактами реле, не занятыми в других схемах. Входы модуля 5 подключены параллельно к указанным контактам для восприятия параллельного кода, состоящего из нулей и единиц, соответствующих разомкнутым и замкнутым контактам опрашиваемой контактной группы. Система также включает модули 7 релейных выходов, связанные с исполнительными устройствами 8 электрической централизации (ЭЦ). Модули 9 безопасных выходов, предназначенные для реализации ответственных команд, выполнены с возможностью перехода в состояние защитного отключения или защитного отказа при возникновении внезапных одиночных неисправностей, а также при постепенных отказах.

Схема встроенного аппаратного контроля представляет собой схему сравнения и состоит из двух каскадов. Первый каскад включает в себя: два оптрона ED1 и ED2. Первые выводы излучающих элементов оптронов ED1 и ED2 подключены соответственно через первый и второй ключевые элементы к отрицательному полюсу источника питания, с которым связаны первые выводы приемных элементов ED1 и ED2. Первый ключевой элемент включает в себя транзистор VT1, к базовому выводу которого одним выводом подключен конденсатор С1, другим выводом которого образован вход первого ключевого элемента. В цепь смещения транзистора VT1 включен резистор R1. Второй ключевой элемент включает в себя транзистор VT 4, к базовому выводу которого одним выводом подключен конденсатор С8, другим выводом которого образован вход второго ключевого элемента. В цепь смещения транзистора VT4 включен резистор R7. Первый диодный мост включает в себя диоды VD3-VD6. Третий ключевой элемент, выполненный на базе схемы с общим коллектором, включает в себя транзистор VT2, к базовому выводу которого одним выводом подключен резистор R3, другим выводом которого образован вход третьего ключевого элемента. В коллекторную цепь транзистора VT2 включен резистор R4. Третий ключевой элемент через конденсатор С5 подключен к соединенным между собой диодам VD3 и VD5 первого диодного моста. К точке соединения диодов VD3 и VD4 первого диодного моста подключен второй вывод излучающего элемента оптрона ED1, а второй вывод приемного элемента указанного оптрона через резистор R2 связан с положительным полюсом источника питания. Второй вывод излучающего элемента оптрона ED2 соединен с одним из выводов конденсатора С3, другим выводом подключенного к отрицательному полюсу источника питания и через диод VD1 с одним из выводов конденсатора С2. Параллельно цепи, образованной упомянутым диодом и конденсатором С3, включен диод VD2 в направлении, противоположном направлению диода VD1. Между точкой подключения второго вывода излучающего элемента оптрона ED1 к диодному мосту и отрицательным полюсом источника питания включен конденсатор С4, второй вывод приемного элемента оптрона ED2 через конденсатор 7 подключен к точке соединения и диодов VD4 и VD6 первого диодного моста и через резистор R10 - к положительному полюсу источника питания. Второй каскад включает в себя: третий оптрон ED3, первый вывод излучающего элемента которого подключен к отрицательному полюсу источника питания через четвертый ключевой элемент. Четвертый ключевой элемент включает в себя транзистор VT5, к базовому выводу которого одним выводом подключен конденсатор С9, другим выводом которого образован вход четвертого ключевого элемента. В цепь смещения транзистора VT1 включен резистор R11. Вход четвертого ключевого элемента связан со вторым выводом приемного элемента оптрона ED2. Второй диодный мост состоит из диодов VD9-VD12. Пятый ключевой элемент, выполненный на базе схемы с общим коллектором, включает в себя транзистор VT3, к базовому выводу которого одним выводом подключен резистор R6, другим выводом которого образован вход третьего ключевого элемента. Выход пятого ключевого элемента через конденсатор С6 подключен к точке соединения диодов VD9 - VD11 второго диодного моста. Второй вывод излучающего элемента оптрона ED3 подключен к точке соединения диодов VD11 и VD12 второго диодного моста, а к точке соединения диодов VD9 и VD10 подключен отрицательный полюс источника питания. Первый вывод приемного элемента оптрона ED3 подключен к отрицательному выводу источника питания, второй вывод приемного элемента оптрона ED3 через резистор R13 связан с положительным полюсом источника питания, через конденсатор С11 - с точкой соединения диодов VD10 и V14 второго диодного моста и через диод VD14 - с входом шестого - выходного двухкаскадного ключевого элемента (транзисторы VT17, VT18, резисторы R14-R16). Входы первого и второго ключевых элементов предназначены для подключения к соответствующим выходам контролируемых процессорных комплектов, входы третьего и пятого ключевых элементов являются входами запуска.

Система работает следующим образом.

Система обеспечивает выполнение основных функций по контролю состояния объектов и управлению маршрутами, стрелками светофора и другими объектами станции и прилегающих перегонов с соблюдением требований безопасности движения поездов в соответствии с принципами, принятыми в существующих устройствах ЭЦ. При этом осуществляется сбор данных о состоянии объектов управления и отдельных релейных схем путем циклического опроса датчиков, в том числе, фиксируя замкнутое или разомкнутое состояние контакта реле 6.1...6.n. Ввод данных осуществляется с использованием фронтового и тылового контактов указанных реле через устройства гальванической развязки с учетом следующих требований:

- для ввода данных используются контакты реле, не занятые в других схемах;

- ввод данных осуществляется через устройство гальванической развязки с обеспечением полнофункционального контроля цепей сбора и ввода данных;

- питание цепей ввода осуществляется от станционной батареи с рабочим напряжением не ниже 24 В и потребляемом токе входа не менее 5 мА;

- при оценке состояния объекта осуществляется накопление и обработка данных, обеспечивающие их требуемую достоверность при воздействии электромагнитных помех и «дребезга» контактов;

- время обработки сигнала с момента изменения состояния контактов до формирования информации о состоянии объекта не превышает 0,5 с.

Центральный процессор формирует управляющие команды для релейных схем перевода стрелок и открытия светофоров, замыкания стрелок, схем задания разделки и отмены маршрутов, схем смены направления и схем других объектов управления. Выходные цепи, обеспечивающие взаимодействие с реле ЭЦ, гальванически развязаны. Изоляция выходных цепей выдерживает испытательное напряжение 1000 В.

Безопасное функционирование системы обеспечивается:

- двумя процессорными комплектами 1 и 2, работающими синхронно по одинаковой программе. Результаты работы комплектов сравниваются схемой 3 встроенного аппаратного контроля. При отказе одного из комплектов исключается возможность реализации ответственных команд;

- помехозащищенным кодированием с кодовым расстоянием

d>=4;

- применением для реализации ответственных команд модулей с безопасными выходами.

В корпусе моноблока системы устанавливается блок питания, модуль 4 центрального процессора и модули, предназначенные для сбора информации и формирования сигналов управления. Все модули связаны между собой системной шиной (не показана), которая состоит из двух идентичных шин. Процессорный модуль устанавливается рядом с блоком питания. Место установки интерфейсных модулей может быть произвольным, но они должны быть установлены за процессорным модулем.

Состояние объектов контроля определяется по замкнутым или разомкнутым контактам реле. Опрос контактов реле осуществляется по принципу «токовая петля». Для реализации этого принципа модуль 5 содержит 16 токовых выходов и 32 токовых входа. На выходах модуля последовательно появляется единичный сигнал, который подается на контактную группу контролируемых объектов, на выходах опрашиваемой контактной группы формируется параллельный код, состоящий из нулей и единиц (0 - при разомкнутом контакте, 1 - при замкнутом контакте). Данная организация позволяет получить информацию о состоянии 16×32=512 двухпозиционных объектов контроля.

Для увеличения количества контролируемых объектов могут быть установлены дополнительные модули.

Модуль 7 релейных выходов предназначены для формирования управляющих сигналов, воздействующих на схемы исполнительных устройств ЭЦ. Управляющие сигналы на выходах модулей выходов сохраняются в течение времени, необходимого для реализации команды управления, и задаются программным путем.

Модуль 7 может содержать 40 управляющих выходов для реализации простых команд. Все выходы имеют гальваническую развязку (используются релейные выходы). 32 выхода выдают управляющие сигналы через фронтовые контакты исполнительных реле модуля, с возможностью подачи различного питания, 8 выходов выдают управляющие сигналы через фронтовые и тыловые контакты.

Модуль 9 предназначен для реализации ответственных команд. Содержит 16 выходов управления для подключения 16 управляющих реле. Для реализации ответственных команд к безопасным выходам подключаются управляющие реле.

Все интерфейсные модули (5, 7, 9) имеют схему формирования базового адреса (СФА) модуля, который однозначно определяет положение адресного пространства данного модуля в общем адресном пространстве портов системы.

Программное обеспечение (ПО) состоит из трех основных блоков:

- тестирования, предназначенного для проверки внутренних ресурсов модуля ЦП;

- инициализации, предназначенной для проверки конфигурации БМ, наличия подключения внешних цепей, программирования режимов работы модемов и приведения в исходное состояние выходных цепей;

- рабочего цикла, предназначенного для установления и поддержания обмена информацией с другими абонентами, сбора и обработки информации о состоянии объектов контроля, выдачи управляющих сигналов на объекты управления и диагностики состояния системы.

Первые два блока ПО являются одинаковыми для любого применения системы и представляют собой системное ПО. Блок рабочего цикла изменяется в зависимости от применения системы и представляет собой прикладное ПО.

Блок тестирования предназначен для проверки исправности микросхемы процессора, микросхем ПЗУ и ОЗУ модуля 4 и состоит, соответственно, из трех частей. Исправность микросхемы процессора определяется по результатам выполнения контрольных операций с регистрами процессора: пересылки данных, установки и сброса битов в регистре флагов, выполнения побитовых операций и др. Заключение об исправности микросхем ПЗУ делается при условии совпадения контрольной суммы и суммы, полученной в результате сложения программного кода по модулю два. Для проверки ОЗУ применен тест «Сдвигаемая диагональ». Любая ошибка в процессе тестирования приводит к выводу на индикатор модуля ЦП соответствующего кода и перезапуску.

Блок инициализации состоит из следующих частей:

- инициализации и программирования схемы встроенного контроля;

- инициализации и программирования схемы защиты от зависания; организации программного стека;

- инициализации и программирования системных таймеров реального времени; инициализации и программирования контроллера прерываний; проверки конфигурации; инициализации и программирования портов.

Для работы схемы встроенного контроля необходимо программировать два канала одного из системных таймеров, входящих в модуль 4, посредством записи управляющих слов и коэффициентов деления в соответствующие порты его ввода/вывода.

Схема защиты от «зависания» контролирует непрерывность выполнения рабочего цикла и построена на одном канале системного таймера. Инициализация и программирование данной схемы состоит в задании режима работы канала системного таймера посредством записи управляющего слова и коэффициента деления в соответствующие порты ввода/вывода.

Система работает в режиме реального времени.

В блоке инициализации проверяется конфигурация системы для выполнения поставленной задачи. Проверка конфигурации основана на том, что модуль, правильно установленный в корпус и имеющий правильно подключенные внешние цепи, "знает" свой адрес и "отвечает" на запрос модуля 4 по этому адресу. Если конфигурация системы удовлетворяет поставленной задаче, внешние цепи приводятся в исходное состояние посредством записи в соответствующие управляющие регистры начальных значений (зависят от конкретной задачи), в противном случае выводится код соответствующей ошибки и происходит сброс.

Работа системы начинается с подачи питания на адресные входы СФА периферийных модулей.

На этапе тестирования, инициализации и работы можно отслеживать состояние модуля 4 по показаниям семи сегментных индикаторов на его лицевой панели. В начале тестирования включается первый каскад схемы 3 сравнения (СС).

Каждый из комплектов 1 и 2 модуля 4 проверяет исправность собственных: процессора, постоянного запоминающего устройства (ПЗУ) и оперативного запоминающего устройства (ОЗУ). По окончании тестирования ОЗУ МБ проверяют работу первого каскада схемы 3 СС. Если каскад работает исправно и тестовые сигналы с МБ одинаковые, происходит запуск ее второго каскада.

На этапе тестирования проверяют наличие подключенных периферийных модулей. Проверка осуществляется путем запроса типа модуля по определенным адресам портов модулей. Если модуль установлен и на его СФА подано соответствующее напряжение, он отвечает на запрос. Опросив таким образом все возможные адреса, система принимает решение о конфигурации.

Испытания схемы аппаратного контроля на безопасность проводились путем моделирования внезапных и постепенных отказов в элементах схем.

Далее под опасным отказом понимается неработоспособное состояние схемы, при котором формируется динамический управляющий сигнал во время несинхронной работы каналов; защитный отказ - это неработоспособное состояние схемы, при котором динамический управляющий сигнал не формируется во время синхронной работы каналов; защитное отключение - это работоспособное состояние схемы, при котором динамический управляющий сигнал не формируется во время несинхронной работы каналов.

В процессе испытаний моделировались:

- одиночные неисправности (обрывы и короткие замыкания) элементов схемы: резисторов, конденсаторов, диодов, транзисторов, оптопар, светодиодов;

- замыкания выводов источников питания на соответствующие выводы элементов;

- постепенные отказы оптронов и транзисторов путем введения цепей утечки между выводами элементов и измерения критической величины сопротивления этой утечки.

Также создавались условия самовозбуждения транзисторов выходных ключей путем введения обратной связи по току и напряжению и проводились испытания, не приводящие к нарушению работоспособности схемы, остальные испытания проводились путем логического анализа работы схемы.

Моделирование отказов производилось при работоспособном и неработоспособном (рассинхронизированном) состоянии контролируемых комплектов.

Как уже упоминалось выше, схема сравнения функционально состоит из двух каскадов. Первый каскад включает элементы R1-R4, R7-R10, С1-С5.С7. С8, ED1, ED2, VT1, VT2, VT4, VD1-VD7. Второй каскад состоит из элементов R5, R6, R11-R16, С6, С9-С12, ED3, VT3, VTS VT7,VD8-VD14.

Работа каскадов схемы сравнения построена на перезаряд конденсаторов и создания отрицательного напряжения на обкладках конденсаторов за счет реализации принципа инверторов напряжения.

Работа безопасной схемы сравнения начинается с приходом импульса запуска первого каскада положительной полярности на первый вход запуска a_ZAP1. При этом на выводе оптрона ED2 формируется отрицательный потенциал, который создает начальные условия для работы первого каскада схемы. В случае успешного включения первого каскада схемы сравнения, на второй вход запуска a_ZAP2 поступает импульс запуска второго каскада положительной полярности. При этом на выводе 2 оптрона ED формируется отрицательный потенциал, создающий начальные условия для работы второго каскада.

На входы a_SIGN и b_SIGN первого каскада безопасной схемы сравнения поступают динамические сигналы с выходов сигнатурных анализаторов соответственно первого и втрого контролируемых процессорных комплектов, находящиеся между собой в противофазе.

На выходе безопасной схемы сравнения формируется динамический сигнал, необходимый для работы выходных безопасных каскадов модулей Выходов Безопасных Выходов.

Результаты испытаний показали следующее:

- обрыв цепей резисторов R1, R2, R7, R9, R10 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей резисторов R11...R16 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей резисторов R3...R6 определяет работоспособность первоначального запуска и повторного перезапуска безопасной схемы сравнения и приводит к ее защитному отключению;

- обрыв цепей конденсаторов С1...С4, С7, С8 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей конденсаторов С9...С12 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей конденсаторов С5, С6 определяет работоспособность первоначального запуска и повторного перезапуска безопасной схемы сравнения и приводит к ее защитному отключению;

- обрыв цепей эмиттер-коллектор и выводов базы транзисторов VT1, VT4 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей эмиттер-коллектор и выводов базы транзисторов VT5...VT7 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей эмиттер-коллектор и выводов базы транзисторов VT2, VTS определяет работоспособность первоначального запуска и повторного перезапуска безопасной схемы сравнения и приводит к ее защитному отключению;

- обрыв цепей светодиодов и фототранзисторов оптронов ED1, ED2 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей светодиода и фототранзистора оптрона ED3 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей диодов VD1...VD6 и светодиода VD7 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв цепей диодов VD9-VD14 и светодиода VD8 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание цепей резисторов R1, R2, R7, R9, R10 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание цепей резисторов R 11... R 16 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание цепей резисторов R3...R6 определяет работоспособность первоначального запуска и повторного перезапуска безопасной схемы сравнения и приводит к ее защитному отключению;

- короткое замыкание цепей конденсаторов С1...С4, С7, С8 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание цепей конденсаторов С9...С12 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание цепей конденсаторов С5, С6 определяет работоспособность первоначального запуска и повторного перезапуска безопасной схемы сравнения и приводит к ее защитному отключению;

- короткое замыкание переходов эмиттер-коллектор, база-эмиттер, база-коллектор транзисторов VT1, VT4 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание переходов эмиттер-коллектор, база-эмиттер, база-коллектор транзисторов VT5...VT7 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание переходов эмиттер-коллектор, база-эмиттер, база-коллектор транзисторов VT2, VT3 определяет работоспособность первоначального запуска и повторного перезапуска безопасной схемы сравнения и приводит к ее защитному отключению;

- короткое замыкание светодиодов и переходов эмиттер-коллектор, база-эмиттер, база-коллектор фототранзисторов и между другими выводами оптронов ED1, ED2 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- обрыв, короткое замыкание светодиода и переходов эмиттер-коллектор, база-эмиттер, база-коллектор фототранзистора и между другими выводами оптрона ED3 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание между выводами диодов VD1...VD6 и светодиода VD7 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- короткое замыкание между выводами диодов VD9-VD14 и светодиода VD8 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- изменение временных параметров управляющих сигналов a_SIGN и b_SIGN приводит к защитному отключению безопасной схемы сравнения;

- имитация утечки между выводами база-эмиттер, база-коллектор транзисторов VT1, VT4 определяет работоспособность первого каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- имитация утечки между выводами база-эмиттер, база-коллектор транзисторов VT5...VT7 определяет работоспособность второго каскада безопасной схемы сравнения и приводит к ее защитному отказу;

- имитация утечки между выводами база-эмиттер, база-коллектор транзисторов VT2, VT3 определяет работоспособность первоначального запуска и повторного перезапуска безопасной схемы сравнения и приводит к ее защитному отключению;

- имитация утечки между выводами база-эмиттер, база-коллектор фототранзисторов оптронов ED1...ED3 приводит к защитному отказу безопасной схемы сравнения или сохранению ее работоспособности в зависимости от величины сопротивления утечки;

- изменение в пределах 50% емкостей конденсаторов С1...С4, С7-С12 от номинальных значений приводит к защитному отключению безопасной схемы сравнения.

Таким образом, одиночные отказы (обрывы, короткие замыкания) элементов безопасной схемы сравнения не приводят к опасным отказам.

При постепенных отказах ряда элементов, безопасная схема сравнения сохраняет свою работоспособность до определенных пределов сопротивлений утечек, а при изменении вне этих пределов переходит в состояние защитного отказа.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЕЗОПАСНАЯ СХЕМА "2И" | 2008 |

|

RU2370395C1 |

| ДВУХКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГУЛИРОВАНИЯ ДВИЖЕНИЯ ПОЕЗДОВ | 2013 |

|

RU2536990C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2009612C1 |

| СХЕМА КОНТРОЛЯ | 1997 |

|

RU2153765C2 |

| СПОСОБ СРАВНЕНИЯ КОНТРОЛЬНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2642347C1 |

| Двухканальная система для регулирования движения железнодорожных транспортных средств | 2020 |

|

RU2726243C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2030832C1 |

| ИНТЕРФЕЙСНАЯ СХЕМА ЦИФРОВОЙ СВЯЗИ ДЛЯ ПРОВОДНОЙ ПАРЫ С ИНДИВИДУАЛЬНО РЕГУЛИРУЕМЫМИ ГРАНИЦАМИ ПЕРЕХОДА | 2013 |

|

RU2624452C2 |

| Источник питания для электронной аппаратуры | 2022 |

|

RU2812647C1 |

| УСТРОЙСТВО-КОНТРОЛЛЕР ДЛЯ УПРАВЛЕНИЯ СВЕРХЪЯРКИМИ СВЕТОДИОДАМИ В АКТИВНЫХ СВЕТОФОРНЫХ ГОЛОВКАХ | 2008 |

|

RU2378706C1 |

Изобретение относится к железнодорожному транспорту и может быть использовано в области железнодорожной автоматики и телемеханики, а именно в устройствах для управления движением поездов. Система содержит два процессорных комплекта, работающих синхронно по одинаковой программе, схему встроенного аппаратного контроля, к которой подключены указанные процессорные комплекты и которая предназначена для сравнения работы процессорных комплектов и воздействия на работу системы, если один из комплектов неисправен. Система представляет собой моноблочную конструкцию и имеет многомодульную структуру, включающую в себя модуль центрального процессора, состоящего из упомянутых двух процессорных комплектов, по меньшей мере, один интерфейсный модуль сбора информации о состоянии объектов контроля железнодорожной станции и прилегающих перегонов, интерфейсные модули формирования управляющих сигналов, воздействующих на исполнительные устройства электрической централизации, и интерфейсные модули передачи ответственных команд. Все модули связаны между собой системной шиной, которая состоит из двух идентичных шин, каждая из которых подключена к соответствующему процессорному комплекту. Техническим результатом, на достижение которого направлено данное изобретение, является расширение функциональных возможностей системы, то есть разработка отказоустойчивой системы для контроля состояния большого количества объектов на станциях и перегонах с возможностью осуществления функций управления, а также повышение устойчивости ее работы путем использования перехода в состояние защитного отключения или защитного отказа в модулях, предназначенных для реализации ответственных команд. 2 н. и 5 з. п. ф-лы, 2 ил.

два оптрона, первые выводы излучающих элементов первого и второго оптронов подключены соответственно через первый и второй ключевые элементы к отрицательному полюсу источника питания, с которым связаны первые выводы приемных элементов первого и второго оптронов,

первый диодный мост,

третий ключевой элемент, выход которого через первый конденсатор подключен к соединенным между собой первым и вторым диодам первого диодного моста, к точке соединения первого и третьего диодов первого диодного моста подключен второй вывод излучающего элемента первого оптрона, а второй вывод приемного элемента первого оптрона через первый резистор связан с положительным полюсом источника питания, второй вывод излучающего элемента второго оптрона соединен с одним из выводов второго конденсатора, другим выводом подключенного к отрицательному полюсу источника питания и через диод с одним из выводов третьего конденсатора, причем параллельно цепи, образованной упомянутым диодом и вторым конденсатором, включен другой диод, а между точкой подключения второго вывода излучающего элемента к диодному мосту и отрицательным полюсом источника питания включен четвертый конденсатор, второй вывод приемного элемента второго оптрона через пятый конденсатор подключен к точке соединения третьего и четвертого диодов первого диодного моста и через второй резистор - к положительному полюсу источника питания,

второй каскад включает в себя:

третий оптрон, первый вывод излучающего элемента которого подключен к отрицательному полюсу источника питания через четвертый ключевой элемент, вход которого через шестой конденсатор связан со вторым выводом приемного элемента второго оптрона,

второй диодный мост,

пятый ключевой элемент, выход которого через седьмой конденсатор подключен к точке соединения первого и второго диодов второго диодного моста, второй вывод излучающего элемента третьего оптрона подключен к точке соединения первого и третьего диодов второго диодного моста, а к точке соединения второго и четвертого диодов подключен отрицательный полюс источника питания, первый вывод приемного элемента третьего оптрона подключен к отрицательному выводу источника питания, второй вывод приемного элемента третьего оптрона через третий резистор связан с положительным полюсом источника питания, через восьмой конденсатор - с точкой соединения третьего и четвертого диодов второго диодного моста и через девятый диод - с входом шестого - выходного двухкаскадного ключевого элемента, при этом входы первого и второго ключевых элементов предназначены для подключения к соответствующим выходам контролируемых процессорных комплектов, входы третьего и пятого ключевых элементов являются входами запуска.

| Поливальщик шланговый навесной | 1961 |

|

SU148995A1 |

| РЕЛЕЙНО-КОМПЬЮТЕРНАЯ ЦЕНТРАЛИЗАЦИЯ | 1999 |

|

RU2173278C2 |

| Роликовая раскатка | 1985 |

|

SU1318388A2 |

| US 3836768, 17.09.1974 | |||

| US 4096990, 27.06.1978. | |||

Авторы

Даты

2006-10-27—Публикация

2004-09-17—Подача