Изобретение относится к области железнодорожной автоматики и телемеханики, а именно к системам для регулирования движения поездов, и может быть использовано на локомотивах, моторвагонных подвижных составах, а также в составе многоуровневой системы интервального регулирования.

Известна двухканальная система для регулирования движения железнодорожных транспортных средств, содержащая установленные на релейном пункте железнодорожной станции два процессорных комплекта, работающих синхронно по одинаковой программе, схему встроенного аппаратного контроля, к которой подключены указанные процессорные комплекты и которая предназначена для сравнения работы процессорных комплектов и воздействия на работу системы, если один из комплектов неисправен, система представляет собой моноблочную конструкцию и имеет многомодульную структуру, включающую в себя модуль центрального процессора, состоящего из упомянутых двух процессорных комплектов, по меньшей мере, один интерфейсный модуль сбора информации о состоянии объектов контроля железнодорожной станции и прилегающих перегонов, содержащий токовые входы и выходы, предназначенные для подключения к контактам реле объектов контроля, по меньшей мере, железнодорожной станции, интерфейсные модули формирования управляющих сигналов, воздействующих на исполнительные устройства электрической централизации, и интерфейсные модули передачи ответственных команд, причем модуль центрального процессора установлен в моноблоке на первом месте рядом с блоком питания, а упомянутые интерфейсные модули установлены за процессорным модулем, при этом все модули связаны между собой системной шиной, которая состоит из двух идентичных шин, каждая из которых подключена к соответствующему процессорному комплекту (RU 2286279, B61L 27/04, 27.02.06).

Недостатком известной системы является низкая надежность, обусловленная тем, что к блоку встроенного аппаратного контроля безопасности функционирования каналов микропроцессорной обработки информации одновременно предъявляются требования к сохранению защищенности от накопления неисправностей и требования работоспособности в широком диапазоне изменения параметров элементов и напряжений питания и при ряде специфических неисправностей их элементов. Выполнение этих противоречивых условий требует усложнения каскадов одноразрядного сравнения двоичных сигналов и снижает рабочие диапазоны изменения параметров элементов, при которых сохраняется работоспособность. Наиболее жесткие ограничения вызваны тем, что каскады безопасного сравнения двоичных сигналов должны обладать пороговыми свойствами для фиксации таких отказов микропроцессоров, когда на их выходах появляются сигналы высокочастотной генерации или сигналы постоянного напряжения, имеющие плавающий уровень, в особенности в области половины уровня напряжения нормального сигнала логической единицы.

Из известных систем наиболее близкой к заявляемой системе по своей структуре и функциям является двухканальная система для регулирования движения поездов, содержащая в каждом из каналов управления первый и второй микропроцессоры, связанные между собой через системный CAN-интерфейс и блок встроенного аппаратного контроля безопасности их функционирования, первые и вторые входы которого соединены соответственно с контрольными выходами первого микропроцессора и с контрольными выходами второго микропроцессора, выход блока встроенного аппаратного контроля соединен с усилителем, выход которого является выходом канала управления, выходы первого и второго каналов управления через блок сопряжения с цепями управления локомотивом соединены с соответствующими обмотками электропневматических клапанов экстренного торможения поезда (Астрахан В.И. и др. «Унифицированное комплексное локомотивное устройство безопасности (КЛУБ-У)», М., 2008. Учебно-методический центр по образованию на железнодорожном транспорте, с.39, рис.2.4).

Недостатком этой двухканальной системы для регулирования движения поездов является невысокая надежность работы блока встроенного аппаратного контроля безопасности в широком диапазоне изменения параметров элементов, температуры и напряжений питания.

Технический результат изобретения заключается в повышении надежности работы двухканальной системы для регулирования движения поездов без ухудшения уровня ее безопасности.

Технический результат достигается тем, что в двухканальной системе для регулирования движения поездов, содержащей в каждом канале управления первый и второй микропроцессоры, связанные системным CAN-интерфейсом, блок питания, блок встроенного аппаратного контроля, первые и вторые входы которого соединены с контрольными выходами соответственно первого и второго микропроцессоров, выход блока встроенного аппаратного контроля соединен через усилитель с выходом первого канала управления, выходы первого и второго каналов управления через блок сопряжения соединены с соответствующими обмотками электропневматических клапанов экстренного торможения поезда, согласно изобретению контрольные выходы первого микропроцессора через первые развязывающие резисторы соединены с контрольными входами второго микропроцессора, а контрольные выходы второго микропроцессора через вторые развязывающие резисторы соединены с контрольными входами первого микропроцессора, каждый из микропроцессоров содержит, по меньшей мере, один встроенный таймер и один аналого-цифровой преобразователь с интерфейсом поочередного подключения его к источнику питания и контрольным выходам микропроцессора своего канала управления.

В двухканальной системе регулирования движения поездов блок питания может включать в себя отдельные источники питания микропроцессоров, одни полюса этих источников объединены, а другой полюс источника питания одного микропроцессора через развязывающий резистор соединен с дополнительным входом другого микропроцессора.

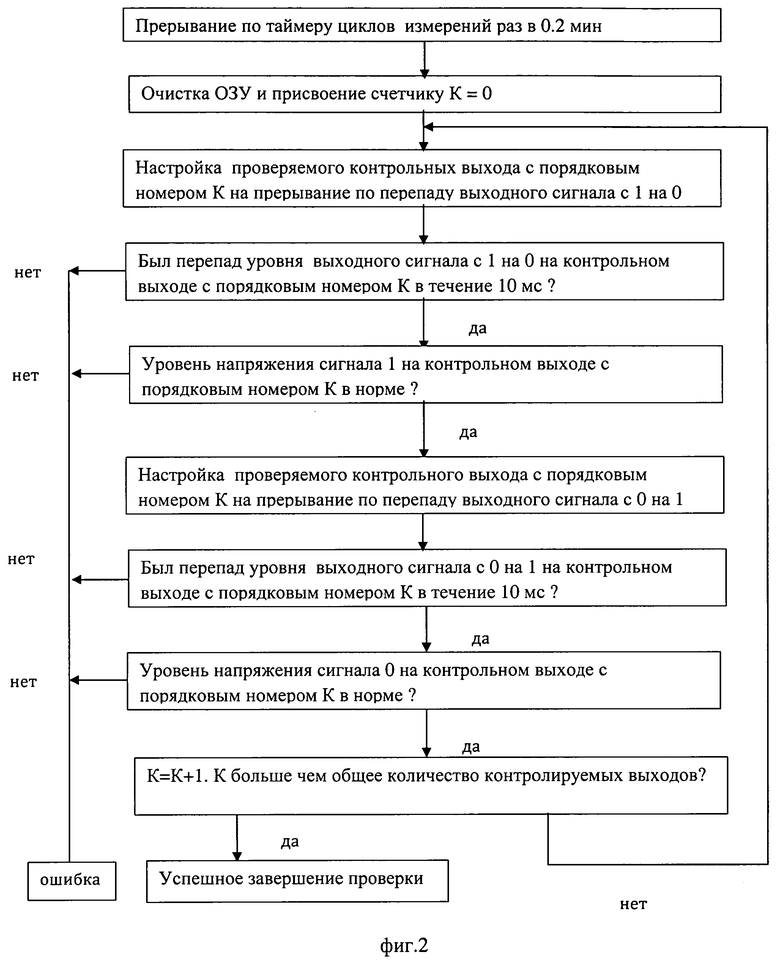

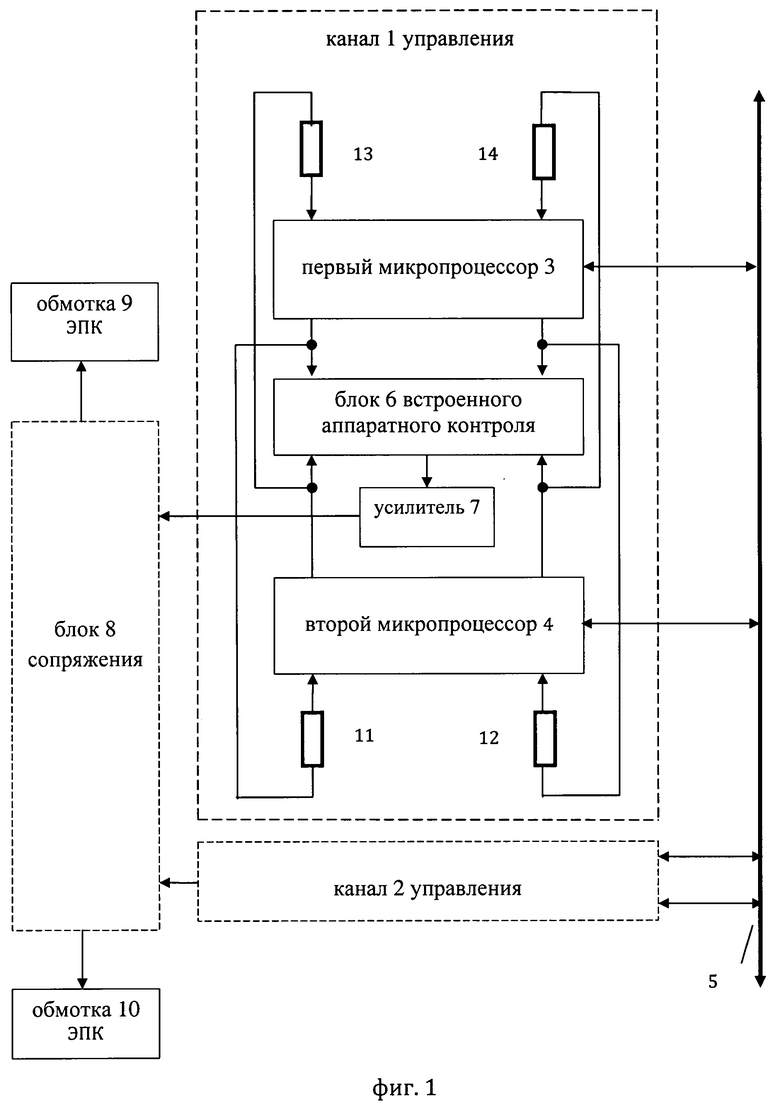

На чертеже (фиг.1) приведена схема предлагаемой двухканальной системы для регулирования движения поездов, на фиг.2 представлена блок-схема основного алгоритма проверки сигналов на контрольных выходах микропроцессоров одного канала управления.

Двухканальная система для регулирования движения поездов содержит каналы 1 и 2 управления. Каждый канал управления содержит первый и второй микропроцессоры 3 и 4, связанные системным CAN - интерфейсом 5, блок питания (на чертеже не показан), блок 6 встроенного аппаратного контроля, первые и вторые входы которого соединены с контрольными выходами соответственно первого и второго микропроцессоров 3 и 4, выход блока 6 встроенного аппаратного контроля соединен через усилитель 7 с выходом первого канала 1 управления, выходы первого и второго каналов 1 и 2 управления через блок 8 сопряжения соединены с соответствующими обмотками электропневматических клапанов 9, 10 экстренного торможения поезда, контрольные выходы первого микропроцессора 3 через первые развязывающие резисторы 11 и 12 соединены с контрольными входами второго микропроцессора 4, а контрольные выходы второго микропроцессора 4 через вторые развязывающие резисторы 13 и 14 соединены с контрольными входами первого микропроцессора 3, каждый из микропроцессоров 3 и 4 содержит (на чертеже не показано), по меньшей мере, один встроенный таймер и один аналого-цифровой преобразователь с интерфейсом поочередного подключения его к источнику питания и контрольным выходам микропроцессора своего канала управления.

Двухканальная система для регулирования движения поездов работает следующим образом.

Каналы 1 и 2 управления и другие бортовые устройства системы управления движением поезда взаимодействуют между собой посредством системного CAN-интерфейса 5. Каждый канал 1 и 2 управления циклически, с периодичностью 450-500 мс выдает в системный CAN-интерфейс 5 информацию о своем состоянии и результаты своей работы. Вместе с тем каждый канал 1, 2 управления выделяет из сообщений, приходящих из системного CAN-интерфейса 5, информацию, необходимую ему для обработки данных и формирования команд управления движением.

При непрерывном соответствии динамически меняющихся двоичных данных на контрольных выходах микропроцессоров 3 и 4 своего канала управления 1 или 2, блок 6 встроенного аппаратного контроля формирует на своем выходе непрерывный динамический сигнал исправной работы. Сигналы от блоков 6 встроенного аппаратного контроля каналов управления 1, 2 логически обрабатываются в блоке 8 сопряжения с цепями управления локомотивом. Если сигнал на выходе любого блока 6 прерывается на время более чем 6 секунд, то блок 8 сопряжения отключает питание обмотки 9, 10 соответствующего клапана торможения и происходит экстренное торможение поезда.

Блок 6 встроенного аппаратного контроля безопасности функционирования микропроцессоров 3 и 4 осуществляет сравнение контрольных слов, формируемых в процессе синхронной работы микропроцессоров 3 и 4 по обработке одинаковой входной информации и выдаче команд для управления движением поездов. Блок 6 состоит (на чертеже не показано) из каскадов безопасного одноразрядного сравнения, подключенных к соответствующим контрольным выходам микропроцессоров 3 и 4, выходы каскадов безопасного одноразрядного сравнения включены последовательно в цепь контрольного сигнала. На вход первого каскада контрольный сигнал поступает от генератора контрольного сигнала. Если проверяемые двоичные слова, формируемые микропроцессорами 3 и 4, соответствуют друг другу, контрольный сигнал проходит непрерывно от выхода генератора последовательно через все каскады безопасного одноразрядного сравнения на выход последнего каскада и далее через усилитель 7 и блок 8 сопряжения на вход исполнительных цепей управления - цепей питания обмоток 9, 10 соответствующего клапана экстренного торможения поезда. Даже при кратковременном несоответствии проверяемых двоичных слов хотя бы в одном разряде цепь прохождения контрольного сигнала прерывается и для возобновления требует перезапуска микропроцессоров 3 и 4 извне.

Кроме случаев, когда экстренное торможение требуется по условиям управления движением поезда, оно может произойти из-за длительного нарушения соответствия данных на контрольных выходах микропроцессоров 3 и 4. Такое несоответствие данных может возникнуть как из-за сбоев в логической обработке информации в микропроцессорах 3 и 4, так и генерироваться микропроцессорами 3 и 4 специально для прекращения работы или перезапуска канала управления при обнаружении ими условий, когда дальнейшее функционирование канала 1 или 2 управления может привести к опасному отказу. В предлагаемой системе этот метод прекращения работы канала управления используется, в частности, для прекращения работы канала управления при обнаружении микропроцессорами 3 и 4 друг у друга накопления неисправностей аналогового типа. Это происходит при выявлении нахождения уровней напряжений логических сигналов и напряжений питания вне разрешенных допусков во время периодического тестирования.

Поскольку проверяется только логическое и временное соответствие логических сигналов на контрольных выходах микропроцессоров 3 и 4, упрощаются требования к блоку 6 встроенного аппаратного контроля.

При работе предлагаемой системы периодическое тестирование напряжений логических сигналов и напряжений питания организовано посредством периодических прерываний нормальной работы микропроцессоров 3 и 4 их внутренними таймерами. В процессе этих прерываний используют дополнительные прерывания по изменениям логических сигналов с 1 на 0 и с 0 на 1 на контрольных выходах, при каждом из которых с помощью внутренних аналого-цифровых преобразователей микропроцессоров 3, 4 тестируются уровни напряжений логических сигналов. В процессе тестирования также используют прерывания по сигналам завершения аналого-цифрового преобразования встроенными аналого-цифровыми преобразователями. Внутренние узлы микропроцессоров 3 и 4 стандартны и для упрощения на чертеже не показаны.

На Фиг.2 приведена блок-схема основного алгоритма проверки правильности по уровню сигналов на контрольных выходах микропроцессоров 3 и 4 одного канала управления. Начало цикла проверки инициируется очередным периодическим прерыванием внутренним таймером проверяющего микропроцессора. Вначале один микропроцессор проверяет другой, а потом они обмениваются своими функциями: если проверяется микропроцессор 3, то проверяющий микропроцессор 4 по прерыванию своим внутренним таймером подключает вход своего внутреннего аналого-цифрового преобразователя сначала к полюсу общего источника питания (на чертеже источники питания не показаны) или, при раздельных источниках питания, к полюсу питания проверяемого микропроцессора 3 и измеряет с помощью своего аналого-цифрового преобразователя его питающее напряжение. После генерации этим аналого-цифровым преобразователем своего сигнала прерывания внутри процедуры обработки прерывания от аналого-цифрового преобразователя измеренное напряжение питания проверяется на соответствие допускам, характеризующим нормальную работу источника питания. Измеренное напряжение и логический результат проверки заносятся в блок оперативной памяти ОЗУ проверяющего микропроцессора 4. После этого последовательно проверяется на соответствие допускам напряжения логических сигналов на всех контрольных выходах микропроцессора 3. Для этого внутренний аналого-цифровой преобразователь микропроцессора 4 поочередно подключается через связанные с ними через первые развязывающие резисторы 11, 12 к контрольным выходам микропроцессора 3. Величины сопротивлений резисторов 11 и 12 выбираются так, чтобы исключить возможность подпитки через них каскадов блоков 6 аппаратного контроля безопасности током, влияющим на их безопасное функционирование.

Порядковый номер проверки очередного проверяемого выхода микропроцессора 3 заносится во внутренний счетчик проверяющего микропроцессора 4, который определяет, что проверен последний проверяемый выход микропроцессора 3, завершена проверка микропроцессора 3 и возможен переход к проверке микропроцессора 4. В конце успешного завершения проверки микропроцессора, счетчик инициирует посылку сообщения об успешном завершении проверки в системный CAN-интерфейс 5 для извещения системы управления движением об исправности соответствующего микропроцессора 3 или 4 канала управления. При возникновении в процессе проверки ошибок, проверяющий микропроцессор формирует сигнал неисправности, который вызывает перезапуск канала и немедленное повторение проверки. Если ситуация повторяется подряд заданное количество раз, то канал управления отключается и система переходит на управление от другого канала управления движением поезда.

Из представленной на фиг.2 блок-схемы основного алгоритма видно, что проверяющий микропроцессор настраивает свой первый вход проверки уровней логических сигналов на соответствующем первом контрольном выходе проверяемого микропроцессора на генерацию прерывания вначале по смене сигнала с 1 на 0, а затем по смене сигнала с 0 на 1. При наступлении прерывания микропроцессор подключает вход своего внутреннего аналого-цифрового преобразователя к входу проверяемого сигнала для измерения на нем уровня напряжения.

При исправной работе проверяемого микропроцессора аналого-цифровой преобразователь гарантированно успевает завершить свою работу до следующего прерывания по изменению логического уровня сигнала.

При неисправной работе проверяемого микропроцессора, например, при автогенерации высокочастотного сигнала на проверяемом выходе, даже если возникает прерывание, уровень напряжения, измеренный аналого-цифровым преобразователем, выйдет за границы допусков. При неисправности «плавающий потенциал» на проверяемом выходе ожидаемое прерывание из-за отсутствия перепада напряжения не наступит в течение заранее установленного времени 10 мс и это будет зафиксировано как неисправность. Если аналого-цифровой преобразователь успешно заканчивает измерение, то он формирует прерывание, при котором измеренный уровень напряжения проверяется на соответствие допускам для уровней логических сигналов относительно измеренного ранее напряжения источника питания. Измеренный уровень напряжения и результаты его допускового контроля заносятся в оперативную память ОЗУ для последующего анализа и формирования результата проверки после проверки всех контрольных выходов микропроцессора 3.

После завершения проверки сигналов на контрольных выходах микропроцессора 3 он становится из проверяемого проверяющим, и процесс повторяется аналогично.

После завершения каждого цикла проверки по таймеру оперативная память ОЗУ микропроцессоров 3, 4 освобождается от устаревших данных, а счетчики числа проверок сбрасываются.

Между циклами проверки каналов 1 и 2 и микропроцессоров 3 и 4 может быть организована мягкая синхронизация, поскольку логическое соответствие сигналов на соответствующих выходах микропроцессоров 3 и 4 синхронно бит за битом проверяет блок 6 аппаратного контроля безопасности функционирования, измерение уровней напряжения логических сигналов и уровня напряжений питания, которое предназначено для защиты от накопления неисправностей, не требует жесткой синхронизации и немедленной реакции при обнаружении ошибок. Если для блока 6 аппаратного контроля безопасности разрешен цикл проверки 0.5 сек., исходя из требований по допустимой задержке времени начала защитного отключения или экстренного торможения, то для защиты от накопления неисправностей допустима большая задержка, так как опасный отказ еще не произошел. В предлагаемой системе выбрана задержка 0,2 мин.

Проверки отсутствия накопления неисправностей осуществляются без создания помех нормальной синхронной обработки информации в каналах 1, 2 управления.

Если микропроцессоры 3 и 4 питаются от отдельных источников питания, объединенных, например, отрицательным полюсом, то для взаимного контроля уровней напряжения питания предусмотрено еще по одному контрольному входу, каждый из которых соединен через развязывающий резистор с положительным полюсом источника питания другого микропроцессора. Если источник питания общий, то внутренние аналого-цифровые преобразователи микропроцессоров 3 и 4 измеряют напряжение питания непосредственно на выводе питания внутри корпуса своего микропроцессора.

Самоконтроль уровней питания, уровней логических сигналов, фиксация автогенерации и плавающих потенциалов постоянного напряжения обеспечивает надежный аппаратный контроль двухканальной системы регулирования движения поездов, одновременно упрощает требования к функциям блока 6 аппаратного контроля. Это дает возможность использования более простых и надежных технических решений, повышает надежность работы двухканальной системы для регулирования движения поездов без ухудшения уровня ее безопасности.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦЕНТРАЛИЗОВАННАЯ ДИСПЕТЧЕРСКАЯ СИСТЕМА С РАСПРЕДЕЛЕННЫМИ КОНТРОЛИРУЕМЫМИ ПУНКТАМИ | 2003 |

|

RU2240245C1 |

| Устройство контроля за управлением поезда и бдительностью машиниста | 2019 |

|

RU2718621C1 |

| СИСТЕМА ИНТЕРВАЛЬНОГО РЕГУЛИРОВАНИЯ ДВИЖЕНИЯ ПОЕЗДОВ НА ПЕРЕГОНЕ | 2014 |

|

RU2550795C1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| СИСТЕМА ПОЛУАВТОМАТИЧЕСКОЙ БЛОКИРОВКИ ДЛЯ ОГРАНИЧЕННЫХ ПО ДЛИНЕ МЕЖСТАНЦИОННЫХ ПЕРЕГОНОВ | 2015 |

|

RU2591554C1 |

| СПОСОБ СРАВНЕНИЯ КОНТРОЛЬНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2016 |

|

RU2642347C1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЦЕНТРАЛИЗАЦИИ СТРЕЛОК И СИГНАЛОВ | 2011 |

|

RU2495778C2 |

| Бортовое навигационное коммуникационное устройство | 2017 |

|

RU2657152C1 |

| Система управления движением поездов по перегону | 2022 |

|

RU2783558C1 |

| ДВУХКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГУЛИРОВАНИЯ ДВИЖЕНИЯ ЖЕЛЕЗНОДОРОЖНЫХ ТРАНСПОРТНЫХ СРЕДСТВ | 2004 |

|

RU2286279C2 |

Изобретение относится к области железнодорожной автоматики и телемеханики, а именно к системам для регулирования движения поездов. Двухканальная система для регулирования движения поездов содержит два канала управления, два микропроцессора, блок питания, блок встроенного аппаратного контроля, блок сопряжения и обмотки ЭПК. Контрольные выходы первого микропроцессора через первые развязывающие резисторы соединены с контрольными входами второго микропроцессора, а контрольные выходы второго микропроцессора через вторые развязывающие резисторы соединены с контрольными входами первого микропроцессора. Помимо этого каждый из микропроцессоров содержит, по меньшей мере, один встроенный таймер и один аналого-цифровой преобразователь с интерфейсом поочередного подключения его к источнику питания и контрольным выходам микропроцессора своего канала управления. Технический результат изобретения заключается в повышении надежности работы двухканальной системы для регулирования движения поездов без ухудшения уровня ее безопасности. 1 з.п. ф-лы, 2 ил.

1. Двухканальная система для регулирования движения поездов, содержащая в каждом канале управления первый и второй микропроцессоры, связанные системным CAN - интерфейсом, блок питания, блок встроенного аппаратного контроля, первые и вторые входы которого соединены с контрольными выходами соответственно первого и второго микропроцессоров, выход блока встроенного аппаратного контроля соединен через усилитель с выходом первого канала управления, выходы первого и второго каналов управления через блок сопряжения соединены с соответствующими обмотками электропневматических клапанов экстренного торможения поезда, отличающаяся тем, что контрольные выходы первого микропроцессора через первые развязывающие резисторы соединены с контрольными входами второго микропроцессора, а контрольные выходы второго микропроцессора через вторые развязывающие резисторы соединены с контрольными входами первого микропроцессора, каждый из микропроцессоров содержит, по меньшей мере, один встроенный таймер и один аналого-цифровой преобразователь с интерфейсом поочередного подключения его к источнику питания и контрольным выходам микропроцессора своего канала управления.

2. Двухканальная система регулирования движения поездов по п.1, отличающаяся тем, что блок питания включает в себя отдельные источники питания микропроцессоров, одни полюса этих источников объединены, а другой полюс источника питания одного микропроцессора через развязывающий резистор соединен с дополнительным входом другого микропроцессора.

| ДВУХКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГУЛИРОВАНИЯ ДВИЖЕНИЯ ЖЕЛЕЗНОДОРОЖНЫХ ТРАНСПОРТНЫХ СРЕДСТВ | 2004 |

|

RU2286279C2 |

| Способ контроля износа долота | 1956 |

|

SU107753A1 |

| Поливальщик шланговый навесной | 1961 |

|

SU148995A1 |

Авторы

Даты

2014-12-27—Публикация

2013-05-22—Подача