Область техники, к которой относится изобретение

Настоящее изобретение относится к интегрированным транзисторно/запоминающим структурам, содержащим один или более слоев полупроводникового материала, два или более электродных слоев, а также контактирующий с электродами, находящимися в указанных, по меньшей мере, двух электродных слоях, и запоминающий материал. При этом запоминающий материал представляет собой поляризуемый диэлектрический материал, способный проявлять гистерезисные свойства, преимущественно ферроэлектрический или электретный материал. Электроды в каждом из, по меньшей мере, двух электродных слоев выполнены в виде протяженных параллельных структур, не имеющих разрывов. По меньшей мере, один слой полупроводникового материала и, по меньшей мере, два электродных слоя формируют структуру полевого транзистора. При этом электроды первого электродного слоя образуют одну пару электродов истока и стока указанной структуры полевого транзистора, а электрод смежного второго электродного слоя формирует электрод затвора указанной структуры полевого транзистора, ориентированный, по существу, ортогонально электродам первого электродного слоя.

Изобретение относится также к массиву (набору) подобных транзисторно/запоминающих структур с матричной адресацией. Данный массив содержит один или более слоев полупроводникового материала, два или более электродных слоев, а также запоминающий материал, контактирующий с электродами, находящимися в указанных, по меньшей мере, двух электродных слоях. При этом запоминающий материал представляет собой поляризуемый диэлектрический материал, способный проявлять гистерезисные свойства, преимущественно ферроэлектрический или электретный материал. Электроды в каждом из, по меньшей мере, двух электродных слоев выполнены в виде протяженных параллельных структур, не имеющих разрывов. По меньшей мере, один слой полупроводникового материала и, по меньшей мере, два электродных слоя формируют структуры полевых транзисторов. При этом электроды первого электродного слоя образуют пары электродов истока и стока указанных структур полевых транзисторов, а электроды смежного второго электродного слоя формируют электроды затвора указанных структур полевых транзисторов. Данные электроды затвора ориентированы, по существу, ортогонально электродам первого электродного слоя.

Уровень техники

Серьезная проблема современной вычислительной техники заключается в наличии физического разрыва между устройствами хранения данных и процессорными блоками, в частности между центральными процессорами (ЦП) и системным программным обеспечением, программными средствами пользователя, а также данными пользователя. Недавние достижения, касающиеся реального быстродействия ЦП (начиная с процессоров Pentium II и далее), стали возможными благодаря интегрированию больших объемов памяти внутри ЦП за счет использования модулей SRAM/EEPROM (Static Random Access Memory/Electrically Erasable Programmable Read-Only Memory). Однако итоговая скорость по-прежнему сильно ограничивается тем фактом, что большинство программ и данных в качестве основной запоминающей среды все еще используют жесткий диск. Хотя скорость передачи применительно к жестким дискам, а также параметры магистральных шин в последние годы повысились, возможности достижения максимальной производительности все еще ограничиваются очень низкой скоростью доступа к жестким дискам, значения которой за последние 10-15 лет улучшились лишь в незначительной степени. При этом данная скорость не будет существенно повышена до тех пор, пока главным средством хранения данных остается механическое устройство.

Если основная часть данных, которая в настоящее время использует жесткий диск, могла бы использовать запоминающие средства, расположенные внутри самого ЦП, был бы достигнут огромный выигрыш по быстродействию. Еще более важным могла бы стать возможность разработки совершенно новых типов процессорных и вычислительных устройств. В частности, открылись бы новые подходы к программному обеспечению с параллельной обработкой данных, намного лучше адаптированному к решению различных сложных задач (например, таких как поиски без предварительного индексирования, непрерывное распознавание речи, искусственный интеллект).

Возрастающая несовместимость между устройствами хранения данных и процессорными блоками, обусловленная наличием физического разрыва между ними, не только приводит к серьезным проблемам, связанным с ограниченностью памяти, но и ведет к простоям и неэффективному использованию высокопроизводительных процессорных контуров.

Раскрытие изобретения

Таким образом, главная задача, на решение которой направлено настоящее изобретение, состоит в том, чтобы решить или ослабить названные проблемы путем создания новой архитектуры, позволяющей осуществить интеграцию энергонезависимой памяти и высокоскоростных транзисторных контуров. Новая архитектура должна быть совместима со схемами на основе как органических, так и неорганических материалов, а также с гибридными схемами, при этом она не должна ограничиваться только планарными устройствами, будучи в равной степени применимой и к трехмерным (объемным) устройствам.

Решение данной задачи, а также другие достоинства и свойства реализованы созданием интегрированных транзисторно/запоминающих структур. Интегрированные транзисторно/запоминающие структуры по изобретению характеризуются тем, что электроды истока и стока единичной транзисторно/запоминающей структуры разделены узкой вертикальной канавкой, расположенной между ними и доходящей по глубине до полупроводникового слоя. В полупроводниковом слое, под канавкой между электродами истока и стока, выполнен транзисторный канал, а под электродами истока и стока, по обе стороны от транзисторного канала, сформированы истоковая и стоковая области. Транзисторно/запоминающая структура дополнительно содержит запоминающий материал, заполняющий канавку между электродами истока и стока и покрывающий их верхнюю поверхность, а электрод затвора находится в контакте с запоминающим материалом. При этом транзисторный канал выполнен с шириной W, соответствующей ширине электрода затвора, и с длиной L, соответствующей ширине канавки и составляющей долю его ширины W. В результате в объеме запоминающего материала сформированы три ячейки памяти, расположенные соответственно между электродом истока и электродом затвора, между электродом стока и электродом затвора и в канавке между электродами истока и стока.

В предпочтительном варианте выполнения транзисторно/запоминающих структур согласно изобретению транзисторно/запоминающая структура содержит третий электродный слой из полупроводникового материала, противолежащий электродному слою, содержащему электроды истока и стока, и содержащий второй электрод затвора, ориентированный в том же направлении, что и первый электрод стока и согласованный с ним в вертикальном направлении. В этом варианте транзисторно/запоминающая структура представляет собой двухзатворный полевой транзистор.

В соответствии с изобретением первая ячейка памяти находится в контакте с электродами истока и затвора, вторая ячейка памяти - в контакте с электродами стока и затвора, а третья ячейка памяти - в контакте с электродами истока и стока. При этом желательно, чтобы запоминающий материал в третьей ячейке памяти имел толщину, отличную от его толщины в первой и во второй ячейках памяти. Желательно также, чтобы запоминающий материал являлся ферроэлектрическим или электретным органическим материалом, предпочтительно полимером или сополимером.

Согласно настоящему изобретению полупроводниковый материал предпочтительно является неорганическим материалом, желательно аморфным, поликристаллическим или микрокристаллическим кремнием. Альтернативно полупроводниковый материал является органическим материалом, предпочтительно полупроводниковым полимером или пентаценом.

В соответствии со вторым предпочтительным вариантом выполнения транзисторно/запоминающих структур по изобретению в дополнение к указанной, первой транзисторно/запоминающей структуре они содержат и вторую, дополнительную транзисторно/запоминающую структуру, расположенную со смещением в вертикальном положении относительно транзисторно/запоминающей структуры, с противоположной стороны электрода затвора первой транзисторно/запоминающей структуры, и имеющую обратный порядок слоев относительно первой транзисторно/запоминающей структуры. Дополнительная транзисторно/запоминающая структура имеет общий электрод затвора с первой транзисторно/запоминающей структурой. Сформированная в результате сдвоенная транзисторно/запоминающая структура имеет общий затвор и шесть ячеек памяти.

Такая сдвоенная транзисторно/запоминающая структура предпочтительно представляет собой комплементарный полевой транзистор, включенный по схеме с общим затвором. Согласно модификации данного варианта сдвоенная транзисторно/запоминающая структура снабжена, по меньшей мере, одним дополнительным электродом затвора, расположенным на одном из слоев полупроводникового материала и противолежащим электродному слою, содержащему электроды истока и стока.

Решение данной задачи, а также другие достоинства и свойства реализованы также созданием массива интегрированных транзисторно/запоминающих структур с матричной адресацией. Массив интегрированных транзисторно/запоминающих структур с матричной адресацией согласно изобретению характеризуется тем, что электроды истока и стока единичной транзисторно/запоминающей структуры разделены узкой вертикальной канавкой, расположенной между ними и доходящей по глубине до полупроводникового слоя. В полупроводниковом слое, под канавкой между электродами истока и стока, выполнен транзисторный канал, под электродами истока и стока, по обе стороны от транзисторного канала, сформированы истоковая и стоковая области. Транзисторно/запоминающая структура дополнительно содержит запоминающий материал, заполняющий канавку между электродами истока и стока и покрывающий их верхнюю поверхность, а электрод затвора находится в контакте с запоминающим материалом. При этом транзисторный канал выполнен с шириной W, соответствующей ширине электрода затвора, и с длиной L, соответствующей ширине канавки и составляющей долю его ширины W. В результате в объеме запоминающего материала сформированы три ячейки памяти, расположенные соответственно между электродом истока и электродом затвора, между электродом стока и электродом затвора и в канавке между электродами истока и стока.

Согласно предпочтительному варианту осуществления указанного массив с матричной адресацией по настоящему изобретению транзисторно/запоминающая структура содержит третий электродный слой из полупроводникового материала, противолежащий электродному слою, содержащему электроды истока и стока, и содержащий второй электрод затвора, ориентированный в том же направлении, что и первый электрод затвора и согласованный с ним в вертикальном направлении, причем транзисторно/запоминающая структура представляет собой двухзатворный полевой транзистор.

Согласно изобретению первая ячейка памяти предпочтительно находится в контакте с электродами истока и затвора, вторая ячейка памяти находится в контакте с электродами стока и затвора, а третья ячейка памяти находится в контакте с электродами истока и стока. В данном варианте запоминающий материал в третьей ячейке памяти имеет толщину, отличную от его толщины в первой и во второй ячейках памяти. При этом запоминающий материал является ферроэлектрическим или электретным органическим материалом, предпочтительно полимером или сополимером.

Далее, в массиве с матричной адресацией согласно изобретению полупроводниковый материал является неорганическим материалом, предпочтительно аморфным, поликристаллическим или микрокристаллическим кремнием. Альтернативно полупроводниковый материал является органическим материалом, предпочтительно полупроводниковым полимером или пентаценом.

В соответствии со вторым предпочтительным вариантом своего осуществления массив с матричной адресацией согласно изобретению, помимо указанной транзисторно/запоминающей структуры, содержит дополнительную транзисторно/запоминающую структуру, расположенную со смещением в вертикальном положении относительно указанной транзисторно/запоминающей структуры, с противоположной стороны электрода затвора указанной транзисторно/запоминающей структуры, и имеющую обратный порядок слоев относительно указанной транзисторно/запоминающей структуры, с которой дополнительная транзисторно/запоминающая структура имеет общий электрод затвора с образованием сдвоенной транзисторно/запоминающей структуры с общим затвором и с шестью ячейками памяти. При этом сдвоенная транзисторно/запоминающая структура предпочтительно представляет собой комплементарный полевой транзистор, включенный по схеме с общим затвором. В модификации данного варианта сдвоенная транзисторно/запоминающая структура снабжена, по меньшей мере, одним дополнительным электродом затвора, расположенным на одном из слоев полупроводникового материала и противолежащим электродному спою, содержащему электроды истока и стока.

В соответствии с третьим предпочтительным вариантом осуществления данного массива согласно изобретению он выполнен в виде трехмерного массива, сформированного путем сборки в пакет двух или более двумерных массивов транзисторно/запоминающих структур. При этом каждый двумерный массив изолирован от смежного двумерного массива разделительным слоем. В качестве разделительного слоя выбран слой изолирующего материала, слой электропроводящего или полупроводникового материала, снабженный покрытием, образующим изолирующий барьер, или слой электропроводящего или полупроводникового материала с поверхностью, оксидированной для образования изолирующего барьера.

Краткое описание чертежей

Настоящее изобретение далее будет описано более подробно со ссылками на необходимые технологические предпосылки, а также на предпочтительные варианты своего осуществления и на прилагаемые чертежи.

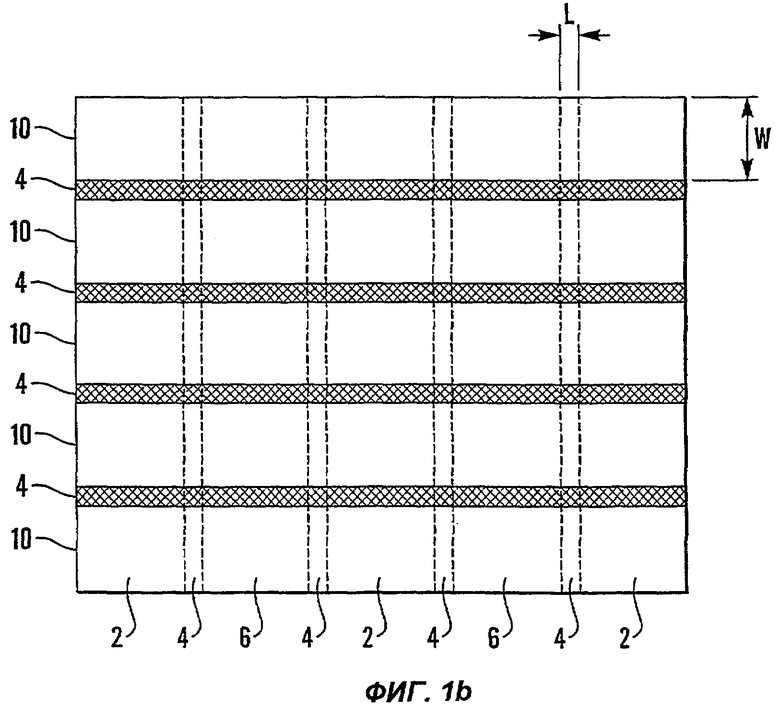

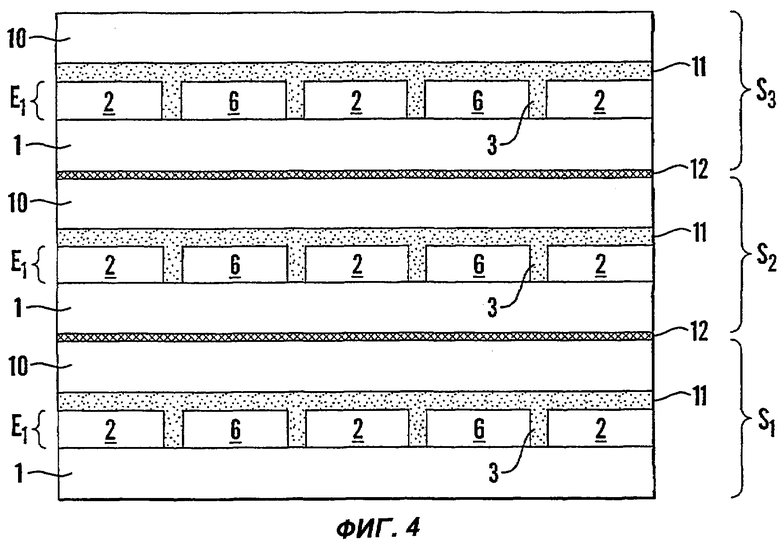

На фиг.1а представлен вид в сечении массива структур полевых транзисторов с плотным расположением электродов.

Фиг.1b соответствует виду сверху на массив по фиг.1а.

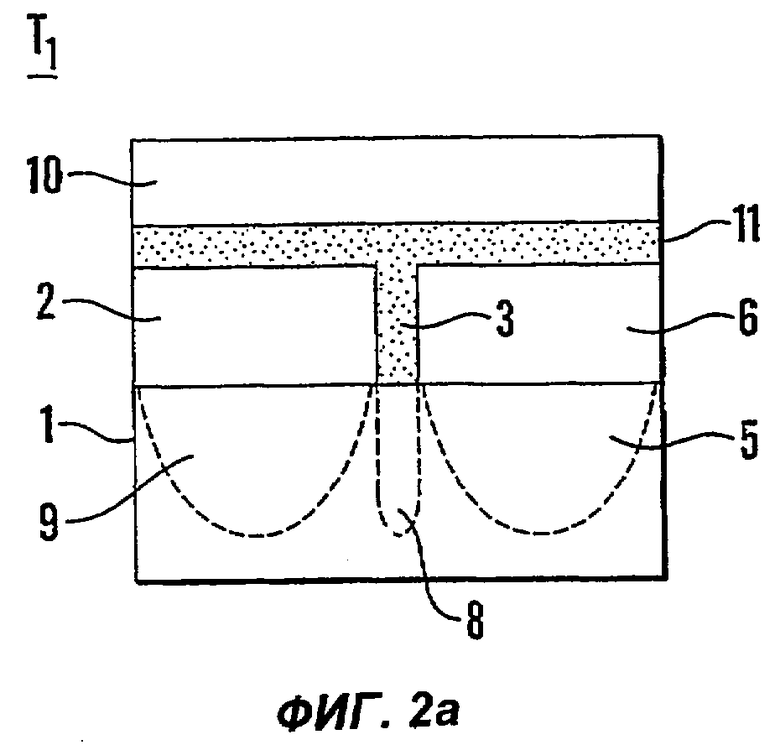

На фиг.2а представлен вид в сечении единичной интегрированной транзисторно/запоминающей структуры согласно изобретению.

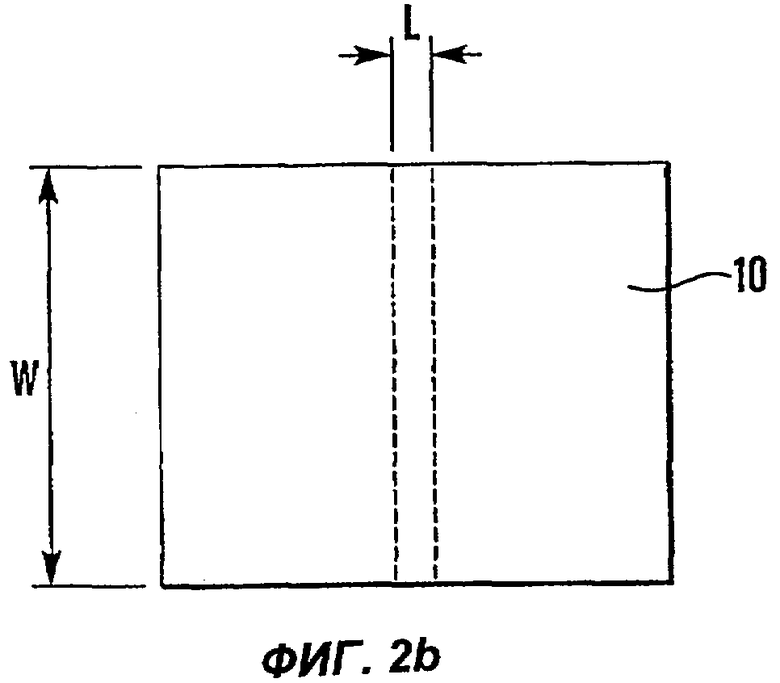

Фиг.2b соответствует виду сверху на транзисторно/запоминающую структуру по фиг.2а.

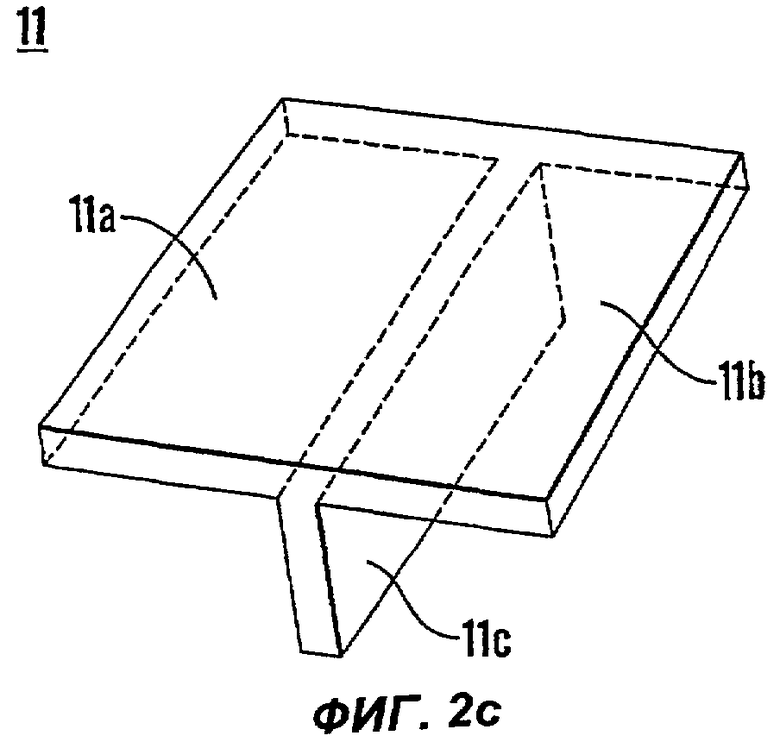

На фиг.2с в перспективном изображении показана геометрическая конфигурация, образованная запоминающим материалом в транзисторно/запоминающей структуре по фиг.2а.

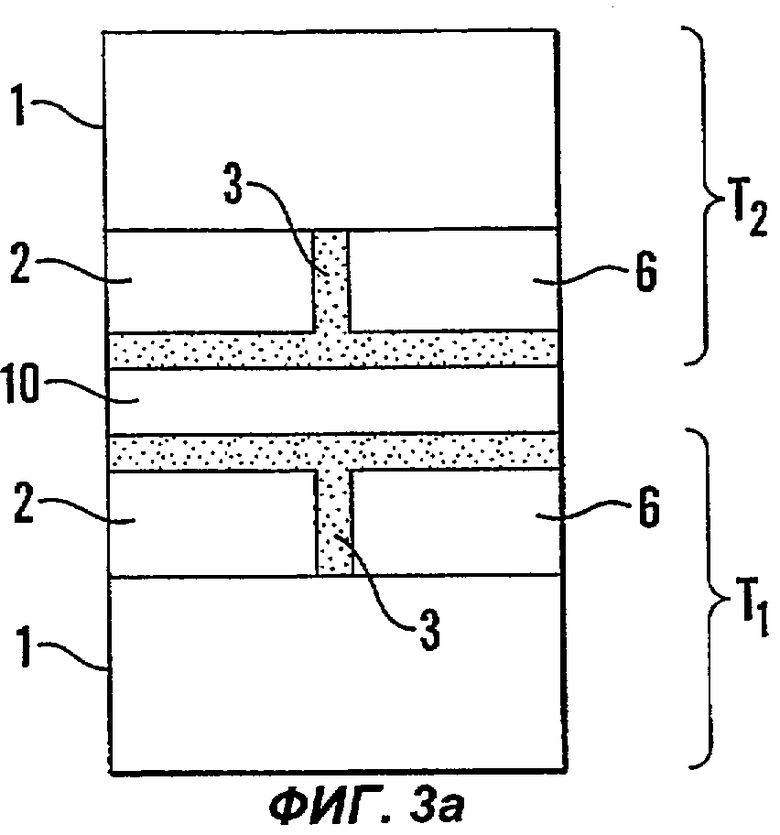

На фиг.3а показана сдвоенная транзисторно/запоминающая структура согласно первому варианту изобретения.

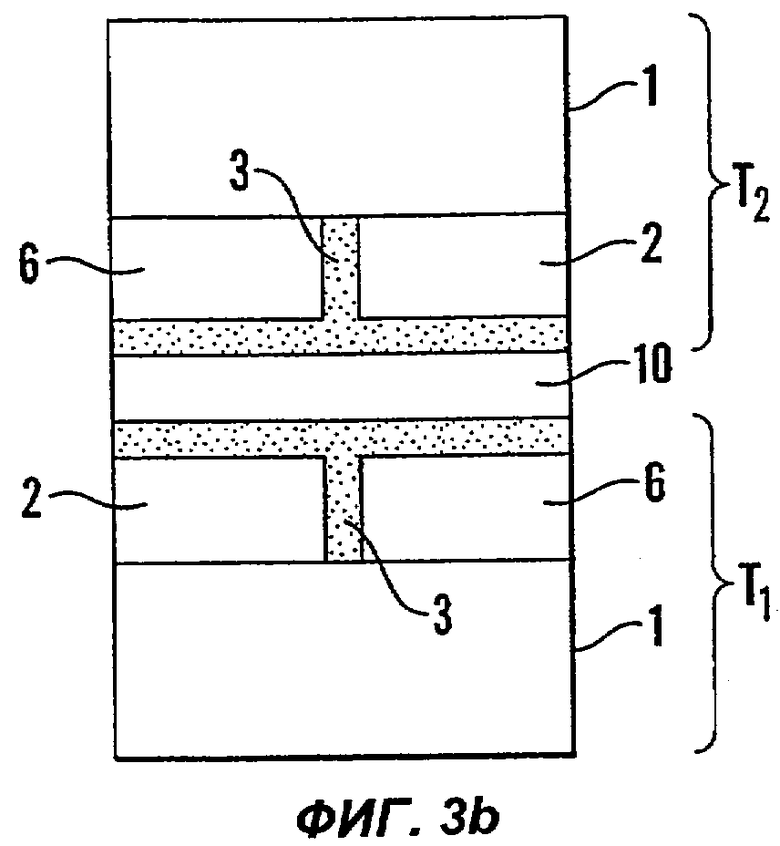

На фиг.3b изображен вариант структуры по фиг.3а.

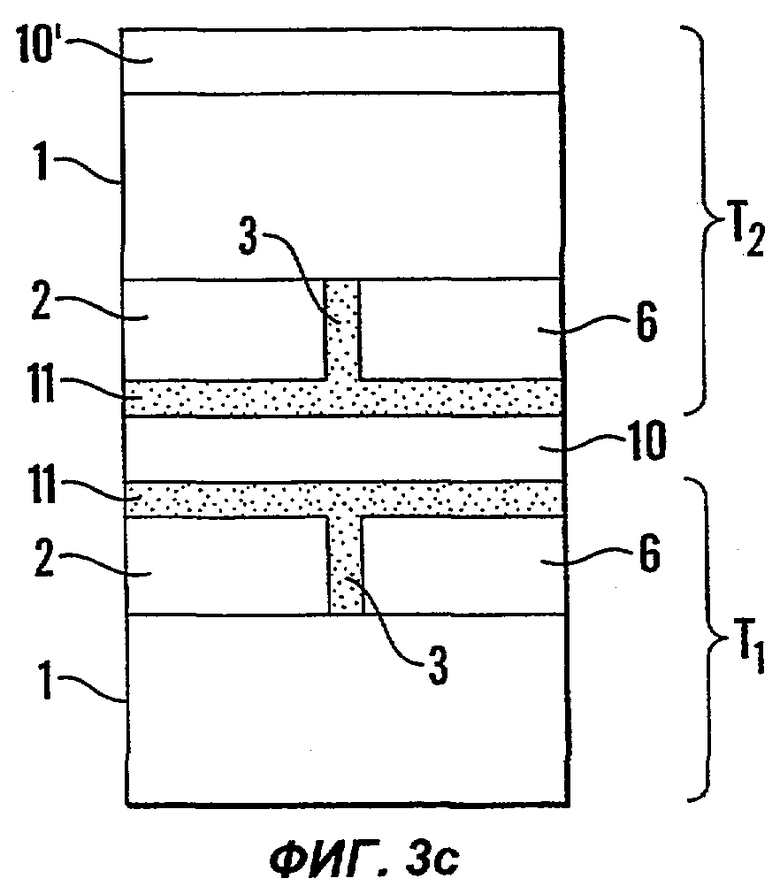

На фиг.3с представлен второй вариант сдвоенной транзисторно/ запоминающей структуры по изобретению.

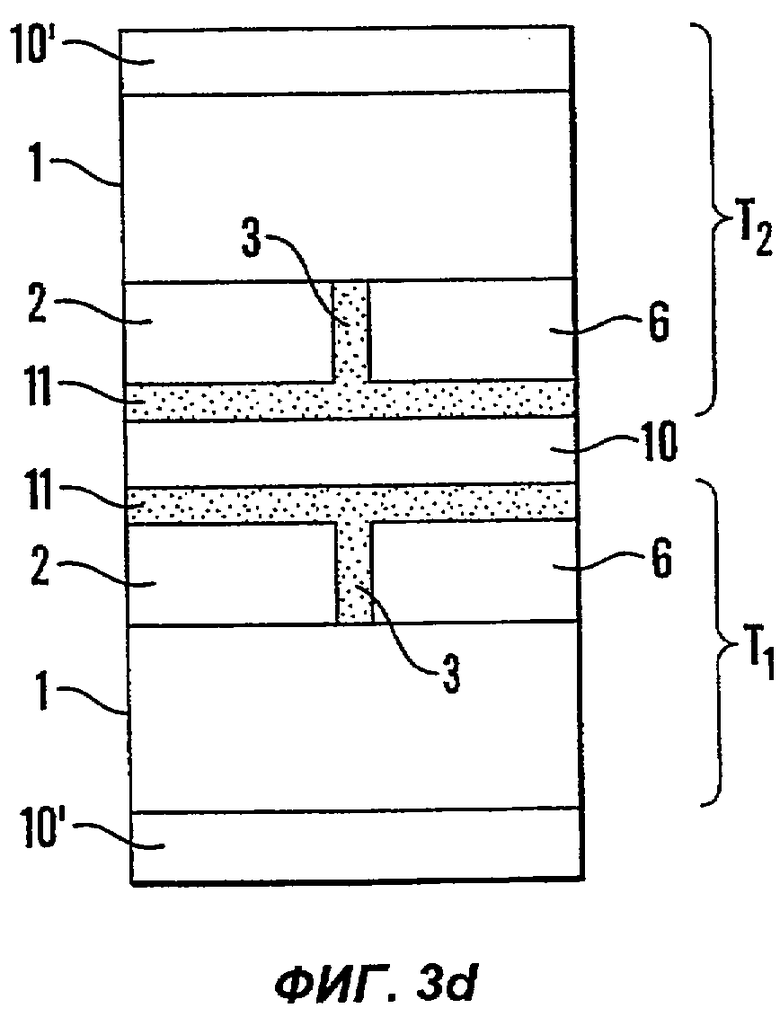

На фиг.3d представлен третий вариант сдвоенной транзисторно/запоминающей структуры по изобретению.

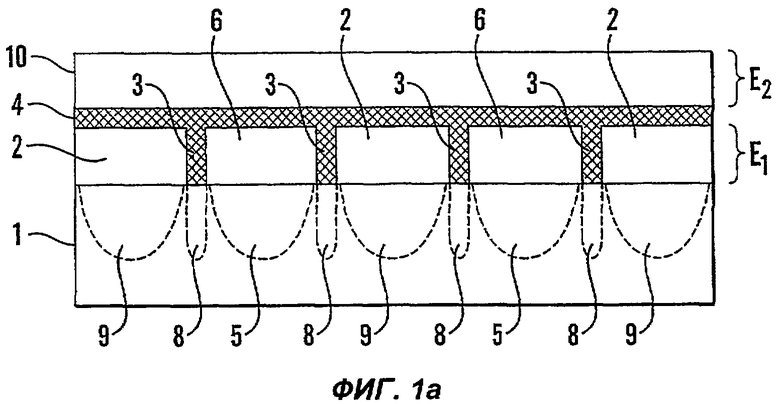

На фиг.4 представлен трехмерный массив с матричной адресацией по настоящему изобретению.

Осуществление изобретения

Далее будут кратко рассмотрены общие предпосылки создания настоящего изобретения. В его основе лежит концепция расположения электродов с высокой плотностью, которая описана в параллельной международной заявке PCT/NO02/00414 (WO 03/041084), принадлежащей заявителю настоящего изобретения. Описанная в указанной заявке плотная схема расположения электродов соответствует конфигурации, показанной в сечении на фиг.1а и на виде сверху на фиг.1b. Данная конфигурация соответствует расположению электродов в электродных слоях Е1 и Е2, как это показано на фиг 1а. Для того чтобы снять ограничения, накладываемые на шаг электродов правилами конструирования, соответствующими традиционной технологии профилирования, например, посредством микрофотолитографии, для формирования электродных слоев Е1; Е2 используются раздельные процессы профилирования и формования. В результате формируются полосковые электроды (в частности, электроды 2, 6 электродного слоя Е1, отстоящие друг от друга на произвольно малое расстояние и взаимно изолированные с помощью изолирующего материала 4, находящегося в канавках 3 между электродами). Аналогичным образом могут быть сформированы и электроды 10 электродного слоя Е2, которые скрещиваются под прямым углом с электродами 2, 6. Электроды 10 затвора взаимно изолированы соответствующим образом, с использованием изолирующего (барьерного) материала 4, как это хорошо видно на фиг.1b.

Расстояние L между электродами 2, 6 не задается какими-либо правилами конструирования и поэтому в принципе может быть равно толщине слоя материала 4, который наносится методами, позволяющими в принципе уменьшить значение L до толщины моноатомного слоя. Благодаря этому схема расположения электродов с высокой плотностью, описанная в указанной международной заявке, позволяет получить плотные матрицы ячеек функционального материала, находящегося, например, между электродными слоями Е1 и Е2 и адресуемого через эти слои.

Настоящее изобретение основано, кроме того, на техническом решении, раскрытом в параллельной международной заявке PCT/NO02/00397 (WO 03/046921), также принадлежащей заявителю настоящего изобретения. В указанной заявке описаны транзисторные матрицы, состоящие из структур полевых транзисторов со сверхкороткой длиной L канала и с произвольно большой шириной W канала. Данное решение открывает казавшиеся недостижимыми перспективы конструирования полевых транзисторов. Фиг.1а можно рассматривать как иллюстрацию поперечного сечения подобных транзисторных структур, организованных в матрицу, что особенно наглядно видно на виде сверху по фиг.1b. На фиг.1а показано, что электрод 2 истока, сформированный в электродном слое Е1, расположен параллельно электроду 6 стока, который имеет примерно такие же размеры.

Электроды 2, 6 истока и стока выполнены на полупроводниковой подложке 1, например, из кремния. С использованием метода, описанного в упомянутой международной заявке, подложка соответствующим образом легирована для образования в ней истоковых областей 9 и стоковых областей 5. Кроме того, подложка дополнительно легирована на участках, расположенных под канавками 3, сформированными между электродами 2, 6 истока и стока, для того, чтобы образовать транзисторные каналы 8 со сверхкороткой длиной L.

Электроды 2, 6 истока и стока взаимно изолированы с помощью изолирующего (барьерного) материала 4, заполняющего канавки 3 между ними и покрывающего их верхние поверхности, образуя тем самым изолирующий слой. Ортогонально ориентированные электроды 10 затвора структур полевых транзисторов расположены так, как это показано на фиг.1b. Длина L транзисторного канала 8 может быть сделана почти произвольно малой, т.е. соответствующей толщине слоя материала 4, причем, как это хорошо известно специалистам, данный материал может быть нанесен с толщиной, соответствующей почти моноатомным слоям. С другой стороны, ширина W канала может задаваться шириной электродов 10 затвора. Как следствие, отношение W/L может быть сделано очень большим. Благодаря этому, если требуется, может быть получен очень большой ток ID стока. Таким образом, современная технология, позволяющая производить профилирование с шагом, превосходящим 0,1 мкм, обеспечивает возможность получения матриц типа представленной на фиг.1b, а также транзисторных структур, имеющих соответственно малый масштаб.

Базовая технология, раскрытая в двух вышеупомянутых международных заявках, создает основу для осуществления транзисторно/запоминающих структур, а также массива транзисторно/запоминающих структур с матричной адресацией в соответствии с настоящим изобретением. Единичная транзисторно/запоминающая структура T1, выполненная согласно изобретению и изображенная на фиг.2а, представляется структурно схожей с соответствующими структурами на фиг.1а. Как и в предыдущем случае, электрод 2 истока и электрод 6 стока сформированы на подложке 1 в виде слоя полупроводникового материала, который легирован соответствующим образом для образования в полупроводниковой подложке истоковой области 9, транзисторного канала 8 сверхкороткой длины и стоковой области 5. Однако теперь барьерный слой изолирующего материала 4, показанный на фиг.1а, заменен запоминающим материалом в форме тонкого слоя 11 поляризуемого диэлектрического материала, способного проявлять гистерезисные свойства, преимущественно ферроэлектрического или электретного материала.

Как это известно специалистам в данной области, ферроэлектрический материал предпочтительно представляет собой ферроэлектрический полимер или сополимер. В последнем случае этим материалом может являться сополимер винилидендифторида и трифторэтилена - П(ВДФ-ТрФЭ), который может наноситься в виде предельно тонких слоев, вплоть до диапазона нанометров, и который, как известно, представляет собой ферроэлектрический материал, способный обеспечить требуемые изолирующие свойства. Запоминающий материал 11 наносится так, как это показано на фиг.2а, т.е. он заполняет канавки 3 между электродами 2, 6 истока и стока и покрывает их верхние поверхности. Тем самым обеспечивается изоляция или барьер относительно электрода 10 затвора. Таким образом, в транзисторно/запоминающей структуре T1 присутствует запоминающий материал 11, формирующий три отдельные запоминающие ячейки.

Эти ячейки более наглядно представлены на фиг.2с, на которой в перспективе показан только слой запоминающего материала, в отсутствие каких-либо других элементов. У запоминающего материала можно выделить три отдельные части, а именно первую часть 11а, образующую первую ячейку памяти, к которой можно адресоваться через электрод 10 затвора и электрод 2 истока; вторую часть 11b, образующую вторую ячейку памяти, к которой можно адресоваться через электрод 10 затвора и электрод 6 стока; и третью часть 11с, образующую третью ячейку памяти, которая расположена в канавке 3 между электродами 2, 6 истока и стока и к которой можно адресоваться через эти электроды. Адресация к этим трем ячейкам 11а, 11b и 11с памяти для записи и считывания может осуществляться независимо от функционирования самого полевого транзистора. В этой связи должно быть ясно, что три ячейки памяти могут хранить одно трехразрядное двоичное слово, например, любое из следующих двоичных слов: 000, 001, 010, 011, 100, 101 и 111. Как это хорошо известно специалистам в данной области, запись и считывание подобных трехразрядных двоичных слов будет производиться в соответствии с надлежащим протоколом и в дальнейшем обсуждении этих процессов нет необходимости. Подробное описание работы структуры по изобретению будет приведено далее.

Изображенный на фиг.2а, 2с запоминающий материал 11, образующий три ячейки 11а, 11b и 11с памяти, позволяет, как это будет описано далее, производить переключения в различных направлениях. Первая ячейка 11а памяти соответствует той части запоминающего материала 11, которая расположена между электродом 2 истока и электродом 10 затвора; она будет переключаться в направлении, ортогональном поверхностям этих электродов и собственным поверхностям, при подаче напряжения на электрод 2 стока и электрод 10 затвора, т.е. при наличии электрического потенциала между ними, соответствующего электрическому полю, приложенному к ячейке 11а памяти. Поскольку в ячейке используется ферроэлектрический материал, она способна поляризоваться в прямом или обратном вертикальном направлении, что позволяет хранить в ней одну двоичную цифру. Те же самые соображения применимы и к ячейке 11b памяти, соответствующей той части запоминающего материала 11, которая расположена между электродом 6 стока и электродом 10 затвора.

Третья ячейка 11с памяти формируется в запоминающем материале в той его части, которая находится в канавке 3 между электродом 2 истока и электродом 6 стока. Эта ячейка будет переключаться аналогичным образом, т.е. за счет подачи напряжения на эти электроды и, соответственно, приложения электрического поля к ячейке 11с памяти, расположенной между ними. В случае использования предпочтительного ферроэлектрического материала, такого как поли(винилидендифторид-трифторэтилен) (П(ВДФ-ТрФЭ)), для того, чтобы поляризовать материал и обеспечить переключение между двумя состояниями поляризации (соответствующими двоичному нулю и двоичной единице), необходимо приложить к нему поле, имеющее достаточную напряженность. Требуемая напряженность поля связана с толщиной тонкопленочного запоминающего материала 11. При этом толщина запоминающего материала в ячейках 11а и 11b памяти может отличаться от толщины того же материала в ячейке 11с памяти.

Для удобства описания ячейка 11а памяти далее будет именоваться ячейкой памяти исток/затвор (ячейкой памяти И/З), аналогичная ячейка 11b памяти - ячейкой памяти сток/затвор (ячейкой памяти С/З), а ячейка 11с памяти - ячейкой памяти исток/сток (ячейкой памяти И/С). Поскольку толщина материала 11 в ячейках памяти И/З и С/З одинакова, эти ячейки будут переключаться при приложении поля одинаковой напряженности, тогда как в ячейке памяти И/С материал может иметь большую или меньшую толщину по сравнению с его толщиной в двух других ячейках памяти. Как следствие, в данном случае переключение возможно при другой напряженности электрического поля, отличной от напряженности поля между электродами 2, 6 истока и стока. При этом транзисторная структура, образованная электродами 2, 6 истока и стока, легированными областями 5, 8, 9 и электродом 10 затвора, может обеспечить переключения транзистора независимо от переключения ячеек памяти. Это подразумевает, что транзистор должен переключаться при приложении меньших напряжений истока и стока, чем те, которые требуются для переключения ячейки памяти И/С.Соответственно, напряжение затвора должно быть ниже, чем напряжение, необходимое для переключения ячейки памяти И/З или С/З. Реально переключение двух последних ячеек памяти будет полностью независимым от переключения транзистора.

Далее будут описаны предпочтительные варианты осуществления транзисторно/запоминающих структур согласно настоящему изобретению.

На фиг.3а представлен первый предпочтительный вариант, в котором над первой транзисторно/запоминающей структурой T1 имеется вторая аналогичная структура Т2. Две транзисторно/запоминающие структуры T1, T2 используют один общий электрод 10 затвора, тогда как электродные слои этих структур, содержащие электроды 2, 6 истока и стока, расположены с противоположных сторон общего электрода 10 затвора. Легированные области транзисторов, как и в предыдущем варианте, находятся в полупроводниковых подложках 1, расположенных на противолежащих сторонах транзисторно/запоминающих структур T1, Т2, как это показано на фиг.3а. Комбинированные структуры такого типа фактически представляют транзисторную структуру с общим электродом затвора при обратном порядке слоев. При соответствующем подключении они образуют контур комплементарного полевого транзистора, включенного по схеме с общим затвором. В подобном контуре структура T1 образует первый транзистор, а структура Т2 - второй транзистор. Разумеется, в этом случае подложки 1 должны быть легированы таким образом, чтобы сформировать каналы с проводимостью n-р-n и р-n-р-типа.

Аналогичная сдвоенная транзисторная структура представлена также на фиг.3b, однако в ней положение электродов 2, 6 истока и стока в структуре T2 является обратным по отношению к их положению в структуре T1. Как можно видеть из фиг.3а, 3b, изображенные на них транзисторно/запоминающие структуры содержат по шесть индивидуально адресуемых ячеек памяти. Следовательно, обеспечивается возможность использовать в каждой из этих структур шесть переключаемых ячеек, т.е. обеспечить хранение шестиразрядного двоичного слова при записи и считывании этого слова с использованием любого приемлемого протокола, как это должно быть понятно специалистам в данной области.

Второй вариант построения сдвоенной транзисторно/запоминающей структуры показан на фиг.3с. В этом варианте вторая транзисторно/запоминающая структура Т2 снабжена вторым электродом 10' затвора. В результате эта структура Т2 представляет собой транзисторно/запоминающую структуру с двухзатворным полевым транзистором.

Третий вариант выполнения сдвоенной транзисторно/запоминающей структуры показан на фиг.3d. Этот вариант похож на вариант по фиг.3с, но в нем вторым электродом 10' затвора снабжена также первая транзисторно/запоминающая структура T1. В результате обе структуры T1, T2 представляют собой транзисторно/запоминающие структуры с двухзатворным полевым транзистором, т.е. с двумя электродами 10, 10' затвора.

Подложка 1, т.е. слой полупроводникового материала, предпочтительно выполняется из кремния, который может быть в аморфном, поликристаллическом или микрокристаллическом состоянии. Одним из достоинств использования неорганического материала, такого как кремний, является возможность формирования на нем барьерного слоя путем оксидирования (окисления) его поверхности. Однако, как это хорошо известно специалистам в данной области, ничто не препятствует и тому, чтобы данный слой полупроводникового материала был выполнен из органического полупроводника, например из полупроводникового полимера или из циклического соединения, такого как пентацен. Однако при формировании электродов в электродном слое Е1, лежащем на органическом полупроводниковом материале, необходимо проявлять осторожность в отношении совместимости между материалами электродов и любым органическим полупроводниковым материалом в части температурного режима и других технологических факторов.

Запоминающий материал 11 должен представлять собой диэлектрический и поляризуемый материал, обладающий ферроэлектрическими или электретными свойствами и способный проявлять гистерезисные свойства при приложении к нему электрического поля. Как уже упоминалось, наиболее предпочтительными в данном случае будут органические материалы, такие как полимеры или сополимеры. Наиболее предпочтительным запоминающим материалом является П(ВДФ-ТрФЭ).

Одним из преимуществ подобных материалов является то, что их диэлектрические свойства позволяют использовать их также в качестве электрически изолирующих (барьерных) материалов. Еще одно преимущество заключается в возможности наносить их в виде цельных слоев крайне малой толщины, вплоть до нескольких нанометров. Кроме того, они могут наноситься, с образованием ячеек памяти, на поверхности, имеющие сложную геометрию. В частности, они способны полностью заполнять канавки 3, которые формируются между электродами 2, 6 истока и стока.

Интегрированные транзисторно/запоминающие структуры согласно изобретению могут быть легко реализованы в виде массивов с матричной адресацией, в частности, в виде двумерного массива известного из уровня техники типа. Подобный массив представлен на фиг.1а и 1b. Однако возможно также собрать подобные двумерные массивы в пакет (стопу) с формированием трехмерных массивов, как это показано на фиг.4. Изображенный на фиг.4 трехмерный массив с матричной адресацией по изобретению образован тремя двумерными массивами S1, S2 и S3, собранными в пакет. Базовым элементом такого трехмерного массива является, очевидно, единичная транзисторно/запоминающая структура, изображенная в сечении на фиг.2а и на виде сверху на фиг.2b. Однако трехмерные массивы подобных транзисторно/запоминающих структур не должны ограничиваться только этим вариантом: они могут строиться также на базе сдвоенных структур, например, подобных приведенным на фиг.3a-3d. Возможны также и другие комбинации электродных слоев и слоев полупроводникового материала. При этом единственное ограничение состоит в том, что должна обеспечиваться возможность раздельного переключения собственно транзисторной структуры и ячеек памяти.

Как можно видеть, в представленном на фиг.4 трехмерном массиве с матричной адресацией, включающем три собранных в пакет двумерных массива S, каждый двумерный массив содержит единственный слой 1 полупроводникового материала и первый электродный слой Е1, содержащий электроды 2, 6 истока и стока, разделенные канавками 3. Канавки 3 заполнены, как и в предыдущих вариантах, запоминающим материалом 11, который покрывает также верхние поверхности электродов 2, 6 истока и стока. Над запоминающим материалом расположен электрод 10 затвора, который может быть отделен от следующего смежного массива разделительным слоем 12. Этот разделительный слой может быть выполнен из соответствующего материала, например из диэлектрического запоминающего материала 11; однако он может представлять собой и барьерное покрытие, обладающее изолирующими свойствами, которое нанесено на электроды 10 затвора. Поскольку за электродами 10 затвора в собранных в пакет двумерных массивах S следует слой полупроводникового материала 1, принадлежащий смежному двумерному массиву с матричной адресацией, данный слой полупроводникового материала может быть обработан таким образом, чтобы сформировать барьерный слой на его поверхности, примыкающей к электроду затвора. В частности, поверхность неорганического полупроводникового материала, используемого в качестве слоя 1, может быть подвергнута оксидированию перед тем, как этот материал будет установлен на нижележащий двумерный массив. Естественно, подобная операция может быть легко осуществлена путем выполнения поверхностного оксидирования, когда неорганический полупроводниковый материал представляет собой кремний.

В принципе, количество двумерных массивов S, собираемых в пакет для формирования трехмерного массива с матричной адресацией, не ограничено. Вместе с тем, на практике оно будет ограничиваться, например, механическими или температурными факторами, а также необходимостью избежать возрастающей неровности поверхности в собранном пакете двумерных структур с возрастанием их количества. Однако эти технические проблемы вполне понятны и могут быть, хотя бы частично, преодолены с помощью технических мер, хорошо известных специалистам в данной области.

Итак, было показано, что настоящее изобретение обеспечивает создание массива с матричной адресацией, образованного интегрированными транзисторно/запоминающими структурами, расположенными в двух или в трех измерениях и интегрирующими в себе ячейки памяти и транзисторные ключи. При этом каждая из названных групп составных элементов может переключаться в индивидуальном режиме подачи напряжения, так что переключение, например, ячейки памяти не оказывает влияния на интегрированный с ней транзистор. Информация, подлежащая обработке или необходимая для функционирования устройства, может храниться в ячейках памяти, интегрированных в транзисторные контура. Как следствие, устраняется потребность во внешнем доступе и в периферийных устройствах хранения данных.

Должно быть также понятно, что в любом двумерном массиве можно сформировать отдельные группы транзисторно/запоминающих структур и построить на их основе соответствующие схемы. В частности, можно удалить подобные транзисторно/запоминающие структуры из некоторых частей двумерного массива, а затем создать соответствующие соединительные дорожки и межсоединения с наличием, в случае необходимости, изолирующих и барьерных слоев. Таким образом можно сформировать, например, логические ячейки и арифметические регистры с интегрированной памятью, образующие комбинированный процессорный/запоминающий контур. Более того, подобный контур может быть реализован в трехмерной конфигурации, что позволит обеспечить более высокую плотность соединений. Такое решение открывает совершенно новые перспективы для создания интегрированных процессорных/запоминающих структур высокой сложности при высокой плотности расположения элементов. Это позволит достичь высокого быстродействия и предельно быстрого доступа к памяти, поскольку необходимые регистры будут находиться внутри контура. При этом будут сняты обычные топологические ограничения, присущие значительной части современных интегральных схем, основанных, в частности, на кремниевых технологиях.

Изобретение относится к интегрированным транзисторно/запоминающим структурам. Сущность изобретения: интегрированные транзисторно/запоминающие структуры содержат один или более слоев полупроводникового материала, два или более электродных слоев, а также запоминающий материал, контактирующий с электродами, находящимися в указанных электродных слоях. По меньшей мере, один слой полупроводникового материала и, по меньшей мере, два электродных слоя формируют транзисторные структуры. При этом электроды первого электродного слоя образуют пары электродов истока и стока, а электроды смежного второго электродного слоя формируют электроды затвора указанных структур. Электроды истока и стока единичной транзисторной/запоминающей структуры разделены узкой канавкой, доходящей по глубине до полупроводникового слоя. При этом в полупроводниковом слое, под канавкой, выполнен транзисторный канал со сверхкороткой длиной L, а под электродами истока и стока, по обе стороны от транзисторного канала, сформированы истоковая и стоковая области. Запоминающий материал заполняет канавку и находится в контакте с электродами транзистора. Длина L транзисторного канала в данной схеме соответствует ширине канавки, а его ширина W - ширине электрода затвора, причем L составляет долю от W. В объеме запоминающего материала сформированы три ячейки памяти, расположенные соответственно между электродом истока и электродом затвора, между электродом стока и электродом затвора и в канавке между электродами истока и стока. Представлен также массив интегрированных транзисторно/запоминающих структур. Техническим результатом заявленного изобретения является создание структур, в которых осуществлена интеграция энергонезависимой памяти и высокоскоростных транзисторных контуров. 2 н. и 23 з.п. ф-лы, 4 ил.

характеризующийся тем, что электроды (2, 6) истока и стока транзисторно-запоминающей структуры разделены узкой вертикальной канавкой (3), расположенной между ними и доходящей по глубине до полупроводникового слоя (1), причем в полупроводниковом слое (1) под канавкой (3) между электродами (2, 6) истока и стока выполнен транзисторный канал (8), под электродами (2, 6) истока и стока по обе стороны от транзисторного канала (8) сформированы истоковая и стоковая области (9, 5), транзисторно-запоминающая структура дополнительно содержит запоминающий материал (11), заполняющий канавку (3) между электродами (2, 6) истока и стока и покрывающий их верхнюю поверхность, а электрод (10) затвора находится в контакте с запоминающим материалом (11), тогда как транзисторный канал (8) выполнен шириной W, соответствующей ширине электрода (10) затвора, и длиной L, соответствующей ширине канавки (3) и составляющей долю его ширины W, при этом в объеме запоминающего материала (11) сформированы три ячейки (11а, 11b, 11с) памяти, расположенные соответственно между электродом (2) истока и электродом (10) затвора, между электродом (6) стока и электродом (10) затвора и в канавке (3) между электродами (2, 6) истока и стока.

| ЕР 902465 А1, 17.03.1999 | |||

| US 6072716 А, 06.06.2000 | |||

| US 4952031 А, 28.08.1990 | |||

| УСТРОЙСТВО СЧИТЫВАНИЯ НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ ДЛЯ ДВУМЕРНЫХ ПРИЕМНИКОВ ИЗОБРАЖЕНИЯ | 1993 |

|

RU2054753C1 |

Авторы

Даты

2006-11-10—Публикация

2002-11-18—Подача