Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству объемного хранения данных, содержащему множество запоминающих устройств с матричной адресацией, собранных в пакет. Каждое запоминающее устройство содержит первую и вторую электродные решетки в виде слоев параллельных электродов, образующих соответственно управляющие шины (линии) и шины (линии) данных запоминающего устройства. Управляющие шины ориентированы ортогонально шинам данных для осуществления матричной адресации к запоминающему устройству. При этом каждое запоминающее устройство содержит слой запоминающего материала, расположенный между первой и второй электродными решетками и находящийся в прямом или непрямом контакте с ними. Вторая электродная решетка одновременно является первой электродной решеткой следующего запоминающего устройства, входящего в пакет. Как следствие, количество электродных решеток на единицу превышает количество запоминающих устройств в составе пакета. Запоминающий материал представляет собой поляризуемый диэлектрический материал, способный проявлять гистерезисные свойства. Предпочтительно он является ферроэлектрическим или электретным материалом, тогда как ячейки памяти заданы в этом запоминающем материале запоминающего устройства в зонах скрещивания управляющих шин и шин данных этого устройства.

Уровень техники

С точки зрения архитектуры электронных схем, использование пассивной матричной адресации в запоминающих устройствах на основе ферроэлектрического запоминающего материала представляется более привлекательным, чем схема 1Т-1С, соответствующая уровню техники применительно к архитектуре запоминающих устройств на базе кремния. Частично это связано с тем, что пассивная матричная адресация обеспечивает более высокую плотность записи данных, соответствующую 4f2 (где f - размер минимального технологически реализуемого элемента) по сравнению с 6f2 и более. Не менее важным достоинством использования пассивной адресации является возможность формирования пакета (стопы) последовательно наложенных друг на друга слоев, управление которыми может осуществляться, например, от контуров, размещенных на общей подложке. Тем не менее, нужно признать, что даже при плотности записи 4f2 коэффициент заполнения поверхности запоминающего материала составляет только 25%. При достижении коэффициента заполнения поверхности от 50% до почти 100% количество запоминающих слоев в объемном (трехмерном) пакете запоминающих устройств может быть сокращено с соответственным снижением сложности и стоимости изготовления при одновременном повышении выхода годных изделий. Кроме того, использование только одного или двух запоминающих слоев привело бы к соответствующему снижению влияния эффектов последующей обработки полимерного материала и, следовательно, предотвратило бы негативные последствия подобной обработки.

Традиционный подход к увеличению плотности расположения ячеек заключается в уменьшении площади каждой ячейки. Однако, чем меньше площадь ячейки, тем меньше сигнал (и меньше отношение сигнал/шум) и тем более чувствительной и, следовательно, сложной должна быть схема считывания (в основном, состоящая из усилителей считывания), которая потребует для себя большей полезной площади кристалла. На деле считается крайне трудной задачей построить коммутационную матрицу с шагом линий меньше чем 0,30-0,40 мкм (размер ячейки 0,09-0,16 мкм2).

Трудность, связанная с формированием многоуровневой структуры, состоит в обеспечении ее плоскостности. При наложении последующих слоев на предыдущие слои постепенно формируется неровная ("волнистая" или "бугристая") топография, которая создает значительные трудности в отношении управления фотолитографическим процессом, а следовательно, и в отношении возможности адресации и считывания содержимого ячеек (например, усилители считывания рассчитываются под ожидаемую площадь ячеек и, если эта площадь варьирует в некоторых пределах из-за неоднородности фотолитографии, становится невозможным осуществлять надежное считывание сигнала, т.е. становится труднее отличать единицы от нулей).

Выбранная архитектура также определяет, какое требуется минимальное число стадий маскирования, причем, чем их меньше, тем дешевле производство. Снижение числа стадий маскирования, приходящихся на бит информации, представляется очень важным. При изготовлении типичного прибора с 8 запоминающими слоями прибор на основе полимерных матриц потребует на 19 стадий маскирования больше, чем конкурирующий с ним прибор на основе флэш-памяти. Это означает почти двойное удорожание процесса обработки пластины с полимерными матрицами по сравнению с отработанными КМОП-процессами, например, для производства устройств флэш-памяти.

В памяти с матричной адресацией на базе ферроэлектрического полимера, использующей предложенное заявителем настоящего изобретения вертикальное коммутирующее (переключающее) поле, именно структура (морфология) полимерных пленок, нанесенных на полупроводниковую пластину методом центрифугирования, в значительной степени определяет пригодность приборов для тех или иных задач. Особенно сложно поддерживать оптимальную структуру в отношении ферроэлектрических свойств, когда толщина пленки становится меньше 100 нм. При таких значениях толщины пленки гораздо более чувствительны к типу используемых растворителей, к условиям центрифугирования и задубливания, к типу и влиянию граничных/барьерных слоев и т.п. С другой стороны, желательно иметь как можно более тонкие пленки, чтобы уменьшить напряжение переключения. Например, чтобы получить напряжения переключения между электродами ниже 5 В, пленки должны быть тоньше 30 нм. Более низкие уровни напряжения требуются, чтобы пользоваться фотолитографическими процессами все более высокой плотности и поддерживать совместимость с соответствующими правилами конструирования, что также позволяет получать пониженное энергопотребление. В приборах памяти на полимерных пленках использование низких напряжений тем более привлекательно, что позволяет большую часть схемы, а, в конечном счете, и всю схему построить под пассивной запоминающей матрицей, что опять-таки приводит к уменьшению эффективной площади ячейки за счет площади вспомогательных элементов, по возможности, до нуля, облегчая проектирование и осуществление межслойных соединений и т.п.

Однако получение таких тонких пленок с приемлемой однородностью/структурой без дефектов на больших площадях (подобных полупроводниковой пластине) представляет собой очень большую трудность также из-за того, что важные ферроэлектрические свойства, такие как кристаллическая упорядоченность, с уменьшением толщины пленки имеют тенденцию к ухудшению. Одновременно обостряются проблемы, связанные с токами утечки и паразитными токами. Это серьезно влияет на свойства памяти, например на уровень поляризации переключения и остаточной поляризации (это важно для различения нулей и единиц), ресурс переключения и скорость переключения. В особенности сильное снижение характеристик происходит при высоких температурах (например, выше 60°С).

Но даже при использовании более толстых запоминающих пленок возникает ряд проблем, подобных тем, с которыми сталкиваются при работе с тонкими пленками, хотя эти проблемы и не столь выражены. Предпочтительным и признанным способом нанесения пленок является центрифугирование с применением соответствующего растворителя. Выбор растворителя, условия центрифугирования, возможные осадки из растворителя, условия задубливания, связанные с выбором растворителя, и другие факторы составляют очень трудную задачу в отношении получения правильного сочетания параметров. Сложность данной задачи сильно возрастает, когда речь идет о тонких пленках. Тем не менее, растворители необходимо использовать, чтобы получать тонкие однородные пленки на полупроводниковых подложках.

Ввиду того, что напряжение переключения зависит от толщины пленки (см. ниже), с ухудшением однородности пленки соответственно будет варьировать и коэрцитивное поле, что будет создавать проблемы во время работы, если эти вариации превосходят расчетный размах напряжения. С другой стороны, чем больше расчетный размах, тем более сложной должна быть схема, чтобы управлять этим размахом. При этом растут затраты, которые связаны с эффективностью использования полезной площади пластины, сложностью изготовления и стоимостью устройства.

Вероятно, еще более серьезные опасения относительно структуры связаны с тем, что в многослойных структурах памяти полимер подвергается существенной последующей обработке, например осаждению верхних электродов, нанесению граничных слоев, выполнению межслойных соединений и т.п. Все это потенциально оказывает на полимер сильное отрицательное влияние, что представляет большую трудность для надлежащего контроля, особенно в условиях промышленного производственного процесса.

Использование полимера и особенно тот факт, что электроды наносятся непосредственно на полимерный материал, который имеет температуру плавления около 150°С, приводят к проблемам, когда дело касается установки приборов в корпуса. При типичном процессе пайки температура (в ограниченные периоды времени) может достигать 210°С, что создает трудности в отношении архитектуры, так как электроды на полимере начинают плавиться и плыть, в результате чего граница электрод/полимерная пленка может быть серьезно нарушена.

Раскрытие изобретения

Устройство хранения данных согласно настоящему изобретению выполняется в форме пакета (стопы) запоминающих устройств, в котором электродные решетки альтернативно действуют как управляющие шины (линии) и шины (линии) данных для смежных устройств. В результате количество отдельных электродных решеток в устройстве хранения данных по изобретению только на единицу превышает количество запоминающих устройств в составе пакета. Такое выполнение, естественно, подразумевает, что протокол адресации должен обеспечить возможность адресации в каждый момент времени только к одному запоминающему устройству в составе пакета. В крайнем случае, возможна одновременная адресация к каждому второму устройству в составе пакета. Электродные решетки, альтернативно функционирующие в качестве управляющих шин и шин данных, уже были предложены ранее применительно к решениям, известным из уровня техники и предусматривающим сборку в пакет запоминающих устройств с пассивной адресацией. Однако такие известные устройства были основаны на традиционных схемах взаимного расположения электродов и ячеек памяти, хотя в них и применялись электродные решетки в виде тонких пленок. Несмотря на то что такие решения обеспечивали упрощение структуры устройства, они были неспособны обеспечить существенное повышение плотности хранения данных.

Соответственно, задачей, решаемой настоящим изобретением, является ослабление вышеупомянутых недостатков и трудностей, возникающих в известных запоминающих устройствах с матричной адресацией, использующих поляризуемые запоминающие материалы, способные к проявлению гистерезисных свойств, такие как ферроэлектрики или электреты, и создание устройства объемного (трехмерного) хранения данных, содержащего собранные в пакет запоминающие устройства с матричной адресацией при предельно высокой плотности хранения данных.

Конкретная задача, решаемая настоящим изобретением, состоит в преодолении проблем, возникающих в тех, уже упоминавшихся, случаях, когда запоминающий материал представляет собой полимер или сополимер.

Решение перечисленных задач, а также достижение других преимуществ и особенностей обеспечены созданием устройства в соответствии с настоящим изобретением. Данное устройство характеризуется тем, что электроды каждой электродной решетки выполнены с высокой плотностью расположения и изолированы друг от друга барьерным слоем с толщиной δ, составляющей долю толщины электродов, так что коэффициент заполнения поверхности для электродов в составе электродной решетки приближается к 1. При этом верхняя поверхность электродной решетки, обращенная к следующей электродной решетке, снабжена параллельными канавками, ориентированными ортогонально по отношению к электродам и пространственно отделенными одна от другой промежутками, близкими к ширине w электродов. В сечении параллельные канавки имеют профиль, соответствующий профилю электродов в сечении, а, по меньшей мере, каждый второй электрод смежной следующей электродной решетки выполнен заглубленным в канавки, сформированные в смежной предшествующей электродной решетке. Запоминающий материал нанесен в виде слоя поверх каждой электродной решетки, покрывая поверхность указанной электродной решетки, а также, по меньшей мере, часть боковых стенок и предпочтительно дно канавок. Электроды, заглубленные в канавки, совместно с ортогонально скрещенными с ними электродами смежной предшествующей электродной решетки задают в запоминающем материале, находящемся внутри канавок, ячейки памяти, имеющие, по меньшей мере, два направления переключения. В результате устройство объемного хранения данных обладает очень высокой плотностью хранения данных. Кроме того, способностью переключения, по меньшей мере, в двух направлениях обладает, по меньшей мере, каждая вторая ячейка памяти в слое запоминающего материала.

В предпочтительном варианте изобретения запоминающий материал является ферроэлектрическим или электретным материалом, представляющим собой полимер или сополимер, а все слои каждого запоминающего устройства выполнены в виде тонких пленок. При этом каждая электродная решетка может быть сформирована из двух или более слоев, первый из которых состоит из металла, а второй - из электропроводящего полимера, образующего контактный слой, находящийся в непосредственном контакте с запоминающим материалом запоминающего устройства.

В предпочтительных альтернативных вариантах заглубленным в канавки, сформированным в смежной предшествующей электродной решетке выполнен каждый или каждый второй электрод смежной следующей электродной решетки. При этом в первом из данных вариантов устройство содержит ячейки памяти только с, по меньшей мере, двумя направлениями переключения, а во втором варианте - примерно равные количества ячеек памяти с единственным и с, по меньшей мере, двумя направлениями переключения. Соответственно коэффициент заполнения поверхности для ячеек памяти в первом варианте равен половине коэффициента заполнения поверхности для электродов в составе электродной решетки, а во втором варианте он равен указанному коэффициенту заполнения поверхности для электродов.

Краткое описание чертежей

Далее устройство согласно настоящему изобретению будет детально описано с подробным обсуждением его составных частей и вариантов осуществления, проиллюстрированных на прилагаемых чертежах.

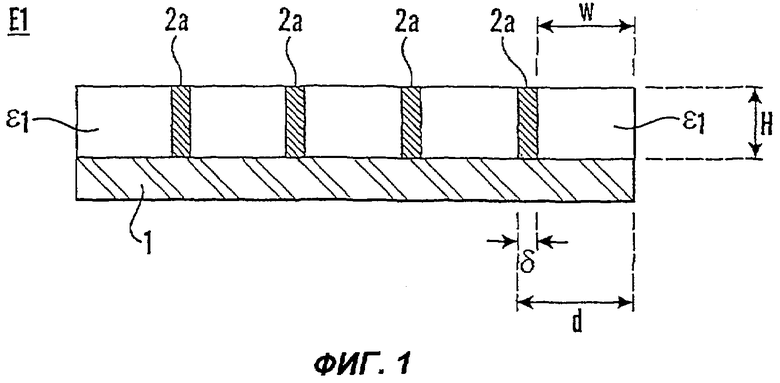

На фиг.1 представлена в сечении первая электродная решетка, входящая в состав устройства хранения данных согласно изобретению.

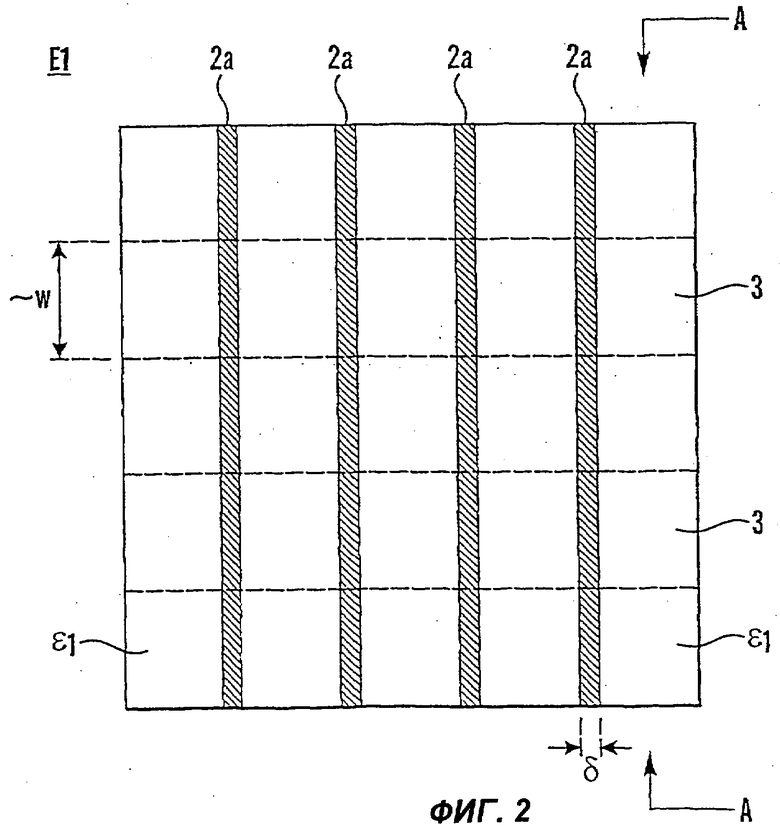

Фиг.2 соответствует виду сверху на первую электродную решетку по фиг.1.

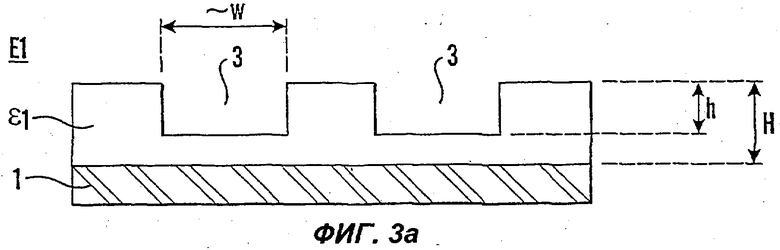

На фиг.3а изображено сечение электродной решетки плоскостью А-А, показанной на фиг.2.

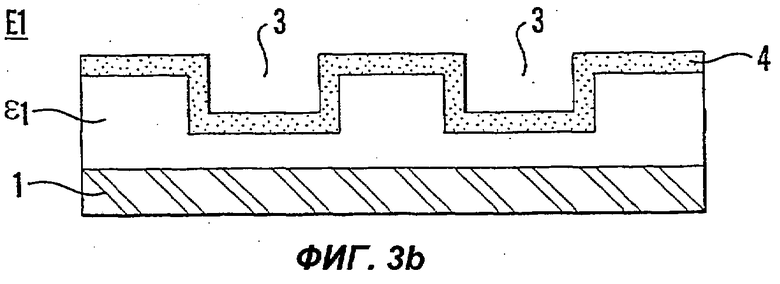

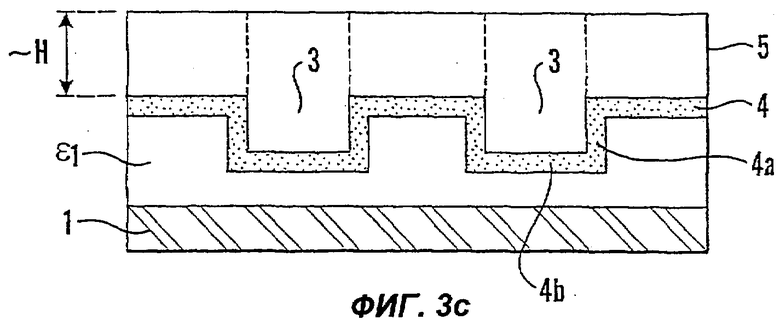

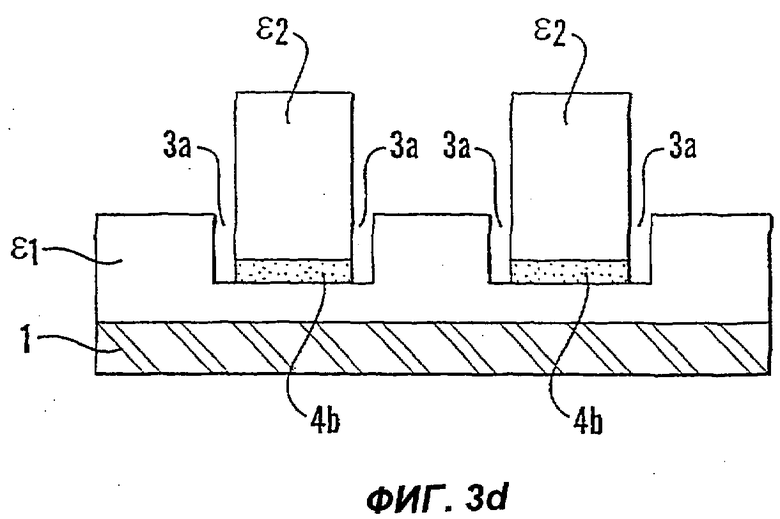

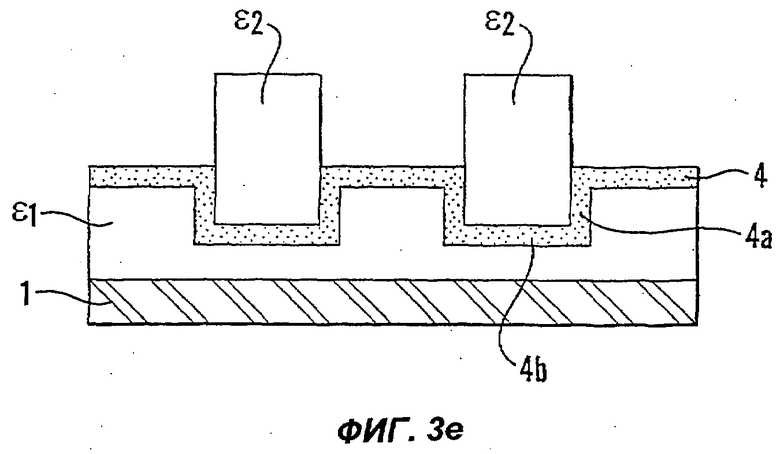

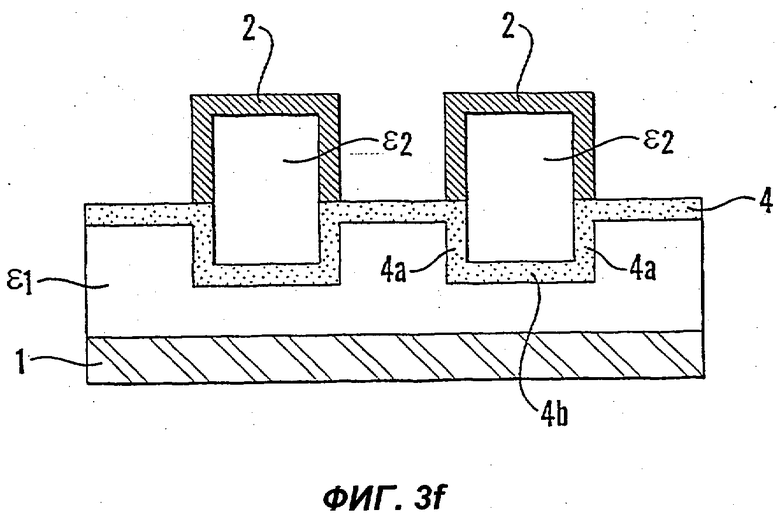

Фиг.3b-3f иллюстрируют различные операции, применяемые для формирования второй электродной решетки в устройстве хранения данных согласно изобретению, причем виды, представленные на данных чертежах, также соответствуют сечениям плоскостью А-А.

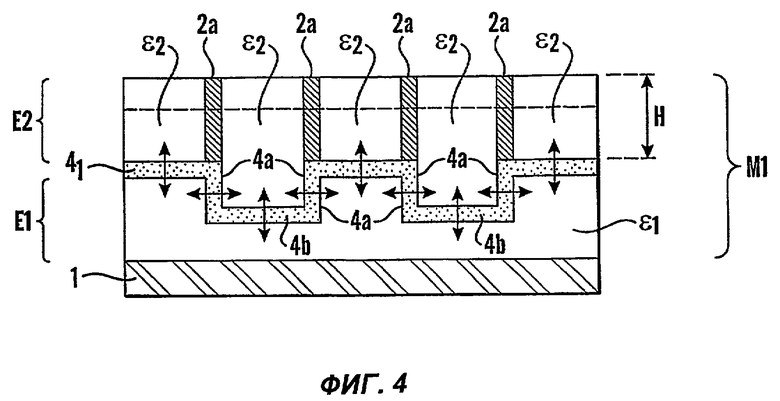

На фиг.4 в сечении той же плоскостью А-А представлено первое запоминающее устройство в составе устройства хранения данных согласно изобретению.

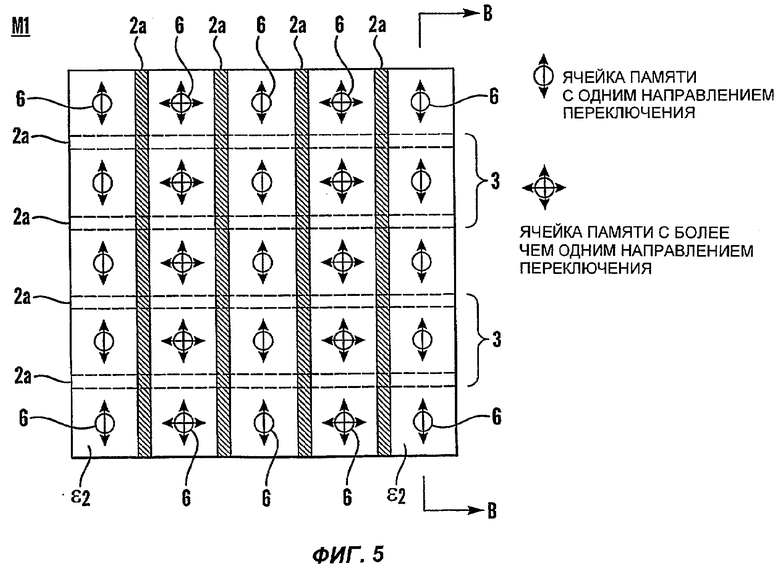

Фиг.5 соответствует виду сверху на первое запоминающее устройство в составе устройства хранения данных согласно изобретению.

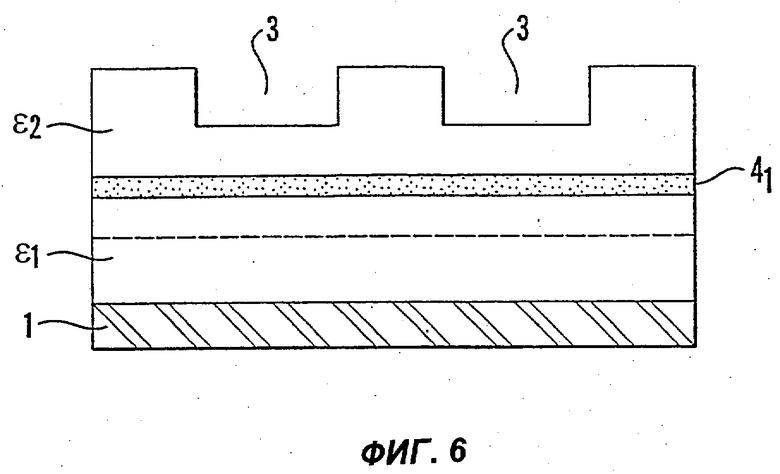

На фиг.6 устройство хранения данных по фиг.5 представлено в сечении плоскостью В-В, показанной на фиг.5.

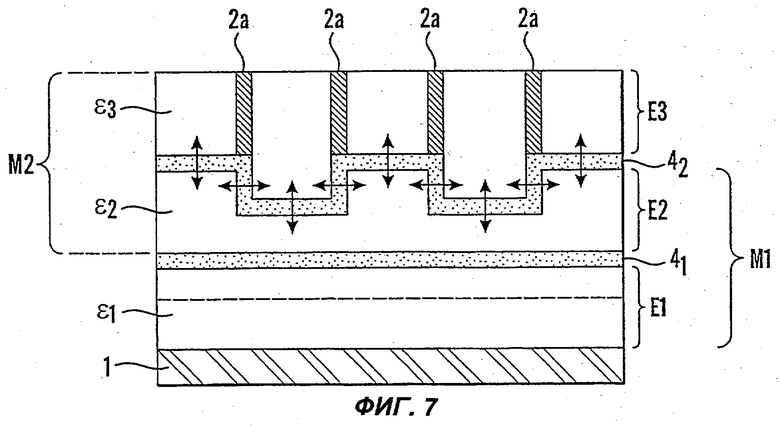

Фиг.7 иллюстрирует формирование второго запоминающего устройства поверх первого запоминающего устройства в составе устройства хранения данных согласно изобретению также в сечении плоскостью В-В.

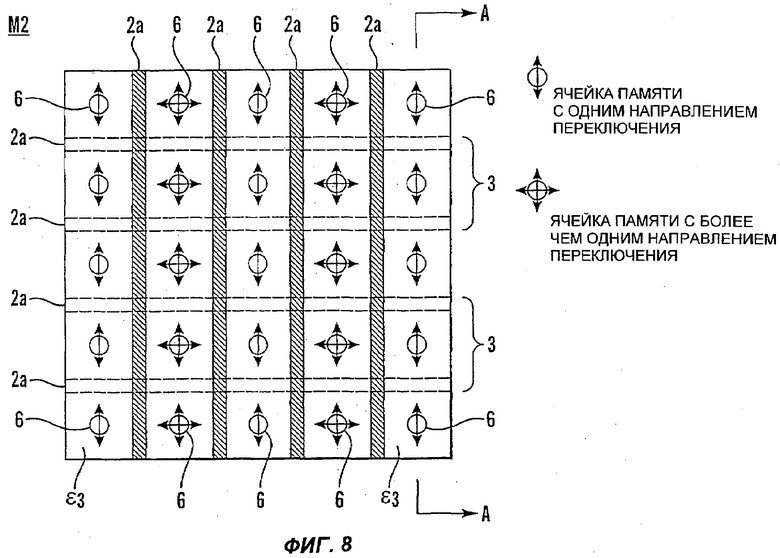

На фиг.8 на виде сверху показано устройство хранения данных согласно изобретению с двумя запоминающими слоями.

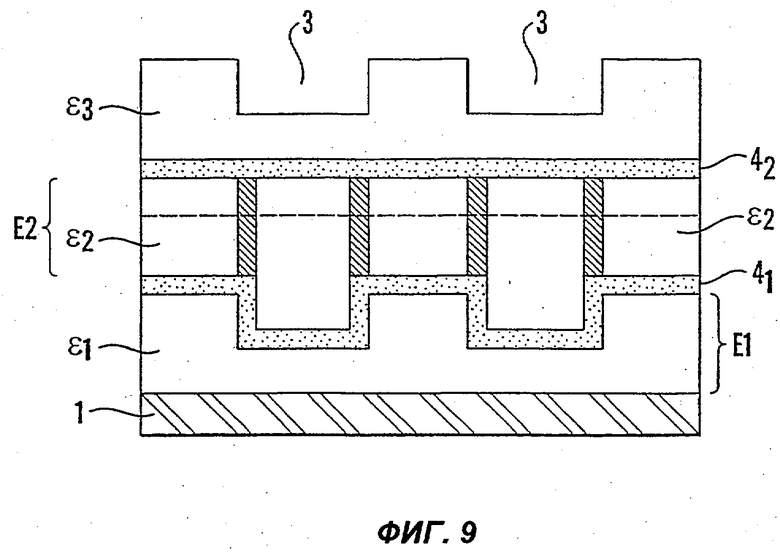

На фиг.9 представлено сечение устройства хранения данных по фиг.8 плоскостью А-А, показанной на фиг.8.

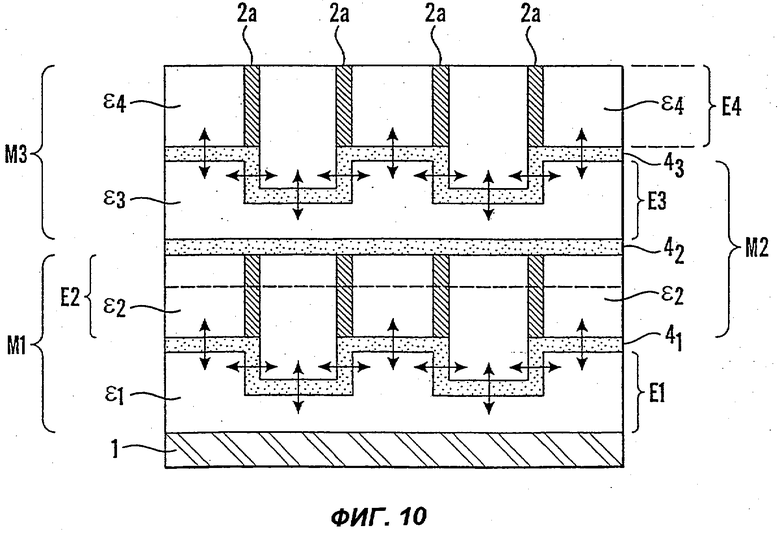

На фиг.10 представлено сечение устройства хранения данных, аналогичное показанному на фиг.9, но иллюстрирующее формирование третьего запоминающего устройства поверх второго запоминающего устройства.

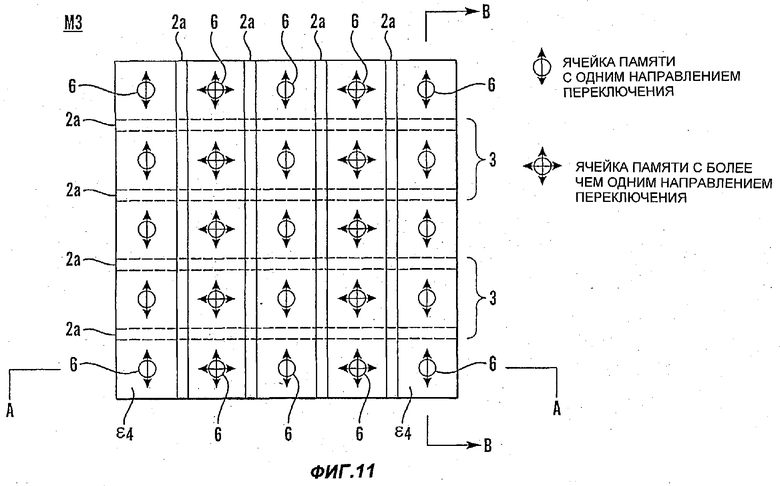

На фиг.11 представлен виду сверху на устройство хранения данных по фиг.10, содержащее третье запоминающее устройство.

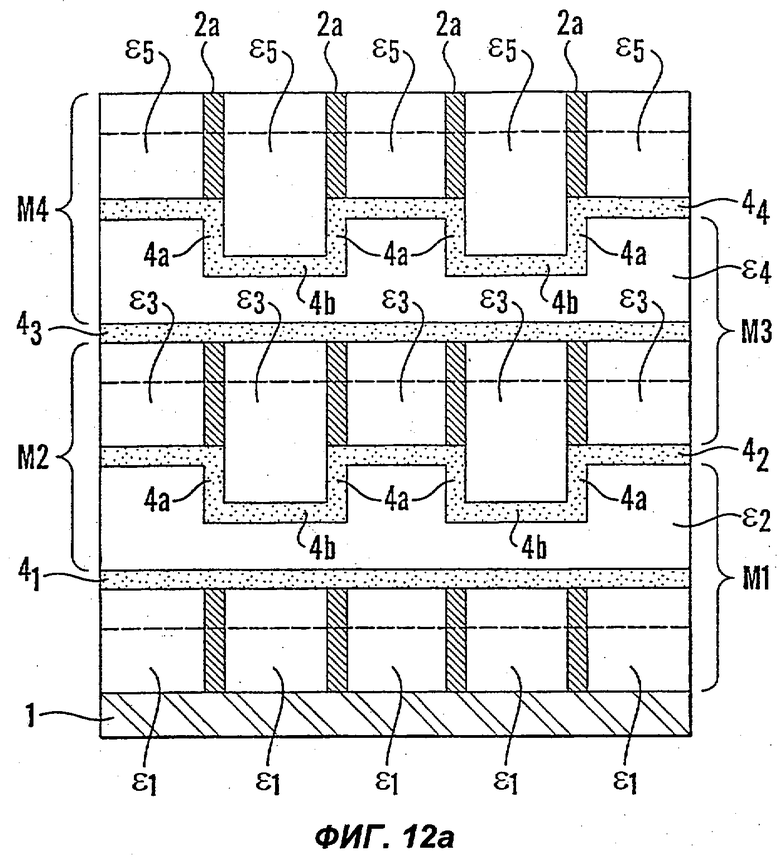

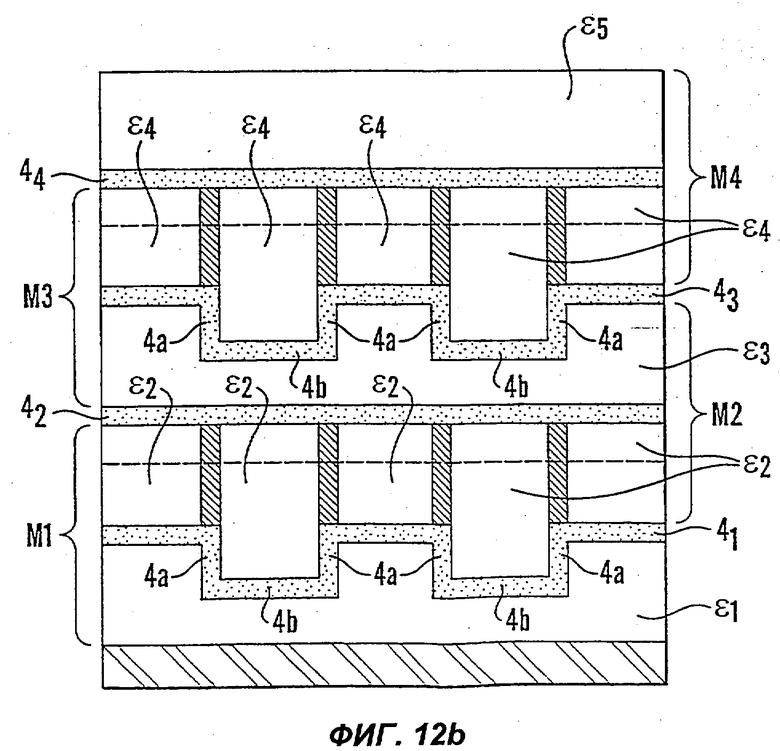

На фиг.12а в сечении плоскостью В-В, показанной на фиг.11, схематично изображен вариант устройства хранения данных согласно изобретению, содержащего четыре запоминающих устройства.

На фиг.12b показан вариант устройства хранения данных согласно изобретению, аналогичный варианту по фиг.12а, но изображенный в сечении плоскостью А-А, показанной на фиг.11.

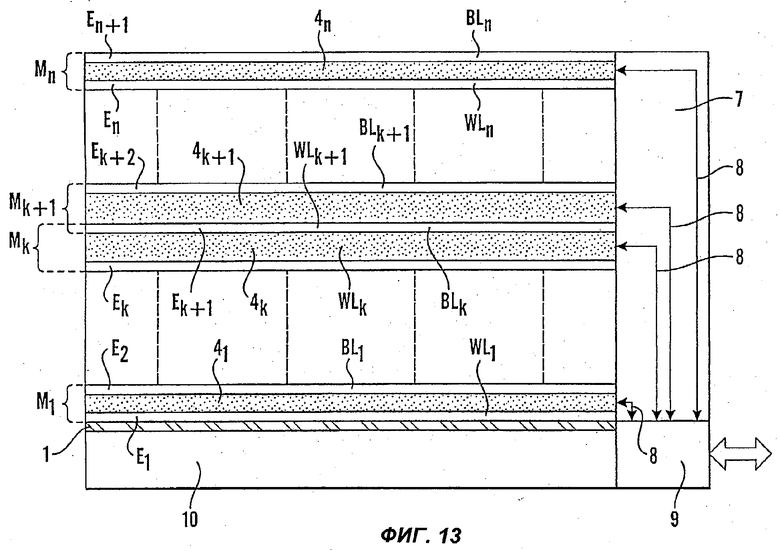

На фиг.13 схематично представлена общая конструкция и составные части устройства хранения данных согласно изобретению.

Осуществление изобретения

На фиг.1 представлена в сечении электродная решетка E1, входящая в состав устройства по изобретению. Электродная решетка E1 содержит множество взаимно параллельных электродов ε1, которые на виде данной электродной решетки Е1 сверху (см. фиг.2) имеют вид полосок. Каждый электрод ε1 расположен на изолирующей подложке 1 и отделен от смежных электродов только тонкой изолирующей пленкой 2а, которая предотвращает омический контакт между смежными электродами ε1. Высота (толщина) Н и ширина w электродов ε1 выбраны из условия получения большого коэффициента формы, т.е. отношения H/w. Тонкая изолирующая пленка 2а имеет толщину δ, которая в типичном случае значительно меньше ширины w электродов. Это означает, что, как показано на фиг.2, основная часть площади поверхности, занимаемой электродной решеткой Е1, приходится на электроды ε1, в то время как тонкая изолирующая пленка (барьерный слой) 2а между электродами занимает лишь малую часть этой поверхности (если используется фотолитография с разрешением 0,15 мкм или хуже; при фотолитографии с более высоким разрешением разность площадей электродов и пленки уменьшается).

Набор электродов такого типа может быть получен способом, раскрытым в международной заявке WO 03/046995 А1, опубликованной 5.06.2003, основанной на заявке на патент Норвегии 20015509, поданной 9.11.2001 и принадлежащей заявителю настоящего изобретения. Поэтому фактический способ получения набора электродов высокой плотности указанного типа более подробно здесь освещаться не будет, тогда как содержание указанной заявки включено в данное описание посредством ссылки на нее. В этой связи, однако, следует заметить, что ширина электрода может быть согласована с минимальным размером f элемента, получение которого ограничивается возможностями технологического процесса и значение которого будет зависеть, например, от правил конструирования, применяемых при разработке рисунка для микрофотолитографии. В любом случае из этого следует, что или ширина w электрода, или расстояние d от одного электрода до следующего в электродной решетке E1 электродов будут регламентироваться правилами конструирования такого рода. Между тем, толщины изолирующей тонкой пленки это может и не касаться, ибо ее нанесение может быть выполнено с использованием процессов, на которые не накладываются ограничения со стороны каких-либо стандартных правил конструирования. Из этого также следует, что фактическая ширина, например, каждого второго электрода ε в электродной решетке Е может быть на величину 2δ меньше минимального размера f элемента, который ограничивается возможностями технологического процесса. Другими словами, параметром, на который правила конструирования фактически накладывают ограничение, будет являться расстояние d=w+2δ.

На виде сверху, представленном на фиг.2, показана электродная решетка E1 с канавками (углублениями) 3, которые отходят вниз от верхней поверхности электродов ε1. Эти канавки 3, имея ширину, примерно такую же, как и ширина w электродов ε1, ориентированы перпендикулярно электродам ε1 и отделены одна от другой оставшимися участками электродов ε1, которые аналогично могут иметь ширину, примерно равную w. Канавки 3 заглублены от верхней поверхности электродов ε1 вниз, в направлении подложки, на величину h и имеют, по существу, прямоугольное поперечное сечение. На дне канавок участки электродов ε1 будут связаны между собой переходами, выступающими над подложкой 1 на высоту Н-h. Следует понимать, что хотя значение h может составлять большую часть Н, применительно к малым Н предпочтительно выбрать значение h равным примерно 50% от Н. Это хорошо видно на фиг.3а, на которой изображено сечение электродной решетки E1 по фиг.2 плоскостью А-А.

Далее со ссылками на фиг.3b-3f будут описаны производственные операции, применяемые для формирования второй электродной решетки Е2 в устройстве хранения данных согласно изобретению. На первой операции, которая иллюстрируется фиг.3b, электродную решетку Е1 с канавками 3 покрывают изолирующим тонкопленочным материалом 4. На второй операции (см. фиг.3с) изолирующий тонкопленочный материал 4 покрывают слоем электродного материала 5, который может быть аналогичен материалу электродов ε1. Высота (толщина) данного слоя может быть равной или превышающей Н. Электродный материал 5 полностью заполняет канавки 3. Изолирующий тонкопленочный материал 4 может представлять собой любой диэлектрический тонкопленочный материал; однако в предпочтительном варианте он является ферроэлектрическим или электретным тонкопленочным материалом, который будет описан далее. Затем выполняется третья операция, состоящая в профилировании, т.е. в создании рисунка рельефа электродов ε2. Электроды ε2 имеют высокий коэффициент формы и расположены в канавках 3, ориентированных ортогонально электродам ε1, входящим в состав первой электродной решетки E1.

Первый вариант операции профилирования иллюстрируется фиг.3d. В данном варианте производят удаление посредством травления электродного материала 5, а также изолирующего тонкопленочного материала 4. Процесс травления может быть двухступенчатым, т.е. предусматривающим сначала удаление расположенного сверху электродного материала 5, а затем изолирующего тонкопленочного материала 4 (см. фиг.3d) без какого-либо воздействия на ранее нанесенные электроды ε1. В результате формируются электроды ε2, имеющие высокий коэффициент формы и локализованные в канавках поверх изолирующей тонкой пленки 4b. При этом между боковыми стенками канавок 3 и сформированными внутри них электродами ε2 образуются карманы 3а. После этого с использованием запоминающего материала 4 заполняют карманы 3а и покрывают верхние поверхности электродов ε1 с получением результирующей структуры, представленной на фиг.3е.

Однако, если тонкопленочный материал 4, нанесенный в ходе первой операции, проиллюстрированной фиг.3b, представлял собой ферроэлектрический или электретный запоминающий материал, процесс травления может быть организован таким образом, чтобы удалить с его помощью только поверхностный слой электродного материала 5. В этом случае структура, представленная на фиг.3е, может быть получена всего за одну операцию. Как видно из данного чертежа, тонкопленочный материал 4, являющийся ферроэлектрическим или электретным запоминающим материалом, полностью покрывает поверхности электродов ε1. В частности, участки 4а этого материала будут покрывать боковые стенки канавок 3, в то время как дно канавок будет покрыто участками 4b того же материала. Отсюда следует, что участки 4а и 4b ферроэлектрического тонкопленочного материала 4, расположенные соответственно вдоль боковых стенок и на дне канавок 3, будут составлять части запоминающего материала соответствующих ячеек памяти, адресация к которым осуществляется через электроды ε1, ε2 электродных решеток E1, Е2.

В ходе четвертой операции электроды ε2, обладающие высоким коэффициентом формы и локализованные в канавках 3, покрывают тонкой пленкой 2 изолирующего материала. Тонкая пленка 2 изолирующего материала может быть сформирована, например, путем селективного окисления (оксидирования) электродов ε2. На пятой, заключительной операции между электродами ε2 (имеющими вид, показанный на фиг.3f), включая пустые участки, не занятые теми электродами ε2, которые расположены в канавках 3, выступая из них, наносят дополнительный электродный материал. Получающаяся при этом конструкция показана в сечении на фиг.4. Данная конструкция образует первое запоминающее устройство M1. В этом устройстве электродная решетка Е2 расположена над электродной решеткой E1, причем взаимно параллельные электроды ε2 с высокой плотностью расположения ориентированы ортогонально по отношению к электродам ε1, входящим в состав первой электродной решетки E1. Электроды ε2 второй электродной решетки аналогичны по форме электродам ε1 первой электродной решетки и изолированы друг от друга посредством тонких изолирующих барьерных слоев 2а.

Запоминающий материал 41 первого запоминающего устройства в устройстве хранения данных согласно изобретению находится между электродными решетками E1, ε2, так что в зонах скрещивания электродов этих решеток образуются ячейки 6 памяти, как это особенно наглядно показано на фиг.5. Каждый второй электрод ε2 находится в канавке, расположенной между электродами ε1 и ориентированной перпендикулярно к ним. Ячейка 6 памяти, образующаяся в зоне скрещивания этих электродов, также расположена в соответствующей канавке. При этом, как показано двойными стрелками на фиг.4, такая ячейка памяти может переключаться в трех направлениях, в том числе в направлениях, перпендикулярных боковым стенкам канавки, а также в направлении, перпендикулярном ее дну. Остальные электроды ε2 электродной решетки Е2 находятся вне канавок и могут переключаться только в единственном направлении, изображенном двойной стрелкой, ориентированной перпендикулярно запоминающему материалу 41 первого запоминающего устройства.

На фиг.5, на виде сверху, изображена законченная конструкция, соответствующая, например, первому запоминающему устройству M1, представленному на фиг.4. Наглядно показано, что электроды ε2 второй электродной решетки Е2 ориентированы перпендикулярно электродам ε1 первой электродной решетки E1. Запоминающий материал 4а и в соответствующем варианте 4b, находящийся между электродами ε1 и ε2 на дне канавок 3 и над электродами ε1, образует запоминающую среду 41 ячеек 6 памяти (только часть которых обозначена на фиг.5) запоминающего устройства M1. В представленной на фиг.5 конструкции запоминающий материал 4 и электроды ε1, ε2 образуют массив ячеек 6 памяти с пассивной матричной адресацией. Эти ячейки памяти предпочтительно являются ферроэлектрическими или электретными; особенно предпочтительно, чтобы запоминающий материал 4 представлял собой полимер или сополимер.

Из фиг.4, соответствующей виду данного устройства в сечении, можно видеть, что приложение напряжения к электродам ε1 и ε2 приведет к созданию между ними электрического потенциала, приложенного к запоминающему материалу 41. Ячейки 6 памяти, адресуемые посредством электродов, расположенных в канавках 3, могут быть поляризованы или переключены в различных направлениях. Часть ячейки памяти, соответствующая участку 4а, может быть, например, переключена в поперечном направлении относительно длины запоминающего устройства M1, тогда как ее часть, соответствующая участку 4b (которая может иметься в одном из вариантов устройства), может быть переключена в направлении, перпендикулярном плоскости запоминающего устройства М1, что на фиг.4 соответствует вертикальному направлению. В данном режиме возможно одновременное переключение трех "областей" ячейки памяти. В результате будет получен сигнал, почти вдвое превышающий сигнал от обычной ячейки памяти, расположенной между слоями электродов, поскольку площадь участка 4а на дне канавки равна площади зоны перекрытия электродов, т.е. w2, а площадь двух участков вдоль боковых стенок канавки составляет 2wh, где h˜1/2w. Таким образом, по сравнению с ячейками памяти, переключаемыми в вертикальном направлении, которые известны из уровня техники, изобретение обеспечивает дополнительное измерение и делает активную площадь ячейки памяти независимой от ограничений, накладываемых существующими правилами конструирования.

Поскольку перед описанным выше нанесением каждого электродного слоя может быть проведена планаризирующая операция, введение дополнительных слоев не должно привести к потере литографической плотности и однородности пленки. Отсюда следует, что если не учитывать потенциальные трудности, связанные с межслойными перемычками и соединениями, не существует технических ограничений в отношении количества слоев, которые могут быть собраны в пакет описанным образом. Это выгодно отличает изобретение от устройств с вертикальной архитектурой, в которых по мере роста количества слоев планаризация становится все более трудноосуществимой.

Таким образом, в составе запоминающего устройства M1 образуется запоминающая матрица с коэффициентом заполнения поверхности, который близок к коэффициенту заполнения поверхности для соответствующих электродных решеток E1, E2. Каждая вторая ячейка 6 памяти в составе запоминающего устройства может быть переключена более чем в одном направлении. При этом можно дополнительно отметить, что запоминающая матрица представляет собой память с пассивной матричной адресацией, т.е. она не содержит дискретных переключающих элементов, связанных с какими-либо ячейками 6 памяти.

Далее, со ссылками на фиг.6-8 будет описан процесс формирования в составе устройства хранения данных по настоящему изобретению второго запоминающего устройства М2, которое образуется поверх первого запоминающего устройства M1, изображенного в сечении на фиг.4. На фиг.6 то же самое устройство также изображено в сечении, но на этот раз плоскостью В-В (см. фиг.5), ориентированной под прямым углом к плоскости, использованной при получении сечения на фиг.4.

Аналогично операции, проиллюстрированной на фиг.3а, в электродах ε2 электродной решетки Е2 производят формирование канавок 3, ориентированных аналогичным образом и имеющих схожие размеры. Вслед за этим выполняют описанные выше операции, проиллюстрированные на фиг.3b-3f с получением конструкции, показанной на фиг.7. Полученная при этом дополнительная электродная решетка Е3 аналогична электродной решетке E2, представленной на фиг.4, но, разумеется, ее электроды ε3 ориентированы ортогонально электродам ε2 электродной решетки Е2. Штриховая линия на фиг.6 и 7 показывает, насколько глубоко канавки 3 заглублены в данные электроды. В результате формируется второе запоминающее устройство M2, входящее в состав пакета, образующего устройство хранения данных по изобретению, и содержащее электродные решетки Е2, Е3 и аналогичный массив ячеек 6 памяти. Это наглядно показано на фиг.8, где запоминающее устройство М2, расположенное над запоминающим устройством M1, представлено на виде сверху.

На фиг.8 видны, в частности, ячейки 6 памяти данного устройства (причем снова обозначены только некоторые из этих ячеек), образующие массив с матричной адресацией. Из фиг.7 видно, что второе запоминающее устройство M2 использует электродную решетку Е2 совместно с предшествующим ему в пакете запоминающим устройством M1. Другими словами, если в запоминающем устройстве M1 электроды ε1 электродной решетки E1 образуют управляющие шины, а электроды ε2 электродной решетки E2 - шины данных, то в запоминающем устройстве М2 электроды ε2 электродной решетки E2 должны соответственно образовать управляющие шины, а электроды ε3 электродной решетки Е3, расположенные в самой верхней части конструкции (см. фиг.7), шины данных. Особенности данной схемы и вытекающие из них следствия будут подробно рассмотрены далее.

Производственные операции, использованные для формирования собранных в пакет запоминающих устройств M1 и М2, разумеется, могут быть повторены с целью формирования требуемого количества запоминающих устройств М, собранных в пакет. Подобный процесс будет далее описан более подробно со ссылками на фиг.9-12, иллюстрирующие один из возможных вариантов устройства хранения данных по настоящему изобретению, содержащего четыре запоминающих устройства M1-M4, собранных в пакет. Разумеется, должно быть понятно, что иллюстрации представленного варианта носят схематичный характер и построены без соблюдения масштабных соотношений, которые должны соблюдаться в реальных условиях производства. Как следствие, представленный на чертежах вариант дает только общее представление о реальных возможностях устройства хранения данных по изобретению в отношении достижимого количества ячеек памяти и собираемых в стопу запоминающих устройств, а также достижимого суммарного объема памяти устройства по изобретению.

На фиг.9 представлено сечение устройства хранения данных по изобретению плоскостью А-А (см. фиг.8), т.е. ориентированное под прямым углом относительно сечения, представленного на фиг.7. Далее следует повторение операций, проиллюстрированных на фиг.3b-3f, с получением в результате конструкции, показанной на фиг.10, в состав которой входят три собранных в пакет запоминающих устройства M1, М2, М3 и четыре электродных решетки E1-E4, выполняющие функции чередующихся управляющих шин и шин данных для запоминающих устройств, составляющих пакет. Горизонтальная штриховая линия, пересекающая электродную решетку Е2 на фиг.9 и 10, показывает, насколько канавки для формирования электродной решетки Е3 заглублены в электроды ε2 электродной решетки E2. Направления переключения сформированных ячеек 6 памяти в составе запоминающих устройств M1, М3 обозначены двойными стрелками. Эти направления показаны также на фиг.11, соответствующей виду сверху на устройство по фиг.10. Как и раньше, каждая вторая ячейка 6 памяти способна переключаться в нескольких направлениях (см. в этой связи пояснительные надписи на фиг.11).

Фиг.12а и 12b схематично иллюстрируют вариант осуществления устройства хранения данных по изобретению, представленный в сечениях соответственно плоскостями А-А и В-В (см. фиг.11), т.е. ориентированными под прямым углом одна к другой. Изображенный на фиг.12а, 12b вариант содержит четыре собранных в пакет запоминающих устройства M1-M4 и электродные решетки E1-E5 с электродами ε1-ε5 соответственно. Как и раньше, нижние границы канавок, в которых расположены электроды следующей электродной решетки, обозначены горизонтальными штриховыми линиями. При этом на фиг.12а эти линии проходят через электроды ε1, ε3, а на фиг.12b - через электроды ε2, ε4.

Как будет показано далее, электроды ε1 можно рассматривать как управляющие шины запоминающего устройства M1, а электроды ε2 - как его шины данных. Аналогичным образом электроды ε2 образуют также управляющие шины следующего запоминающего устройства М2 и т. д. Отсюда с очевидностью следует, что количество электродных решеток, которые содержатся в устройстве хранения данных по настоящему изобретению, только на единицу превышает количество используемых запоминающих устройств. Таким образом, в устройстве хранения данных описанного типа количество электродов составляет примерно половину от аналогичного количества электродов, использующихся в традиционных известных структурах типа "сэндвич". Данное свойство изобретения обеспечивает упрощение конструкции и, разумеется, приводит к уменьшению высоты пакета запоминающих устройств.

Поскольку электродные решетки альтернативно функционируют в качестве управляющих шин и шин данных для соответствующих запоминающих устройств М, протокол адресации должен с учетом этого обстоятельства строиться таким образом, чтобы избегать одновременной адресации к двум смежным запоминающим устройствам. Применительно к варианту, представленному на фиг.12а, 12b, это означает, что одновременная адресация для осуществления записи, считывания или стирания допустима к запоминающим устройствам M1 и М3 или к запоминающим устройствам М2 и М4. Другими словами, напряжение, приложенное к электродам ε1 и ε2 с целью адресации к ячейкам памяти, соответствующим запоминающему слою 41 запоминающего устройства M1, не должно влиять на ячейки памяти в запоминающем слое 42 запоминающего устройства М2 или создавать существенные помехи этим ячейкам памяти, несмотря на то, что на запоминающем слое 42 запоминающего устройства М2 может в данном случае присутствовать разность потенциалов. Наличие этой разности потенциалов может быть, однако, преодолено за счет принятия соответствующих мер по адаптации применяемого протокола адресации. Очевидной мерой такого типа стала бы подача на электроды ε2, ε3 такого же напряжения, что и приложенное к электродам ε2. Это гарантировало бы, что на запоминающий материал 42 не воздействует никакая разность потенциалов.

Из уровня техники известны различные протоколы, минимизирующие так называемое возмущение соседних ячеек. Некоторые из этих протоколов патентуются заявителем настоящего изобретения. Следует, однако, отметить, что протоколы, разработанные для того, чтобы избежать мешающих воздействий на неадресуемые ячейки или взаимных помех между адресуемыми ячейками, обычно ограничиваются вариантами, принимающими во внимание только отдельные запоминающие устройства с матричной адресацией. Известные протоколы не адаптированы специально для вариантов сборки запоминающих устройств в пакет с использованием электродов, выполненных аналогично их выполнению согласно изобретению. Тем не менее, имеется возможность применить известные принципы проектирования и к трехмерному случаю, т.е. к структурам, собранным в пакет (стопу), когда существует вероятность создания помех в адресуемом запоминающем устройстве.

Устройство хранения данных согласно изобретению позволяет создать трехмерную (объемную) память с очень высокой плотностью хранения данных, а также с коэффициентом заполнения поверхности, близким к оптимальному в отношении как электродов, так и ячеек памяти, поскольку указанный коэффициент заполнения поверхности и в том, и в другом случае близок к единице. Для изготовления каждой электродной решетки требуются только две операции травления или профилирования: первая операция профилирования или травления для получения электродов с высокой плотностью расположения, образующих электродную решетку E1, и последующее травление канавок 3 в указанной электродной решетке. При этом следует указать, что для выполнения обеих операций может быть использована одна и та же маска, которая для выполнения операции, проиллюстрированной на фиг.3а, должна быть развернута на 90°. Кроме того, нанесение слоев барьерного или запоминающего материала и электродного материала 5 может быть произведено посредством двух последовательных операций, как это показано на фиг.3b и 3с. Таким образом, для получения конструкции, показанной на фиг.3е, требуется только одна операция маскирования. При этом та же самая маска, которая была применена для формирования первой электродной решетки E1, может быть при соответствующей ориентации, использована на всех последующих операциях маскирования в процессе формирования последующих электродных решеток Е2, Е3 и т. д. при условии использования тех же самых конструктивных параметров. Данное обстоятельство будет способствовать значительному сокращению затрат на изготовление устройства хранения данных согласно настоящему изобретению.

Что касается ячеек памяти, например, подобных представленным на фиг.10, можно заметить, что половина этих ячеек может быть переключена только в одном направлении. Данный тип ячеек соответствует расположению запоминающего материала между электродами, образующими управляющие шины и шины данных. В то же время в случае, когда электроды находятся в канавках, сформированных в предшествующей электродной решетке, ячейку памяти можно переключать более чем в одном направлении, в частности в трех направлениях, как это показано на фиг.10. С учетом того, что глубина h канавки 3 может быть, по меньшей мере, сравнимой с половиной высоты Н предшествующего электрода, должно быть понятно, что запоминающий материал 4 (например, в виде запоминающей пленки), который покрывает обе боковые стенки, а также дно канавки, обладает значительно большей поверхностью, обращенной к управляющей шине и к шине данных, которые служат для адресации к соответствующей ячейке памяти, чем запоминающий материал, расположенный между электродами по схеме сэндвича. Переключение во всех направлениях будет, очевидно, происходить одновременно, причем таким образом, что эффективная площадь поверхности ячейки может быть более чем удвоена, с соответствующим увеличением отношения сигнал/шум, по меньшей мере, в 2 раза.

Можно видеть также, что увеличение коэффициента формы электродов ε и соответственно формирование более глубоких канавок приведет к увеличению эффективной поверхности ячеек памяти. В этой связи следует отметить, что площадь поверхности вертикальных участков ячейки памяти не является критическим фактором в случае, если применяемая фотолитографическая технология ориентирована на малые значения шага рисунка и ширины линий, достижимые для фотолитографии в крайней ультрафиолетовой области. Можно также отметить, что увеличение эффективной поверхности ячеек и улучшение отношения сигнал/шум для адресуемой ячейки (например, в ходе операции деструктивного считывания, приводящего к обращению поляризации или к переключению направления поляризации ячейки памяти) будет способствовать сопротивляемости так называемой усталости. Усталость - это явление, проявляющееся после совершения некоторого (большого) количества переключений и заключающееся в том, что достижимая степень поляризации ячеек памяти будет уменьшаться с возрастанием количества осуществленных циклов переключения.

При сборке в пакет очень большого количества запоминающих устройств, у которых каждый слой состоит из тонких пленок, может иметь место нарушение плоскостности (бугристость). Однако этого явления можно легко избежать путем выполнения планаризующей операции в качестве заключительной операции в процессе изготовления каждой электродной решетки. Это должно стать понятно из рассмотрения фиг.4. Здесь, в сечении, представлено запоминающее устройство с двумя электродными решетками E1, Е2, причем изолирующий материал 2, расположенный поверх электродов ε2 (как это показано на фиг.3f), удаляется при нанесении остающейся части электродов ε2, входящих в состав электродной решетки Е2 (данная операция, разумеется, сохраняет изолирующие барьеры 2а между электродами ε2). Указанная операция удаления может быть использована также для планаризации верхней поверхности электродной решетки E2, поскольку процесс удаления может включать в себя либо механическое, либо химико-механическое полирование. Тем самым обеспечивается получение электродной решетки Е2 с гладкой верхней поверхностью, пригодной для выполнения следующих производственных операций по формированию следующего запоминающего устройства в составе собираемого пакета.

В принципе, существует только одно реальное ограничение для количества слоев, которые могут быть нанесены, или для количества запоминающих устройств, которые могут быть собраны в единый пакет с образованием объемного (трехмерного) устройства хранения данных согласно изобретению. Это (очевидное) ограничение, накладываемое на количество собираемых в пакет запоминающих устройств, заключается в необходимости подключения всех электродов (и косвенно всех ячеек памяти) к драйверным или управляющим контурам, расположенным на подложке 1, или к соответствующим контурам, связанным с этой подложкой. Подложка, в частности, может быть выполнена из кремния, а указанные контуры могут быть, например, изготовлены по соответствующей КМОП-технологии. При заданном объеме памяти увеличение коэффициента заполнения поверхности применительно к ячейкам памяти, соответствующее в данном случае уменьшению шага электродов, обеспечивает возможность сокращения количества запоминающих устройств в составе пакета без уменьшения заданного объема памяти. Еще одно решение проблемы подключения, разумеется, могло бы состоять в выполнении контуров для осуществления драйверных или управляющих функций в самом запоминающем устройстве, входящем в состав пакета. В этом случае в значительной степени сократится необходимость применения соединительных перемычек, электрически связанных с подложкой.

Вариант устройства хранения данных согласно изобретению, представленный на фиг.12а и 12b, разумеется, изображен весьма схематично. Показаны только четыре запоминающих устройства с 25 ячейками памяти в каждом устройстве, т.е. с общим количеством ячеек памяти, равным 100. При этом в данном варианте только 40 ячеек могут быть переключены в более чем одном направлении. Вместе с тем, в случае реального осуществления изобретения переключаемой в нескольких направлениях будет каждая вторая ячейка памяти, так что коэффициент заполнения поверхности подобными ячейками в каждом запоминающем устройстве приблизится к 0,5. С учетом очевидных достоинств ячеек памяти, способных переключаться в нескольких направлениях, обычные ячейки памяти, соответствующие конфигурации "сэндвич" и переключаемые только в одном направлении, становятся менее привлекательными. Поэтому они могут быть просто исключены из конструкции, тем более, что при этом будет обеспечен вполне адекватный коэффициент заполнения поверхности, равный 0,5. В подобном случае электродный материал для формирования электродов будет наноситься только в канавки, выполненные в предшествующей электродной решетке, тогда как промежутки между электродами, имеющие форму каналов, могут быть полностью заполнены, например, барьерным материалом.

В случае практической реализации изобретения на уровне, достигнутом современной технологией, устройство хранения данных, подобное представленному на фиг.12а и 12b (т.е. содержащее 4 запоминающих устройства, имеющих в сумме 100 ячеек памяти), могло бы быть выполнено с шириной линии порядка 0,5 мкм и с шагом около 1 мкм, поскольку толщина 5 барьерного слоя между электродами составляет лишь малую долю ширины w электродов.

Более реалистичный подход к функциональной реализации устройства хранения данных согласно изобретению представлен на фиг.13, разумеется, также в схематичном и обобщенном виде. Тем не менее, данный вариант включает в себя все функциональные части, необходимые для его работы. Устройство хранения данных представлено на фиг.13, содержащим n запоминающих устройств М1-Мn, собранных в пакет, т. е. расположенных одно над другим. Каждое из запоминающих устройств содержит, как это показано на чертеже, слой запоминающего материала 4. Для осуществления адресации к каждому запоминающему устройству М служат две электродные решетки Е, содержащие неизображенные электроды, находящиеся в контакте со слоем запоминающего материала 4 и образующие управляющие шины WL и шины BL данных для осуществления связи с ячейками памяти запоминающего устройства М. Разумеется, в представленном устройстве шины данных образуют управляющие шины следующего смежного запоминающего устройства. В частности, на фиг.13 показано, что для произвольно выбранного запоминающего устройства Mk электродная решетка Ek+1, образующая шины BLk данных запоминающего устройства Mk, одновременно образует управляющие шины WLk+1 запоминающего устройства Mk+1.

Соответственно, электродная решетка Ek+2 будет образовывать шины BLk+1 данных запоминающего устройства Mk+1 и т. д. Следствием такой конфигурации является, очевидно, то, что общее количество используемых электродных решеток равно n+1, т. е. на единицу превышает количество n запоминающих устройств М в устройстве хранения данных согласно изобретению. Собранные в пакет запоминающие устройства М расположены на подложке 1. Эта подложка, однако, может рассматриваться как часть подложки 10, которая может быть выполнена с использованием технологии обработки кремния и содержать драйверные и управляющие контуры, а также контуры для осуществления адресации к запоминающим устройствам М в составе пакета, расположенного над данной подложкой. В таком случае устройство хранения данных по изобретению содержит соединительную, или интерфейсную часть 7, расположенную со стороны боковых кромок запоминающих устройств. При этом для обеспечения необходимой коммуникации между частью подложки 10, несущей вышеупомянутые контуры, и запоминающими устройствами М используются соединительные перемычки (линии) 8, идущие от каждого запоминающего устройства М к интерфейсу 9 подложки. Данный интерфейс 9 подложки может быть дополнительно соединен с внешними или периферийными устройствами или с вычислительными устройствами. Альтернативно интерфейс 9 подложки может быть использован для интегрирования устройства хранения данных согласно изобретению в любую систему обработки данных, для которой требуется значительный объем памяти, т. е. высокая плотность хранения данных.

Приведенные выше значения ширины линий и шага расположения электродов подразумевают, что на площади 1 мкм2 будут расположены 4 ячейки памяти; соответственно для получения 4 миллионов ячеек в каждом запоминающем устройстве потребуется площадь 1 мм × 1 мм. Следовательно, пакет из четырех таких устройств обеспечит наличие 16 миллионов ячеек памяти на чипе площадью 1 мм2. Поскольку толщина пакета может быть порядка 1 мкм, объемная плотность хранения данных составит 16 Гбит/мм3. В случае уменьшения ширины линии до 0,2 мкм (что реально для современных фотоэлектрических технологий) запоминающее устройство в составе устройства хранения данных согласно изобретению будет способно разместить 25 ячеек памяти на площади 1 мкм2. При этом пакет из четырех запоминающих устройств займет объем 1 мкм3, что обеспечит объемную плотность хранения данных, равную 100 Гбит/мм3. Приведенные параметры представляются вполне достижимыми на уровне современной технологии. Правда, будет необходимо обратить особое внимание на решение проблем обеспечения требуемых соединений, а также проблем, связанных с возможными физическими помехами как термического, так и электрического характера. Однако эксперименты, проведенные заявителем, подтверждают, что названные проблемы являются преодолимыми, так что уменьшение размерных параметров в устройстве хранения данных согласно изобретению может быть доведено до предела, определяемого существующими технологическими возможностями в отношении профилирования.

Изобретение относится к устройству объемного хранения данных. Техническим результатом является высокая плотность хранения данных. Устройство содержит множество запоминающих устройств (М) с матричной адресацией, каждое из запоминающих устройств содержит две электродные решетки в виде слоев параллельных электродов, образующих управляющие шины и шины данных, при этом электроды каждой электродной решетки выполнены с высокой плотностью расположения и изолированы друг от друга барьерным слоем с толщиной, составляющей долю толщины электродов, причем верхняя поверхность одной электродной решетки, обращенная к следующей электродной решетке, снабжена параллельными канавками, ориентированными ортогонально по отношению к электродам и пространственно отделенными одна от другой промежутками, близкими к ширине электродов. 5 з.п. ф-лы, 19 ил.

| US 5550770 A, 27.08.1996.SU 1596392 A1, 30.09.1990.EP 0486901 A2, 27.05.1992.RU 2172975 C2, 27.08.2001. |

Авторы

Даты

2006-04-27—Публикация

2003-03-21—Подача