Область техники, к которой относится изобретение

Настоящее изобретение относится к средствам, обеспечивающим возможность адресации в устройстве, содержащем один или более объемных элементов. Объемные элементы в указанном устройстве, образующие совместно с указанными средствами части двумерной или трехмерной матрицы, представляют собой ячейки памяти, ячейки дисплеев, диоды, транзисторы и/или переключающие/модулирующие элементы. Для выполнения данных функций каждый объемный элемент содержит одну или более ячеек, обладающих, в зависимости от электронных или электрических свойств материала данного элемента, функциональными возможностями хранения данных, обработки данных или обработки сигналов. Указанное средство обеспечивает возможность адресации конкретного участка в объемном элементе путем установления селективного электрического соединения с объемным элементом или с его ячейкой (в случае, когда объемный элемент содержит более одной ячейки). Соответственно, выбор конкретного объемного элемента или его ячейки производится путем создания не обязательно одновременного электрического соединения с тремя или более электродами. Эти электроды сформированы указанным средством и находятся в контакте с объемным элементом для осуществления селективного взаимодействия с ним на участке этого элемента, находящемся в непосредственной близости к электродам, таким образом, что указанный участок определяет ячейку в указанном объемном элементе, с которой таким образом осуществляется взаимодействие.

Изобретение относится также к устройству, содержащему описанное средство, образующее совместно с одним или более объемными элементами часть двумерной или трехмерной матрицы в составе указанного устройства. При этом объемный элемент содержит одну или более ячеек, обладающую (обладающих), в зависимости от электронных или электрических свойств материала ячейки, функциональными возможностями хранения данных, обработки данных или обработки сигналов. Устройство содержит более одной матрицы описанного типа.

В широком смысле настоящее изобретение предлагает архитектуры адресации, которые обеспечивают электронный доступ через N выводов к объемным элементам или к их зонам в двумерных или трехмерных матричных структурах, в которых количество N выводов, с которыми должна быть осуществлена связь по каждому адресу в матрице, равно, по меньшей мере, трем.

Уровень техники

Ортогональные двумерные матрицы адресации очень широко применяются во многих различных электронных устройствах, таких как камеры, устройства памяти (запоминающие устройства) и дисплеи, в которых необходимо обеспечить индивидуальный электронный доступ к каждому отдельному элементу матрицы.

Простейший тип подобной матрицы состоит из одного набора взаимно параллельных электродных линий (называемых далее для краткости "а-электродами"), лежащих в одной плоскости, расположенной вблизи другой, параллельной ей плоскости, содержащей другой набор взаимно параллельных электродных линий (называемых далее для краткости "b-электродами"). Наборы электродов "а" и "b" ориентированы таким образом, что являются скрещивающимися, обычно ортогонально, обеспечивая тем самым возможность обращения к объемным элементам, расположенным между скрещивающимися электродами. Так, на объемный элемент между электродом аi в наборе а-электродов и электродом bi в наборе b-электродов можно воздействовать электрически путем подключения электродов аi и bi к соответствующему источнику тока или напряжения. Объемные элементы могут включать в себя активные элементы контура, способные запускаться при подаче на них входного сигнала. Альтернативно они могут быть выполнены в качестве переключающих или пассивных элементов, физическое состояние которых может быть изменено при приложении входного сигнала или определено при адресации по электродам "а" и "b". Подобные элементы могут быть, в частности, использованы для построения элементов памяти для хранения бинарных или многоуровневых логических величин.

Устройство, основанное на использовании матриц описанного типа, раскрыто, например, в международной заявке №PCT/NO 98/00185 (аналог - патент США №6055180), принадлежащей заявителю настоящего изобретения. Оно представляет собой пассивное устройство с электрической адресацией, которое может быть применено в оптических приемниках, объемных устройствах памяти или обработки данных. Известное устройство содержит функциональную среду в форме сплошной протяженной или профилированной структуры, которая может изменять свое физическое или химическое состояние. Данная функциональная среда, которая в рамках настоящего изобретения соответствует объемному элементу, имеет в своем составе индивидуально адресуемые ячейки, сформированные между анодом и катодом, входящими в состав электродных средств, которые контактируют с функциональной средой в ячейке и тем самым обеспечивают электрическую связь с данной ячейкой. Аноды выполнены в виде первого набора ленточных электродов, расположенных в слое, контактирующем с функциональной средой на одной ее стороне. Аналогично катоды выполнены в виде второго набора взаимно параллельных ленточных электродов, расположенных в слое, контактирующем с функциональной средой на другой ее стороне. При этом ленточные электроды в пределах каждого набора взаимно параллельны, а взаимная ориентация наборов электродов такова, что электроды одного набора ориентированы ортогонально по отношению к электродам другого набора.

Реально ячейка в объемном элементе функциональной среды в данном случае задается в зоне взаимного пространственного наложения (т.е. скрещивания) ленточного электрода первого набора и ленточного электрода второго набора. При адресации ячейки в известном устройстве, например, для осуществления записи, считывания или переключения (т.е. изменения логического значения, приписанного ячейке), электрическая энергия прикладывается непосредственно к функциональной среде ячейки через выбранную пару скрещенных электродов, входящих в первый и второй наборы электродов.

Международная заявка №PCT/NO 98/00212, также принадлежащая заявителю настоящего изобретения, описывает схожее устройство. Однако в нем используется электродная матрица с наборами электродов, взаимно изолированными и выполненными в виде мостиков. При этом функциональная среда охватывает и закрывает указанные наборы электродов. В дополнение к своему возможному использованию в качестве устройства памяти с электрической адресацией данная схема с электродами, используемыми как мостики и закрытыми функциональной средой (в отличие от описанного ранее устройства, в котором функциональная среда заключена между электродами), более легко применима, например, в оптической или электронной камере или в дисплее с электрической адресацией.

Наконец, в международной заявке №PCT/NO 98/00237, принадлежащей тому же заявителю, описано ферроэлектрическое устройство для обработки и/или хранения данных с пассивной электрической адресацией функциональной среды, которая представляет собой тонкую пленку ферроэлектрического материала, нанесенную поверх наборов электродов и закрывающую наборы электродов, которые и в этом случае выполнены в виде мостиков.

Во всех рассмотренных известных устройствах функциональная среда, соответствующая объемному элементу, расположенному между наборами электродов или поверх их, может быть нанесена в виде глобального (т.е. единого протяженного) слоя, в котором, разумеется, индивидуальные ячейки будут задаваться взаимным наложением электродов из первого и второго набора электродов. Вместе с тем, функциональная среда может быть структурирована или разбита на пикселы, так что в зонах между взаимно наложенными (скрещенными) электродами или над ними будут сформированы индивидуальные объемные элементы. Таким образом, в этом случае объемный элемент будет содержать только одну ячейку. Это, разумеется, не влияет на общее возможное количество ячеек в матрице, которое, по существу, будет равняться произведению количества электродов в каждом наборе.

В системах и матрицах описанного типа, обеспечивающих хранение или обработку электрических сигналов, элементы системы или матрицы, задаваемые описанным образом, могут включать, в зависимости от конкретного применения, различные компоненты и контуры. Однако к каждой зоне наложения электродов могут быть подведены извне только две электрические связи. Таким образом, два набора электродов, дающие только два соединения, могут обеспечить индивидуальную (эксклюзивную) адресацию устройств или контуров, имеющих не более двух выводов.

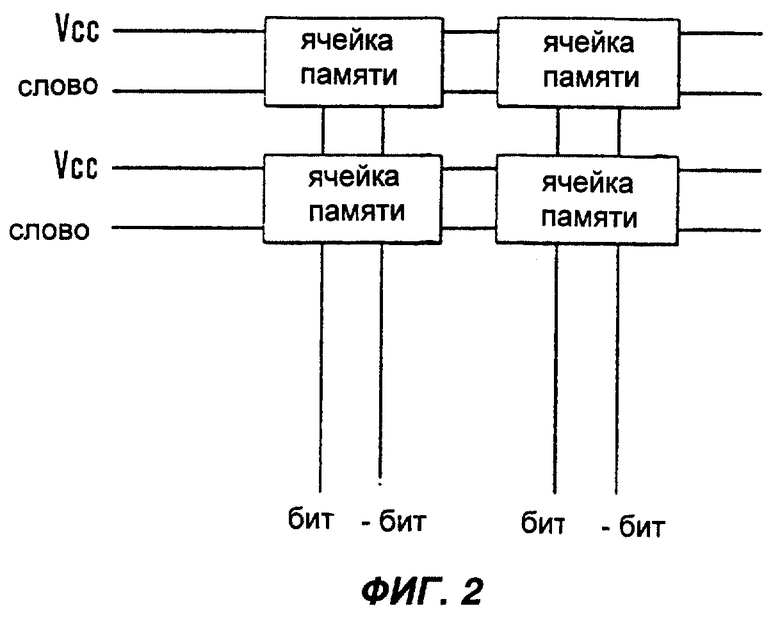

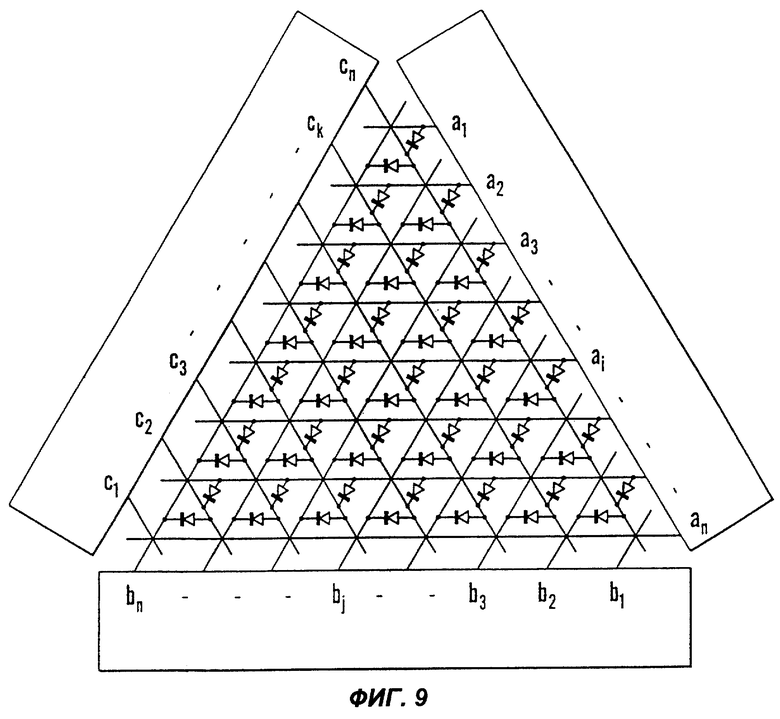

В настоящее время существуют различные подходы к работе с электронными системами, основанными на матрицах, в которых каждый элемент матрицы требует наличия более двух выводов. В SRAM-технологии ячейки памяти требуют более двух линий, в частности, четырех линий: Vcc, бит, -бит и слово (число). Известное решение для матрицы адресации ячеек по SRAM-технологии показано на фиг.1. В нем используются две параллельные линии, Vcc-линия и числовая линия, которые ориентированы перпендикулярно двум другим параллельным линиями, т.е. -бит и бит-линиям. Никакая индивидуальная адресация невозможна между двумя параллельными линиями, например, между -бит и бит-линиями.

Другое известное решение для осуществления индивидуальной адресации между более чем двумя линиями (или электродами) представлено на фиг.2. Здесь используется трехмерная матрица. Индивидуальная адресация обеспечивается между определенным набором линий, а именно ai, bj и ck. В случае выбора комбинации аi, bj обеспечивается выбор столбца, т.е. адресации конкретного элемента не происходит, пока не будет выбран также ck. Доступ к любому элементу, для которого выполнено требование i∈(1, imax), j∈(1, jmax) и k∈(1, kmax), может быть обеспечен с использованием для адресации комбинации аi, bj и ck.

Физическая реализация схем адресации, рассмотренных выше, не является простой, когда доступ к каждому элементу в матрице должен осуществляться не менее чем через три вывода.

В известных двумерных схемах типа рассмотренной выше, со ссылкой на фиг.1, для SRAM-устройств электронные контуры в типичном случае строятся по квазипланарному принципу, когда физическое положение элемента в матрице задается двумя координатами. При этом слои наносятся друг на друга путем последовательных операций нанесения, маскирования и травления, включающих в себя прецизионные операции по настройке и т.д. Подобный подход обеспечивает лишь ограниченные возможности дальнейшего расширения и ограниченную гибкость и ведет к быстро возрастающей топологической сложности по мере увеличения количества выводов в каждой точке матрицы.

Что касается истинно трехмерных схем матричной адресации типа представленной на фиг.2, заявителю неизвестны примеры известных устройств, характеризующихся высокой плотностью и изготовленных методами массового производства. На практике схемы функциональной адресации для трехмерной матричной адресации представляют трудности для осуществления при условии одновременного обеспечения низкой сложности и хорошей совместимости с простыми и недорогими методами изготовления.

Сущность изобретения

Таким образом, главная задача, на решение которой направлено настоящее изобретение, состоит в преодолении перечисленных недостатков известных устройств путем создания базовых архитектур для адресации электронных устройств или элементов, имеющих N выводов (N>2) и физически расположенных в виде матрицы в двух или трех измерениях.

Другая задача, поставленная перед настоящим изобретением, заключается в создании простого и практичного средства для индивидуального соединения отдельного элемента с N выводами в двумерной матрице, имеющей n внешних выводов для подачи тока или напряжения, где 2≤n≤N.

Названные задачи, а также различные свойства и преимущества достигнуты в соответствии с настоящим изобретением за счет создания средства для обеспечения возможности адресации в устройстве, содержащем один или более объемных элементов, которое характеризуется тем, что содержит, по меньшей мере, три набора электропроводных линий (например, ленточных электродов) с расположением указанных ленточных электродов в каждом наборе взаимно параллельно в соответствующем двумерном плоском слое, образующем дополнительную часть указанной матрицы, при взаимно параллельном расположении слоев, в которых расположены ленточные электроды, причем набор ленточных электродов в одном из указанных слоев ориентирован под углом к проекции ленточных электродов смежных слоев на указанный слой, с результирующим взаимно неортогональным расположением наборов ленточных электродов смежных слоев. При этом указанные электроды, контактирующие с указанным участком объемного элемента, образованы взаимным пространственным наложением трех или более указанных ленточных электродов в указанных соответствующих наборах электродов, контактирующих с указанным объемным элементом, так что указанная ячейка или ячейки указанного объемного элемента расположена (расположены) в зоне взаимного наложения указанных трех или более ленточных электродов, тогда как селективная адресация ячейки производится путем приложения тока или напряжения к выбранному ленточному электроду в каждом наборе электродов одновременно или в определенной временной последовательности, определяемой заранее заданным протоколом адресации.

В предпочтительном варианте выполнения указанного средства по изобретению, по существу, параллельные ленточные электроды в наборе электродов расположены эквидистантно.

Согласно другому предпочтительному варианту средства по изобретению набор электродов в матрице развернут на заданный угол или на различные заданные углы вокруг оси, по существу, перпендикулярной матрице, относительно смежных электродных наборов для предотвращения конформного наложения каких-либо ленточных электродов в смежных электродных наборах. В этом случае желательно, чтобы все наборы электродов в матрице были взаимно развернуты на заданный угол или на различные заданные углы вокруг указанной оси для предотвращения конформного наложения каких-либо ленточных электродов в любых электродных наборах. В качестве варианта заданный угол разворота набора электродов относительно следующего смежного набора электродов может быть выбран равным 2π/m·N (т.е. 360°/m·N), где N - это количество электродов, находящихся в контакте с выводом ячейки, a m - целое число при m<N.

В целом ряде предпочтительных вариантов выполнения средства по изобретению оно содержит три набора электродов для обеспечения электрического соединения с ячейками, имеющими до трех выводов, или, альтернативно, четыре набора электродов для обеспечения электрического соединения с ячейками, имеющими до четырех выводов. Средство может также содержать три набора электродов для обеспечения электрического соединения, по меньшей мере, с двумя ячейками, имеющими до двух выводов каждая.

Количество ленточных электродов в соответствующем электродном наборе выбирается согласно изобретению с учетом количества и геометрической конфигурации ячеек в матрице таким образом, чтобы максимизировать количество адресуемых ячеек в матрице. При этом желательно, чтобы количество ленточных электродов в соответствующем электродном наборе выбиралось из условия обеспечения возможности адресации отдельной ячейки в матрице.

В варианте изобретения, соответствующем случаю, когда каждая ячейка в объемном элементе в составе матрицы снабжена, по меньшей мере, двумя выводами, представляется предпочтительным выполнить электродные слои и слой или слои, образующие объемный элемент, в виде многослойной структуры с чередующимися слоями, с возможностью контактного взаимодействия между электродом, примыкающим к поверхности, по меньшей мере, одного слоя объемного элемента, и этим слоем. В этом случае взаимное наложение между ленточными электродами в каждом электродном слое будет определять ячейку в объемном элементе, причем средство по изобретению предпочтительно содержит также диодный переход между электродом у зоны взаимного наложения электродов и ячейкой, образованной в этой зоне.

Наконец, если одна или более ячеек в составе объемного элемента содержит (содержат), по меньшей мере, одну транзисторную структуру, в соответствующем варианте средства по изобретению один электрод в, по меньшей мере, двух наборах электродов предпочтительно электрически соединяет указанные транзисторные структуры одна с другой через их выводы. Если же одна или более ячеек в составе объемного элемента содержит (содержат) более чем одну транзисторную структуру, то соответственно один электрод в, по меньшей мере, двух наборах электродов электрически соединяет указанные транзисторные структуры одну с другой через их выводы.

Устройство для хранения и/или обработки данных или приема, и/или обработки, и/или отображения сигналов по настоящему изобретению характеризуется тем, что входящие в его состав матрицы выполнены в виде стопы, так что устройство образует объемную структуру на основе стопы матриц для хранения данных, обработки данных или обработки сигналов в зависимости от функциональных свойств каждой матрицы в стопе.

В соответствии с предпочтительным вариантом изобретения предлагаемое устройство выполнено на подложке, несущей интегральные контуры, соединенные с электродами указанного средства для обеспечения выполнения функций управления, контроля и коррекции ошибок в ячейках объемных элементов матриц.

Перечень фигур чертежей

Дальнейшие особенности и достоинства предлагаемого решения станут ясны из нижеследующего подробного описания и прилагаемой формулы изобретения.

Далее будет приведено более детальное описание, относящееся к предпочтительным вариантам выполнения, которые будут рассмотрены совместно с прилагаемыми чертежами.

На фиг.1 представлена упомянутая выше известная матрица адресации с четырьмя линиями (шинами).

На фиг.2 представлена также упоминавшаяся известная ортогональная трехмерная матричная схема.

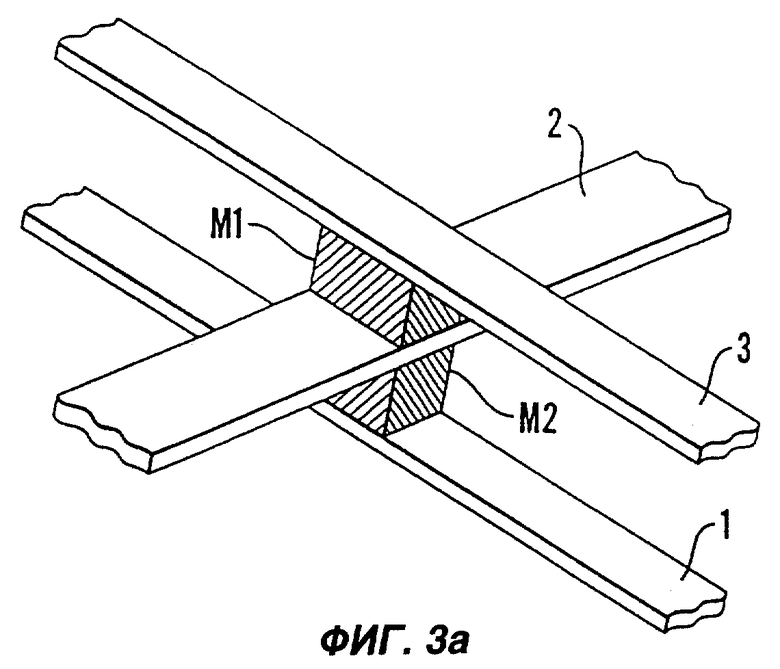

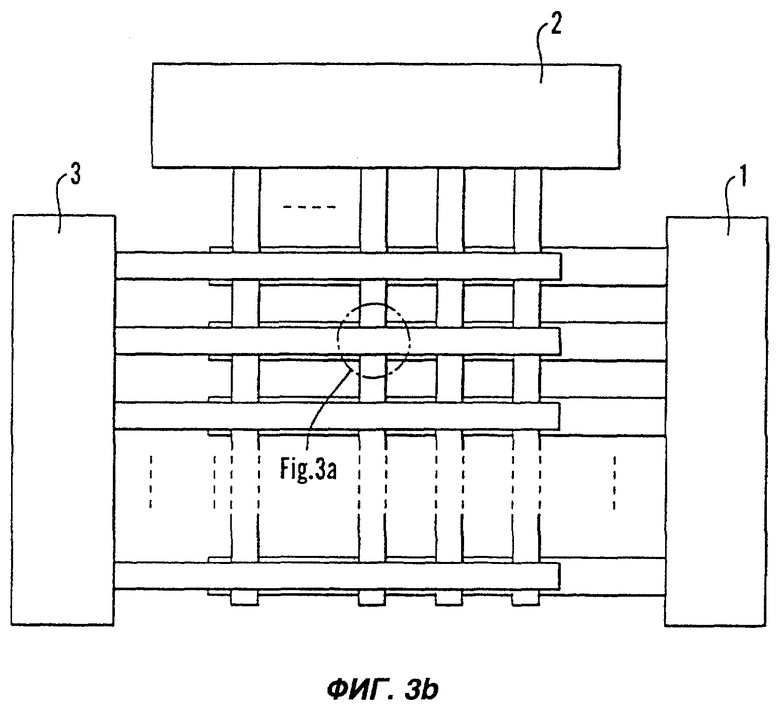

На фиг.3а, 3b представлена известная ортогональная схема матричной адресации для устройств с тремя выводами, состоящими из двух блоков, имеющих по два вывода.

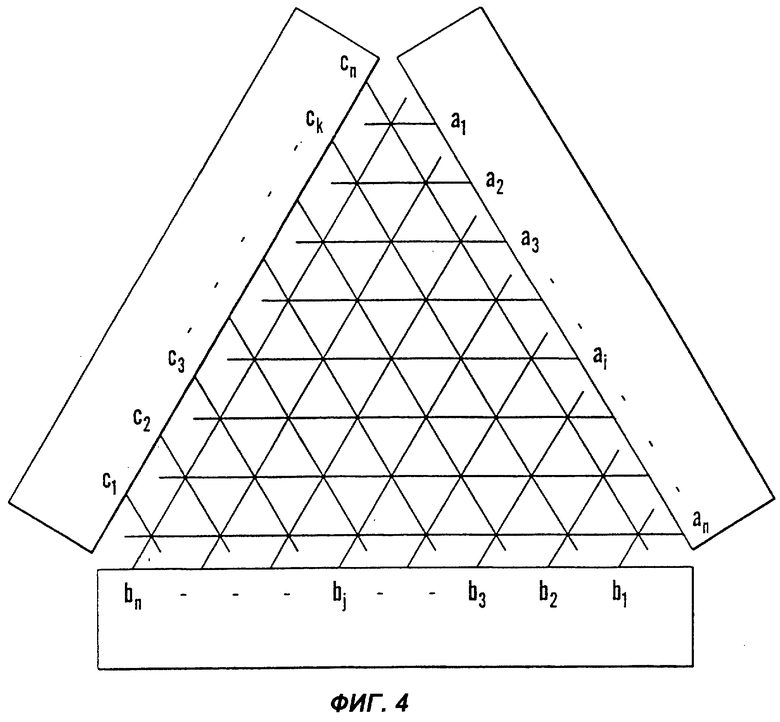

Фиг.4 иллюстрирует матрицу адресации, выполненную с использованием настоящего изобретения.

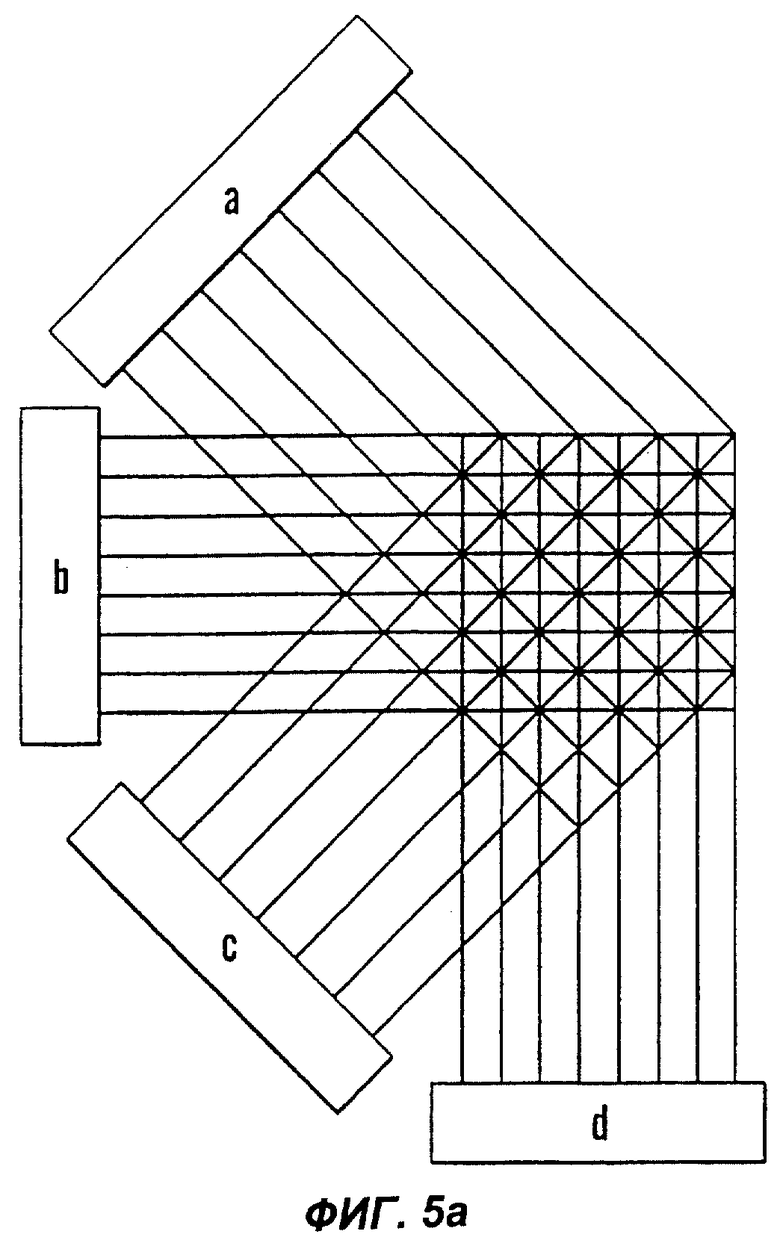

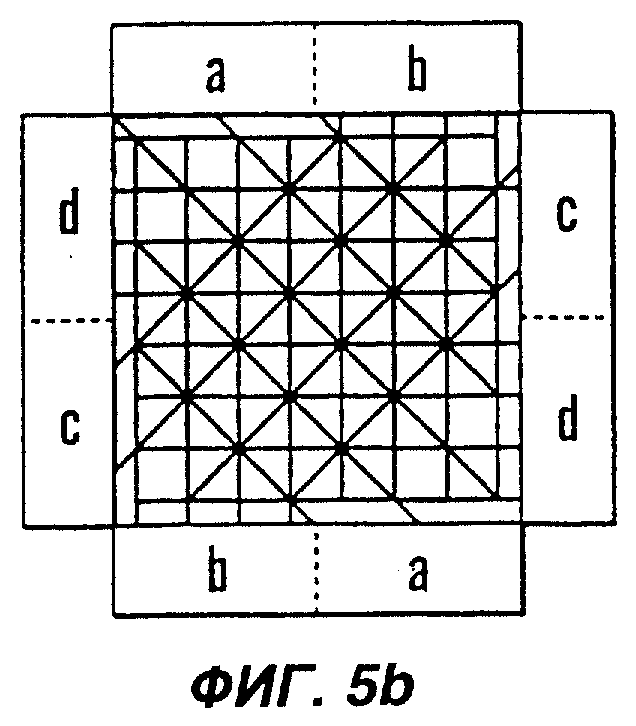

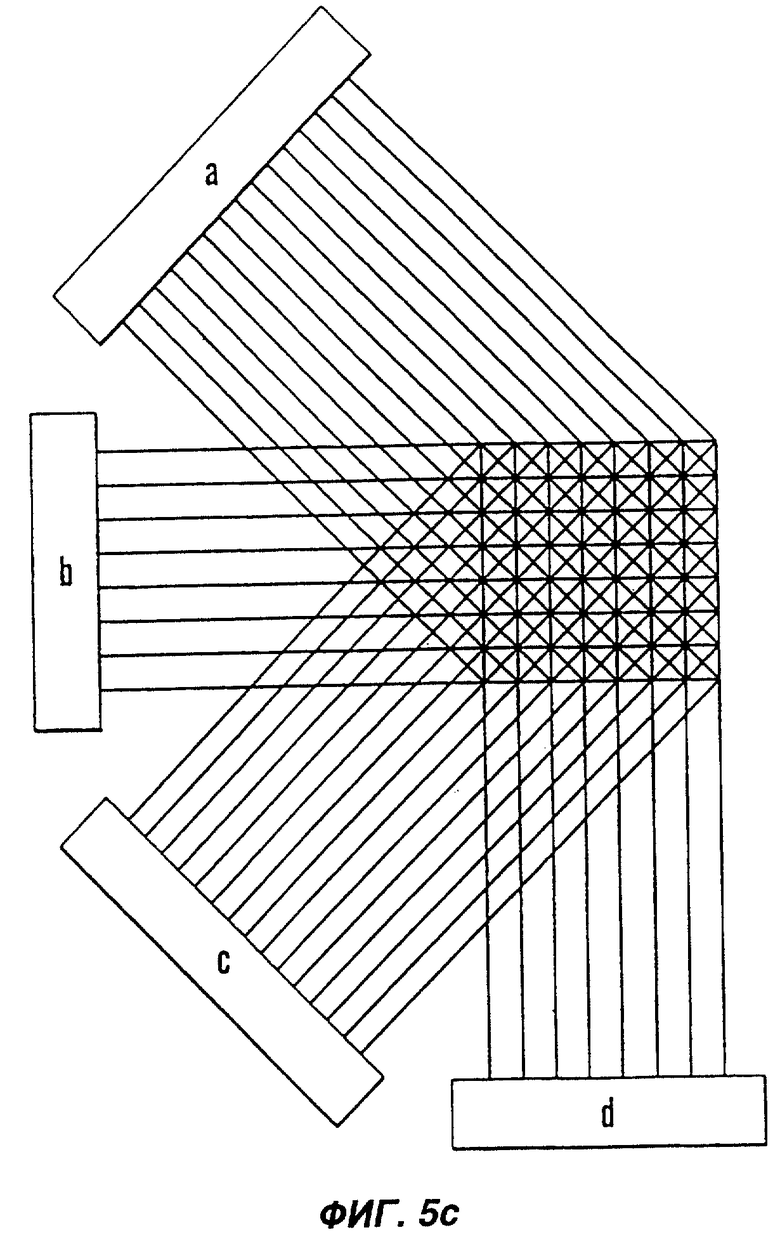

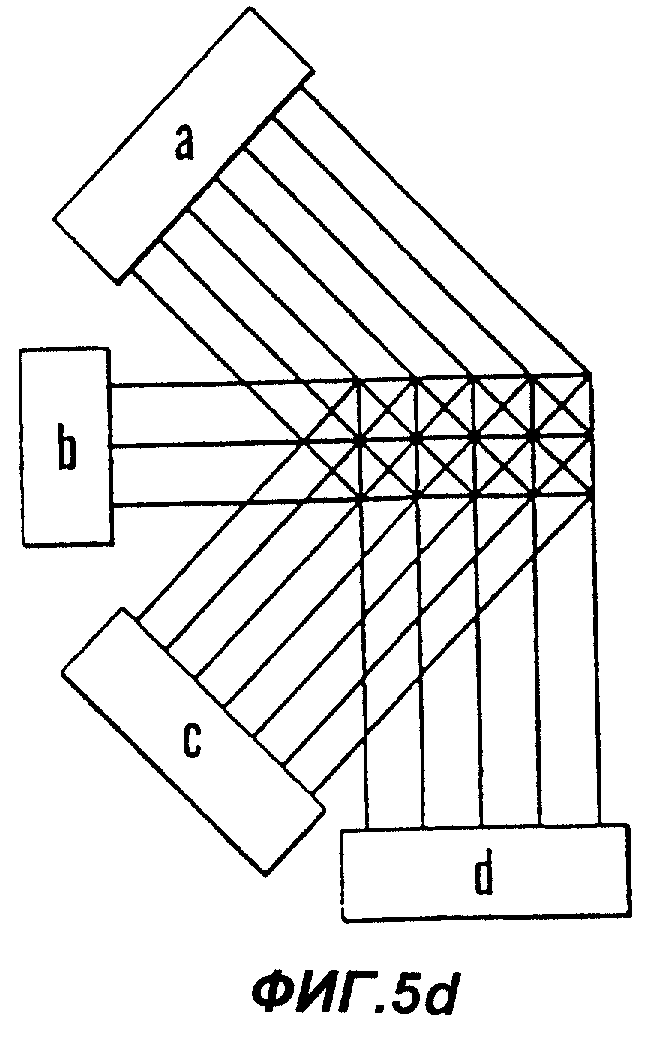

На фиг.5a-5d приведены примеры осуществления первого варианта матриц адресации.

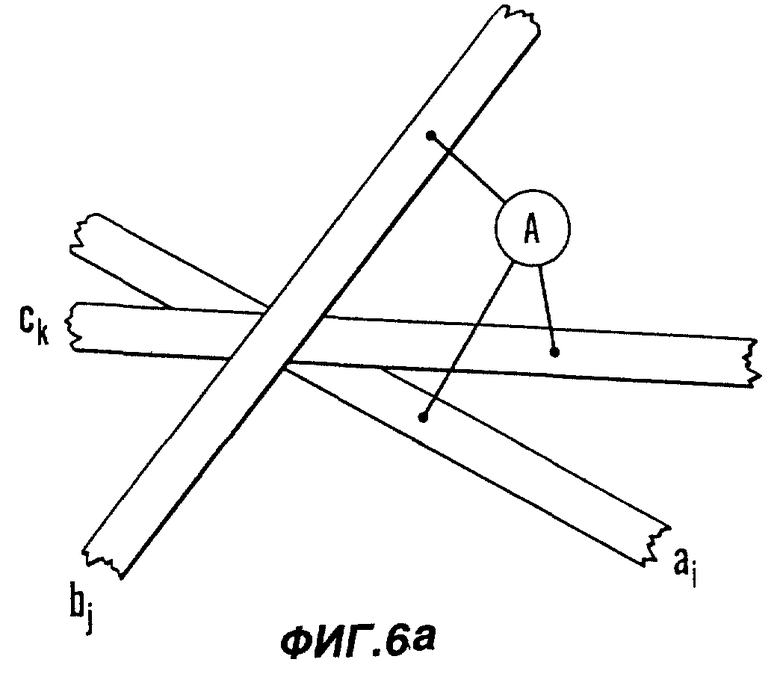

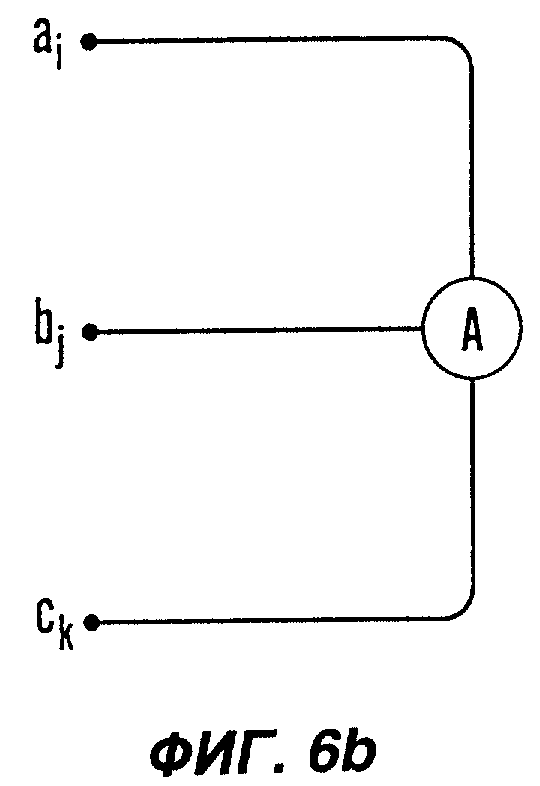

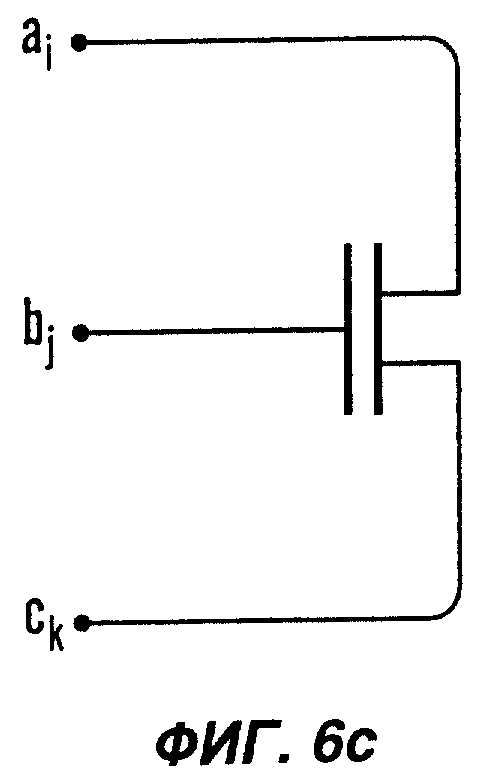

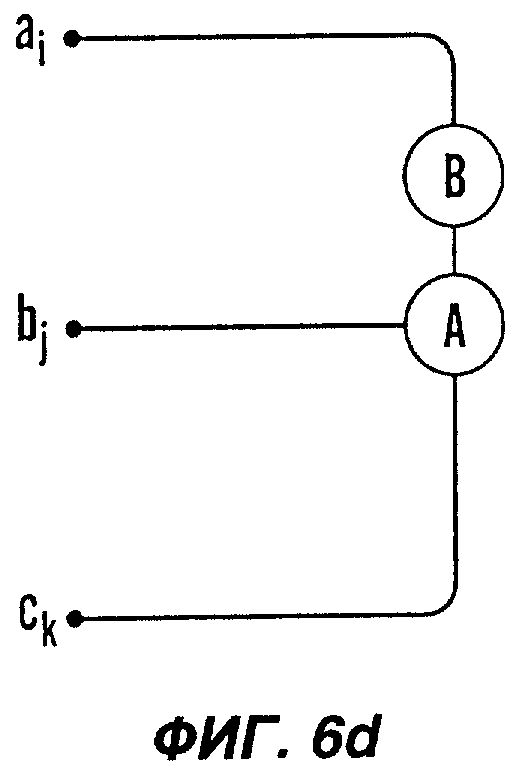

На фиг.6a-6f приведены примеры осуществления второго варианта матриц адресации.

На фиг.7а-7е приведены примеры осуществления третьего варианта матриц адресации.

На фиг.8а, 8b представлен пример выполнения предпочтительного варианта настоящего изобретения.

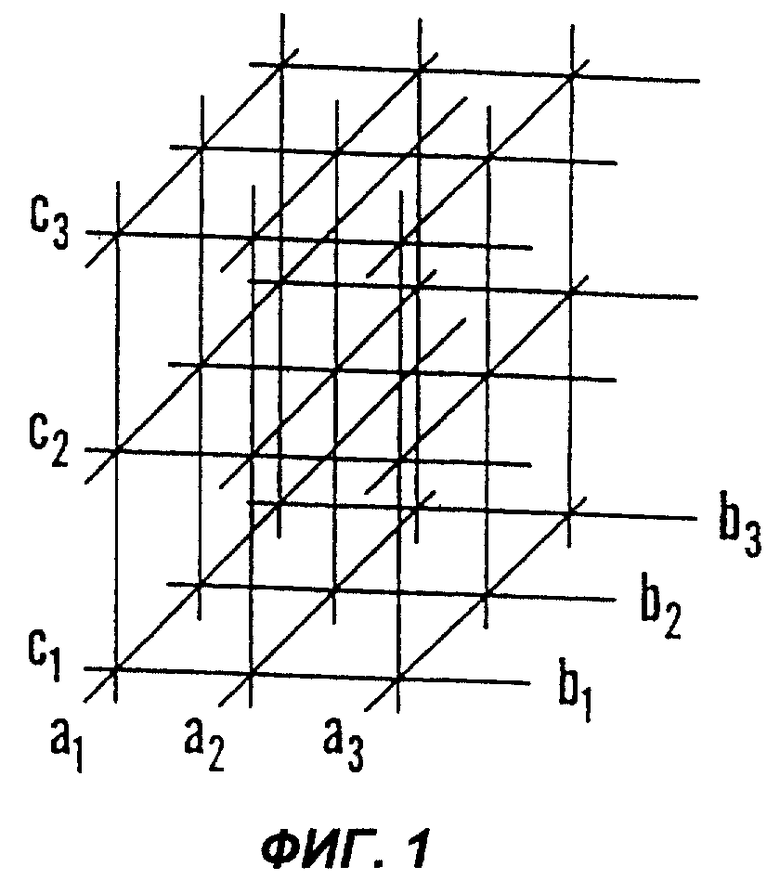

На фиг.9 представлен пример выполнения варианта изобретения, в котором элементы в матрице обладают свойствами выпрямительного диода

Сведения, подтверждающие возможность осуществления изобретения

Как уже упоминалось в одном из предыдущих разделов, на фиг.1 показана известная схема адресации для четырех ячеек памяти типа SRAM в планарной ортогональной матрице. Для осуществления обновления, записи и считывания необходимы 4 линии. Если выбраны бит и -бит, то адресация производится ко всему столбцу.

На фиг.2 показана в трех измерениях также упоминавшаяся ранее известная ортогональная схема матричной адресации элементов, имеющих по три вывода. Каждая точка наложения электродных линий задает физическую координату в матрице и может обслуживать контур или элемент с тремя выводами.

Для того чтобы наилучшим образом представить существующий уровень техники и основные идеи настоящего изобретения, далее будет кратко описано, как в принципе может осуществляться адресация в известном устройстве с тремя выводами, состоящем из блоков с двумя выводами в каждом, с использованием трех групп параллельных электродов, ориентированных ортогонально по отношению к расположенному над ними или под ними набору электродов. Однако в этой связи важно отметить, что данное устройство представляет собой простое приложение принципов известного пассивного матричного устройства с адресацией ячеек, задаваемой взаимным пространственным наложением электродов. Как следствие, оно обладает теми же недостатками, которые уже были отмечены в разделе описания, относящемся к уровню техники.

Если каждый элемент двумерного набора содержит два блока, каждый из которых имеет по два вывода, то адресация данного элемента в принципе может быть осуществлена посредством ортогональной пассивной матричной сети. Известная схема такого типа показана на фиг.3а, 3b, на которых представлены только три электродных слоя 1, 2, 3 в стопе, которая может содержать намного большее количество слоев. Два элемента, М1, М2, расположенные, как это показано на фиг.3а, между зонами взаимного наложения электродов (например, электродов 1 и 2, а также 2 и 3), могут адресоваться отдельно за счет соответствующей активации взаимно наложенных (скрещивающихся) электродов. Элемент, действительно имеющий три вывода и расположенный в зоне взаимного наложения электродов или вблизи от нее, не может быть помещен между зонами взаимного наложения электродов по варианту, показанному на фиг.3а, т.е. в виде двух раздельных сегментов. Как следствие, для него будет необходимо, по меньшей мере, одно отдельное прямое соединение с третьим электродом. Подобная ортогональная пассивная матричная адресация имеет ряд недостатков.

Как можно видеть из фиг.3b, ортогональная электродная структура требует наличия длинных параллельных дорожек (линий). Это приводит к появлению индуктивных и/или емкостных перекрестных помех между электродами в каждом втором электроде показанной стопы. Более важным является то, что структуре устройств, основанных на применении цельных (сплошных) протяженных функциональных слоев, расположенных между наборами электродов, присуще фундаментальное ограничение, обусловленное массивным наложением электродов 1 и 3 вне полезной зоны наложения, включающей в себя элемент или ячейку устройства. Более конкретно, если каждый функциональный слой является проводящим в направлении, перпендикулярном слоям, между электродами 1 и 3 существует прямой канал для тока утечки, протянувшийся по всей длине электродов от зоны заданного взаимного наложения до края матрицы. Данное ограничение является весьма серьезным и делает невозможным ряд важных применений, таких как устройства памяти с одним бистабильным запоминающим слоем (между электродами 1 и 2) и одним управляющим, или переключающим слоем (между электродами 2 и 3).

Более того, существует проблема перенасыщенности вспомогательной электроники и соединений на краях адресуемой матрицы. Сложность этой проблемы быстро возрастает с ростом количества выводов для адреса каждого элемента. Как показано на фиг.3b, эта проблема может быть слегка смягчена за счет размещения управляющей электроники для наборов электродов 1 и 3 на противоположных сторонах матрицы. Эта стратегия позволяет получить не более четырех раздельно управляемых наборов электродов, что соответствует четырехслойной стопе, вместо трехслойной стопы, показанной на фиг.3b. Однако, как уже было упомянуто, во многих случаях может быть желательно иметь стопы с большим количеством слоев.

Может также оказаться желательным, чтобы вся электроника располагалась на общей подложке, например, на кремниевой пластине. Это означает, что многослойные ортогональные матрицы типа показанной на фиг.3b потребуют наличия электродных соединений высокой плотности, имеющих большую длину для того, чтобы достичь других, неиспользуемых частей подложки. В большинстве случаев такое решение является нежелательным. Альтернативно управляющие электронные модули, принадлежащие различным наборам электродов, могут располагаться в виде стопы, друг над другом. Это влечет за собой ряд нежелательных последствий, например, необходимость применения полупроводниковых технологий другого типа (тонкопленочных транзисторов и др.), а также сложности, связанные с перекрестными помехами, необходимостью контроля температуры и технологической несовместимости при получении стопы активных контуров.

Фиг.4 иллюстрирует основные принципы реализации средства по настоящему изобретению, предназначенному, в частности, для адресации матрицы. Матрица включает в себя устройства, или ячейки с тремя выводами, размещенные в планарной конфигурации. Электродное средство, содержащее три планарных набора электродных линий (называемых также ленточными электродами или просто электродами) ai, bj и ck, показано в проекции на одну плоскость. Электродные линии в пределах каждого набора параллельны друг другу. Каждый набор электродных линий развернут на определенный угол относительно двух других наборов. При этом электроды одного набора налагаются на электроды двух других наборов (т.е. скрещиваются с ними) в общих зонах (называемых также для простоты понимания точками) наложения, в которых расположены адресуемые устройства. Хотя взаимно развернутые наборы электродов изображены лежащими в одной плоскости, в точках наложения они физически разделены и в типичном случае лежат в раздельных плоскостях. Однако данные плоскости могут лежать в непосредственной близости друг от друга, будучи разделенными тонкой профилированной пленкой или сплошной (цельной) тонкой пленкой, которая формирует объемный элемент матрицы (на фиг.4 не изображен). В рассматриваемом примере к устройствам или функциональным элементам, расположенным в точках матрицы, соответствующих наложениям электродов, имеется доступ по N=3 независимым соединениям (линиям), ведущим к краям матрицы, где электроды могут быть подсоединены к управляющим или отслеживающим контурам.

Различные электроды могут быть взаимно развернуты таким образом, чтобы образовать симметричную конфигурацию без взаимного наложения даже при больших N. Например, углы между смежными плоскостями (или слоями, или наборами) могут соответствовать 360°/mN, где N - это количество выводов, a m - целое число, меньшее или равное N. Поскольку в данной схеме ни одна пара смежных электродных наборов не является конформно налагающейся, емкостные связи будут, в основном, отсутствовать.

Важный аспект настоящего изобретения, который является отличительным по отношению к уровню техники, становится ясным при сопоставлении фиг.4 с фиг.3. Как уже было объяснено ранее, конфигурация по фиг.3 не может быть использована применительно к устройствам, изготовленным с применением сплошных функциональных слоев, которые являются проводящими в направлении, перпендикулярном слоям. Эта невозможность обусловлена значительным взаимным наложением электродов, входящих в наборы 1 и 3. Кроме того, такое взаимное наложение может привести к недопустимым индуктивным или емкостным перекрестным помехам. В неортогональном варианте, представленном на фиг.4, единственной точечной зоной (точкой) взаимного наложения трех электродов, связанных с определенным устройством, является зона (точка) их скрещивания. Очевидно, что, хотя этот принцип проиллюстрирован для конфигурации с N=3, он приложим и к неортогональным матрицам с N>3.

Далее, сравнивая истинную трехмерную матрицу известного типа, показанную на фиг.2, с матрицей адресации по настоящему изобретению, представленной на фиг.4, можно заметить, что в последнем случае элемент может быть полностью задан выбором только двух непараллельных линий. Таким образом, эксклюзивная (индивидуальная) адресация элемента в точке наложения линий ai, bj и сk обеспечивается с помощью как пар (ai, bj), (аi, ck) и (bj, ck), так и тройки (аi, bj, ck).

Каждый элемент вышеописанной матрицы связан с тремя линиями, которые могут быть электрически активированы независимо одна от другой, как попарно, так и по три. Следует заметить, что допустимые комбинации i, j, k подчиняются следующему правилу отбора:

i+j+k=2n+1, где n=imax=jmax=kmax.

Данное правило отбора применимо не только к электродным конфигурациям, образующим в проекции равносторонние треугольники, типа показанной на фиг.4, но к общему случаю электродов, образующих треугольники, которые могут иметь произвольную форму, но при наличии общих точек наложения.

Далее будут описаны примеры осуществления первого варианта адресации матриц в соответствии с изобретением. Все эти примеры предназначены для устройств или ячеек с четырьмя выводами в планарной конфигурации.

На фиг.5а и 5b показано распространение описанного принципа на случай N=4. Адресуемая матрица в обоих случаях остается одной и той же, но схема внешних соединений по фиг.5b является более компактной, чем по фиг.5а. Как можно заметить, помимо точек наложения, соответствующих четырем выводам, существуют также наложения только между двумя линиями, ориентированными под прямым углом одна к другой. Подобные двоичные наложения в принципе соответствуют потерям в плотности адресации, если матрица должна включать только адресуемые устройства или кластеры устройств с четырьмя выводами. Однако в некоторых случаях может оказаться желательным включить в одну матрицу устройства как с двумя, так и с четырьмя выводами при соответствующем увеличении плотности их расположения.

В примерах, показанных на фиг.5а и 5b, матрица адресации построена в виде квадрата с 8×8=64 элементами или устройствами. Однако, если количество линий адресации ограничено 8 для каждого электродного набора а, b, с и d, количество устройств с четырьмя выводами окажется меньшим 64. Вариант выполнения, позволяющий использование 64 подобных устройств в квадратной матрице 8×8, представлен на фиг.5с. Каждый из электродных наборов b, d включает в себя по 8 линий, соответственно параллельных рядам и столбцам матрицы. Однако наборы а, с, развернутые на 45° относительно наборов b, d, должны содержать по 15 линий для того, чтобы обеспечить доступ ко всем 64 элементам. В общем случае для матрицы р; q - количество линий, параллельных диагонали матрицы, задается выражением р+q-1, а при р=q - выражением 2р-1. Следовательно, матрица 8×8 должна иметь по 15 линий в диагональных электродных наборах. На фиг.5d показано приложение того же принципа к матрице 5×3, в которой электродные наборы а, с должны иметь по 5+3-1=7 линиям для того, чтобы сформировать 15-элементную прямоугольную матрицу с полным доступом по четырем выводам ко всем элементам.

Путем простого расширения базового принципа взаимно развернутых наборов параллельных электродов адресации могут быть получены матрицы адресации с N>4.

Далее со ссылками на фиг.6a-6f и 7а-7е будут рассмотрены примеры осуществления соответственно второго и третьего вариантов выполнения изобретения. Примерами устройств, которые могут быть включены в матрицу адресации, соответствующую настоящему изобретению, могут служить сенсорные устройства, ячейки памяти, транзисторные компоненты и контура с тремя или четырьмя выводами. Настоящее изобретение впервые обеспечивает практическую возможность построения квази-двумерных сетей, содержащих устройства подобных типов. При этом данные устройства включают в себя планарные устройства как с пассивными, так и с активными матричными характеристиками. В качестве примера класса таких устройств могут служить активные матричные дисплеи с ячейками, которые являются люминесцентными (например, светодиодными, микролазерными или газоразрядными) или модулирующими отражение/пропускание (светодиоды, элементы MEM). Кроме того, сюда, очевидно, входят и устройства памяти с архитектурой SRAM, DRAM и FRAM (в частности, SRAM-ячейка с четырьмя выводами, показанная на фиг.1). Как должно быть очевидно специалистам в данной области, возможный диапазон применений является значительно более широким, чем совокупность приведенных примеров, так что объем настоящего изобретения ни в коем случае нельзя ограничивать данными примерами.

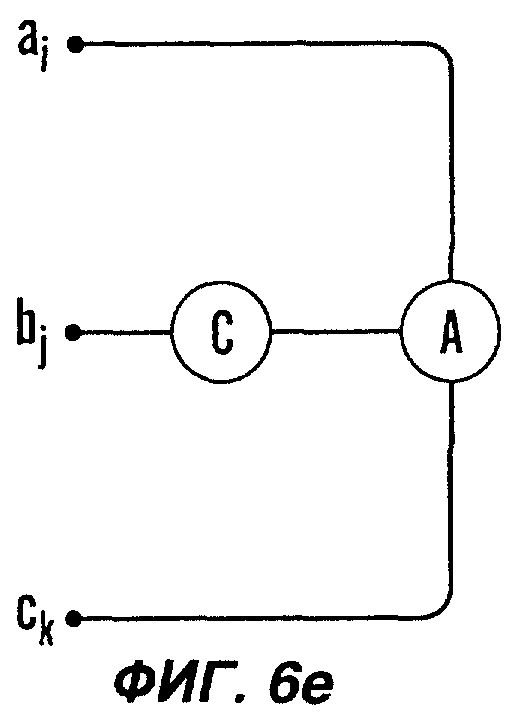

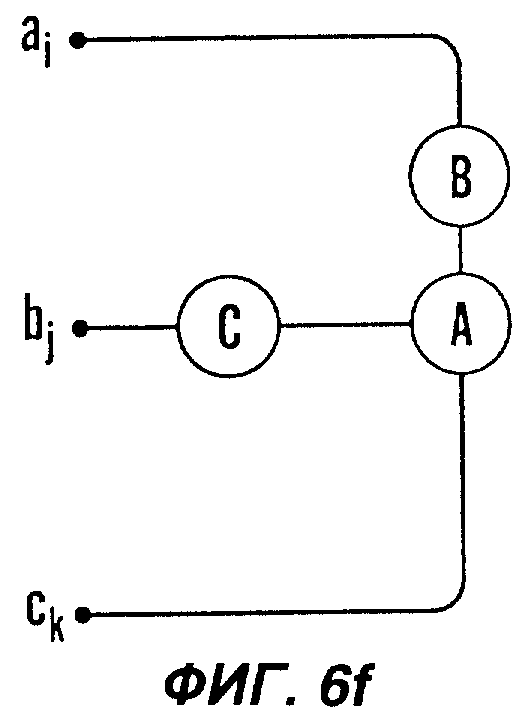

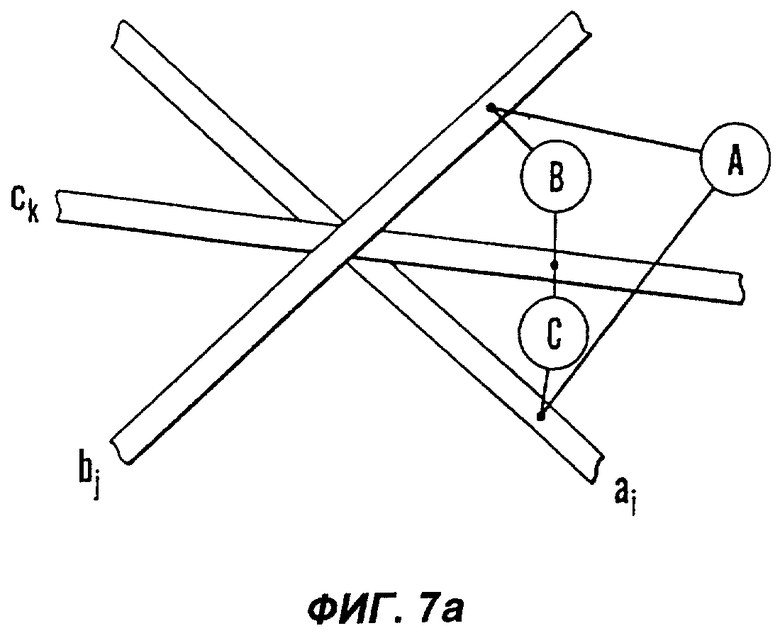

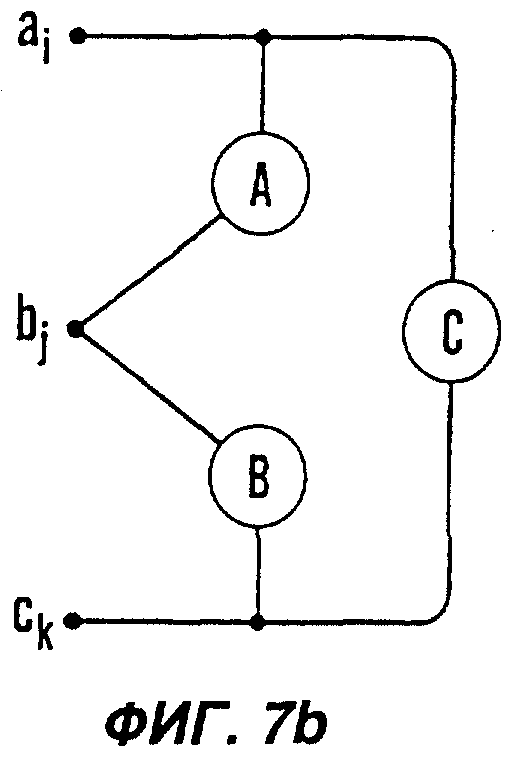

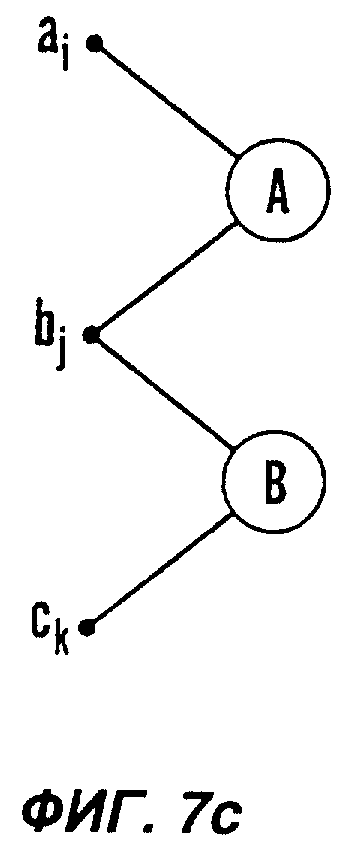

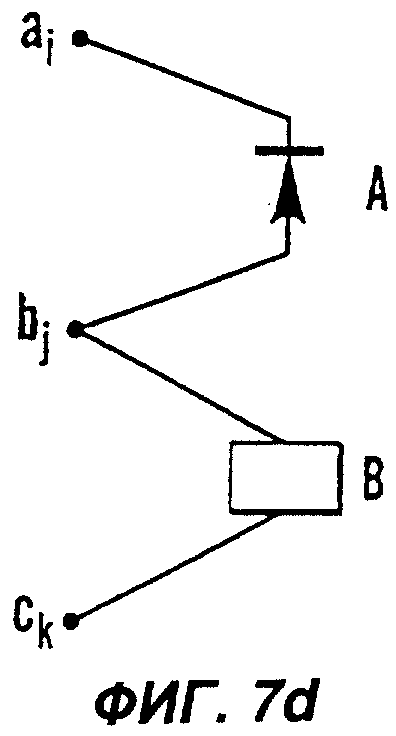

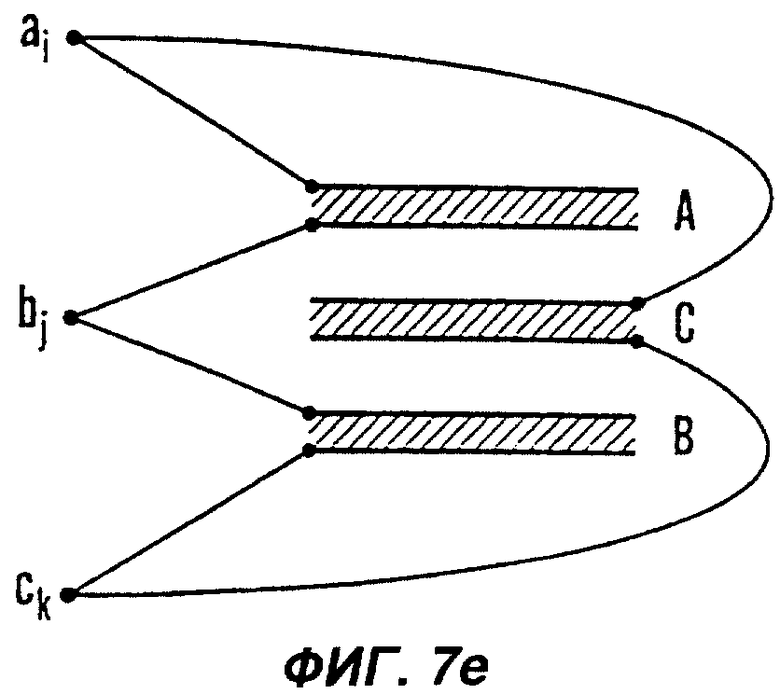

Все приведенные на фиг.6a-6f и 7а-7е примеры соответствуют количеству линий в точках наложения, составляющему N=3, т.е. трем электродным наборам согласно изобретению. Для иллюстрации адаптируемости настоящего изобретения рассматриваются два явно различных варианта. На фиг.6a-6f представлены устройства или ячейки с тремя выводами, подключенные к трем линиям в точке их наложения (матричном адресе). На фиг.7а-7е два или более устройств или ячеек с двумя выводами образуют кластеры в точке наложения (матричном адресе) с различными вариантами присоединения к трем электродам, скрещивающимся в данной точке.

В первом случае, как видно из фиг.6a-6f, устройство (или ячейка) А с тремя выводами присоединена к трем скрещивающимся электродным линиям. Фиг.6а и 6b соответствуют перспективному и схематичному изображению такого соединения. Устройство А может являться транзистором типа представленного на фиг.6с, который в типичном случае подключен к другим компонентам для выполнения набора различных заданий. Еще одним примером является светоизлучающий пиксел дисплея, показанный на фиг.6d, в котором светоизлучающий элемент В управляется транзистором А. Транзистор А, в свою очередь, управляется по электродной линии bj затвора. Еще один пример дан на фиг.6е. Здесь в линию bj затвора включен химический или физический датчик С. При аналогичном построении в других точках наложения создается двумерное сенсорное устройство или устройство формирования изображения. При совместном использовании всех компонентов А, В и С, как это показано на фиг.6f, создается двумерный дисплей, в котором пространственное распределение испускаемого света соответствует пространственному распределению интенсивности входных стимулов, поступающих на компонент С.

Во втором случае, как это показано на фиг.7а-7е, к определенному матричному адресу, т.е. к точке наложения электродных линий (аi, bj, ck) в матрице подключается до трех компонентов (или устройств) А, В и С с двумя выводами в каждом. При этом компоненты могут быть активированы независимо друг от друга, т.е. адресация одной и той же зоны взаимного наложения может быть осуществлена путем активации любой пары электродов (аi, bj), (ai, ck) или (bj, ck), как это видно из перспективного и схематичного изображений на фиг.7а, 7b.

На фиг.7с представлена схема для случая двух компонентов (или устройств) А и В с двумя выводами, которые оба расположены по одному матричному адресу (т.е. в рассматриваемом случае у точки взаимного наложения трех электродов). Конкретный вариант данной схемы, пригодный для использования в пассивной матричной памяти типа WORM (с однократной записью и многократным считыванием) или REWRITABLE (с многократной записью), приведен на фиг.7d. Здесь А и В - это выпрямительный диод и ячейка памяти соответственно. Диод А обеспечивает подавление паразитных токовых петель в схеме пассивной матричной адресации, а ячейка В может быть приведена в заданное логическое состояние, после чего это логическое состояние будет определено на операции считывания.

Применительно к одному из классов WORM-памяти В представляет собой перемычку, которая во время операции записи изменяет свое сопротивление с умеренного или низкого до высокого или бесконечного. В принципе эту операцию можно осуществить в схеме двумерной пассивной матрицы по фиг.7d и без помощи среднего электрода bj. Однако в таком случае во время операции записи через диод должен протекать сильный ток. Это накладывает ограничение на конструкцию и характеристики диода, что в общем случае ведет к снижению общей эффективности устройства. Наличие третьего электрода bj, показанного на фиг.7d, обеспечивает прямой доступ к изолированной ячейке памяти во время записи, причем он может быть отключен во время считывания. Тем самым создается возможность оптимизировать компоненты А и В независимо друг от друга. Существуют важные случаи, когда наличие третьего электрода, обеспечивающего доступ к ячейке памяти типа показанной на фиг.7d, является критичным. Например, протоколы записи/считывания/стирания для некоторых типов памяти с многократной записью предусматривают приложение к ячейке памяти напряжений, которые имеют различные полярности и уровень которых может изменяться в широких пределах. Это условие может быть выполнено в схеме пассивной матричной адресации по фиг.7d, но явно невыполнимо при удалении вывода, связанного с линией bj.

На фиг.7е представлен трехэлементный (полноцветный) пиксел в дисплее, работающем на испускание, отражение или пропускание света. На каждый элемент А, В и С могут быть поданы различные напряжения VA, VB и VC соответственно. Следует отметить, что для напряжений, прикладываемых ко всем трем электродам одновременно, должно выполняться следующее условие:

VA+VB=Vc.

Это не препятствует индивидуальному управлению элементами А, В и С, которое может быть реализовано с помощью мультиплексирования. Однако в этом случае подразумевается, что рабочий цикл электрической стимуляции каждого элемента не может в общем случае составлять 100%.

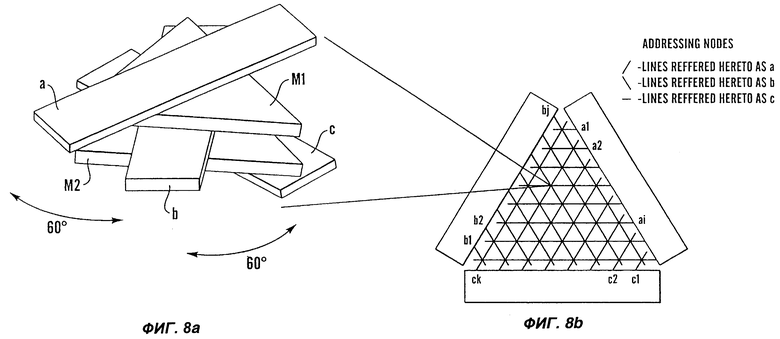

Далее будет более подробно рассмотрен предпочтительный вариант изобретения со ссылкой на фиг.8а, 8b, где представлена практическая реализация системы пассивной матричной адресации при N=3, основанной на размещении сплошных слоев функциональных материалов между тремя наборами электродов. В частности, на фиг.8а изображена единичная ячейка, расположенная в зоне наложения электродов а, b, с, функциональные материалы М1, М2 которой расположены между двумя парами электродов a, b; b, с соответственно. На фиг.8b представлена результирующая матрица, в которой ячейки с функциональными материалами М1, М2 сформированы в виде объемных элементов, задаваемых точками наложения скрещенных ленточных электродов. Во многих предпочтительных примерах выполнения материалы слоев представляют собой некристаллические материалы, которые могут быть нанесены одним из нескольких различных методов, например, центрифугированием, напылением, с помощью ракельного ножа и т.д. Последовательность операций при изготовлении следующая.

1. На подложку наносят первый электродный слой.

2. Поверх первого электрода наносят материал М1.

3. Поверх материала М1 наносят второй электродный слой.

4. Поверх второго электрода наносят материал М2.

5. Поверх материала М2 наносят третий электродный слой.

Слои материалов не должны обладать слишком высокой электропроводностью в поперечном направлении (перпендикулярном толщине пленки), чтобы исключить чрезмерные перекрестные помехи между электродами в матрице. В тех применениях, в которых слоям материала присуща некоторая конечная электропроводность, перекрестные помехи минимизируются за счет использования слоев, которые являются достаточно тонкими или в которых предусмотрены пустые участки между электродными линиями. Альтернативно могут быть сформированы слои с анизотропной проводимостью, в которых подавляются токи в поперечном направлении.

Паразитные токи представляют собой проблему, хорошо известную применительно к известным схемам пассивной матричной адресации с двумя ортогональными наборами электродов. Эта проблема, вместе с мерами по ее преодолению, в определенной степени обсуждена в трех вышеупомянутых международных заявках, принадлежащих заявителю настоящего изобретения. Данные паразитные токи обусловлены нежелательными токовыми каналами в пределах сетки электродов адресации, включающими наложения между электродами в некоторых неадресуемых точках наложения. В типичном случае подобные токи подавляются использованием элемента с нелинейным импедансом, например, выпрямительного диода, в каждой точке наложения. Та же самая мера может быть предусмотрена и в устройствах по настоящему изобретению. Это иллюстрируется фиг.9, на которой изображены устройства с тремя выводами в треугольной матрице, где каждое устройство включает в себя выпрямительный диод.

Физическая структура, представленная на фиг.8а, является полезной при создании устройств класса, который иллюстрируется фиг.7с (и включает в себя варианты по фиг.7d, 7e). В устройствах памяти типа показанного на фиг.7d диод формируется спонтанно в контактной области между электродом аi и соответственно подобранным полупроводником (например, на основе сопряженных полимеров), который образует материал М1. При этом ячейка В памяти образуется использованием в качестве материала М2, находящегося между скрещенными электродами bj и ck, соответствующего вещества со свойствами памяти. Схожие структуры могут быть применены и для построения дисплеев. В этом случае материалы М1 и М2 обладают свойством либо испускать свет при электрической стимуляции (т.е. являются, например, светоизлучающими сопряженными полимерами), либо модифицировать световой поток путем поглощения, отражения или поляризации (т.е. являются жидкими кристаллами). Естественно, что в случае дисплея с объемным элементом или элементами, когда функциональная среда полностью заключена между электродами, электрод или электроды, по меньшей мере, расположенный (расположенные) на одной стороне объемного элемента или элементов, должен (должны) быть прозрачным (прозрачными). Исключением из этого правила может являться один электрод, расположенный на противоположной стороне данной многослойной структуры.

Следует также учитывать, что материалы М1 и М2 (см. фиг.8а), вместе образующие объемный элемент, контактирующий с электродами a, b и с, могут быть сформированы в виде сплошных слоев, располагающихся по всей матрице. При этом зона, в которой происходит селективное взаимодействие с объемным элементом, будет, разумеется, располагаться между электродами, в точке (зоне) их наложения, которая таким образом задает положение ячейки в указанном объемном элементе. Однако для построения более сложных контуров типа использованных в вариантах по фиг.6f, 7b или 7е, более эффективными могут оказаться дискретные объемные элементы заданной конфигурации типа показанного на фиг.8а. В подобных случаях, по меньшей мере, часть объемного элемента должна быть отделена от других его частей, расположенных между парами электродов, и находиться в пространстве между самым верхним и самым нижним электродами в непосредственной близости от зоны их наложения. Другими словами, возможность адресации объемного элемента в зоне взаимного наложения электродов не означает, что единичная ячейка на основе объемного элемента не может быть активирована в областях, выходящих за пределы наложения всех трех электродов. Можно представить дискретный объемный элемент, формирующий ячейку в виде вертикальной транзисторной структуры, у которой электроды истока и стока образованы соответственно электродами а и с, показанными на фиг.8а, тогда как электрод b образует управляющий электрод (электрод затвора). В этом случае материалы М1 и М2 должны обладать свойствами изоляторов, тогда как полупроводниковый материал (не изображен), образующий транзисторный канал, будет располагаться от электрода а до электрода с. Таким образом, средства по изобретению могут быть использованы для реализации матриц, содержащих вертикальные структуры полевых транзисторов типа описанных в международной заявке PCT/N0 99/0013, принадлежащей заявителю настоящего изобретения.

В том случае, когда устройству, воплощающему настоящее изобретение, придана структура, схожая со структурой, описанной в вышеупомянутой международной заявке PCT/N0 98/00212, по меньшей мере, часть компонента в виде объемного элемента будет открыта в окружающее пространство. В этом случае отпадает необходимость в использовании, по меньшей мере, одного набора прозрачных электродов, что делает устройство с двумерной матрицей подобного типа весьма удобным для применения в камерах или дисплеях, как это уже упоминалось.

Когда устройства с архитектурой, схожей с описанной в уже упоминавшихся международных заявках, принадлежащих заявителю настоящего изобретения, должны использоваться только как устройства обработки и хранения данных, подобные устройства могут быть выполнены в виде многослойной стопы с образованием объемного элемента, как это представлено в данном описании. Двумерные матрицы, содержащие функциональную среду, образующую цельный протяженный (сплошной) объемный элемент матрицы, или дискретные элементы в каждой двумерной матрице, могут быть затем наложены друг на друга с образованием трехмерного устройства по настоящему изобретению с соответствующим количеством электродных наборов. Количество таких наборов, приданных каждой двумерной матрице в трехмерной стопе подобных матриц, может равняться трем или более. В том случае, если структура описанного типа представляет собой устройство хранения данных, функциональная среда в объемных элементах может представлять собой соответствующий неорганический или органический тонкопленочный материал, обладающий электронными или электрическими свойствами, придающими объемному элементу требуемую функциональность. Разумеется, может быть использована и любая подходящая комбинация подобных материалов, включая материалы, способные формировать спонтанные диодные переходы со смежным металлическим электродом, как это было описано при обсуждении уровня техники.

Функциональная среда объемного элемента для целей хранения данных может иметь в своей основе материал, обладающий требуемыми характеристиками в отношении импеданса и позволяющий задавать, определять и считывать значение импеданса при приложении напряжений к выбранным электродам с целью эксклюзивной адресации любого объемного элемента или ячейки на основе данного материала. Функциональная среда объемных элементов может быть также образована поляризующимся материалом, таким как электретный или ферроэлектрический материал, имеющий, например, вид неорганической или органической тонкой пленки. В последнем случае наиболее подходящим является сополимер типа сополимера поливинилидендифторида с трифторэтиленом (ПВДФ-ТрФЭ). Материалы данного типа являются удобными для хранения данных в пассивных адресуемых матрицах. Однако в данном случае операции записи и считывания применительно к конкретной ячейке или к объемному элементу с помощью выбранной числовой и разрядной линий (шин) могут потребовать заземления других, не выбранных числовых и разрядных шин или подачи на них соответствующего смещения. В этом случае устройства с двумя выводами для каждой ячейки, воплощающие принципы настоящего изобретения, явно являются предпочтительными.

Аналогичные соображения применимы также к активным запоминающим устройствам (устройствам памяти), в которых каждая ячейка памяти содержит, по меньшей мере, один или несколько транзисторов и, по меньшей мере, один ферроэлектрический конденсатор. В данном случае также объемный элемент или ячейка памяти подобного устройства могут быть построены в виде устройства с тремя или более выводами, воплощающего принципы настоящего изобретения.

Изобретение относится к средствам, обеспечивающим возможность адресации в устройстве, содержащем один или более объемных элементов. Техническим результатом является расширение функциональных возможностей. Средство для обеспечения возможности адресации в устройстве, содержащем один или более объемных элементов, представляющих собой ячейки памяти, ячейки дисплеев, диоды, транзисторы и/или переключающие/модулирующие элементы и образующих совместно с указанным средством часть двумерной или трехмерной матрицы в составе указанного устройства, содержит три набора электропроводных линий или ленточных электродов, образующем дополнительную часть указанной матрицы. Устройство для хранения и/или обработки данных или приема, и/или обработки, и/или отображения сигналов содержит указанное средство и более одной матрицы, причем указанные матрицы выполнены в виде стопы, расположенной на подложке, а устройство образует объемную структуру в зависимости от функциональных свойств каждой матрицы в стопе. 2 с. и 14 з.п. ф-лы, 9 ил.

| US 4287571 А, 01.09.1981 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ МАТРИЦЫ ТОНКОПЛЕНОЧНЫХ ТРАНЗИСТОРОВ ДЛЯ УПРАВЛЕНИЯ ЖИДКОКРИСТАЛЛИЧЕСКИМ ИНДИКАТОРОМ | 1990 |

|

RU1762690C |

| US 5075889 A, 24.12.1991 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

Авторы

Даты

2005-03-20—Публикация

2001-03-22—Подача