Изобретение относится к радиотехнике и может найти применение в системах радиосвязи, использующих широкополосные сигналы.

Известны системы радиосвязи с псевдослучайной перестройкой рабочей частоты (ППРЧ), описанные в монографии К.Феер "Беспроводная цифровая связь", Москва, "Радио и связь", 2000 г., стр.327-328, в монографии Р.К.Диксона "Широкополосные системы", Москва, "Связь", 1979 г., стр.29-36, недостатком которых является низкая помехоустойчивость к преднамеренным помехам.

Наиболее близким по технической сущности к заявляемому устройству является система радиосвязи с ППРЧ, описанная в монографии В.И.Борисова и др. "Помехоустойчивость систем радиосвязи с расширением спектра сигналов методом псевдослучайной перестройки рабочей частоты". Москва, "Радио и связь", 2000 г., стр.24, рис.1.7а и 1.7б, принятая за прототип.

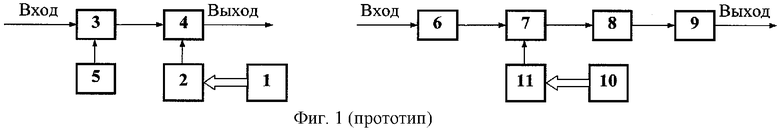

Структурная схема устройства-прототипа представлена на фиг.1, где введены следующие обозначения.

Передающая часть:

1 - первый генератор псевдослучайного кода;

2 - первый синтезатор частот;

3 - модулятор;

4 - первый перемножитель (смеситель);

5 - генератор частоты.

Приемная часть:

6 - широкополосный фильтр;

7 - второй перемножитель (смеситель);

8 - полосовой фильтр (ПФ);

9 - демодулятор;

10 - второй генератор псевдослучайного кода;

11 - второй синтезатор частот.

Устройство-прототип состоит из передающей и приемной частей.

Передающая часть содержит следующие функциональные связи: последовательно соединенные модулятор 3, первый, информационный вход которого является входом передающей части, а также входом устройства, и первый перемножитель (смеситель) 4, выход которого является выходом передающей части; выход генератора частоты 5 соединен со вторым опорным входом модулятора 3; группа выходов первого генератора псевдослучайного кода 1 шиной соединена с группой входов первого синтезатора частот 2, выход которого соединен со вторым опорным входом первого перемножителя 4.

Приемная часть содержит следующие функциональные связи: последовательно соединенные широкополосный фильтр 6, вход которого является входом приемной части, второй перемножитель (смеситель) 7, полосовой фильтр 8 и демодулятор 9, выход которого является выходом приемной части, а также выходом устройства; группа выходов второго генератора псевдослучайного кода 10 шиной соединена с группой входов второго синтезатора частот 11, выход которого соединен со вторым опорным входом второго перемножителя 7.

Устройство-прототип работает следующим образом.

С входа устройства информационные символы (цифровая информация) поступают на первый информационный вход блока 3, на второй опорный вход которого подается гармоническое колебание с выхода блока 5. В блоке 3 осуществляется модуляция гармонического колебания информационными символами. После чего напряжение с выхода блока 3 поступает на первый сигнальный вход блока 4, на второй опорный вход которого с выхода блока 2 поступает опорный сигнал, закон формирования которого определяется параллельным двоичным кодом, поступающим через шину с группы выходов блока 1 на группу входов блока 2. В блоке 4 происходит перемножение (смешение) сигналов, результат которого с выхода блока 4 подается на выход передающей части устройства.

В приемной части устройства входной сигнал фильтруется блоком 6, после чего он подается на первый сигнальный вход блока 7, на второй опорный вход которого подается сигнал с выхода блока 11, закон формирования которого определяется параллельным двоичным кодом, поступающим через шину с группы выходов блока 10 на группу входов блока 11. Сигнал на выходе блока 2 синхронен с входным сигналом приемной части, но отличается от него сдвигом всех частей программы перестройки на величину Δf, равную промежуточной частоте приемной части системы (fпр), на которую настроен блок 8. Результат перемножения (смешения) двух сигналов с выхода блока 7 поступает на вход блока 8, настроенный на частоту fпр, где он фильтруется в полосе частот ΔF, определяемой скоростью передачи информации. С выхода блока 8 отфильтрованный сигнал поступает на вход блока 9, где он демодулируется. Выделенные информационные символы с выхода блока 9 поступают на выход устройства.

Следовательно, система радиосвязи, принятая за прототип, основана на использовании периодической программы перестройки несущей частоты, что определяет возможность распознавания передаваемого сигнала и создания преднамеренных (например, имитационных помех).

Недостатком устройства-прототипа является низкая помехоустойчивость в условиях преднамеренных помех.

Для устранения указанного недостатка в систему радиосвязи, содержащую в передающей части первый синтезатор частот и модулятор, в приемной части - первый широкополосный фильтр, вход которого является входом приемной части, демодулятор и последовательно соединенные второй синтезатор частот, перемножитель и полосовой фильтр, согласно изобретению введены в передающую часть первый регистр, формирователь синхросигнала и формирователь синхроимпульсов, причем одиночный выход формирователя синхросигнала соединен со вторым опорным входом модулятора, а группа выходов формирователя синхросигнала шиной соединена с группой входов формирователя синхроимпульсов, выход которого соединен с введенным дополнительно одиночным управляющим входом первого синтезатора частот и вторым управляющим входом первого регистра, первый информационный вход которого является входом устройства, группа выходов первого регистра шиной соединена с группой информационных входов первого синтезатора частот, выход которого соединен с первым информационным входом модулятора, выход которого является выходом передающей части; введены в приемную часть - последовательно соединенные ограничитель, второй широкополосный фильтр, аналого-цифровой преобразователь, блок временного сжатия и цифроаналоговый преобразователь; последовательно соединенные амплитудный детектор, блок сравнения с порогом и второй регистр, выход которого является выходом устройства; последовательно соединенные согласованный фильтр и формирователь комбинаций информационных символов в пачке; при этом выход первого широкополосного фильтра соединен с входами ограничителя и демодулятора, выход которого соединен с входом согласованного фильтра, выход которого соединен со вторым управляющим входом блока временного сжатия и с введенным дополнительно одиночным управляющим входом второго синтезатора частот, группа информационных входов которого шиной соединена с группой выходов формирователя комбинаций информационных символов в пачке и с группой информационных входов второго регистра.

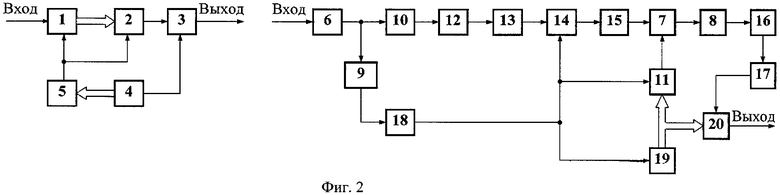

Структурная схема предлагаемого устройства представлена на фиг.2, где введены следующие обозначения.

Передающая часть:

1 - первый регистр;

2 - первый синтезатор частот;

3 - модулятор;

4 - формирователь синхросигнала;

5 - формирователь синхроимпульсов.

Приемная часть:

6, 12 - первый и второй широкополосные фильтры;

7 - перемножитель (смеситель);

8 - полосовой фильтр (ПФ);

9 - демодулятор;

10 - ограничитель;

11 - второй синтезатор частот;

13 - аналого-цифровой преобразователь (АЦП);

14 - блок временного сжатия;

15 - цифроаналоговый преобразователь (ЦАП);

16 - амплитудный детектор;

17 - блок сравнения с порогом;

18 - согласованный фильтр;

19 - формирователь комбинаций информационных символов в пачке;

20 - второй регистр.

Заявляемое устройство состоит из передающей и приемной частей.

Передающая часть содержит следующие функциональные связи: входом устройства, а также входом передающей части является первый информационный вход первого регистра 1, группа выходов которого шиной соединена с группой информационных входов первого синтезатора частот 2, выход которого соединен с первым информационным входом модулятора 3, выход которого является выходом передающей части; одиночный выход формирователя синхросигнала 4 соединен со вторым опорным входом модулятора 3, а группа выходов формирователя синхросигнала 4 шиной соединена с группой входов формирователя синхроимпульсов 5, выход которого соединен с одиночным управляющим входом первого синтезатора частот 2 и вторым управляющим входом первого регистра 1.

Приемная часть содержит следующие функциональные связи: последовательно соединенные первый широкополосный фильтр 6, вход которого является входом приемной части, ограничитель 10, второй широкополосный фильтр 12, аналого-цифровой преобразователь 13, блок временного сжатия 14, цифроаналоговый преобразователь 15, перемножитель (смеситель) 7, полосовой фильтр 8, амплитудный детектор 16, блок сравнения с порогом 17 и второй регистр 20, выход которого является выходом приемной части, а также выходом устройства; кроме того, выход первого широкополосного фильтра 6 подключен к последовательно соединенным демодулятору 9, согласованному фильтру 18 и формирователю комбинаций информационных символов в пачке 19, группа выходов которого шиной соединена с группами информационных входов второго регистра 20 и второго синтезатора частот 11, выход которого соединен со вторым опорным входом перемножителя 7; кроме этого, выход согласованного фильтра 18 соединен со вторым управляющим входом блока временного сжатия 14 и одиночным управляющим входом второго синтезатора частот 11.

Заявляемое устройство работает следующим образом.

С входа устройства информационные символы (цифровая информация) поступают на первый информационный вход блока 1 (в последовательном коде). На второй управляющий вход блока 1 поступают синхроимпульсы с выхода блока 5, формируемые следующим образом. Блок 4 формирует периодическую ПСП, которая в виде параллельного двоичного кода с группы выходов блока 4 поступает на группу входов блока 5. Блок 5 выполняет функцию дешифратора, на его выходе формируется последовательность коротких синхроимпульсов с периодом повторения, равным:

T=N·τи,

где N - число информационных символов, записываемых в блок 1;

τи - длительность информационного символа.

В блоке 1 формируется параллельный двоичный код из N информационных символов, который через шину из N проводов подается на группу информационных входов блока 2, на одиночный управляющий вход 1 которого поступают синхроимпульсы с выхода блока 5, под управлением которых происходит запись информации в блок 2. Записанные в блок 2 информационные символы определяют закон чередования частот на временном интервале Т на выходе блока 2. При записи пачки из N информационных символов в блок 2 на его выходе в течение временного интервала Т формируется сигнал ППРЧ. Таким образом, закон чередования частот на выходе блока 2 в течение временного интервала Т определяется комбинацией информационных символов в пачке из N информационных символов, записанных в данный момент в блок 2. Сигнал с ППРЧ с выхода блока 2 поступает на первый информационный вход блока 3, на второй опорный вход которого подается псевдослучайная последовательность (ПСП) в виде последовательного кода с одиночного выхода блока 4. В блоке 3 осуществляется модуляция (например, амплитудная) сигнала со случайной перестройкой рабочей частоты периодической ПСП, результат которой с выхода блока 3 подается на выход передающей части устройства.

В приемной части устройства входной сигнал фильтруется в блоке 6, ограничивается по амплитуде в блоке 10, после чего повторно фильтруется в блоке 12. Полоса пропускания блоков 6 и 12 согласовывается со спектром пачек радиоимпульсов на выходе блока 3. Радиоимпульсы постоянной амплитуды, частоты заполнения которых меняются по случайному закону, с выхода блока 12 подаются на вход блока 13, где они переводятся в цифровую форму. Цифровой сигнал с выхода блока 13 поступает на первый сигнальный вход блока 14, на второй управляющий вход которого подается сигнал с выхода блока 18. В блоке 14 цифровой сигнал сжимается в М раз (где М - число возможных комбинаций двоичных символов в пачке). Сжатый во времени сигнал с выхода блока 14 поступает на вход блока 15, где он переводится в аналоговую форму, и с выхода блока 15 подается на первый сигнальный вход блока 7, на второй опорный вход которого поступает сигнал с выхода блока 11. Блок 11 работает в сжатом в М раз масштабе времени за счет того, что его тактовая частота выбирается в М раз выше тактовой частоты блока 2. На выходе блока 11 формируется опорный сигнал, представляющий собой последовательность пачек радиоимпульсов длительностью ТЗ/М, где ТЗ=Т - время задержки цифрового сигнала в блоке 14. Пачки радиоимпульсов отличаются между собой порядком чередования частот заполнения. Ансамбль частот заполнения радиоимпульсов, формируемых блоками 2 и 11, отличается сдвигом всех частот на величину Δf, равную промежуточной частоте приемника - частоте настройки блока 8. Таким образом, за счет сжатия в блоке 14 входного сигнала в М раз на его выходе на временном интервале ТЗ формируется М копий записанного сигнала с длительностью каждой копии, равной ТЗ/М. В блоке 7 выполняется последовательное во времени перемножение каждой из М копий сжатого во времени сигнала, поступающего на его первый сигнальный вход с выхода блока 15, с одним из М опорных сигналов длительностью ТЗ/М, формируемых блоком 11 и поступающих на второй опорный вход блока 7 с выхода блока 11. Результат перемножения с выхода блока 7 подается на вход блока 8, где он фильтруется. Результат фильтрации с выхода блока 8 подается на вход блока 16, где за счет амплитудного детектирования выделяется его огибающая, которая поступает на вход блока 17, где она сравнивается с порогом. Порог в блоке 17 выбирается таким образом, чтобы его превышение с высокой вероятностью достигалось при свертке результатов перемножения входного и опорного сигналов в блоке 7, то есть при совпадении одной из копий входного сигнала с одним из опорных сигналов. Полоса пропускания блока 8 согласуется с длительностью свернутой копии. При превышении порога блок 17 формирует сигнал логической единицы, который подается на одиночный управляющий вход блока 20. По этой команде записанные в блоке 20 двоичные символы списываются с его выхода в последовательном коде на выход устройства. Блоки 14, 11 и 19 синхронизируются синхроимпульсами, поступающими от блока 18. Формирование синхроимпульсов происходит следующим образом. Входной сигнал после фильтрации в блоке 6 поступает на блок 9, где за счет его демодуляции (например, амплитудного детектирования) выделяется синхропоследовательность, которая подается на вход блока 18, где осуществляется ее согласованная фильтрация (свертка сигнала), результат которой подается на вход блока 19, второй управляющий вход блока 14 и одиночный управляющий вход блока 11. Блок 19 поочередно формирует комбинации из N двоичных символов, которые подаются с группы выходов блока 19 на группы информационных входов блоков 11 и 20.

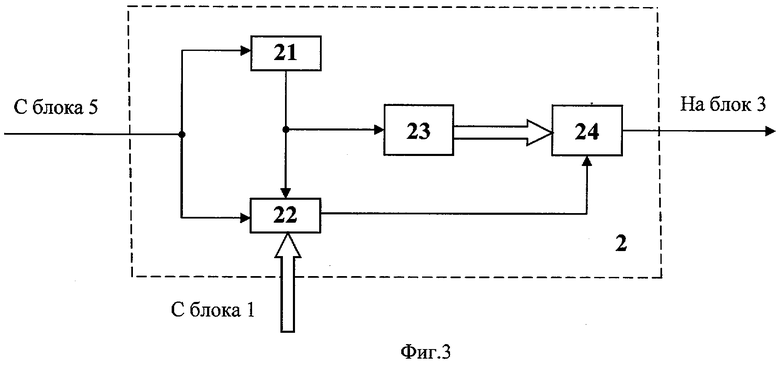

Функциональная схема первого синтезатора частот 2 приведена на фиг.3, где введены следующие обозначения:

21 - управляемый генератор тактовых частот;

22 - генератор числовой последовательности;

23 - генератор сетки частот;

24 - цифровой коммутатор.

Первый синтезатор частот 2 содержит последовательно соединенные управляемый генератор тактовых частот 21, генератор числовой последовательности 22 и цифровой коммутатор 24, выход которого является выходом первого синтезатора частот 2. Вход управляемого генератора тактовых частот 21, соединенный со вторым одиночным входом генератора числовой последовательности 22, является также и одиночным управляющим входом первого синтезатора частот 2, группа информационных входов которого является группой информационных входов генератора числовой последовательности 22, первый одиночный вход которого соединен с входом генератора сетки частот 23, группа выходов которого шиной соединена с группой информационных входов цифрового коммутатора 24.

Первый синтезатор частот 2 работает следующим образом.

С одиночного управляющего входа блока 2 на вход блока 21 подаются синхроимпульсы, под управлением которых блок 21 вырабатывает тактовые импульсы для синхронизации блоков 22 и 23. Кроме того, с одиночного управляющего входа блока 2 синхроимпульсы подаются на второй одиночный вход блока 22, на группу входов которого подаются информационные символы с группы информационных входов блока 2. При поступлении каждого синхроимпульса очередная пачка из N информационных символов (одна из М пачек) записывается в блок 22. Разрядность блока 22 выбирается равной N. При записи в блок 22 N двоичных символов осуществляется его принудительная установка, при этом блок 22 обеспечивает формирование чисел от 1 до L, где L=(2N-1). Блок 23 вырабатывает сетку гармонических сигналов, которые подаются на группу информационных входов блока 24, на одиночный управляющий вход которого подается цифровой код от блока 22. Блок 24 ставит в соответствие каждому числу заранее определенный сигнал сетки частот и именно этот сигнал пропускает на выход блока 2. Смена пачки из N двоичных символов на первом информационном входе блока 22 осуществляется через временные интервалы T=N·τи. Порядок чередования частот на выходе блока 24 зависит от комбинаций информационных символов, записываемых в блок 22. Число различных порядков чередования частот на выходе блока 2 определяется числом М возможных комбинаций из N двоичных символов.

Структура блока 11 и его работа аналогична структуре и работе блока 2, при этом единственным отличием является то обстоятельство, что на группу его информационных входов поступает не информация, а двоичные символы, формируемые блоком 19, имитирующие возможные сочетания двоичных символов в пачках.

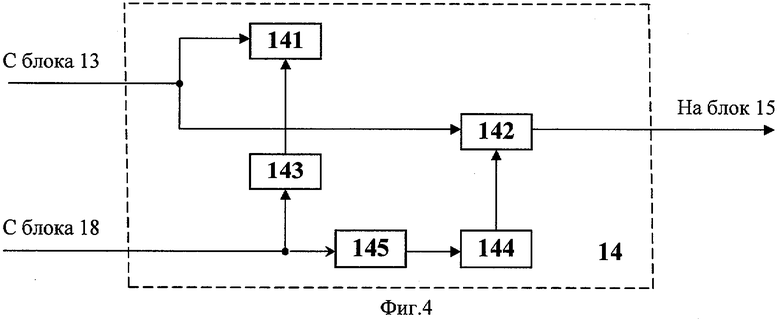

Функциональная схема блока временного сжатия 14 приведена на фиг.4, где введены следующие обозначения:

141 и 142 - первый и второй оперативно-запоминающие блоки (ОЗБ);

143 и 144 - первый и второй генераторы тактовой частоты;

145 - инвертор.

Блок временного сжатия (БВС) 14 содержит первый 141 и второй 142 оперативно-запоминающие блоки (ОЗБ), объединенные входы которых являются первым сигнальным входом БВС 14, а объединенные выходы - выходом БВС 14. Второй управляющий вход первого ОЗБ 141 соединен с выходом первого генератора тактовой частоты 143, вход которого является вторым управляющим входом БВС 14, соединенным с входом инвертора 145, выход которого через второй генератор тактовой частоты 144 соединен со вторым управляющим входом второго оперативно-запоминающего блока 142.

Блок временного сжатия 14 работает следующим образом.

Блок 14 выполняет функции оперативно-запоминающего устройства, работающего в двухтактном режиме работы. Необходимые тактовые импульсы, обеспечивающие запись и считывание информации, формируются в блоках 143 и 144. Но так как на вход блока 144 поступает сигнал, проинветртированный блоком 145, выходные сигналы блоков 143 и 144 имеют разные логические уровни (например, если на выходе блока 143 лог. "1", то на выходе блока 144 - лог. "0") и, следовательно, когда в блоке 141 осуществляется процедура записи сигнала, то в блоке 142 - процедура считывания записанного ранее в нем сигнала. При этом тактовая частота считывания выбирается в М раз выше частоты записи. На следующем цикле в блоке 142 осуществляется процедура записи сигнала, а в блоке 141 - считывания, при этом на интервале Т при считывании формируется М идентичных копий записанного сигнала.

Оперативно-запоминающие блоки строятся на основе применения RS-триггеров, спроектированных специально для работы с синхронизацией (Б.Соучек. "Микропроцессоры и микроЭВМ": перевод с английского, под ред. А.И.Петренко, Москва, "Сов. радио", 1979 г., стр.31, рис.2.10).

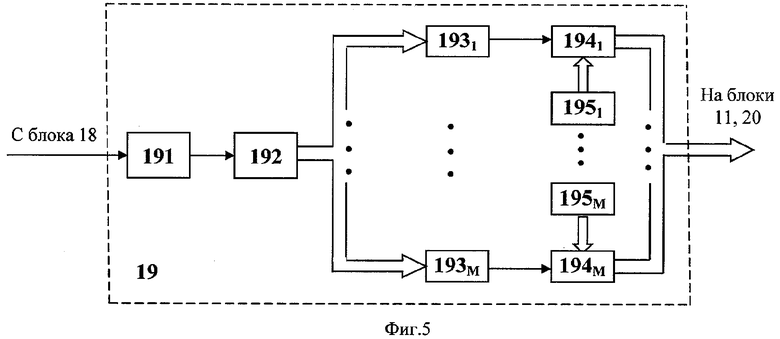

Функциональная схема формирователя комбинаций информационных символов в пачке 19 приведена на фиг.5, где введены следующие обозначения:

191 - генератор тактовых импульсов;

192 - счетчик;

1931,..., 193м - первый,..., М-ый дешифраторы;

1941,..., 194м - первый,..., М-ый коммутаторы;

1951,..., 195м - первый,..., М-ый запоминающие блоки.

Формирователь комбинаций информационных символов в пачке 19 содержит последовательно соединенные генератор тактовых импульсов 191, вход которого является входом формирователя информационных символов в пачке 19, и счетчик 192, группа выходов которого шиной соединена с объединенными между собой соответственно группами входов М дешифраторов 1931-193м, выходы каждого из которых соединены с одиночными управляющими входами соответствующих М коммутаторов. 1941-194м, группы входов которых шинами соединены с группами выходов соответствующих М запоминающих блоков 1951-195м; выходы М коммутаторов 1941-194м, шиной соединенные между собой соответственно, образуют группу выходов формирователя комбинаций информационных символов в пачке 19.

Блок 19 работает следующим образом.

В каждом из М блоков 1951-195м записана одна из М комбинаций двоичных символов в пачке из N двоичных символов. Записанные комбинации подаются в параллельном коде на выход блока 19 через соответствующие блоки 1941-194м, которые поочередно открываются при поступлении на их одиночные управляющие входы управляющих сигналов от соответствующих блоков 1931-193м, формирование которых осуществляется следующим образом. Блок 191 формирует тактовые импульсы, синхронные с синхроимпульсами, формируемыми блоком 4 (см. фиг.2). Синхронизация блока 19 осуществляется за счет подачи на его вход с выхода блока 18 синхроимпульсов. Тактовая частота fТ1, формируемая блоком 191, определяемая соотношением:

поступает на блок 192, представляющий собой счетчик на М. После подсчета М тактовых импульсов он сбрасывается и начинает следующий цикл. Все М состояний счетчика дешифрируются поочередно в блоках 1931-193м, формируя управляющие сигналы для блоков 1941-194м, которые обеспечивают периодическое поочередное прохождение сигналов с выходов одного из соответствующих блоков 1951-195м на выход устройства.

Поочередность отпирания блоков 1941-194м достигается следующим образом. Блок 192 формирует двоичные числа от 1 до М, каждое из которых соответствует одному из десятичных чисел. Так, двоичное число 1 соответствует десятичному числу 10, двоичное число 10 - десятичному числу 2, двоичное число 11 - десятичному числу 3 и т.д. (Б.Соучек. "Микропроцессоры и микроЭВМ": перевод с английского, под ред. А.И.Петренко, Москва, "Сов. радио", 1979 г., стр.17, таблица 13). В зависимости от состояния своих входов каждый из блоков 1931-193м формирует на своем выходе сигнал уровня логической "1", который отпирает соответствующий блок 1941-194м.

Блок 3 может быть выполнен, например, как амплитудный модулятор, в этом случае блок 9 может быть выполнен как амплитудный детектор.

Блок 4 может быть реализован как генератор ПСП с N параллельными выходами.

Реализация остальных блоков не вызывает сомнений, так как они широко опубликованы в научно-технической литературе.

Таким образом, в заявляемой системе радиосвязи закон перестройки рабочей частоты является случайным, так как он определяется случайными комбинациями информационных символов в пачках, что исключает возможность определения закона перестройки частоты и создания эффективных преднамеренных помех.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 2002 |

|

RU2210860C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МОДУЛЯЦИИ, СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ, МАШИНОЧИТАЕМЫЙ НОСИТЕЛЬ И ПРИМЕНЕНИЕ СПОСОБА ДЛЯ СИНХРОНИЗАЦИИ ПРИЕМА СИГНАЛОВ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МОДУЛЯЦИИ | 2005 |

|

RU2286025C1 |

| Устройство для передачи и приема многопозиционных широкополосных сигналов | 1986 |

|

SU1345361A1 |

| ГИДРОАКУСТИЧЕСКАЯ СИСТЕМА ПОДВОДНОЙ СВЯЗИ | 2015 |

|

RU2597685C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| УСТРОЙСТВО ПРИЕМОПЕРЕДАЧИ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1985 |

|

SU1840078A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| АППАРАТУРА ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ И АНАЛОГОВОЙ ИНФОРМАЦИИ | 2001 |

|

RU2192093C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| СПОСОБ ПЕРЕДАЧИ КОМАНД РАДИОУПРАВЛЕНИЯ СИГНАЛАМИ С РАСШИРЕННЫМ СПЕКТРОМ | 2021 |

|

RU2778439C1 |

Изобретение относится к радиотехнике и может найти применение в системах радиосвязи с перестройкой рабочей частоты. Технический результат - повышение помехоустойчивости к воздействию преднамеренных помех. Для этого в передающую часть известной системы радиосвязи введены первый регистр, формирователь синхросигнала и формирователь синхроимпульсов, а в приемную часть - ограничитель, второй широкополосный фильтр, аналого-цифровой преобразователь, блок временного сжатия, цифроаналоговый преобразователь, согласованный фильтр, амплитудный детектор, блок сравнения с порогом, второй регистр и формирователь комбинаций информационных символов в пачке. 5 ил.

Система радиосвязи, содержащая в передающей части первый синтезатор частот и модулятор, в приемной части - первый широкополосный фильтр, вход которого является входом приемной части, демодулятор и последовательно соединенные второй синтезатор частот, перемножитель и полосовой фильтр, отличающаяся тем, что введены в передающую часть первый регистр, формирователь синхросигнала и формирователь синхроимпульсов, причем одиночный выход формирователя синхросигнала соединен со вторым, опорным входом модулятора, а группа выходов формирователя синхросигнала шиной соединена с группой входов формирователя синхроимпульсов, выход которого соединен с введенным дополнительно одиночным управляющим входом первого синтезатора частот и вторым, управляющим входом первого регистра, первый, информационный вход которого является входом устройства, группа выходов первого регистра шиной соединена с группой информационных входов первого синтезатора частот, выход которого соединен с первым, информационным входом модулятора, выход которого является выходом передающей части; введены в приемную часть последовательно соединенные ограничитель, второй широкополосный фильтр, аналого-цифровой преобразователь, блок временного сжатия и цифроаналоговый преобразователь; последовательно соединенные амплитудный детектор, блок сравнения с порогом и второй регистр, выход которого является выходом устройства; последовательно соединенные согласованный фильтр и формирователь комбинаций информационных символов в пачке; при этом выход первого широкополосного фильтра соединен с входами ограничителя и демодулятора, выход которого соединен с входом согласованного фильтра, выход которого соединен со вторым, управляющим входом блока временного сжатия и с введенным дополнительно одиночным управляющим входом второго синтезатора частот, группа информационных входов которого шиной соединена с группой выходов формирователя комбинаций информационных символов в пачке и с группой информационных входов второго регистра.

| БОРИСОВ В.И | |||

| и др | |||

| Помехоустойчивость систем радиосвязи с расширением спектра сигналов методом псевдослучайной перестройки рабочей частоты, Москва, Радио и связь, 2000, стр.24, рис.1.7а, 1.7б | |||

| RU 2002376 С1, 30.10.1993 | |||

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| RU 94002883 A1, 20.04.1996 | |||

| US 4653087 A, 24.03.1987 | |||

| US 5361401 A, 01.11.1994. | |||

Авторы

Даты

2007-03-27—Публикация

2005-10-24—Подача