Изобретение относится к многоканальной радиорелейной связи, может найти применение при построении систем передачи дискретной информации. и является усовершенствованием изобретения по авт. св. № 1262741.

Целью изобретения является повышение помехоустойчивости за счет снижения влияния фазовых дрожаний тактовых импульсов.

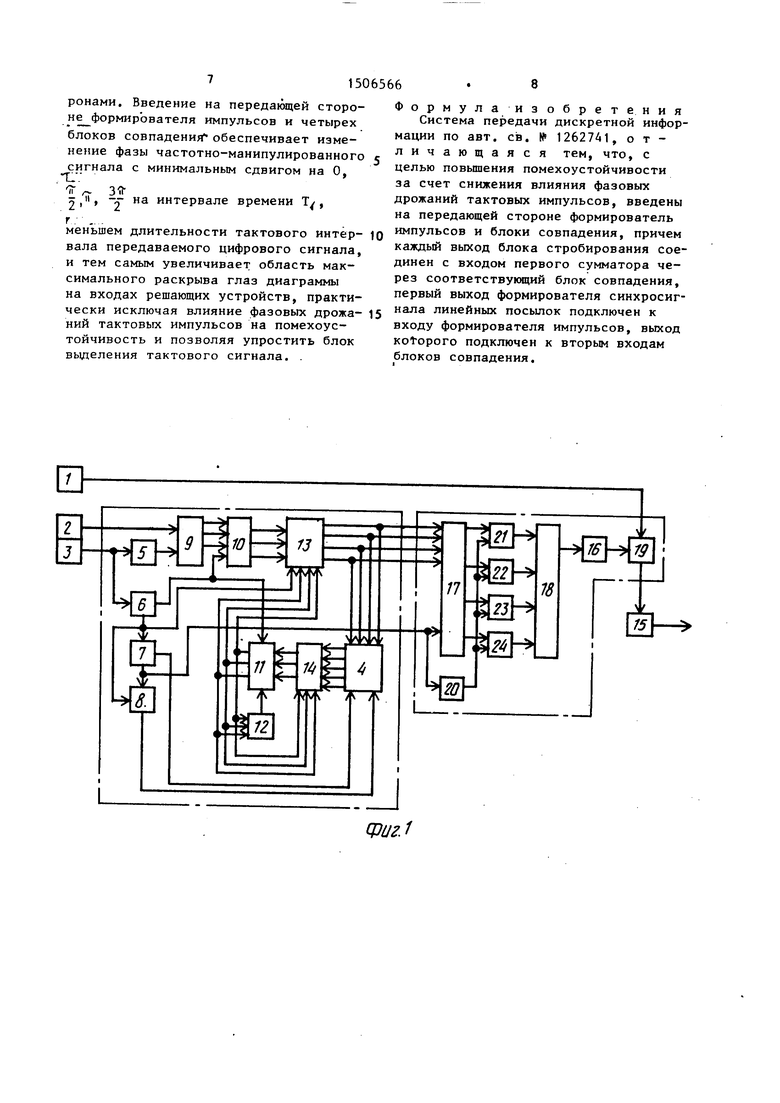

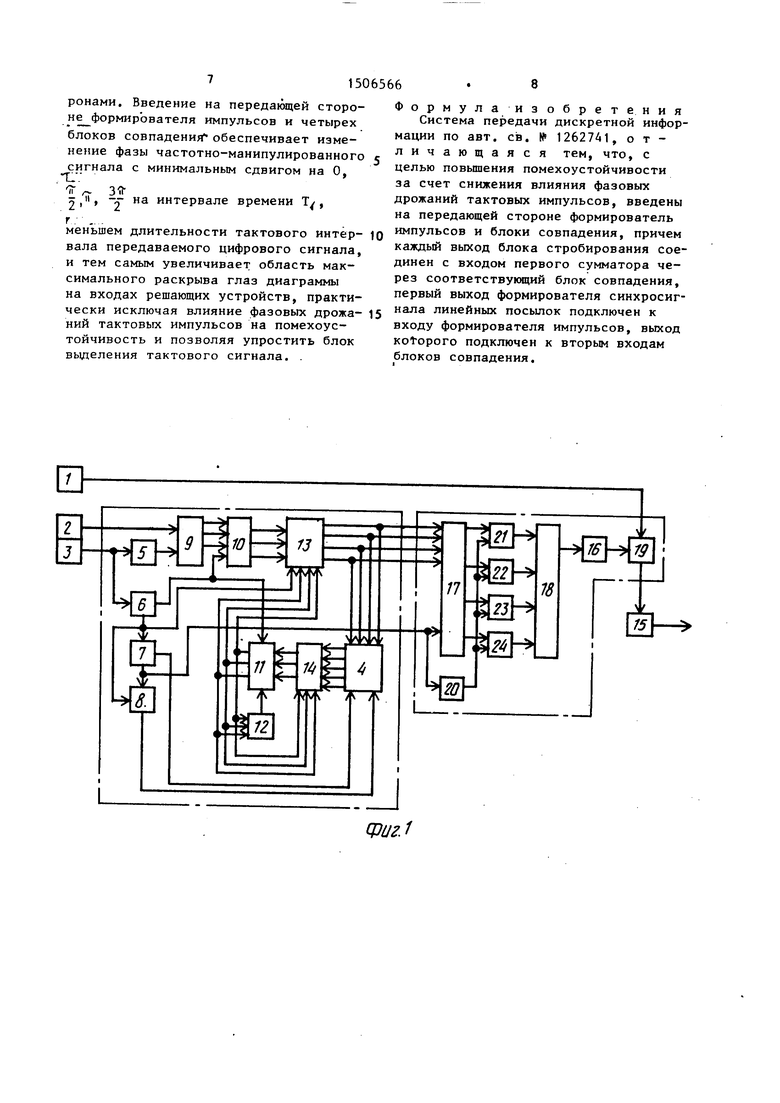

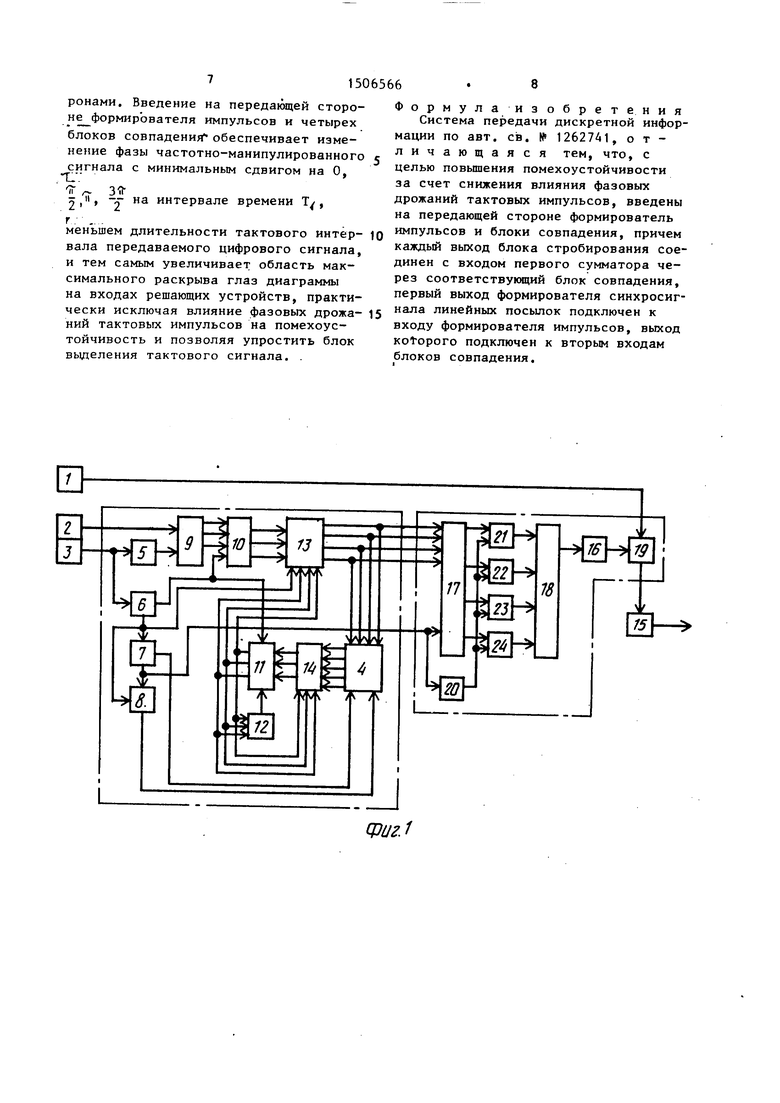

На фиг.1 изображена структурно- электрическая схема передающей стороны системы; на фиг.2 - то же, приемной стороны системы.

Система содержит на передающей стороне источник 1 сигналов служебной связи, источник 2 дискретной информации, блок 3 синхронизации, первый счетчик 4, инвертор 5, формирователь 6 синхросигнала кодовых групп,

формирователь 7 синхросигнала линейных посылок, блок В сдвига, последо- вательньш регистр 9, параллельный регистр 10, блок 11 памяти, блок 12 запрета, преобразователь 13 основания кода, второй счетчик 14, частотный модулятор 15, фильтр 16 верхних частот, блок 17 стробирования, первый сумматор 18, второй сумматор 19, формирователь 20 импульсов и блоки 21- 24 совпадения, а на приемной сторо . не - приемник 25 сигналов служебной связи, приемник 26 дискретной информации, формирователь 27 двоичного с сигнала, блок 28 восстановления гра- ниц информационных посылок, усилитель 29 промежуточной частоты, корреляци- онный приемник 30, обратный преобразователь 31 основания кода, первый решающий блок 32, второй решающий

У

:л

1Ч

31506

блок 33, блок 34 восстановления границ линейных посылок, декодер 35, блок 36 восстановления границ кодовых групп, блок 37 контроля, регист- ратор 38 ошибок, причем корреляцион- ньш приемник 30 содержит перемножители 39 и 40, управляемый фазовращатель 41, формирователь 42 сигнала ошибки, элемент 43 задержки, интеграторы 44 и 45, фильтры 46 и 47 нижних частот, фазовращатели 48 и 49 и блок 50 селекции, а регистратор 38 ошибок содержит счетчик 51 и блок 52 индикации.

Система работает следующим образом.

Преобразование двоичного основания в четверичное осуществляется в соответствии со следующей таблицей.

35

45

В таблице рядом с каждой четверичной кодовой группой: указано значение цифровой суммы в данной группе, вычисленное как алгебраическая сумма амплитуд импульсов в кодовой группе при условии, что символам О,1,2,и 3 Q кода поставлено в соответствие нормированное напряжение -1,5; -0,5; +0,5; +1,5.

Над каждой из трех колонок кодовых групп указано значение цифровой суммы на границе кодовых групп, хранящейся в блоке 11 памяти на передающей стороне к моменту поступления следующей двоичной группы, состоящей из трех символов, с выхода источника 2 дискретной инфор 1ации, синхронизируемого блоком 3 синхронизации, и записываемой в последовательный регистр 9 инверсной двоичной тактовой частотой

с выхода инвертора 5. Три символа, записанные в последовательном регистре 9, переписываются Инверсным кодовым синхросигналом с второго выхода формирователя 6 синхросигнала кодовьсх

55

0

5

0

5

5

Q

5

групп в параллельный регистр 10 и хранятся там в течение времени, равного трем двоичным тактовым интервалам. На вторую группу входов преобразователя 13 основания кода с выхода блока 11 памяти поступает значение

предшествующей цифровой суммы на границе кодовых групп, представленное в двоичном виде, а на первый вход - кодовый синхросигнал с первого выхода формирователя 6, который также подается через формирователь 7 и блок 8 на первый счетчик 4. Причем нуль в кодовом синхросигнале соответствует первому четверичному символу на выходе преобразователя 13, а единица - второму. Четыре выхода преобразователя 13 являются шинами символов 0;1,2 и 3. Так, если (соответствует сигналу 100 на выходе блока 11 памяти), то в соответствии с таблицей приходящая двоичная группа, например 011, кодируется группой из левой колонки таблицы, в данном случае 32, которая на выходе первого сумматора 18 представляется двумя импульсами с амплитудами +1,5 и +0,5 и длительностью Т, с Т, где Т - период крдирЬванного сигнала. Длительность импульсов Tj формируется формирователем 20 импульсов и блоками 21-24 совпадения. Подсчитанная в первом с.чет- чике 4 цифровая сумма (для группы 32 цифровая сумма равна +2) складывается во втором счетчике 14с предыдущим значением и результат сложения записывается в блок 11 памяти и т.д. Блок 12 запрета исключает появление запрещенных значений цифровой суммы на выходах блока 11 памяти при включении системы передачи посредством установки блока 11 памяти в одно из разрешенных значений цифровой суммы, Таким образом, на выходе первого сумматора 18 формируется пятиуровневый балансный сигнал, в энергетическом спектре которого отсутствует постоянная составляющая, а мощность низкочастотных составляющих незначительна. Поэтому четьфехуровневый сигнал на выходе фильтра 16 верхних частот не искажается, а мощность помех от цифрового сигнала в канапе служебной связи на выходе второго сумматора 19 пренебрежимо мала. Суммарный сигнал с выхода второго сумматора 19 поступает на вход частотного нодулятора 15 и далее в радиотракт. Следует отметить, что изменение значений фаэы

частотно-манипулированного сигнала

п 37

на и, ,11 , - происходит на интервале времени Т,t Т, что позволяет расширить зону максимального раскрыв глаз диаграммы на выходах корреляционного приемника 30 и тем самым повысить помехоустойчивость приема цифровой информации за счет снижения влияния фазовьпс дрожаний тактовых импульсов на входах решающих блоков 32 и 33.

На приемной стороне сигнал с выхода усилителя 29 промежуточной частоты поступает на управляемый фазовращатель 41 корреляционного приемника 30, создающий начальный сдвиг фаз между сигналами, поступающими на перемножители 39 и 40. После перемножения и интегрирования в фильтрах 46 и 47 нижних частот на их выходах формируются двоичные сигналы. Выходы фильтров 46 и 47 нижних частот подключены к выходам блока 50 селекции, который выделяет напряжение квадратурных составляющих, находящихся в первом или третьем квадрантах сигнала четырехпозиционной частотной манипуляции с минимальным сдвигом.

Выбор первого или третьего квадрантов определяется тем, что в этих квадрантах знаки квадратурных составляющих одинаковы, что позволяет однозначно определить величину и знак сигнала ошибки. Выходы блока 50 селекции соединены с входами интеграторов 44 и 45, которые формируют напряжения, подаваемые на формирователь 42 сигнала ошибки и пропорциональные средним значениям напряжений квадратурных составляющих при передачах частотно-манипулированного сигнала в первом или третьем квадрантах.

о

Сигнал ошибки с выхода формирователя 42 подается на вход управляемого фазовращателя 41, который компенсирует сдвиг фаз, возникающий между поступающими на перемножители 39 и 40. напряжениями и тем самым исключает уменьшение помехоустойчивости приема из-за нестабильности несущей частоты. Сигналы управлейия поступают на перемножители 39 и 40 через элемент 43 задержки и фазовращатели 48 и 49. С выходов фильтров 46 и 47 нижних ча с- тот сигналы поступают на первые вхо- ы решающих блоков 32 и 33, на вторые входы которых поступает тактовый сиг0

5

0

5

0

5

0

5

0

5

нал, вьщеленный из сигналов с выходов фильтров 46 и 47 нижних частот в блоке 37 восстановления границ линейных посылок. Двоичные последовательности с выходов первого и второго

решающих блоков 32 и 33 преобразуются в декодере 35 в четыре двоичных последовательности, соответствующие символам 0,1,2 и 3 четверичного ос-, нования, которые поступают на соот- . ветствующие входы обратного преобразователя 31 основания кода и блока 37 контроля. С выхода блока 37 сигнат лы, -пройдя блоки 36 и 28, поступают на другие входы обратного преобразователя 31. На его выходе формируются два цифровых потока, полученных в результате обратного преобразования четверичных символов в двоичные в соответствии с таблицей. Эти два цифровых потока, пройдя формирователь 27, поступают в приемник 26. Нормальная работа обратного преобразователя 31 обеспечивается двумя импульсными последовательностями, следующими с частотой информационных посылок и границ кодовых групп. Первая из этих последовательностей создается в блоке 28 восстановления границ информационных посылок, а вторая - в блоке 36 восстановления границ кодовых групп. Причем сигналы служебной связи с выхода усилителя 29 поступают в приемник 25 сигналов служебной связи.

Под нарушениями правил кодирования в коде ЗВ20 понимаются превьш1ения граничных значений цифровой суммы ( и ), которые возникают при наличии ошибочных символов в принимаемом сигнале. При этом все одиночные ошибки в принимаемом сигнале приводят к превьш1ению граничных значений цифровой суммы. Для обнаружения нарушений граничных значений цифровой суммы служит блок 37 контроля, а регистрация ошибок осуществляется в регистраторе 38 посредством подсчета ошибок в счетчике 51 и индикации показаний в блоке 52 индикации.

Технико-экономическая эффективность изобретения связана с увеличе- нием помехоустойчивости, приема цифровой информации и, следовательно, либо с уменьшением мощности передающей станции, либо с yвeличf ниeм расстояния между передающей и приемной сторонами. Введение на передающей стороне формирователя импульсов и четырех блоков совпадения обеспечивает изменение фазы частотно-манипулированного сигнала с минимальным сдвигом на О,

С-к .

3ff 2

- II. - на интервале времени Т ,

меньшем длительности тактового интер- вала передаваемого цифрового сигнала, и тем самым увеличивает область максимального раскрыва глаз диаграммы на входах решающих устройств, практически исключая влияние фазовых дрожа- НИИ тактовых импульсов на помехоустойчивость и позволяя упростить блок выделения тактового сигнала. .

Формулаизобретения Система передачи дискретной информации по авт. св. № 1262741, отличающаяся тем, что, с целью повышения помехоустойчивости за счет снижения влияния фазовых дрожаний тактовых импульсов, введены на передающей стороне формирователь импульсов и блоки совпадения, причем каждый выход блока стробирования соединен с входом первого сумматора через соответствующий блок совпадения, первый выход формирователя синхросигнала линейных посылок подключен к входу формирователя импульсов, выход KOtoporo подключен к вторым входам блоков совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Кодер кода 3В2 @ | 1984 |

|

SU1244803A1 |

| Кодер балансного кода 3B2Q | 1987 |

|

SU1531223A1 |

| Устройство кодовой синхронизации | 1985 |

|

SU1328941A1 |

| Кодер двоичного кода 3В4В-3 | 1986 |

|

SU1444964A1 |

| Устройство регистрации ошибок | 1985 |

|

SU1478346A1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Устройство для приема сигналов с двухкратной фазоразностной модуляцией | 1987 |

|

SU1453613A1 |

| Система передачи цифровой информациибииМпульСНыМ СигНАлОМ | 1976 |

|

SU815953A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

Изобретение относится к многоканальной радиорелейной связи. Цель изобретения - повышение помехоустойчивости за счет снижения влияния фазовых дрожаний тактовых импульсов. Введение на передающей стороне формирователя импульсов и четырех блоков совпадения обеспечивает изменение фазы частотноманипулированного сигнала с минимальным сдвигом на 0, φ/2, φ, 3φ/2 на интервале времени Т1, меньшем длительности тактового интервала передаваемого цифрового сигнала, и тем самым увеличивает область максимального раскрыва глаз диаграммы на входах решающих устройств, практически исключая влияние фазовых дрожаний тактовых импульсов на помехоустойчивость. 2 ил.

0}1/г.

Составитель О.Андрушко Редактор Г.Гербер Техред М.Ходанич Корректор М.Шароши

Заказ 5448/56

Тираж 626

ВНИИПИ ГЛгударственного комитета по изобретениям и открытиям при ГКНТ СССР It3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1987-11-16—Подача