Изобретение относится к электросвязи и может быть использовано в аппаратуре многоканальных цифровых системах передачи с временным разделением каналов.

Известно устройство временного группообразования по патенту РФ №2073955, кл. Н04J 3/22, опубл. 20.02.1997, содержащее, как и предлагаемое устройство, в передающей части n преобразователей стыкового кода приема, n блоков асинхронного сопряжения передачи, блок объединения, генераторное оборудование передачи, преобразователь линейного кода передачи, в приемной части преобразователь линейного кода приема, приемник циклового синхросигнала, генераторное оборудование приема, канальный распределитель, n блоков асинхронного сопряжения приема, n преобразователей стыкового кода передачи. При этом входы преобразователей стыкового кода приема являются информационными входами устройства, информационный выход каждого из n преобразователей стыкового кода приема соединены с информационным входом соответствующего одного из n блоков асинхронного сопряжения передачи, а первый выход управления считывания генераторного оборудования передачи соединен с входом управления считывания первого блока асинхронного сопряжения передачи, информационный выход каждого из n блоков асинхронного сопряжения передачи соединены с соответствующими с 1 по n входами блока объединения, выход которого соединен с входом преобразователя линейного кода передачи, выход которого является выходом передающей части устройства, а вход преобразователя линейного кода приема является входом приемной части устройства, информационный выход преобразователя линейного кода приема соединен с групповым входом канального распределителя, а также с информационным входом приемника циклового синхросигнала, тактовый вход приемника циклового синхросигнала объединен с входом тактовой синхронизации генераторного оборудования приема и соединен с тактовым выходом преобразователя линейного кода приема, вход цикловой синхронизации генераторного оборудования приема соединен с выходом приемника циклового синхросигнала, информационные входы каждого из n блоков асинхронного сопряжения приема соединены с соответствующими информационными выходами канального распределителя, с первым выходом управления считывания генераторного оборудования приема соединен вход управления считывания первого блока асинхронного сопряжения приема, выход каждого из блоков асинхронного сопряжения приема соединен с входом соответствующего одного из n преобразователя стыкового кода передачи, выходы которых являются информационными выходами устройства. Недостатком такого устройства является потеря принимаемой информации, обусловленная неправильным разделением группового цифрового потока на компонентные цифровые потоки при сбое циклового синхронизма и несинхронной работе канального распределителя. При необходимости восстановления потерянной информации, например при передаче дискретной информации, приемнику дискретной информации необходимо осуществлять запрос на передатчик дискретной информации о повторной передаче потерянной информации. Тем самым увеличивается время на передачу дискретной информации. При этом при передаче некоторых видов дискретной информации потери могут оказаться невосполнимыми.

Известно многоканальное приемопередающее устройство с временным разделением цифровых асинхронных каналов по патенту РФ №2033695, кл. Н04J 3/00, опубл. 20.04.1995, Бюл. №11, содержащее, как и предлагаемое устройство, в передающей части n преобразователей стыкового кода приема, n блоков асинхронного сопряжения передачи, блок объединения, генераторное оборудование передачи, передатчик циклового синхросигнала, преобразователь линейного кода передачи, в приемной части преобразователь линейного кода приема, приемник циклового синхросигнала, генераторное оборудование приема, канальный распределитель, состоящий из n элементов И, n блоков асинхронного сопряжения приема, n преобразователей стыкового кода передачи. При этом в передающей части входы преобразователей стыкового кода приема являются информационными входами устройства, информационный и тактовый выход каждого из n преобразователей стыкового кода приема соединены соответственно с информационным и входом управления записи соответствующего одного из n блоков асинхронного сопряжения передачи, а с 1 по п выходы управления считывания генераторного оборудования передачи соединены с входами управления считывания соответствующих блоков асинхронного сопряжения передачи, информационный выход и выход команд согласования скоростей каждого из n блоков асинхронного сопряжения передачи соединены с соответствующими с 1 по 2n входами блока объединения, а (n+1)-й выход управления считывания генераторного оборудования передачи соединен с входом передатчика циклового синхросигнала, выход которого соединен с (2n+1)-м входом блока объединения, выход которого соединен с входом преобразователя линейного кода передачи, выход которого является выходом передающей части устройства, а вход преобразователя линейного кода приема является входом приемной части устройства, информационный выход преобразователя линейного кода приема соединен с групповым входом канального распределителя, а также с информационным входом приемника циклового синхросигнала, при этом объединенные первые входы n элементов И канального распределителя являются его групповым входом, тактовый вход приемника циклового синхросигнала объединен с входом тактовой синхронизации генераторного оборудования приема и соединен с тактовым выходом преобразователя линейного кода приема, вход цикловой синхронизации генераторного оборудования приема соединен с первым выходом приемника циклового синхросигнала, а вторые входы каждого элемента И канального распределителя, являющиеся его входами управления, соединены с выходами управления соответствующих одного из n блоков асинхронного сопряжения приема, информационные входы каждого из которых соединены с выходами соответствующих элементов И канального распределителя, являющиеся его информационными выходами, а с 1 по n выходы управления считывания генераторного оборудования приема соединены с входами управления считывания соответствующих блоков асинхронного сопряжения приема, выход каждого из блоков асинхронного сопряжения приема соединен с входом соответствующего одного из n преобразователя стыкового кода передачи, выходы которых являются информационными выходами устройства. Недостатком такого устройства является потеря принимаемой информации, обусловленная неправильным разделением группового цифрового потока на компонентные цифровые потоки при сбое циклового синхронизма и несинхронной работе канального распределителя. При необходимости восстановления потерянной информации, например при передаче дискретной информации, приемнику дискретной информации необходимо осуществлять запрос на передатчик дискретной информации о повторной передаче потерянной информации. Тем самым увеличивается время на передачу дискретной информации. При этом при передаче некоторых видов дискретной информации потери могут оказаться невосполнимыми.

Наиболее близким к предлагаемому является устройство временного группообразования, описанное в книге Левин Л.С., Плоткин М.А. Цифровые системы передачи информации. - М.: Радио и связь, 1982. - С.53-59, рис.3.2, прототип, содержащий, как и предлагаемое устройство, в передающей части n преобразователей стыкового кода приема, n блоков асинхронного сопряжения передачи, блок объединения, генераторное оборудование передачи, передатчик циклового синхросигнала, преобразователь линейного кода передачи, а в приемной части преобразователь линейного кода приема, приемник циклового синхросигнала, генераторное оборудование приема, канальный распределитель, состоящий из n элементов И, n блоков асинхронного сопряжения приема, n преобразователей стыкового кода передачи. При этом в передающей части входы n приемных преобразователей стыкового кода являются информационными входами устройства, информационный и тактовый выход каждого из n преобразователей стыкового кода приема соединены соответственно с информационным и входом управления записи соответствующего одного из n блоков асинхронного сопряжения передачи, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования передачи соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих блоков асинхронного сопряжения передачи, информационный выход и выход команд согласования скоростей каждого из n блоков асинхронного сопряжения передачи соединены с соответствующими с 1 по 2n входами блока объединения, а (n+1)-й выход управления считывания генераторного оборудования передачи соединен с входом передатчика циклового синхросигнала, выход которого соединен с (2n+1)-м входом блока объединения, выход которого соединен с входом преобразователя линейного кода передачи, выход которого является выходом передающей части устройства, а вход преобразователя линейного кода приема является входом приемной части устройства, информационный выход преобразователя линейного кода приема соединен с групповым входом канального распределителя, а также с информационным входом приемника циклового синхросигнала, при этом объединенные первые входы n элементов И канального распределителя являются его групповым входом, тактовый вход приемника циклового синхросигнала объединен с входом тактовой синхронизации генераторного оборудования приема и соединен с тактовым выходом преобразователя линейного кода приема, вход цикловой синхронизации генераторного оборудования приема соединен с первым выходом приемника циклового синхросигнала, а вторые входы каждого элемента И канального распределителя, являющиеся его входами управления, соединены с выходами управления соответствующих одного из n блоков асинхронного сопряжения приема, информационные входы каждого из которых соединены с выходами соответствующих элементов И канального распределителя, являющиеся его информационными выходами, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования приема соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих блоков асинхронного сопряжения приема, выход каждого из блоков асинхронного сопряжения приема соединен с входом соответствующего, одного из n, преобразователя стыкового кода передачи, выходы которых являются информационными выходами устройства. Недостатком прототипа является потеря принимаемой информации, обусловленная неправильным разделением группового цифрового потока на компонентные цифровые потоки при сбое циклового синхронизма и несинхронной работе канального распределителя. При необходимости восстановления потерянной информации, например при передаче дискретной информации, приемнику дискретной информации необходимо осуществлять запрос на передатчик дискретной информации о повторной передаче потерянной информации. Тем самым увеличивается время на передачу дискретной информации. При этом при передаче некоторых видов дискретной информации потери могут оказаться невосполнимыми.

Объединение компонентных цифровых потоков в групповой поток (на передающей стороне устройства временного группообразования) производится на циклической основе. Для того чтобы групповой цифровой поток в приемной части устройства временного группообразования возможно было разделить на компонентные потоки, в передающей части групповой поток маркируется - в него вводится детерминированный цикловой синхросигнал, с помощью которого обозначается начало каждого цикла. Приемником циклового синхросигнала в групповом цифровом потоке отыскивается цикловой синхросигнал, по которому синхронизируются цикловые распределители генераторного оборудования передачи и приема, обеспечивая тем самым с помощью канального распределителя правильное распределение цифровых сигналов группового потока по компонентным цифровым потокам. Сбой циклового синхронизма в устройстве временного группообразования приводит к неправильному разделению группового потока, что приводит к потере принимаемой информации. При необходимости восстановления потерянной информации, например при передаче дискретной информации, приемнику дискретной информации необходимо осуществлять запрос на передатчик дискретной информации о повторной передаче потерянной информации. Тем самым увеличивается время на передачу дискретной информации. При этом при передаче некоторых видов дискретной информации потери могут оказаться невосполнимыми. Указанные факторы обуславливают необходимость обеспечения передачи информации с помощью устройства временного группообразования без потерь и в минимальные сроки в условиях сбоя циклового синхронизма.

Устройство временного группообразования содержит в передающей стороне n преобразователей стыкового кода приема, n блоков асинхронного сопряжения передачи, блок объединения, генераторное оборудование передачи, передатчик циклового синхросигнала, преобразователь линейного кода передачи, а в приемной части преобразователь линейного кода приема, приемник циклового синхросигнала, генераторное оборудование приема, канальный распределитель, состоящий из n элементов И, n блоков асинхронного сопряжения приема, n преобразователей стыкового кода передачи. При этом в передающей части входы n приемных преобразователей стыкового кода являются информационными входами устройства, информационный и тактовый выход каждого из n преобразователей стыкового кода приема соединены соответственно с информационным и входом управления записи соответствующего одного из n блоков асинхронного сопряжения передачи, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования передачи соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих блоков асинхронного сопряжения передачи, информационный выход и выход команд согласования скоростей каждого из n блоков асинхронного сопряжения передачи соединены с соответствующими с 1 по 2n входами блока объединения, а (n+1)-й выход управления считывания генераторного оборудования передачи соединен с входом передатчика циклового синхросигнала, выход которого соединен с (2n+1)-м входом блока объединения, выход которого соединен с входом преобразователя линейного кода передачи, выход которого является выходом передающей части устройства, а вход преобразователя линейного кода приема является входом приемной части устройства, информационный выход преобразователя линейного кода приема соединен с групповым входом канального распределителя, а также с информационным входом приемника циклового синхросигнала, при этом объединенные первые входы n элементов И канального распределителя являются его групповым входом, тактовый вход приемника циклового синхросигнала объединен с входом тактовой синхронизации генераторного оборудования приема и соединен с тактовым выходом преобразователя линейного кода приема, вход цикловой синхронизации генераторного оборудования приема соединен с первым выходом приемника циклового синхросигнала, а вторые входы каждого элемента И канального распределителя, являющиеся его входами управления, соединены с выходами управления соответствующих одного из n блоков асинхронного сопряжения приема, информационные входы каждого из которых соединены с выходами соответствующих элементов И канального распределителя, являющиеся его информационными выходами, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования приема соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих блоков асинхронного сопряжения приема, выход каждого из блоков асинхронного сопряжения приема соединен с входом соответствующего одного из n преобразователя стыкового кода передачи, выходы которых являются информационными выходами устройства.

Технический результат при осуществлении изобретения - обеспечение передачи информации с помощью устройства временного группообразования без потерь и в минимальные сроки в условиях сбоя циклового синхронизма достигается введением буферного запоминающего устройства, дополнительного канального распределителя, дополнительных блоков асинхронного сопряжения приема, дополнительных преобразователей стыкового кода передачи. При этом информационный выход и тактовый выход преобразователя линейного кода приема также соединены соответственно с информационным входом и тактовым входом буферного запоминающего устройства, первый, второй, третий и четвертый входы которого соединены соответственно со вторым, третьим, четвертым и пятым выходами приемника циклового синхросигнала, а выход буферного запоминающего устройства соединен с групповым входом дополнительного канального распределителя, входы управления дополнительного канального распределителя соединены с выходами управления соответствующих дополнительных блоков асинхронного сопряжения приема, информационные входы каждого из которых соединены с соответствующими информационными выходами дополнительного канального распределителя, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования приема также соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих дополнительных блоков асинхронного сопряжения приема, выход каждого из дополнительных блоков асинхронного сопряжения приема соединен с входом соответствующего одного из n дополнительного преобразователя стыкового кода передачи, выходы которых являются дополнительными информационными выходами устройства.

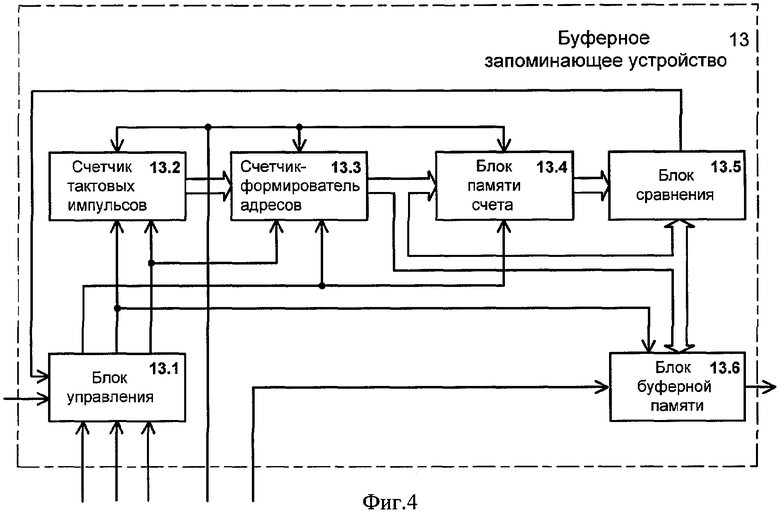

В частном случае выполнения буферное запоминающее устройство может состоять из блока управления, счетчика тактовых импульсов, счетчика-формирователя адресов, блока памяти счета, блока сравнения и блока буферной памяти, при этом второй, третий, четвертый и пятый входы блока управления являются соответственно первым, вторым, третьим и четвертым входами буферного запоминающего устройства, а совместно включенные счетный вход счетчика тактовых импульсов и счетчика-формирователя адресов, а также тактовый вход блока памяти счета являются тактовым входом буферного запоминающего устройства, вход управления блока памяти счета объединен с входом разрешения параллельной загрузки данных счетчика-формирователя адресов и подключен к первому выходу блока управления, второй выход которого совместно подключен к входу управления блока буферной памяти и входу управления счетчика тактовых импульсов, выход сброса которого объединен с входом сброса счетчика-формирователя адресов и подключен к третьему выходу блока управления, выход счетчика тактовых импульсов подключен к входу параллельной загрузки данных счетчика-формирователя адресов, выход которого совместно подключен к входу данных блока памяти счета, второму входу блока сравнения и адресному входу блока буферной памяти, выход блока памяти счета подключен к второму входу блока сравнения, выход которого подключен к первому входу блока управления, а информационный вход буферного запоминающего устройства является входом данных блока буферной памяти, выход которого является выходом буферного запоминающего устройства.

Благодаря введению буферного запоминающего устройства становится возможным во время сбоя циклового синхронизма записывать групповой цифровой поток, а после восстановления циклового синхронизма - его считывать. С помощью введения дополнительного канального распределителя n дополнительных блоков асинхронного сопряжения и n дополнительных преобразователей стыкового кода передачи становится возможным правильное разделение считываемого из буферного запоминающего устройства группового цифрового потока по компонентным потокам и предоставление восстановленной информации ее получателю. При этом установление необходимых моментов записи и считывания буферного запоминающего устройства осуществляет приемник циклового синхросигнала. Для этого из приемника циклового синхросигнала дополнительно выведены: выход накопителя по выходу из синхронизма; выход анализатора совпадений (анализатора появления отклика на истинный синхросигнал); выход анализатора несовпадений (анализатора потери отклика на истинный синхросигнал); а также выход решающего устройства (определяющего обнаружение нового состояния циклового синхронизма). При этом дополнительные выходы приемника циклового синхросигнала подключены соответственно к первому, второму, третьему и четвертому входам буферного запоминающего устройства.

Проведенный заявителем анализ уровня техники, включающий поиск по патентным и научно-техническим источникам информации, и выявление источников, содержащих сведения об аналогах заявленного изобретения, позволили установить, что заявитель не обнаружил аналог, характеризующийся признаками, тождественными всем существенным признакам заявленного изобретения. Выбор из перечня выявленных аналогов прототипа как наиболее близкого по совокупности существенных признаков аналога позволил выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном устройстве, изложенных в формуле изобретения. Следовательно, заявленное изобретение соответствует критерию «новизна».

Для проверки соответствия заявленного изобретение критерию «изобретательский уровень» заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного устройства. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, определенного заявителем. Не выявлено влияние преобразований, предусматриваемых существенными признаками заявленного изобретения, на достижение технического результата. В частности, заявленным изобретением не предусматриваются следующие преобразования: дополнение известного средства какой-либо известной частью, присоединяемой к нему по известным правилам, для достижения технического результата, в отношении которого установлено влияние именно таких дополнений; замену какой-либо части известного средства другой известной частью для достижения технического результата, в отношении которого установлено влияние именно такой замены; исключение какой-либо части средства с одновременным исключением обусловленной ее наличием функции и достижением при этом обычного для такого исключения результата; увеличение однотипных элементов для усиления технического результата, обусловленного наличием в средстве именно таких элементов; выполнение известного средства или его части из известного материала для достижения технического результата, обусловленного известными свойствами материала; создание средства, состоящего из известных частей, выбор которых и связь между которыми осуществлены на основании известных правил, рекомендаций и достигаемый при этом технический результат обусловлен только известными свойствами частей этого объекта и связей между ними; изменение количественных признаков или взаимосвязи признаков, если известен факт влияния каждого из них на технический результат и новые значения признаков или их взаимосвязь могли быть получены из известных зависимостей. Следовательно, заявленное изобретение соответствует критерию «изобретательский уровень».

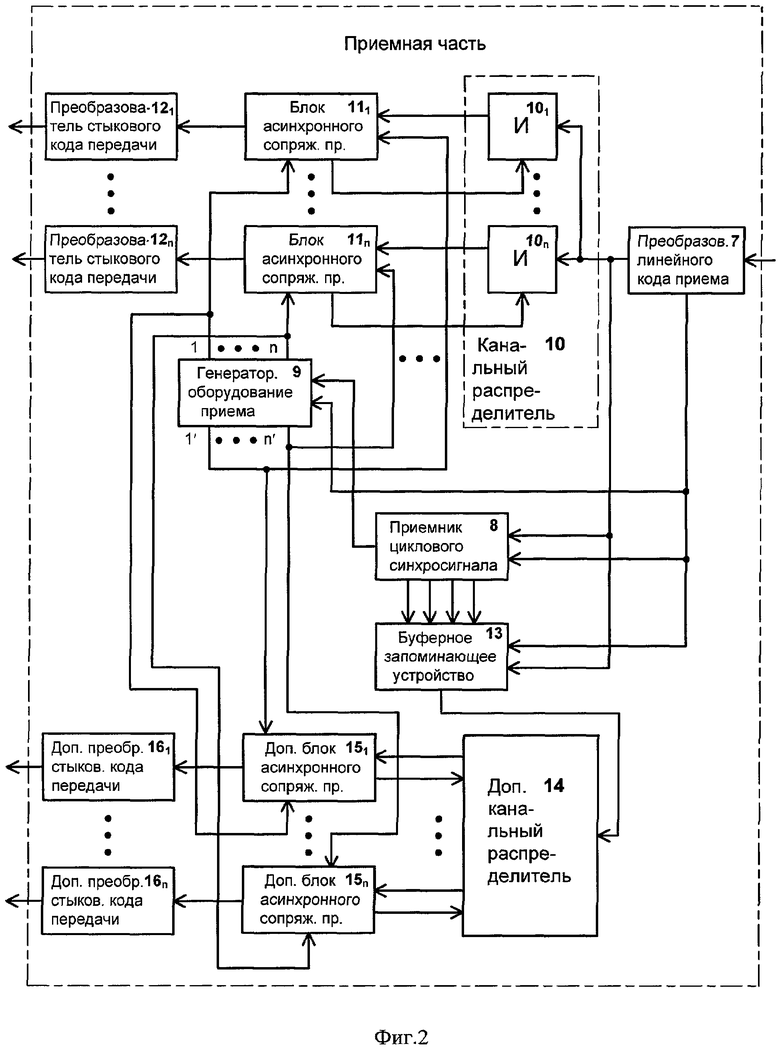

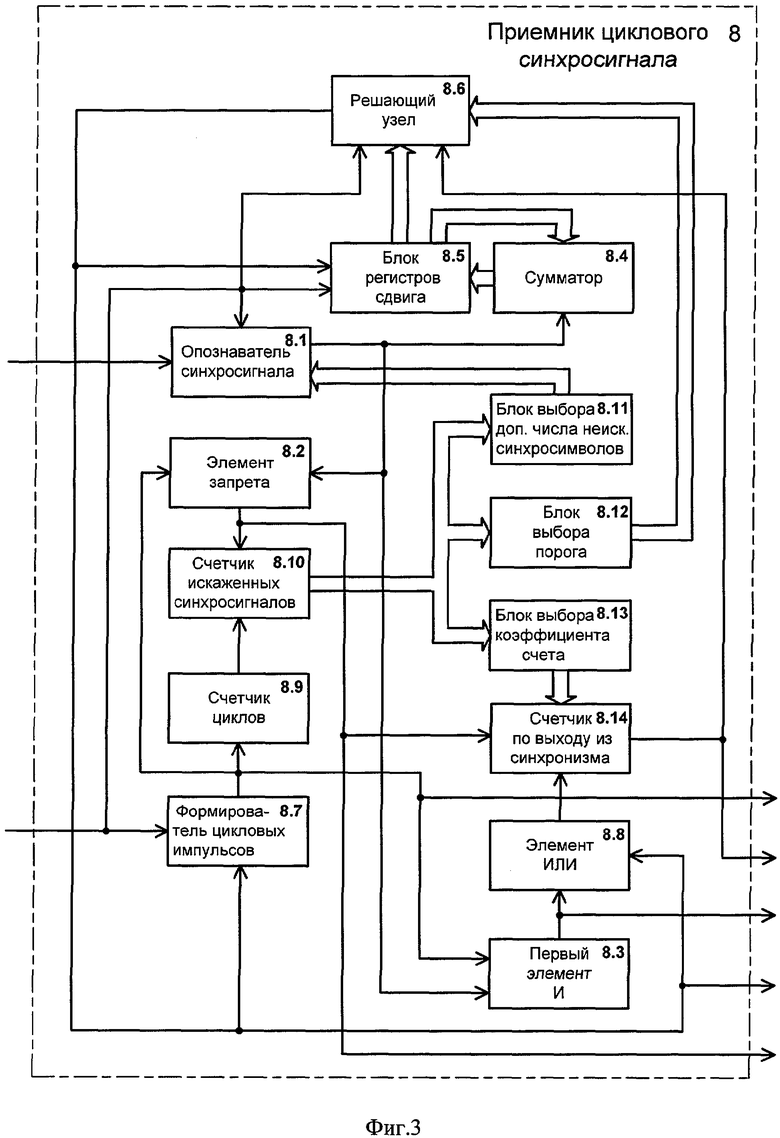

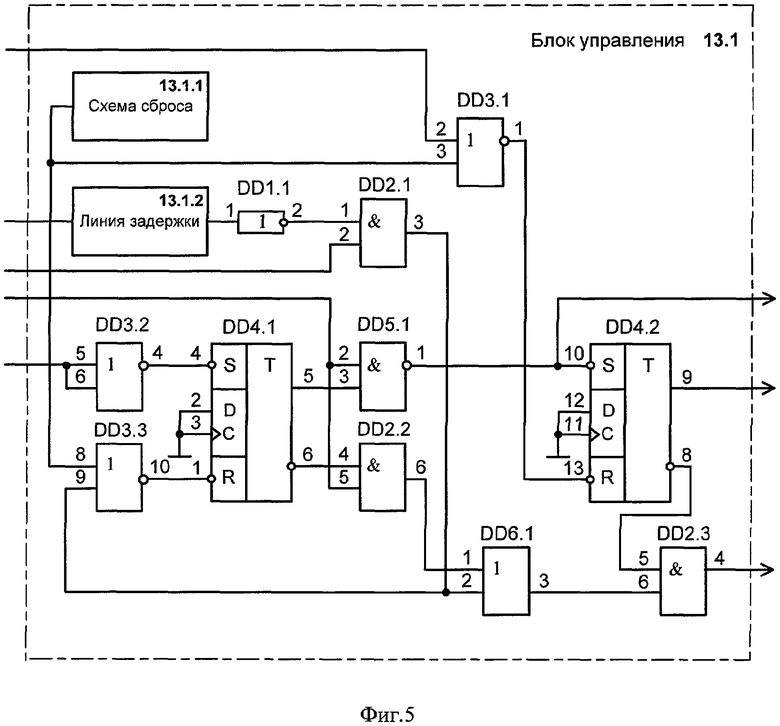

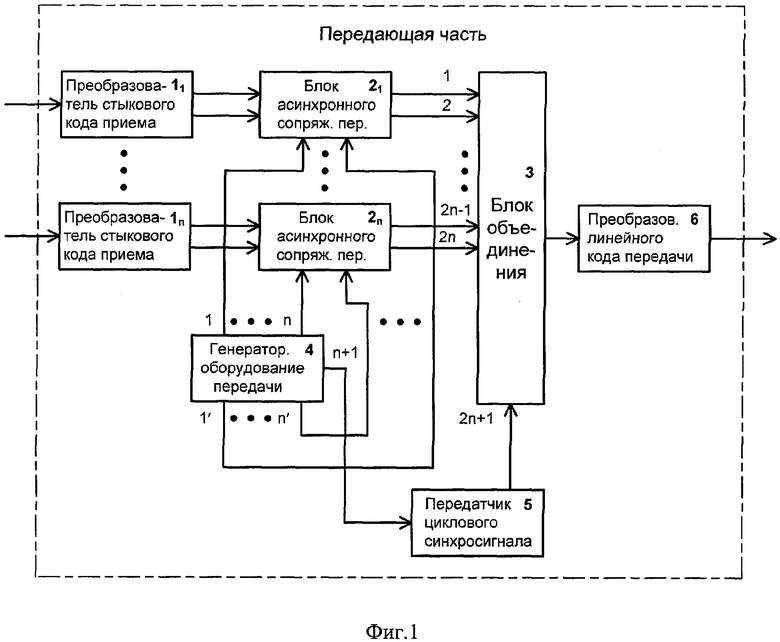

Изобретение поясняется графическими материалами, на которых изображено: на фиг.1 - структурная схема передающей части устройства временного группообразования, на фиг.2 - структурная схема приемной части устройства временного группообразования, на фиг.3 - структурная схема приемника циклового синхросигнала, на фиг.4 - структурная схема буферного запоминающего устройства, на фиг.5 - функциональная схема блока управления буферного запоминающего устройства.

Сведения, подтверждающие возможность осуществления изобретения с получением вышеуказанного технического результата, заключаются в следующем.

Устройство временного группообразования содержит в передающей части преобразователи 11-1n стыкового кода приема, блоки 21-2n асинхронного сопряжения передачи, блок 3 объединения, генераторное оборудование 4 передачи, передатчик 5 циклового синхросигнала, преобразователь 6 линейного кода передачи, а в приемной части преобразователь 7 линейного кода приема, приемник 8 циклового синхросигнала, генераторное оборудование 9 приема, канальный распределитель 10, состоящий из элементов 101-10n И, блоки 111-11n асинхронного сопряжения приема, преобразователи 121-12n стыкового кода передачи, буферное запоминающее устройство 13, дополнительный канальный распределитель 14, дополнительные блоки 151-15n асинхронного сопряжения приема и дополнительные преобразователи 161-16n стыкового кода передачи. При этом в передающей части устройства временного группообразования входы преобразователей 11-1n стыкового кода приема являются информационными входами устройства, а информационный выход и тактовый выход каждого из приемных преобразователей 11-1n стыкового кода соединен соответственно с информационным входом и входом управления записи соответствующего блока 2 асинхронного сопряжения передачи, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования 4 передачи соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих блоков 21-2n асинхронного сопряжения передачи, а информационные выходы и выходы команд согласования скоростей каждого из блоков 21-2n асинхронного сопряжения передачи соединены с соответствующими с 1 по 2n входами блока 3 объединения, а n+1 выход управления считывания генераторного оборудования 4 передачи соединен с входом передатчика циклового синхросигнала, выход которого соединен с 2n+1 входом блока 3 объединения, выход которого соединен с входом преобразователя 6 линейного кода передачи, выход которого является выходом передающей стороны устройства временного группообразования. А в приемной части устройства временного группообразования вход преобразователя 7 линейного кода приема является входом приемной части устройства, информационный выход преобразователя 7 линейного кода приема соединен с групповым входом канального распределителя 10, а также с информационным входом приемника 8 циклового синхросигнала, при этом объединенные первые входы n элементов И канального распределителя 10 являются его групповым входом, тактовый вход приемника 8 циклового синхросигнала объединен с входом тактовой синхронизации генераторного оборудования приема 9 и соединен с тактовым выходом преобразователя 7 линейного кода приема, вход цикловой синхронизации генераторного оборудования 9 приема соединен с первым выходом приемника 8 циклового синхросигнала, а вторые входы элементов 101-10n И канального распределителя 10, являющиеся его входами управления, соединены с выходами управления соответствующих блоков 111-11n асинхронного сопряжения приема, информационные входы каждого из которых соединены с выходами соответствующих элементов 101-10n И канального распределителя 10, являющиеся его информационными выходами, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования 9 приема соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих блоков 111-11n асинхронного сопряжения приема, выход каждого из блоков 111-11n асинхронного сопряжения приема соединен с входом соответствующего преобразователя 121-12n стыкового кода передачи, выходы которых являются информационными выходами устройства временного группообразования. При этом информационный выход и тактовый выход преобразователя 7 линейного кода приема также соединены соответственно с информационным входом и тактовым входом буферного запоминающего устройства 13, первый, второй, третий и четвертый входы которого соединены соответственно со вторым, третьим, четвертым и пятым выходами приемника 8 циклового синхросигнала, а выход буферного запоминающего устройства 13 соединен с групповым входом дополнительного канального распределителя 14, входы управления дополнительного канального распределителя 14 соединены с выходами управления соответствующих дополнительных блоков 151-15n асинхронного сопряжения приема, информационные входы каждого из которых соединены с соответствующими информационными выходами дополнительного канального распределителя 14, а с 1 по n выходы управления считывания и с 1' по n' выходы управления согласования скоростей генераторного оборудования 9 приема также соединены соответственно с входами управления считывания и с входами согласования скоростей соответствующих дополнительных блоков 151-15n асинхронного сопряжения приема, выход каждого из дополнительных блоков 151-15n асинхронного сопряжения приема соединен с входом соответствующего дополнительного преобразователя 161-16n стыкового кода передачи, выходы которых являются дополнительными информационными выходами устройства.

Устройство временного группообразования работает следующим образом. Компонентные цифровые потоки от n источников поступают на входы соответствующих преобразователей 11-1n кода приема, каждый из которых осуществляет преобразование стыкового кода в двоичный и выделение тактовой частоты входного цифрового компонентного потока.

Сигналы с выходов преобразователей 11-1n стыкового кода приема подаются в блоки 21-2n асинхронного сопряжения передачи, в каждом из которых осуществляется синхронизация входного цифрового компонентного потока с тактовой частотой, формируемой генераторным оборудованием 4 передачи (кратной тактовой частоте группового потока), методом двухстороннего согласования скоростей с формированием команд согласования скоростей в моменты рассогласования скоростей. Блоки 21-2n асинхронного сопряжения передачи могут быть выполнены по известной схеме (см. Левин Л.С., Плоткин М.А. Цифровые системы передачи информации. - М.: Радио и связь, 1982. - С.55-56, рис.3.2) и состоять из следующих элементов: запоминающего устройства; временного детектора; элемента НЕТ; элемента ИЛИ и передатчика команд согласования скоростей. При этом в каждом из блоков 21-2n асинхронного сопряжения передачи цифровой компонентный поток, поступающий на его информационный вход, записывается в запоминающее устройство, а считывается сигналом, поступающим с соответствующего выхода 1-n генераторного оборудования 4 передачи. Процессом записи управляет импульсная последовательность с тактовой частотой входного цифрового компонентного потока, поступающей на вход управления записи блока 2 асинхронного сопряжения передачи. Сигналы считывания и управления записью поступают на вход временного детектора, в котором определяются моменты возникновения и вид (знак) неоднородности. По сигналу о наличии неоднородности того или иного вида в передатчике команд согласования скоростей вырабатывается соответствующая команда согласования скоростей. При этом положительное согласование скоростей осуществляется запретом с помощью логического элемента НЕТ одного импульса считывания, а отрицательное согласование скоростей - дополнительным считыванием, которое производится с помощью логического элемента ИЛИ.

Генераторное оборудование 4 передачи предназначено для формирования и распределения во времени импульсных последовательностей, управляющих работой всех блоков передающей части аппаратуры временного группообразования и служащих для формирования группового цифрового потока. При этом сигналы с выходов 1-n генераторного оборудования 4 передачи предназначены для установления моментов передачи в групповом потоке сигналов определенных компонентных потоков, а сигнал n+1 - для установления момента передачи в групповом потоке циклового синхросигнала. Сигналы с выходов 1'-n' генераторного оборудования 4 передачи предназначены для установления моментов разрешения передачи в групповом потоке команд согласования скоростей.

Полученные в блоках 21-2n асинхронного сопряжения передачи сигналы и цикловой синхросигнал, формируемый передатчиком 5 циклового синхросигнала, объединяются в групповой поток с помощью блока 3 объединения. Блок объединения может быть выполнен на основе логического элемента ИЛИ, на входы которого подаются объединенные сигналы, а выход которого является групповым выходом блока 3 объединения.

Передатчик 5 циклового синхросигнала может быть выполнен как регистр сдвига, отводы с выходов которого через включенные инверторы или повторители объединяются на элементе ИЛИ. При этом подключение инверторов к определенным выходам регистра определяет структуру циклового синхросигнала. Передатчик 5 циклового синхросигнала может быть реализован, например, как описано в книге Кириллов В.И. Многоканальные системы передачи. - М.: Новое знание, 2002. - С.540-541, рис.13.64.

Затем групповой цифровой поток поступает на преобразователь 6 линейного кода передачи, где приобретает структуру, необходимую для передачи по заданной линии связи.

На приеме поступающий групповой поток в линейном коде преобразуется в преобразователе 7 линейного кода приема в двоичный код. Кроме того, в преобразователе 7 линейного кода приема осуществляется выделение тактовой частоты принимаемого группового потока, с помощью которой обеспечивается синхронность работы генераторного оборудования 9 приема и генераторного оборудования 4 передачи, которые могут быть реализованы, например, как описано в книге Скалин Ю.В. и др. Цифровые системы передачи. - М.: Радио и связь, 1988. - С.62-69.

В приемнике 8 циклового синхросигнала осуществляется выделение сигнала циклового синхронизма, который фазирует блок генераторного оборудования 9 передачи и обеспечивает его синфазную работу с генераторным оборудованием приема. Импульсные последовательности с соответствующих выходов приемного генераторного оборудования 9 открывают поочередно логические элементы 101-10n И канального распределителя 10, обеспечивая правильное распределение группового потока на компонентные потоки, поступающие на соответствующие блоки 111-11n асинхронного сопряжения приема, в которых восстанавливается первоначальная скорость передающего компонентного цифрового потока.

Блоки 111-11n асинхронного сопряжения приема могут быть выполнены по известной схеме (см. Левин Л.С., Плоткин М.А. Цифровые системы передачи информации. - М.: Радио и связь, 1982. - С.57-59, рис.3.2) и состоять из следующих элементов: запоминающего устройства; элемента НЕТ; элемента ИЛИ1, элемента ИЛИ2, приемника команд согласования скоростей и устройства фазовой автоматической подстройки частоты. При этом в каждом из блоков 111-11n асинхронного сопряжения приема производится запись цифрового потока в запоминающее устройство и считывание с частотой, равной средней частоте записи, вырабатываемой устройством фазовой автоподстройки частоты, которое включает в себя генератор, управляемый напряжением, схему управления и временной детектор, на выходе которого формируется сигнал, соответствующий текущему значению временного интервала между моментами записи и считывания. Процессом записи управляет импульсная последовательность с соответствующего 1-n выхода генераторного оборудования 9 приема. По сигналу о необходимости положительного согласования скоростей, вырабатываемому приемником команд согласования скоростей, осуществляется запрет записи информации в запоминающее устройство. Временное положение сигнала запрета соответствует моменту осуществления согласования скоростей в передающем устройстве. По сигналу о необходимости отрицательного согласования скоростей с помощью логического элемента ИЛИ1 открывается соответствующий элемент И канального распределителя 10, вводя тем самым дополнительный символ в передаваемый сигнал. Одновременно дополнительный импульс через логический элемент ИЛИ2 вводится в сигнал управления записью. Частота генератора, управляемого напряжением, регулируется напряжением, соответствующим постоянной составляющей сигнала на выходе временного детектора. Восстановленные компонентные потоки с выходов блоков 111-11n асинхронного сопряжения приема поступают на соответствующие преобразователи 121-12n стыкового кода передачи, в которых сигналы двоичного кода преобразуются в сигналы стыкового кода.

Преобразователи кода стыка 11-1n, 121-12n, 161-16n и преобразователи линейного кода 6, 7 при использовании одинакового кода для передачи стыковых и линейных сигналов могут быть выполнены по одинаковой схеме. При этом преобразователи передачи состоят из кодера, а преобразователи приема из декодера и устройства выделения тактовой частоты, которые могут быть реализованы, например, как описано в книге Скалин Ю.В. и др. Цифровые системы передачи. - М.: Радио и связь, 1988. - С.78-80, 104-105, рис.3.31, 4.7.

При этом правильное разделение на приеме группового сигнала по потокам, контроль и поиск циклового синхронизма обеспечивается приемником 8 циклового синхросигнала. Приемник 8 циклового синхросигнала может быть реализован, например, как описано в описании изобретения к патенту РФ №2231228, кл. Н04L 7/08, опубл. 20.06.2004, Бюл. №17. Структурная схема приемника 8 циклового синхросигнала представлена на фиг.3. Он состоит из следующих элементов: опознавателя 8.1 синхросигнала, элемента 8.2 запрета, элемента 8.3 И, сумматора 8.4, блока 8.5 регистров сдвига, решающего узла 8.6, формирователя 8.7 цикловых импульсов, элемента 8.8 ИЛИ, счетчика 8.9 циклов, счетчика 8.10 искаженных синхросигналов, блока 8.11 выбора допустимого числа неискаженных синхросимволов, блока 8.12 выбора порога, блока 8.13 выбора коэффициента счета, счетчика 8.14 по выходу из синхронизма. При этом в известной схеме приемника 8 циклового синхросигнала кроме вывода (первый выход приемника 8) сигнала цикловой синхронизации (с выхода формирователя 8.7 цикловых импульсов) дополнительно осуществлены следующие выводы: с выхода счетчика 8.14 по выходу из синхронизма (второй выход приемника 8), с выхода элемента 8.3 И (третий выход приемника 8), с выхода решающего узла 8.6 (четвертый выход приемника 8) и с выхода элемента 8.2 элемента запрета (пятый выход приемника 8). При этом на первом выходе приемника 8 циклового синхросигнала по окончании каждого цикла следования цифрового группового потока формируются импульсы циклового синхросигнала. На втором выходе формируется сигнал сбоя циклового синхронизма. На третьем выходе формируется сигнал отклика опознавателя 8.1 на истинный цикловой синхросигнал. На четвертом выходе формируется сигнал синхронизации приемника 8 циклового синхросигнала. На пятом выходе формируется сигнал «неопознания» синхросигнала (в случае его искажения или сбоя). Сигналы со второго, третьего, четвертого и пятого выходов приемника 8 циклового синхросигнала поступают соответственно на первый, второй, третий и четвертый входы буферного запоминающего устройства 13, на пятый и шестой входы которого поступают соответственно тактовые импульсы и цифровой групповой поток.

Структурная схема буферного запоминающего устройства 13 представлена на фиг.4, которое состоит из следующих элементов: блока 13.1 управления, счетчика 13.2 тактовых импульсов, счетчика-формирователя 13.3 адресов, блока 13.4 памяти счета, блока 13.5 сравнения, блока 13.6 буферной памяти. При этом второй, третий, четвертый и пятый входы блока управления 13.1 являются соответственно первым, вторым, третьим и четвертым входами буферного запоминающего устройства 13, а совместно включенные счетный вход счетчика 13.2 тактовых импульсов и счетчика-формирователя 13.3 адресов, а также тактовый вход блока 13.4 памяти счета являются тактовым входом буферного запоминающего устройства 13, вход управления блока 13.4 памяти счета объединен с входом разрешения параллельной загрузки данных счетчика-формирователя 13.3 адресов и подключен к первому выходу блока управления 13.1, второй выход которого совместно подключен к входу управления блока 13.6 буферной памяти и входу управления счетчика 13.2 тактовых импульсов, выход сброса которого объединен с входом сброса счетчика-формирователя 13.2 адресов и подключен к третьему выходу блока управления 13.1, выход счетчика 13.2 тактовых импульсов подключен к входу параллельной загрузки данных счетчика-формирователя 13.3 адресов, выход которого совместно подключен к входу данных блока 13.4 памяти счета, второму входу блока 13.5 сравнения и адресному входу блока 13.6 буферной памяти, выход блока 13.4 памяти счета подключен к второму входу блока 13.5 сравнения, выход которого подключен к первому входу блока управления 13.1, а информационный вход буферного запоминающего устройства 13 является входом данных блока буферной памяти 13.6, выход которого является выходом буферного запоминающего устройства 13.

Блок 13.1 управления предназначен для формирования сигналов «записи/считывания» для блока буферной памяти 13.6, а также для формирования сигала «сброс» счетчика тактовых импульсов 13.2 и счетчика-формирователя адресов 13.3, сигнала «разрешения параллельной загрузки данных» в счетчик-формирователь 13.3 адресов, сигнала установки блока памяти счета 13.4 в режим «хранения» и сигнала «остановка» счетчика тактовых импульсов 13.2. На фиг.5 представлена функциональная схема блока управления 13.1. Он может быть реализован, например на микросхемах: DD1 - К1533 ЛН1; DD2 -К1533 ЛИ1; DD3 - К1533 ЛЕ1; DD4 - К1533 ТМ2; DD5 - К1533 ЛАЗ, DD6 - К1533 ЛЛ1. Схема сброса 13.1.1 может быть реализована с помощью простой RC-цепи, например, как описано в книге Аверьянов Н.Н. и др. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник. В 2 т. - М.: Радио и связь, 1988. - Т.2. - С.294, рис.16.32. Линия задержки 13.1.2 может быть построена, например, на элементах НЕ. При этом время задержки рассчитывается как время установки триггера DD4.2 в «единичное» состояние и определяется количеством включенных элементов НЕ (см., например, Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. Микросхемы и их применение: Справ. пособие. - М.: Радио и связь, 1989. - С.207)

tлз=qtзд.р.ср,

где q - четное число элементов НЕ, участвующих в задержке сигнала, tзд.р.ср - время задержки распространения в элементе НЕ, равный половине суммы времени задержки распространения сигнала при включении и выключении интегральной схемы (например, для микросхемы К555ЛН1 tзд.р.ср=20 нс), например, как описано в книге Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник. - М.: Машиностроение, 1993. - С.76.

Счетчик 13.2 тактовых импульсов предназначен для счета тактовых импульсов. С помощью счетчика 13.2 тактовых импульсов определяется начальный адрес считывания группового потока из буферного запоминающего устройства. Это становится возможным благодаря формированию блоком 13.1 управления сигнала остановки счетчика 13.2 тактовых импульсов в момент восстановления циклового синхронизма. В синхронном состоянии приемника 8 циклового синхросигнала счетчик 13.2 тактовых импульсов осуществляет непрерывный счет с начала цикла до его окончания, т.е. от нуля до N-1 (где N - количество тактовых интервалов в цикле). При искажении циклового синхросигнала или его сбое счет осуществляется с начала цикла до окончания второго цикла, т.е. от нуля до 2N-2. Затем, после достижения состояния счета 2N-2, счетчик 13.2 устанавливается в состояние N, а счет осуществляется от N до 2N-2. При обнаружении нового состояния синхронизма счетчик 13.2 тактовых импульсов останавливается. Счетчик 13.2 тактовых импульсов может быть выполнен, например, на основе синхронного двоично-десятичного счетчика с возможностью синхронной параллельной загрузки данных. При этом к выходу счетчика подключается дешифратор максимального состояния счетчика 2N-2. Выход дешифратора подключен к входу разрешения параллельной загрузки данных. К входам параллельной загрузки данных счетчика подан двоично-десятичный код числа N (например, с помощью подключения сигналов низкого и высокого уровня с общей шины и шины питания с использованием резистора 1 кОм). Счетчик 13.2 может быть реализован, например, как описано в книге Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник. - М.: Машиностроение, 1993. - С.108-109, 194-195.

Счетчик - формирователь 13.3 адресов предназначен для формирования адресных кодов для блока буферной памяти 13.6. Он может быть выполнен на основе каскадно объединенных двоично-десятичных синхронных счетчиков с возможностью параллельной загрузки данных. Счетчик - формирователь 13.3 адресов может быть реализован, например, как описано в книге Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник. - М.: Машиностроение, 1993. - С.191-192.

Блок 13.4 памяти счета предназначен для хранения кода конечного адреса записи группового цифрового потока в блок 13.6 буферной памяти. Он может быть выполнен на основе параллельно включенных регистров сдвига с параллельными входами и выходами данных. Блок 13.4 памяти счета может быть реализован, например, как описано в книге Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник. - М.: Машиностроение, 1993. - С.172-173.

Блок 13.5 сравнения предназначен для сравнения кода адреса, записанного в блоке 13.4 памяти счета с кодом адреса, формируемом на выходе счетчика-формирователя 13.3 адресов, и при их совпадении формирования сигнала перевода блока 13.6 буферной памяти из режима «записи» в режим «считывания». Блок 13.5 сравнения может быть выполнен, например, в виде параллельно включенных компараторов двоичных кодов, формирующих признак «больше», «меньше» при соответствующем знаке разницы значений входных операндов, а также признак их равенства, подаваемых на первый и второй входы блока. При этом выходом блока 13.5 сравнения является выход X=Y компаратора. Он может быть реализован, например, как описано в книге Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник. - М.: Машиностроение, 1993. - С.149-151.

Блок 13.6 буферной памяти предназначен для записи группового цифрового потока (в момент сбоя циклового синхронизма приемником 8 циклового синхросигнала) и его считывания (после восстановления циклового синхронизма). Он может быть выполнен с помощью оперативного запоминающего устройства с одноразрядной организацией, основанного на последовательной во времени поразрядной записи кодовой последовательности при переборе адресов с нулевого до конечного, и считывания группового цифрового потока в том же порядке, как осуществлялась его запись. Блок 13.6 буферной памяти может быть реализован, например, как описано в книге Лебедев О.Н. Микросхемы памяти и их применение - М.: Радио и связь, 1990. - С.104-107, рис.3.17.

Процесс записи цифрового группового потока в буферное запоминающее устройство 13 после потери циклового синхронизма и его считывание после восстановления циклового синхронизма производится следующим образом. При включении устройства временного объединения схемой сброса 13.1.1 формируется «сигнал сброса», который осуществляет установку триггеров DD4.1 и DD4.2 в «нулевое» состояние. При нахождении приемника 8 цикловой синхронизации в синхронном состоянии на выходах формирователя 8.7 цикловых импульсов и опознавателя 8.1 синхросигнала одновременно формируются сигналы «единица», которые поступают на первый и второй входы первого элемента 8.3 И, на выходе которого формируется сигнал «единица», которая подается на второй вход буферного запоминающего устройства 13 (на третий вход блока управления 13.1). При этом на третьем выходе блока управления 13.1 формируется сигнал «сброс» счетчика тактовых импульсов 13.2 и счетчика-формирователя адресов 13.3. С приходом следующего тактового импульса счетчик 13.2 тактовых импульсов и счетчик-формирователь адресов 13.3 начинают счет тактовых импульсов (поступающих с тактового входа буферного запоминающего устройства 13). Счетчик-формирователь 13.3 адресов на своем выходе начинает формировать коды адресов, которые поступают на адресный вход блока буферной памяти 13.6 и вход данных блока 13.4 памяти счета. А на вход данных блока буферной памяти 13.6 поступает групповой цифровой поток (с информационного входа буферного запоминающего устройства 13). При этом со второго выхода блока 13.1 управления на вход управления блока буферной памяти 13.6 поступает сигнал «запись» (сигнал «нулевого» уровня). Поэтому блок буферной памяти 13.6 начинает осуществлять запись цифрового группового потока, а блок памяти счета - запись текущего состояния счетчика-формирователя 13.3 адресов. С началом нового цикла на выходе первого элемента 8.3 И формируется сигнал «единичного» уровня, который сбрасывает счетчик тактовых импульсов 13.2 и счетчик-формирователь адресов 13.3. С приходом следующего тактового импульса процесс записи цифрового группового потока в блок 13.6 буферной памяти начинается заново.

При нахождении приемника 8 циклового синхросигнала в синхронном состоянии и при кратковременных сбоях циклового синхросигнала на выходе первого элемента 8.3 И сигнал логической «единицы» не формируется. А на выходе элемента 8.2 запрета сигнал логической «единицы» формируется. Поэтому счетчик 13.2 тактовых импульсов и счетчик-формирователь 13.3 адресов с началом нового цикла не сбрасываются, а продолжают счет тактовых импульсов. Блок буферной памяти 13.6 продолжает записывать поступающий на его вход данных цифровой групповой поток, а блок памяти счета - запись текущего состояния счетчика-формирователя 13.3 адресов. При этом с выхода элемента 8.2 запрета сигнал логической «единицы» поступает на пятый вход блока 13.1 управления, с помощью которого триггер DD4.1 устанавливается в «единичное» состояние. Если с началом нового цикла цикловой синхросигнал будет «распознан», на выходе первого элемента 8.3 И будет сформирован сигнал логической «единицы», с помощью которого триггер DD4.1, а также счетчик 13.2 тактовых импульсов и счетчик-формирователь 13.3 адресов будут сброшены в «нуль». С приходом следующего тактового импульса процесс записи цифрового группового потока в блок буферной памяти начинается заново.

При нахождении приемника 8 циклового синхросигнала в синхронном состоянии и при долговременном сбое циклового синхросигнала (ложный сбой циклового синхронизма) или потере циклового синхронизма (истинный сбой циклового синхронизма) на выходе первого элемента 8.3 И не формируется сигнал логической «единицы», а триггер DD4.1 устанавливается в «единичное» состояние. Поэтому сброс счетчика 13.2 тактовых импульсов и счетчика-формирователя 13.3 адресов не производится, а продолжается их счет. Блок буферной памяти 13.6 продолжает записывать поступающий на его вход данных цифровой групповой поток до восстановления состояния синхронизма приемником 8 циклового синхросигнала, а блок памяти счета - запись текущего состояния счетчика-формирователя 13.3 адресов. Во время поиска и восстановления синхронизма счетчик 13.2 тактовых импульсов осуществляет непрерывный счет от N до стояния максимального счета 2N-2 и продолжается до восстановления состояния синхронизма. При обнаружении циклового синхросигнала на четвертом выходе приемника 8 циклового синхросигнала формируется сигнал логической «единицы», который поступает на четвертый вход блока 13.1 управления. При этом триггер DD4.2 устанавливается в «единичное» состояние, счетчик 13.2 тактовых импульсов останавливается, а его состояние счета соответствует начальному адресу, с которого начался процесс записи группового цифрового сигнала в блок 13.6 буферной памяти. Момент остановки счетчика 13.2 тактовых импульсов соответствует началу цикла в принимаемом групповом потоке и в групповом потоке, записанном в блоке 13.6 буферной памяти. Если со следующим тактовым импульсом считывать записанный в блок 13.6 буферной памяти групповой цифровой поток, начиная с адреса, соответствующего состоянию остановленного счетчика 13.2 тактовых импульсов, становится возможным правильное разделение группового потока. После восстановления состояния синхронизма приемника 8 циклового синхросигнала (обнаружения нового положения синхронизма) на выходе решающего узла 8.6 формируется сигнал логической «единицы», который подается на третий вход буферного запоминающего устройства 13 (четвертый вход блока 13.1 управления). При этом триггер DD4.2 устанавливается в «единичное» состояние. На первом выходе блока 13.1 управления формируется сигнал логического «нуля», который подается на вход разрешения параллельной загрузки данных счетчика-формирователя 13.3 адресов и вход управления блока 13.4 памяти счета (перевода в режим хранения информации). При этом в блоке 13.4 памяти счета сохраняется состояние счета счетчика-формирователя 13.3 адресов, которое соответствует конечному адресу, по которому в блок 13.6 буферной памяти (во время несинхронной работы) был записан последний символ цифрового группового потока. Кроме того, после восстановления состояния синхронизма приемника 8 циклового синхросигнала на втором выходе блока 13.1 управления формируется сигнал логической «единицы», который подается на вход управления режимами «запись/чтение» блока 13.6 буферной памяти и на вход управления счетчика 13.2 тактовых импульсов. При этом блок 13.6 буферной памяти переводится в режим «чтения», а счетчик 13.2 тактовых импульсов останавливается. Счетчик-формирователь 13.3 адресов с помощью параллельного входа данных асинхронно устанавливается в состояние счета остановившегося счетчика 13.2 тактовых импульсов. Также после восстановления состояния синхронизма на третьем выходе блока 13.1 управления формируется сигнал логического «нуля», который подается на входы сброса счетчика 13.2 тактовых импульсов и счетчика-формирователя 13.3 адресов. При этом запрещается сброс счетчика 13.2 тактовых импульсов и счетчика-формирователя 13.3 адресов. Со следующим тактовым импульсом после формирования на выходе решающего узла 8.6 приемника 8 цикловой синхронизации сигнала синхронизации начинается процесс считывания цифрового группового потока с блока буферной памяти 13.6. При этом считывание начинается с адреса, установленного на выходе счетчика-формирователя 13.3 адресов и соответствующего начальному адресу, по которому начался процесс записи цифрового группового потока в блок 13.6 буферной памяти. С приходом очередного тактового импульса состояние счета счетчика-формирователя 13.3 адресов изменяется. Таким образом, формируется код адреса, который подается на адресный вход блока 13.6 буферной памяти. На выход блока 13.6 буферной памяти считывается символ группового потока, записанный по этому адресу во время восстановления синхронизма. При этом считываемый из буферного запоминающего устройства 13 групповой поток подается на дополнительный канальный распределитель 14, где производится его разделение на соответствующие компонентные потоки. Канальные распределители 10 и 14 осуществляют разделение групповых потоков синхронно, так как управление их работой осуществляется от одного генераторного оборудования 9 приема. В дополнительных блоках 151-15n асинхронного сопряжения производится восстановление первоначальной скорости компонентных цифровых потоков. В дополнительных преобразователях 161-16n кода стыка передачи осуществляется преобразование двоичного кода компонентных цифровых потоков в стыковой код. С выходов дополнительных преобразователей 161-16n стыкового кода передачи восстановленные информационные сигналы в случае необходимости подаются к соответствующим приемникам информации.

Кроме того, код адреса подается на второй вход блока 13.5 сравнения, на первый вход которого с выхода блока 13.4 памяти счета подается код конечного адреса считывания группового потока из блока 13.6 буферной памяти. В блоке 13.5 сравнения производится процедура сравнения поступающих на его входы данных кодов адресов. Их совпадение означает достижение конечного адреса считывания группового цифрового потока с блока 13.6 буферной памяти. При этом на выходе блока 13.5 сравнения формируется сигнал логической «единицы», который подается на первый вход блока 13.1 управления. При этом триггер DD4.2 сбрасывается в нуль. В результате на втором выходе блока 13.1 управления формируется сигнал «запись» для блока 13.6 буферной памяти. Кроме того, во время опознания опознавателем 8.1 синхросигнала истинного синхросигнала на третьем выходе блока 13.1 управления разрешается формирование сигнала «сброс» счетчика 13.2 тактовых импульсов и счетчика-формирователя 13.3 адресов. После этого процесс считывания группового цифрового потока из буферного запоминающего устройства 13 заканчивается, и он продолжает функционировать в соответствии с описанным выше алгоритмом при нахождении приемника 8 циклового синхросигнала в синхронном состоянии.

Таким образом, предлагаемое устройство временного группообразования обеспечивает передачу информации без потерь и в минимальные сроки в условиях сбоя циклового синхронизма за счет записи группового цифрового потока в буферное запоминающее устройство во время сбоя циклового синхронизма, а после восстановления циклового синхронизма - его считывания. С помощью дополнительного канального распределителя n дополнительных блоков асинхронного сопряжения и n дополнительных преобразователей стыкового кода передачи становится возможным правильное разделение считываемого из буферного запоминающего устройства группового цифрового потока по компонентным потокам и предоставление восстановленной информации ее получателю.

Вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного устройства следующей совокупности условий:

- средство, воплощающее заявленное устройство при его осуществлении, может быть использовано в аппаратуре многоканальных цифровых системах передачи с временным разделением каналов;

- для заявленного устройства в том виде, как оно охарактеризовано в формуле изобретения, подтверждена возможность его осуществления с помощью описанных в заявке или известных до даты приоритета средств и методов;

- средство, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата.

Таким образом, заявленное изобретение соответствует критерию «промышленная применимость».

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Система передачи и приема цифровой информации | 1985 |

|

SU1288923A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| СИСТЕМА СИНХРОННОГО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1995 |

|

RU2096916C1 |

| Многоканальное устройство для приема дискретной информации | 1985 |

|

SU1292200A1 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2234195C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1994 |

|

RU2073955C1 |

| МНОГОФУНКЦИОНАЛЬНАЯ СИСТЕМА ПРИЕМА, ДЕМОДУЛЯЦИИ И ОБРАБОТКИ СИГНАЛОВ I-IV УРОВНЕЙ ИЕРАРХИЧЕСКОГО УПЛОТНЕНИЯ | 2001 |

|

RU2224375C2 |

| УСТРОЙСТВО ДЛЯ ОТВЕТВЛЕНИЯ ЦИФРОВЫХ СИГНАЛОВ | 1991 |

|

RU2012144C1 |

| Устройство коммутации дискретных каналов с временным разделением | 1989 |

|

SU1663785A1 |

Изобретение относится к электросвязи и может быть использовано в аппаратуре многоканальных цифровых системах передачи с временным разделением каналов. Устройство содержит в передающей части n преобразователей стыкового кода приема, n блоков асинхронного сопряжения передачи, блок объединения, генераторное оборудование передачи, передатчик циклового синхросигнала, преобразователь линейного кода передачи, а в приемной части преобразователь линейного кода приема, приемник циклового синхросигнала, генераторное оборудование приема, канальный распределитель, состоящий из n элементов И, n блоков асинхронного сопряжения приема, n преобразователей стыкового кода передачи, буферное запоминающее устройство, дополнительный канальный распределитель, n дополнительных блоков асинхронного сопряжения приема и n дополнительных преобразователей стыкового кода передачи. Технический результат, достигаемый при реализации изобретения, состоит в обеспечении передачи информации без потерь и в минимальные сроки в условиях сбоя циклового синхронизма. 1 з.п. ф-лы, 5 ил.

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2234195C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1994 |

|

RU2073955C1 |

| Контактный теплообменник | 1981 |

|

SU1035395A1 |

| US 5398249 A, 14.03.1995. | |||

Авторы

Даты

2007-09-20—Публикация

2006-03-06—Подача