Изобретение относится к электросвязи и может быть использовано для коммутации дискретных каналов с временным разделением в сетях, телеграфной связи, передачи данных и телефонной связи.

Цель изобретения - обеспечение возможности установления циркулярных соединений, а также предотвращение несанкционированного доступа к передаваемой информации при нарушении цикловой синхронизации, а также повышение пропускной способности.

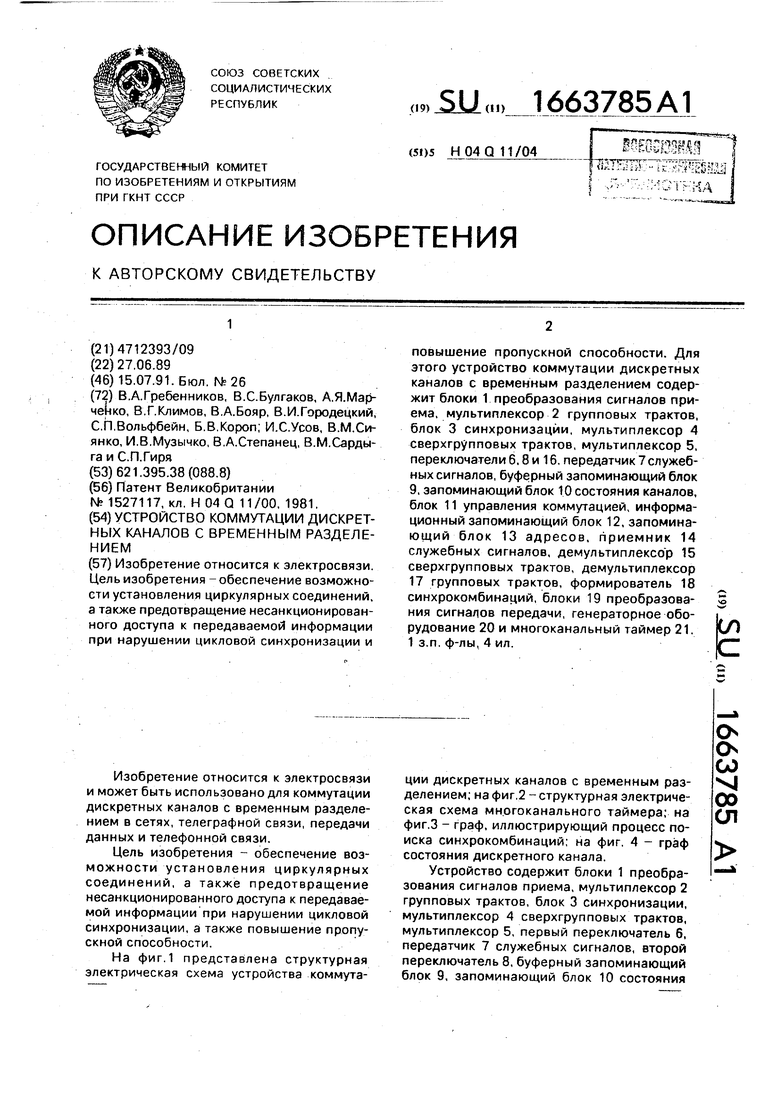

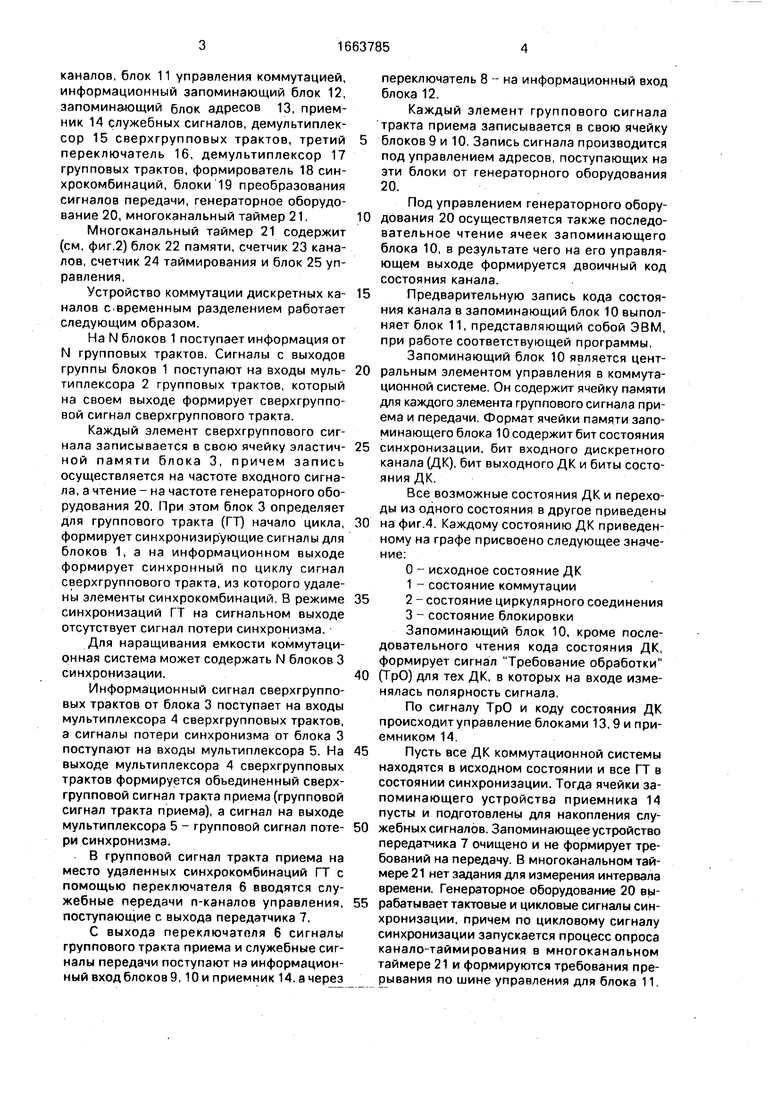

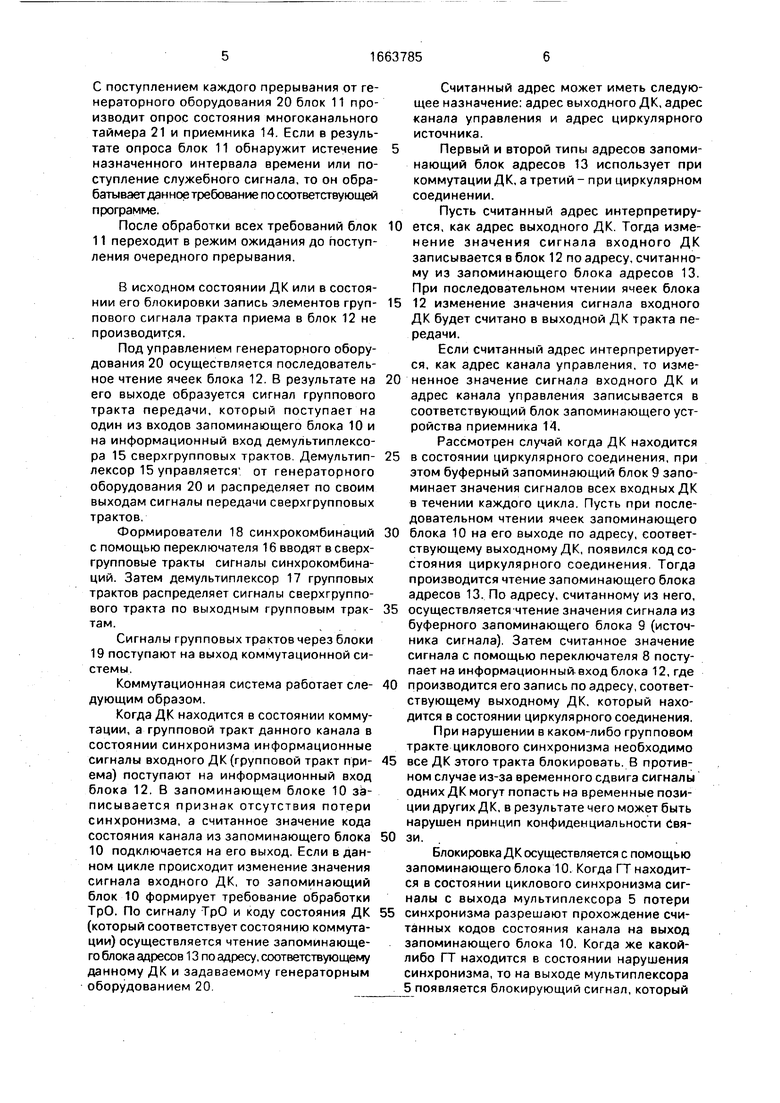

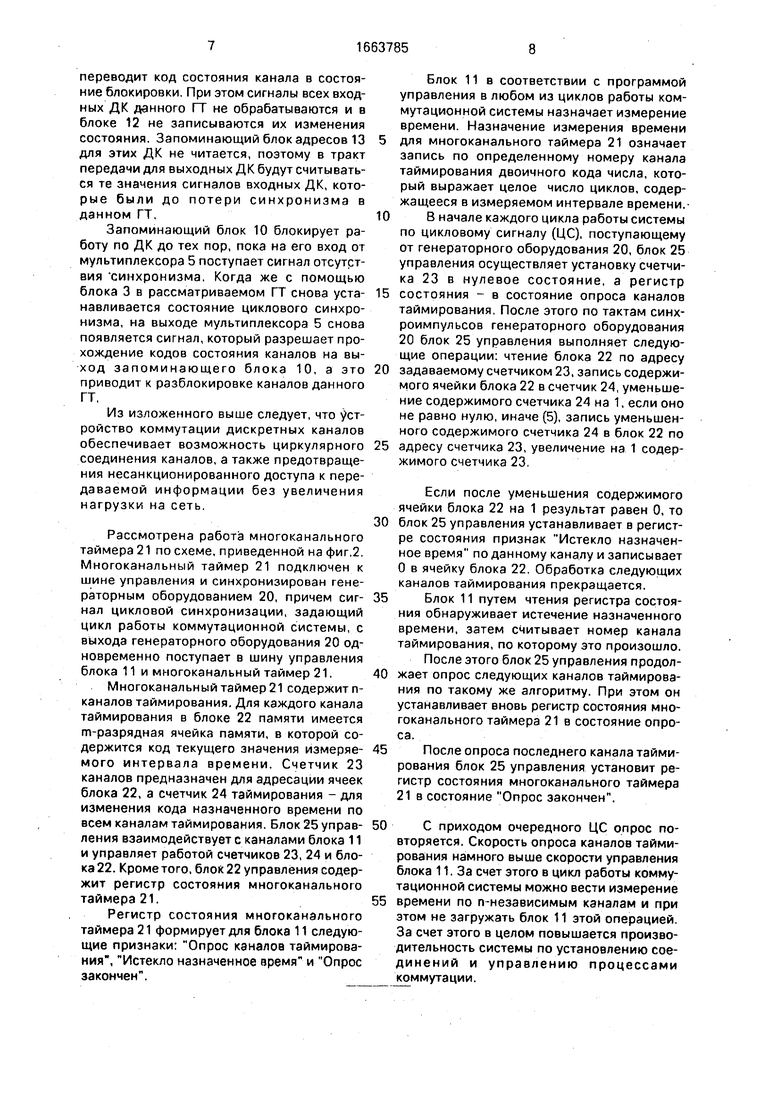

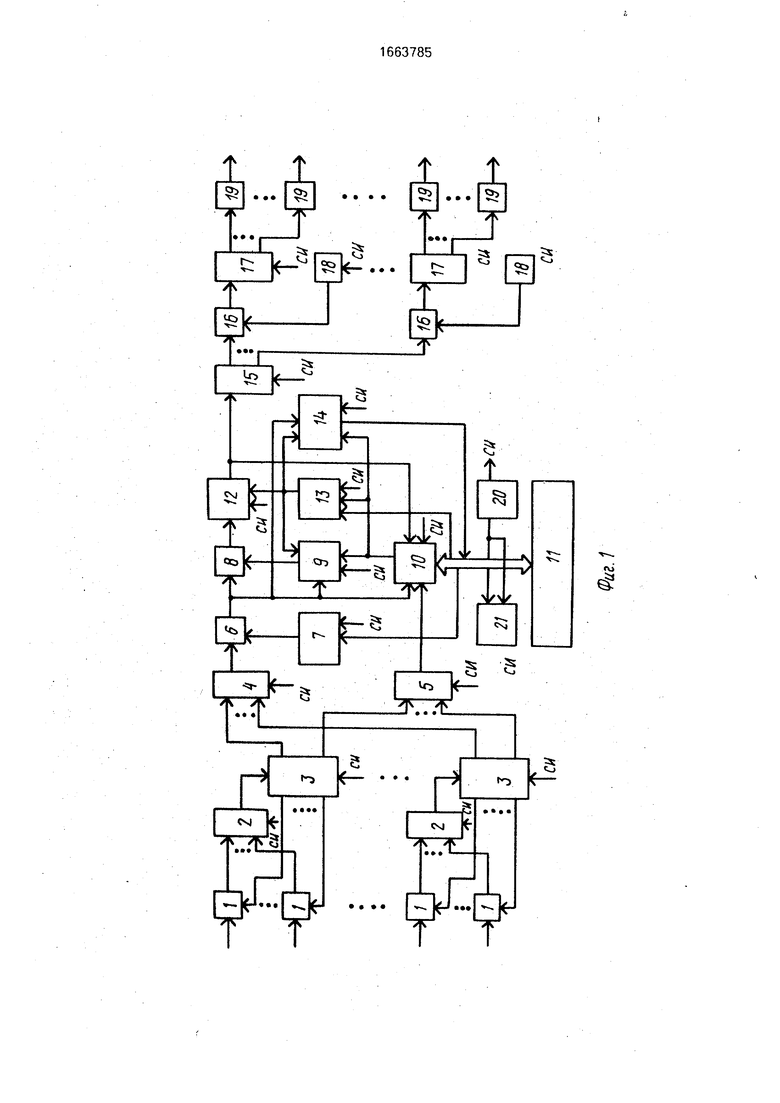

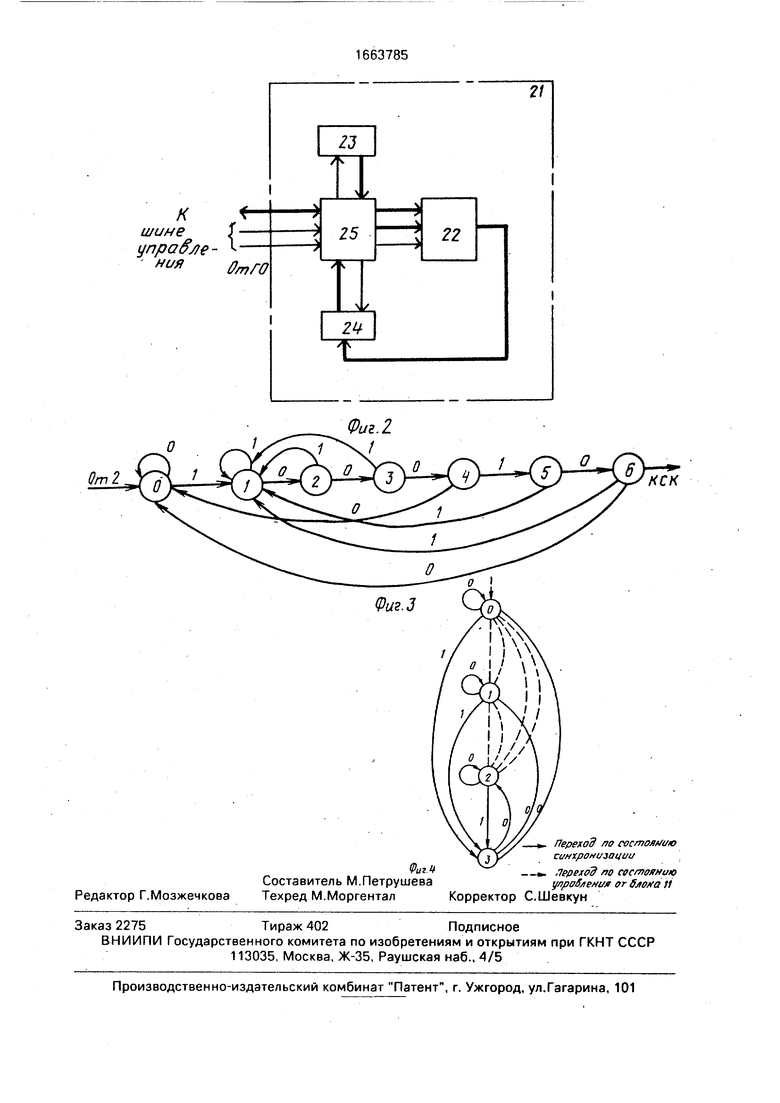

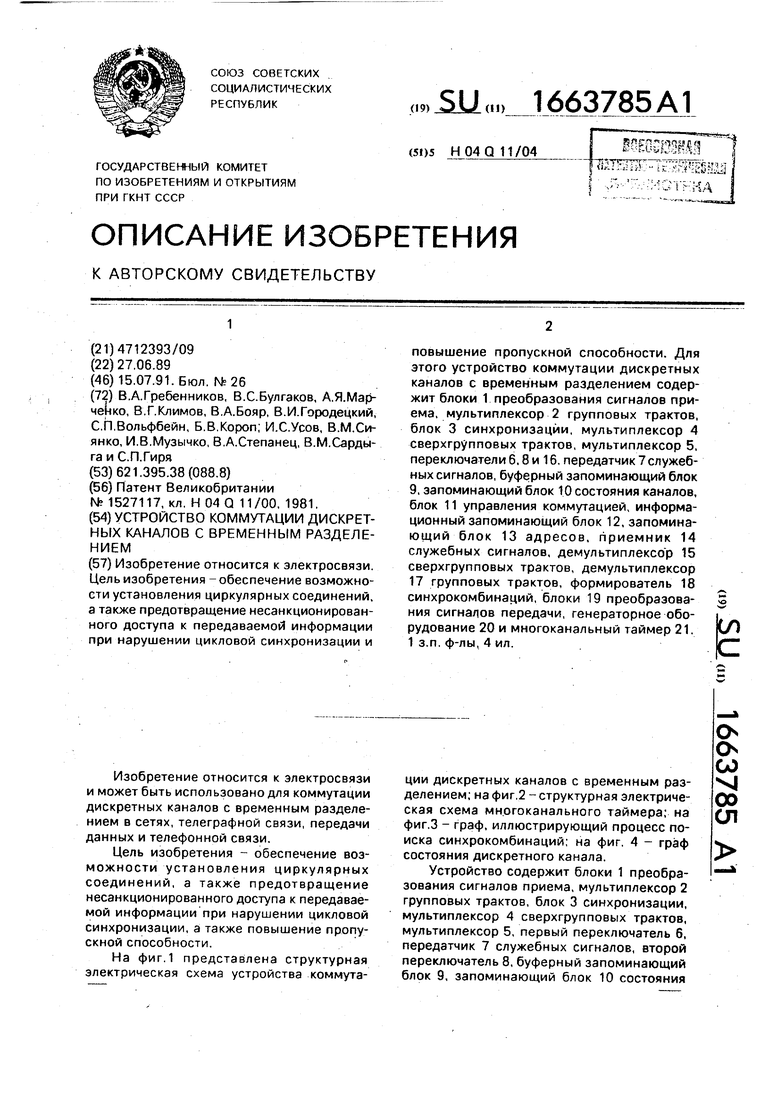

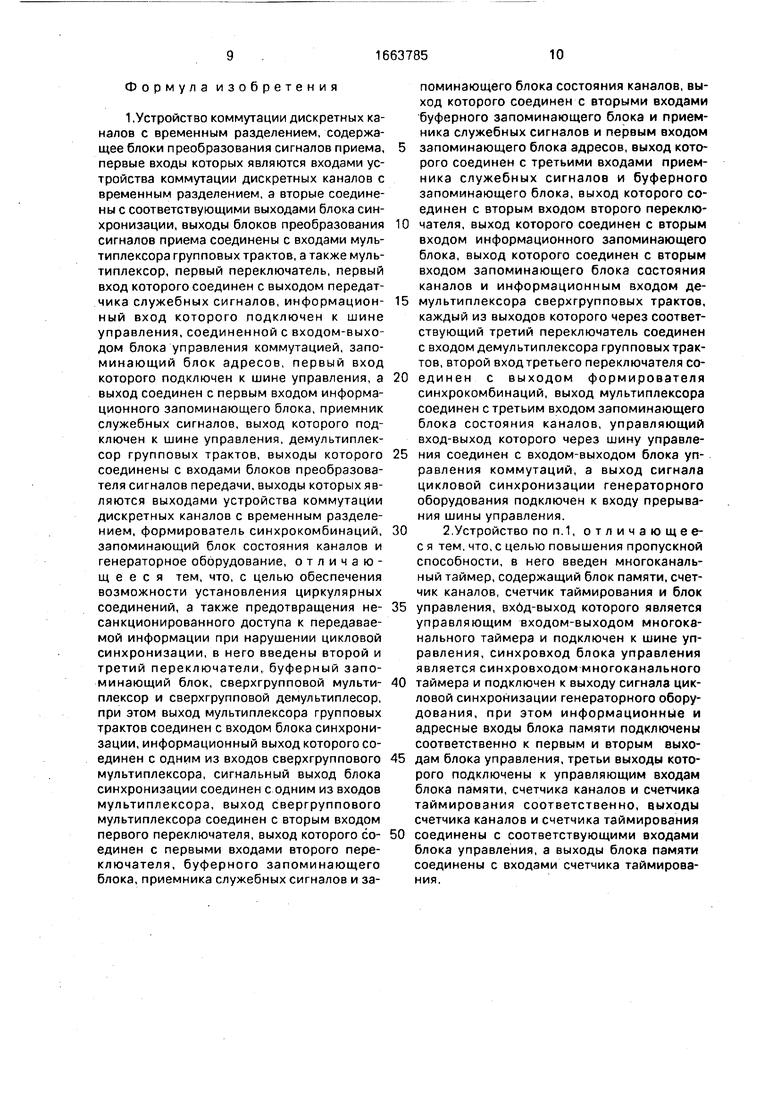

На фиг.1 представлена структурная электрическая схема устройства коммутации дискретных каналов с временным разделением; на фиг,2 - структурная электрическая схема многоканального таймера; на фиг.З - граф, иллюстрирующий процесс поиска синхрокомбинаций; на фиг. 4 - граф состояния дискретного канала.

Устройство содержит блоки 1 преобразования сигналов приема, мультиплексор 2 групповых трактов, блок 3 синхронизации, мультиплексор 4 сверхгрупповых трактов, мультиплексор 5, первый переключатель 6, передатчик 7 служебных сигналов, второй переключатель 8, буферный запоминающий блок 9, запоминающий блок 10 состояния

ON ON OJ VI 00 СЛ

каналов, блок 11 управления коммутацией, информационный запоминающий блок 12, запоминающий блок адресов 13, приемник 14 служебных сигналов, демультиплек- сор 15 сверхгрупповых трактов, третий переключатель 16, демультиплексор 17 групповых трактов, формирователь 18 син- хрокомбинаций, блоки 19 преобразования сигналов передачи, генераторное оборудование 20, многоканальный таймер 21.

Многоканальный таймер 21 содержит (см. фиг,2) блок 22 памяти, счетчик 23 каналов, счетчик 24 таймирования и блок 25 управления.

Устройство коммутации дискретных каналов современным разделением работает следующим образом.

На N блоков 1 поступает информация от N групповых трактов. Сигналы с выходов группы блоков 1 поступают на входы мультиплексора 2 групповых трактов, который на своем выходе формирует сверхгрупповой сигнал сверхгруппового тракта.

Каждый элемент сверхгруппового сигнала записывается в свою ячейку эластичной памяти блока 3, причем запись осуществляется на частоте входного сигнала, а чтение - на частоте генераторного оборудования 20. При этом блок 3 определяет для группового тракта (ГТ) начало цикла, формирует синхронизирующие сигналы для блоков 1, а на информационном выходе формирует синхронный по циклу сигнал сверхгруппового тракта, из которого удалены элементы синхрокомбинаций. В режиме синхронизации ГТ на сигнальном выходе отсутствует сигнал потери синхронизма.

Для наращивания емкости коммутационная система может содержать N блоков 3 синхронизации.

Информационный сигнал сверхгрупповых трактов от блока 3 поступает на входы мультиплексора 4 сверхгрупповых трактов, а сигналы потери синхронизма от блока 3 поступают на входы мультиплексора 5. На выходе мультиплексора 4 сверхгрупповых трактов формируется объединенный сверхгрупповой сигнал тракта приема (групповой сигнал тракта приема), а сигнал на выходе мультиплексора 5 - групповой сигнал потери синхронизма.

В групповой сигнал тракта приема на место удаленных синхрокомбинаций ГТ с помощью переключателя 6 вводятся служебные передачи n-каналов управления, поступающие с выхода передатчика 7,

С выхода переключателя 6 сигналы группового тракта приема и служебные сигналы передачи поступают на информационный вход блоков 9, Юи приемник 14.ачерез

переключатель 8 -- на информационный вход блока 12.

Каждый элемент группового сигнала тракта приема записывается в свою ячейку

блоков 9 и 10. Запись сигнала производится под управлением адресов, поступающих на эти блоки от генераторного оборудования 20.

Под управлением генераторного обору0 дования 20 осуществляется также последовательное чтение ячеек запоминающего блока 10, в результате чего на его управляющем выходе формируется двоичный код состояния канала.

5 Предварительную запись кода состояния канала в запоминающий блок 10 выполняет блок 11, представляющий собой ЭВМ, при работе соответствующей программы. Запоминающий блок 10 является цент0 ральным элементом управления в коммутационной системе. Он содержит ячейку памяти для каждого элемента группового сигнала приема и передачи, Формат ячейки памяти запоминающего блока 10содержит бит состояния

5 синхронизации, бит входного дискретного канала (ДК), бит выходного ДК и биты состояния ДК.

Все возможные состояния ДК и переходы из одного состояния в другое приведены

0 на фиг.4. Каждому состоянию ДК приведенному на графе присвоено следующее значение:

0- исходное состояние ДК

1- состояние коммутации

5 2 - состояние циркулярного соединения 3 - состояние блокировки Запоминающий блок 10, кроме последовательного чтения кода состояния ДК, формирует сигнал Требование обработки

0 (ТрО) для тех ДК, в которых на входе изменялась полярность сигнала,

По сигналу ТрО и коду состояния ДК происходит управление блоками 13,9 и приемником 14.

5 Пусть все ДК коммутационной системы находятся в исходном состоянии и все ГТ в состоянии синхронизации. Тогда ячейки запоминающего устройства приемника 14 пусты и подготовлены для накопления слу0 жебных сигналов. Запоминающее устройство передатчика 7 очищено и не формирует требований на передачу. В многоканальном таймере 21 нет задания для измерения интервала времени. Генераторное оборудование 20 вы5 рабатывает тактовые и цикловые сигналы синхронизации, причем по цикловому сигналу синхронизации запускается процесс опроса канало-таймирования в многоканальном таймере 21 и формируются требования прерывания по шине управления для блока 11.

С поступлением каждого прерывания от генераторного оборудования 20 блок 11 производит опрос состояния многоканального таймера 21 и приемника 14. Если в результате опроса блок 11 обнаружит истечение назначенного интервала времени или поступление служебного сигнала, то он обрабатывает данное требование по соответствующей программе.

После обработки всех требований блок 11 переходит в режим ожидания до поступления очередного прерывания.

В исходном состоянии ДК или в состоянии его блокировки запись элементов группового сигнала тракта приема в блок 12 не производится.

Под управлением генераторного оборудования 20 осуществляется последовательное чтение ячеек блока 12. В результате на его выходе образуется сигнал группового тракта передачи, который поступает на один из входов запоминающего блока 10 и на информационный вход демультиплексо- ра 15 сверхгрупповых трактов. Демультип- лексор 15 управляется от генераторного оборудования 20 и распределяет по своим выходам сигналы передачи сверхгрупповых трактов.

Формирователи 18 синхрокомбинаций с помощью переключателя 16 вводят в сверхгрупповые тракты сигналы синхрокомбинаций. Затем демультиплексор 17 групповых трактов распределяет сигналы сверхгруппового тракта по выходным групповым трактам.

Сигналы групповых трактов через блоки 19 поступают на выход коммутационной системы.

Коммутационная система работает следующим образом.

Когда ДК находится в состоянии коммутации, а групповой тракт данного канала в состоянии синхронизма информационные сигналы входного ДК (групповой тракт приема) поступают на информационный вход блока 12. В запоминающем блоке 10 записывается признак отсутствия потери синхронизма, а считанное значение кода состояния канала из запоминающего блока 10 подключается на его выход. Если в данном цикле происходит изменение значения сигнала входного ДК, то запоминающий блок 10 формирует требование обработки ТрО. По сигналу ТрО и коду состояния ДК (который соответствует состоянию коммутации) осуществляется чтение запоминающего блока адресов 13 по адресу, соответствующему данному ДК и задаваемому генераторным оборудованием 20.

Считанный адрес может иметь следующее назначение: адрес выходного ДК, адрес канала управления и адрес циркулярного источника.

5Первый и второй типы адресов запоминающий блок адресов 13 использует при коммутации ДК, а третий - при циркулярном соединении.

Пусть считанный адрес интерпретиру10 ется, как адрес выходного ДК. Тогда изменение значения сигнала входного ДК записывается в блок 12 по адресу, считанному из запоминающего блока адресов 13. При последовательном чтении ячеек блока

15 12 изменение значения сигнала входного ДК будет считано в выходной ДК тракта передачи.

Если считанный адрес интерпретируется, как адрес канала управления, то изме20 ненное значение сигнала входного ДК и адрес канала управления записывается в соответствующий блок запоминающего устройства приемника 14,

Рассмотрен случай когда ДК находится

5 в состоянии циркулярного соединения, при этом буферный запоминающий блок 9 запоминает значения сигналов всех входных ДК в течении каждого цикла. Пусть при последовательном чтении ячеек запоминающего

0 блока 10 на его выходе по адресу, соответствующему выходному ДК, появился код состояния циркулярного соединения. Тогда производится чтение запоминающего блока адресов 13. По адресу, считанному из него,

5 осуществляется чтение значения сигнала из буферного запоминающего блока 9 (источника сигнала). Затем считанное значение сигнала с помощью переключателя 8 поступает на информационныЛвход блока 12, где

0 производится его запись по адресу, соответствующему выходному ДК. который находится в состоянии циркулярного соединения. При нарушении в каком-либо групповом тракте циклового синхронизма необходимо

5 все ДК этого тракта блокировать. В противном случае из-за временного сдвига сигналы одних ДК могут попасть на временные позиции других ДК, в результате чего может быть нарушен принцип конфиденциальности свя0 зи.

Блокировка ДК осуществляется с помощью запоминающего блока 10. Когда ПГ находится в состоянии циклового синхронизма сигналы с выхода мультиплексора 5 потери

5 синхронизма разрешают прохождение считанных кодов состояния канала на выход запоминающего блока 10. Когда же какой- либо ГТ находится в состоянии нарушения синхронизма, то на выходе мультиплексора 5 появляется блокирующий сигнал, который

переводит код состояния канала в состояние блокировки. При этом сигналы всех входных ДК данного ГТ не обрабатываются и в блоке 12 не записываются их изменения состояния. Запоминающий блок адресов 13 для этих ДК не читается, поэтому в тракт передачи для выходных ДК будут считываться те значения сигналов входных ДК, которые были до потери синхронизма в данном ГТ.

Запоминающий блок 10 блокирует работу по ДК до тех пор, пока на его вход от мультиплексора 5 поступает сигнал отсутствия синхронизма. Когда же с помощью блока 3 в рассматриваемом ГТ снова устанавливается состояние циклового синхронизма, на выходе мультиплексора 5 снова появляется сигнал, который разрешает прохождение кодов состояния каналов на выход запоминающего блока 10, а это приводит к разблокировке каналов данного ГТ,

Из изложенного выше следует, что устройство коммутации дискретных каналов обеспечивает возможность циркулярного соединения каналов, а также предотвращения несанкционированного доступа к передаваемой информации без увеличения нагрузки на сеть.

Рассмотрена работа многоканального таймера 21 по схеме, приведенной на фиг.2. Многоканальный таймер 21 подключен к шине управления и синхронизирован генераторным оборудованием 20, причем сигнал цикловой синхронизации, задающий цикл работы коммутационной системы, с выхода генераторного оборудования 20 одновременно поступает в шину управления блока 11 и многоканальный таймер 21.

Многоканальный таймер 21 содержит п- каналовтаймирования. Для каждого канала таймирования в блоке 22 памяти имеется m-разрядная ячейка памяти, в которой содержится код текущего значения измеряемого интервала времени. Счетчик 23 каналов предназначен для адресации ячеек блока 22, а счетчик 24 таймирования - для изменения кода назначенного времени по всем каналам таймирования. Блок 25 управления взаимодействует с каналами блока 11 и управляет работой счетчиков 23, 24 и блока 22. Кроме того, блок 22 управления содержит регистр состояния многоканального таймера 21.

Регистр состояния многоканального таймера 21 формирует для блока 11 следующие признаки: Опрос каналов таймирования, Истекло назначенное время и Опрос закончен.

Блок 11 в соответствии с программой управления в любом из циклов работы коммутационной системы назначает измерение времени. Назначение измерения времени

для многоканального таймера 21 означает запись по определенному номеру канала таймирования двоичного кода числа, который выражает целое число циклов, содержащееся в измеряемом интервале времени.В начале каждого цикла работы системы по цикловому сигналу (ЦС), поступающему от генераторного оборудования 20, блок 25 управления осуществляет установку счетчика 23 в нулевое состояние, а регистр

состояния - в состояние опроса каналов таймирования. После этого по тактам синхроимпульсов генераторного оборудования

20блок 25 управления выполняет следующие операции: чтение блока 22 по адресу

задаваемому счетчиком 23, запись содержимого ячейки блока 22 в счетчик 24, уменьшение содержимого счетчика 24 на 1, если оно не равно нулю, иначе (5), запись уменьшенного содержимого счетчика 24 в блок 22 по

адресу счетчика 23, увеличение на 1 содержимого счетчика 23,

Если после уменьшения содержимого ячейки блока 22 на 1 результат равен 0, то

блок 25 управления устанавливает в регистре состояния признак Истекло назначенное время по данному каналу и записывает О в ячейку блока 22. Обработка следующих каналов таймирования прекращается.

Блок 11 путем чтения регистра состояния обнаруживает истечение назначенного времени, затем считывает номер канала таймирования, по которому это произошло. После этого блок 25 управления продолжает опрос следующих каналов таймирования по такому же алгоритму. При этом он устанавливает вновь регистр состояния многоканального таймера 21 в состояние опроса.

После опроса последнего канала таймирования блок 25 управления установит регистр состояния многоканального таймера

21в состояние Опрос закончен.

С приходом очередного ЦС опрос повторяется. Скорость опроса каналов таймирования намного выше скорости управления блока 11. За счет этого в цикл работы коммутационной системы можно вести измерение

времени по n-независимым каналам и при этом не загружать блок 11 этой операцией. За счет этого в целом повышается производительность системы по установлению соединений и управлению процессами коммутации.

Формула изобретения

1 .Устройство коммутации дискретных каналов с временным разделением, содержащее блоки преобразования сигналов приема, первые входы которых являются входами устройства коммутации дискретных каналов с временным разделением, а вторые соединены с соответствующими выходами блока синхронизации, выходы блоков преобразования сигналов приема соединены с входами мультиплексора групповых трактов, а также мультиплексор, первый переключатель, первый вход которого соединен с выходом передатчика служебных сигналов, информационный вход которого подключен к шине управления, соединенной с входом-выходом блока управления коммутацией, запоминающий блок адресов, первый вход которого подключен к шине управления, а выход соединен с первым входом информационного запоминающего блока, приемник служебных сигналов, выход которого подключен к шине управления, демультиплек- сор групповых трактов, выходы которого соединены с входами блоков преобразователя сигналов передачи, выходы которых являются выходами устройства коммутации дискретных каналов с временным разделением, формирователь синхрокомбинаций, запоминающий блок состояния каналов и генераторное оборудование, отличающееся тем, что, с целью обеспечения возможности установления циркулярных соединений, а также предотвращения несанкционированного доступа к передаваемой информации при нарушении цикловой синхронизации, в него введены второй и третий переключатели, буферный запоминающий блок, сверхгрупповой мультиплексор и сверхгрупповой демультиплесор, при этом выход мультиплексора групповых трактов соединен с входом блока синхронизации, информационный выход которого соединен с одним из входов сверхгруппового мультиплексора, сигнальный выход блока синхронизации соединен с одним из входов мультиплексора, выход свергруппового мультиплексора соединен с вторым входом первого переключателя, выход которого соединен с первыми входами второго переключателя, буферного запоминающего блока, приемника служебных сигналов и запоминающего блока состояния каналов, выход которого соединен с вторыми входами буферного запоминающего блока и приемника служебных сигналов и первым входом 5 запоминающего блока адресов, выход которого соединен с третьими входами приемника служебных сигналов и буферного запоминающего блока, выход которого соединен с вторым входом второго переклю10 чателя, выход которого соединен с вторым входом информационного запоминающего блока, выход которого соединен с вторым входом запоминающего блока состояния каналов и информационным входом де5 мультиплексора сверхгрупповых трактов, каждый из выходов которого через соответствующий третий переключатель соединен с входом демультиплексора групповых трактов, второй вход третьего переключателя со0 единен с выходом формирователя синхрокомбинаций, выход мультиплексора соединен с третьим входом запоминающего блока состояния каналов, управляющий вход-выход которого через шину управле5 ния соединен с входом-выходом блока управления коммутаций, а выход сигнала цикловой синхронизации генераторного оборудования подключен к входу прерывания шины управления.

0 2.Устройство поп.1, отличающее- с я тем, что, с целью повышения пропускной способности, в него введен многоканальный таймер, содержащий блок памяти, счетчик каналов, счетчик таймирования и блок

5 управления, вход-выход которого является управляющим входом-выходом многоканального таймера и подключен к шине управления, синхровход блока управления является синхровходом многоканального

0 таймера и подключен к выходу сигнала цикловой синхронизации генераторного оборудования, при этом информационные и адресные входы блока памяти подключены соответственно к первым и вторым выхо5 дам блока управления, третьи выходы которого подключены к управляющим входам блока памяти, счетчика каналов и счетчика таймирования соответственно, выходы счетчика каналов и счетчика таймирования

0 соединены с соответствующими входами блока управления, а выходы блока памяти соединены с входами счетчика таймирования.

t t

t t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации станции коммутации каналов | 1987 |

|

SU1536518A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302084C2 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Устройство для коммутации телеграфных каналов | 1979 |

|

SU866774A1 |

| Система передачи и приема цифровой информации | 1985 |

|

SU1288923A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| Устройство цикловой синхронизации | 1985 |

|

SU1293849A1 |

Изобретение относится к электросвязи. Цель изобретения - обеспечение возможности установления циркулярных соединений, а также предотвращение несанкционированного доступа к передаваемой информации при нарушении цикловой синхронизации и повышение пропускной способности. Для этого устройство коммутации дискретных каналов с временным разделением содержит блоки 1 преобразования сигналов приема, мультиплексор 2 групповых трактов, блок 3 синхронизации, мультиплексор 4 сверхгрупповых трактов, мультиплексор 5, переключатели 6, 8 и 16, передатчик 7 служебных сигналов, буферный запоминающий блок 9, запоминающий блок 10 состояния каналов, блок 11 управления коммутацией, информационный запоминающий блок 12, запоминающий блок 13 адресов, приемник 14 служебных сигналов, демультиплексор 15 сверхгрупповых трактов, демультиплексор 17 групповых трактов, формирователь 18 синхрокомбинаций, блоки 19 преобразования сигналов передачи, генераторное оборудование 20 и многоканальный таймер 21. 1 з.п. ф-лы, 4 ил.

2

&

.. |S

v v

к

«i

СЧ1

Ј

г

СГ5

a

ГЧ

F

r-Tpg

I. I....

e- т

i i

3

5

Ё

(W

.

Zr

s

I K.

evo

ZIVTTL

F

s s

ri

«41

TL -

F

Т

К шине /

упра&ле- ния /7

Фиг. 2

О

Редактор Г.Мозжечкова

. Переход по состоянию синхронизации

Фиг Ч- переход по состоянию

Составитель М.Петрушеваупрабления or бло/ta п

Техред М.МоргенталКорректор С.Шевкун

ИСК

Фиг.З

| Устройство для намотки полотна | 1988 |

|

SU1527117A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-07-15—Публикация

1989-06-27—Подача