Изобретение относится к электросвязи и может быть использовано при асинхронном цифровом группообразовании в многоканальном приемопередающем оборудовании.

Цель уменьшение потерь информации на выходах каналов при перерывах связи.

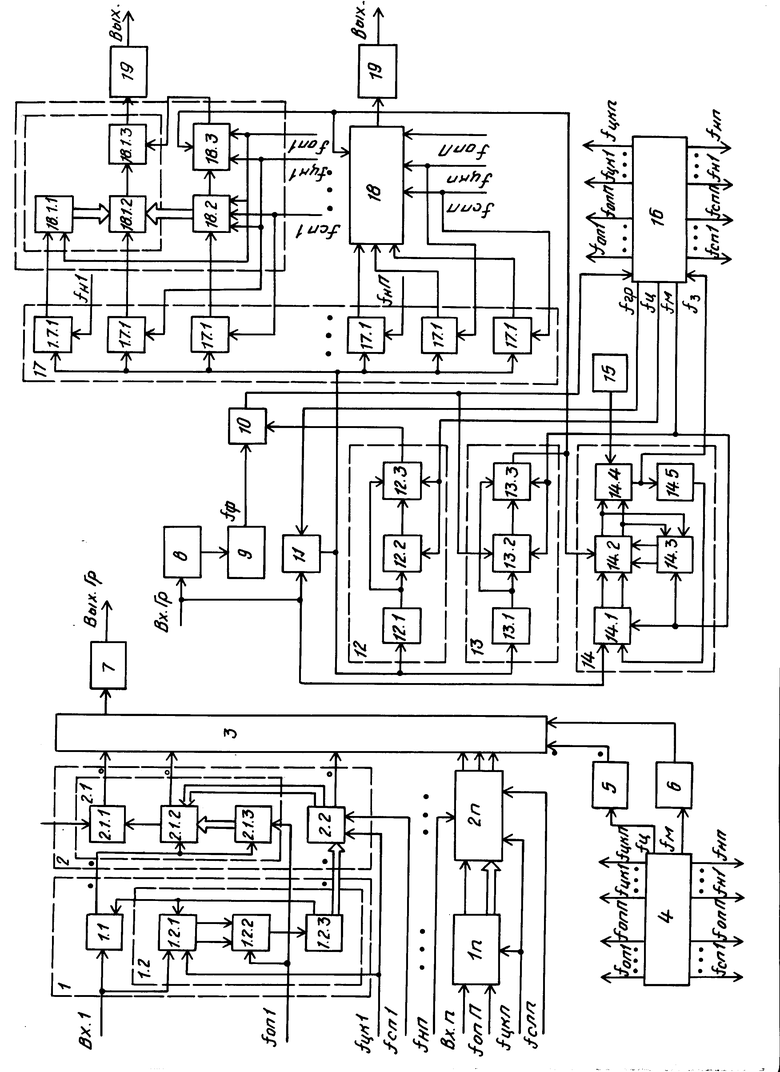

Многоканальное приемопередающее устройство с временным разделением цифровых асинхронных каналов содержит на передающей стороне приемные преобразователи 11-1n кода, содержащие декодер 1.1 и узел 1.2 дискретной фазовой автоподстройки, состоящий из фазового дискриминатора 1.2.1, блока 1.2.3 добавления и исключения импульсов, делителя 1.2.3 частоты, узлы 21-2n асинхронного сопряжения передачи, содержащие запоминающий блок 2.1, состоящий из триггера 2.1.1, мультиплексора 2.1.2, сдвигающего регистра 2.1.3, и преобразователь 2.2 фаза-код, блок 3 объединения, генераторное оборудование 4 передачи, передатчик 5 синхросигнала, формирователь 6 метки, передающий преобразователь 7 кода, на приемной стороне приемный преобразователь 8 кода, приемник 9 синхросигнала, элемент И 10, декодер 11, анализатор 12 состояния синхронизма, состоящий из дешифратора 12.1, Д-триггера 12.2, накопителя 12.3 по выходу из синхронизма, анализатор 13 перерывов, состоящий из дешифратора 13.1, реверсивного счетчика 13.2, Д-триггера 13.3, узел 14 запоминающей фазовой автоподстройки, состоящий из фазового дискриминатора 14.1, селектора 14.2 импульсов, запоминающего блока 14.3, блока 14.4 добавления и исключения импульсов, делителя 14.5 частоты, высокостабильный задающий генератор 15, генераторное оборудование 16 приема, канальный распределитель 17, состоящий из элементов И 17.1, узел 18 асинхронного сопряжения приема, содержащий запоминающий блок 18.1, состоящий из сдвигающего регистра 18.1.1, мультиплексора 18.1.2, Д-триггера 18.1.3, преобразователь 18.2 код-фаза, блок 18.3 запоминающей дискретной фазовой подстройки, передающие преобразователи 191-19n кода.

Многоканальное приемопередающее устройство с временным разделением асинхронных каналов работает следующим образом.

На передаче генераторное оборудование 4 вырабатывает сетку частот, включающую опорные частоты fоп1 fопn для синхронизации коррекций в блоке 1.2 автоподстройки и в запоминающем блоке 2.1, несущие частоты fн1 fнn для синхронизации основной информации, служебные частоты fсл1 fсл для синхронизации сигналов управления выравниванием, частоты цикла канала fцк1 fцкn для синхронизации скоростей указанных коррекций и выравнивающих символов и несущие частоты синхросигнала fц и метки fм.

Информационные сигналы поступают в преобразователи 1 кода, каждый из которых преобразует линейный код в двоичный с помощью декодера 1.1 и тактовой частоты, выделенной блоком 1.2 автоподстройки путем определения в фазовом дискриминаторе 1.2.1 рассогласования фаз информационного сигнала и сигнала с выхода делителя 1.2.3 и соответствующего добавления или исключения импульсов к частоте fоп с помощью блока 1.2.2. Сигнал с выхода декодера 1.1 поступает в блок 2, где с помощью запоминающего блока 2.1 осуществляется двустороннее цифровое выравнивание (стаффинг) его скорости методом управляемой задержки. Эта задержка с дискретностью в период частоты fоп вводится K-разрядным регистром 2.1.3 и мультиплексором 2.1.2 так, чтобы сигнал на входе триггера 2.1.1 и считывающая его частота fн были синхронны, за исключением моментов согласования скорости, когда задержка меняется скачком на период частоты fн. При этом информационные символы, не считанные (пропущенные) триггером 2.1.1, вводятся в групповой сигнал через соответствующий канал мультиплексора 2.1.2. Такое управление задержкой обеспечивает преобразователь 2.2 фаза-код, формирующий для этого K параллельных сигналов, равных числу разрядов делителя 1.2.3. Каждый такой сигнал представляет собой синхронизированное частотой fцк двоичное состояние соответствующего разряда делителя 1.2.3, кроме того, преобразователь 2.2 фаза-код обеспечивает объединение этих параллельных сигналов по ИЛИ, синхронизированное частотой fсп.

Полученные в блоках 2 сигналы, а также синхросигнал, формируемый передатчиком 5 синхросигнала, и сигнал метки, формируемый в виде кодовой комбинации формирователем 6 метки, объединяются по ИЛИ в групповой сигнал с помощью блока 3 объединения. Затем групповой сигнал поступает в преобразователь 7 кода, где приобретает структуру, необходимую для передачи по заданной линии связи.

На приеме генераторное оборудование 16 вырабатывает на основе задающей частоты fз сетку частот, идентичную сетке частот передачи. Синхронность этих сеток частот обеспечивается синхронизацией fз с входным групповым сигналом с помощью узла 14 запоминающей автоподстройки, где в фазовом дискриминаторе 14.1 сравниваются по фазе групповой сигнал и сигнал с выхода делителя 14.5. Результат сравнения в виде сигналов на добавление или исключение импульсов поступает через селектор 14.2 в блок 14.4, осуществляющий соответствующее добавление или исключение импульсов к частоте fз, поступающей с генератора 15 далее на вход делителя 14.5. Кроме того, указанные сигналы поступают на соответствующие входы запоминающего блока 14.3, куда записываются с частотой fм, синхронизирующей одновременно скорость работы фазового дискриминатора 14.1.

При перерыве связи анализатор 14 перерывов через селектор 14.2 обеспечивает подключение к блоку 14.4 вместо сигналов с фазового дискриминатора 14.1 сигналов из запоминающего блока 14.3, благодаря чему удерживается синхронизация сетки частот приема. Анализ перерывов в анализаторе 14 перерывов осуществляется с помощью дешифратора 14.1, обнаруживающего код метки, триггера 13.3, реагирующего на каждый сбой этого кода, и интегратора реверсивного счетчика 13.2, удерживающего триггер 13.3 в состоянии обнаружения перерыва для уменьшения количества его переключений, приводящих к накоплению фазовой ошибки при удержании сетки частот.

Анализатор 12 состояний синхронизма состояния синхронизма обеспечивает через элемент И 10 однократное фазирование генераторного оборудования 16, что снижает вероятность его ложной пересинхронизации сигналом, выделенным приемником 9 из группового сигнала, поступающего с преобразователя 8 кода, и предотвращает сброс анализатора 13 перерывов, необходимый при первоначальном вхождении в синхронизм. Анализ состояния синхронизма осуществляется с помощью дешифратора 12.1, обнаруживающего код синхросигнала, триггера 12.2, обеспечивающего при обнаружении первого правильного кода запрет элемента И 10 путем соответствующего сброса накопителя 12.3, обеспечивающего задержку снятия этого запрета при сбоях кода. Декодер 11 производит раскодирование группового сигнала с помощью групповой тактовой частоты fгр, обеспечивающей синфазность информационных символов с сеткой частот приема, после чего групповой сигнал поступает в канальный распределитель 17, где с помощью элементов И 17.1 для каждого канала считываются информационный сигнал на частоте fн, выравнивающие символы на частоте fцк и сигнал управления выравниванием на частоте fсл.

Все указанные сигналы поступают в узел 18 асинхронного сопряжения приема. Сигнал управления выравниванием с помощью преобразователя 18.2 код-фаза разъединяется на составляющие сигналы с частотой fцк, обеспечивающие управление запоминающим блоком 18.1 и синхронизацию тактовой частоты, получаемой делением частоты fоп. Эта тактовая частота отслеживается блоком 18.3 запоминающей автоподстройки, аналогичным блоком 14 с целью подавления скачков фазы при отдельных сбоях в сигнале управления выравниванием и удержания тактовой частоты при перерывах. В блоке 18.1 сдвигающим регистром 18.1.1 и управляемым мультиплексором 18.1.2 вводится задержка информационного сигнала с дискретностью в период частоты fоп так, чтобы сигнал на входе Д-триггера 18.1.3 и считывающая его тактовая частота были синхронны, за исключением моментов согласования скорости, когда задержка меняется скачком на период тактовой частоты. При этом триггер 18.1.3 исключает лишний или добавляет недостающий символ, считывая его через соответствующий канал мультиплексора 18.1.2. Восстановленный таким образом сигнал поступает в преобразователь 19 кода, где приобретает структуру, необходимую для передачи по заданной линии связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| МНОГОФУНКЦИОНАЛЬНАЯ СИСТЕМА ПРИЕМА, ДЕМОДУЛЯЦИИ И ОБРАБОТКИ СИГНАЛОВ I-IV УРОВНЕЙ ИЕРАРХИЧЕСКОГО УПЛОТНЕНИЯ | 2001 |

|

RU2224375C2 |

| Устройство передачи и приема команд согласования скоростей | 1989 |

|

SU1793553A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1994 |

|

RU2073955C1 |

| РАДИОПРИЕМНИК ЦИФРОВОЙ ИНФОРМАЦИИ | 2008 |

|

RU2371845C1 |

| Приемник команд стаффинга | 1982 |

|

SU1075433A1 |

| Устройство преобразования сигналов для каналов тональной частоты | 1989 |

|

SU1709551A1 |

Использование: электросвязь, точнее асинхронное цифровое преобразование в многоканальном приемопередающем оборудовании. Сущность изобретения: устройство содержит на передающей стороне: приемные преобразователи кода, узлы асинхронного сопряжения передачи, блок объединения, генераторное оборудование передачи, передатчик синхросигнала, формирователь метки, передающий преобразователь кода, на приемной стороне: приемный преобразователь кода, приемник синхросигнала, элемент И, декодер, анализатор состояния синхронизма, анализатор перерывов, узел запоминающей фазовой автоподстройки, высокостабильный задающий генератор, генераторное оборудование приема, канальный распределитель, узел асинхронного сопряжения приема, передающие преобразователи кода. Устройство обеспечивает обрывоустойчивость циклового синхронизма как собственную, так и абонентов цифровых каналов за счет удержания тактовых частот и использования для цифрового выравнивания скоростей в запоминающих блоках устройства метода управляемых задержек, позволяющего избежать необратимых проскальзываний при сбоях сигналов управления выравниванием. 1 ил.

МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ, содержащее на передающей стороне n узлов асинхронного сопряжения передачи, к первому и второму входам каждого из которых подключены выход соответствующего приемного преобразователя кода и соответствующий выход сигнала несущей частоты fн генератор оборудования передачи, а первый и второй выходы каждого узла асинхронного сопряжения передачи подключены к соответствующим первым входам блока объединения, к второму входу которого через передатчик синхросигнала подключен выход сигнала частоты цикла fц генераторного оборудования передачи, а выход блока объединения подключен к входу передающего преобразователя кода, при этом каждый узел асинхронного сопряжения передачи содержит запоминающий блок, первый и второй входы которого являются первым и вторым входами узла асинхронного сопряжения передачи, а на приемной стороне приемный преобразователь кода, выход которого подключен к входу приемника синхросигнала, канальный распределитель, генераторное оборудование приема и n узлов асинхронного сопряжения приема, выход каждого из которых соединен с входом преобразователя кода, при этом каждый узел асинхронного сопряжения приема содержит запоминающий блок, выход которого является выходом узла асинхронного сопряжения приема, отличающееся тем, что, с целью уменьшения потери информации на выходах каналов при перерывах связи, введены на передающей стороне формирователь метки, к входу которого подключен дополнительный выход сигнала частоты метки fм генераторного оборудования передачи, выход формирователя метки подключен к дополнительному входу блока объединения и в каждый узел асинхронного сопряжения передачи введен преобразователь фаза код, а каждый приемный преобразователь кода на передающей стороне содержит декодер и блок дискретной фазовой автоподстройки, первый вход которого соединен с первым входом декодера и является первым входом приемного преобразователя кода и соответствующим входом устройства, при этом выход блока дискретной фазовой автоподстройки подключен к второму входу декодера, выход которого является первым выходом каждого приемного преобразователя кода, а к второму входу блока дискретной фазовой автоподстройки каждого приемного преобразователя кода и третьему входу запоминающего блока каждого узла асинхронного сопряжения подключен соответствующий выход сигнала опорной частоты fоп генераторного оборудования передачи, выход частоты цикла fцк канала которого подключены соответственно к третьим входам блоков дискретной фазовой подстройки соответствующих приемных преобразователей кода и первым входам преобразователей фаза код соответствующих узлов асинхронного сопряжения передачи, причем выходы сигнала служебной частоты fсл генераторного оборудования подключены к вторым входам преобразователей фаза - код соответствующих узлов асинхронного сопряжения передачи, а группа выходов блоков дискретной фазовой автоподстройки каждого приемного преобразователя кода подключена к группе входов соответствующего преобразователя фаза код, выходы которых подключены к дополнительным первым входам блока объединения, а группа выходов преобразователя фаза код подключена к группе входов соответствующего запоминающего блока, а на приемной стороне декодер, анализатор состояния синхронизма, анализатор перерывов, блок памяти дискретной фазовой автоподстройки, элемент И, высокостабильный задающий генератор, в каждый узел асинхронного сопряжения приема введены преобразователь код фаза и блок памяти дискретной фазовой автоподстройки, при этом первый вход декодера соединен с входом приемного преобразователя кода и первым входом блока памяти дискретной фазовой автоподстройки, к второму входу декодера подключен выход сигнала групповой частоты fгр генераторного оборудования приема, а выход декодера подключен к первым входам элементов И канального распределителя и к первым входам анализатора перерывов и анализатора состояния синхронизма, к второму входу которого подключен выход сигнала частоты цикла fц генераторного оборудования приема, а выходы анализатора состояния синхронизма подключены соответственно к первому и второму входам элемента И, выход которого подключен к входу генераторного оборудования приема и к второму входу анализатора перерывов, к третьему входу которого и второму входу первого блока памяти дискретной фазовой автоподстройки подключен выход сигнала частоты метки fм генераторного оорудования приема, а выход анализатора перерывов подключен к третьему входу блока памяти дискретной фазовой автоподстройки и первым входам блоков памяти дискретной фазовой автоподстройки соответствующих узлов асинхронного сопряжения приема, причем выход высокостабильного задающего генератора подключен к четвертому входу блока памяти дискретной фазовой автоподстройки, выход которого подключен к входу сигнала задающей частоты fз генераторного оборудования приема, в каждом узле асинхронного сопряжения приема к первому и второму входам запоминающего блока и первому входу преобразователя код фаза подключены выходы соответствующих элементов И канального распределителя, причем к вторым входам первых элементов И подключены соответствующие выходы сигналов несущей частоты генераторного оборудования приема, к вторым входам вторых элементов И канального распределителя соединенным со вторыми входами преобразователей код фаза и блока памяти дискретной фазовой автоподстройки подключены соответственно выходы сигнала частоты цикла канала fцк генераторного оборудования приема, выходы сигналов служебной частоты fсл которого подключены к вторым входам третьих элементов И канального распределителя и третьим входам преобразователей код фаза каждого блока асинхронного сопряжения приема, к третьим входам блоков памяти дискретной фазовой автоподстройки которых, а также к четвертым входам преобразователей код фаза и третьему входу запоминающего блока подключены соответствующие выходы сигнала опорной частоты fоп генераторного оборудования приема, а выход и группа выходов преобразователя код фаза подключены соответственно к четвертому входу блока памяти дискретной фазовой автоподстройки и группе входов запоминающего блока каждого узла асинхронного сопряжения приема, выход блока памяти дискретной фазовой автоподстройки которого подключен к четвертому входу запоминающего блока.

| Левин Л.С | |||

| и Плоткин М.А | |||

| Цифровые системы передачи информации | |||

| М.: Сов.радио, 1982, с.53-59, рис.3.2. |

Авторы

Даты

1995-04-20—Публикация

1989-04-11—Подача