Предлагаемое устройство относится к области радиотехники и может найти применение при построении систем радиосвязи, радионавигации, управления, использующих широкополосные сигналы.

Известны устройства поиска широкополосных сигналов (см. а.с. №1003372, Н04L 7/02, 1981 г.; №809619 Н04L 7/02, 1979 г.), которым присущ общий недостаток, заключающийся в низкой помехоустойчивости поиска широкополосных сигналов (ШПС) по задержке, а именно в большой вероятности синхронизации устройств на структурные помехи.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в патенте №2223606, Н04В 1/10, Н04L 7/02, принятое за прототип.

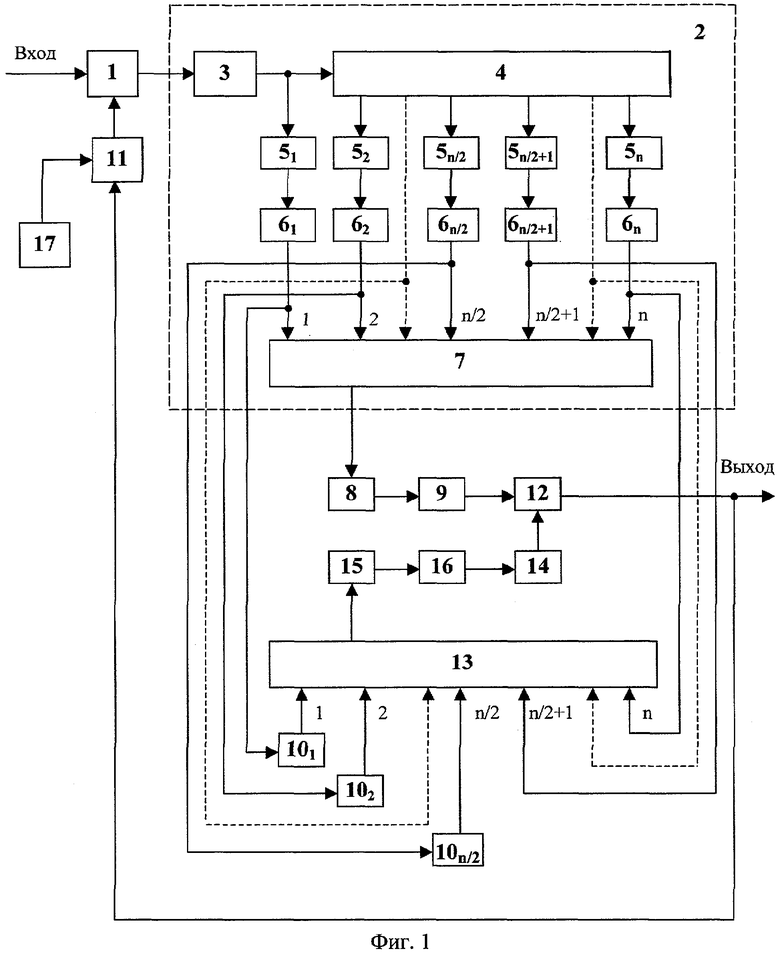

На фиг.1 изображена блок-схема устройства-прототипа, где приведены следующие обозначения:

1 - линейная часть;

2 - согласованный фильтр;

3 - предварительный фильтр;

4 - линия задержки;

51-5n - первый, ..., n-й аттенюаторы;

61-6n - первый, ..., n-й фазовращатели;

7 и 13 - первый и второй сумматоры;

8 и 15 - первый и второй детекторы;

9 и 16 - первый и второй блоки сравнения с порогом;

101-10n/2 - первый, ..., n/2-й инверторы;

11 - блок управления переключением каналов;

12 - элемент И;

14 - элемент НЕ;

17 - генератор тактовых импульсов.

Устройство-прототип имеет следующие функциональные связи: последовательно соединенные линейную часть 1, первый, сигнальный вход которой является входом устройства, и согласованный фильтр 2; последовательно соединенные генератор тактовых импульсов 17 и блок управления переключением каналов 11, выход которого соединен со вторым, управляющим входом линейной части 1. При этом согласованный фильтр 2 содержит последовательно соединенные предварительный фильтр 3, вход которого является также и входом согласованного фильтра 2, и линию задержки 4, (n-1) выходов которой (где n - четное число) соединены соответственно с входами со второго по n-й аттенюаторов 52-5n, выходы которых соединены соответственно с входами со второго по n-й фазовращателей 62-6n, выходы которых соединены со второго по n-й входами первого сумматора 7 соответственно, а вход линии задержки 4 через последовательно соединенные первый аттенюатор 51 и первый фазовращатель 61 соединен с первым входом первого сумматора 7, выход которого является также и выходом согласованного фильтра 2, подключенным к последовательно соединенным первому детектору 8, первому блоку сравнения с порогом 9 и элементу И 12, выход которого является выходом устройства, соединенным с первым, управляющим входом блока управления переключением каналов 11. Кроме того, выходы с первого по n/2-й фазовращателей 61-6n/2 через соответствующие с первого по n/2-й инверторы 101-10n/2 соединены с первой группой n/2 входов второго сумматора 13 соответственно, а выходы с (n/2+1)-го по n-й фазовращателей 6n/2+1-6n соединены соответственно со второй группой n/2 входов второго сумматора 13, выход которого через последовательно соединенные второй детектор 15, второй блок сравнения с порогом 16 и элемент НЕ 14 соединен со вторым входом элемента И 12.

Устройство-прототип работает следующим образом.

На первый, сигнальный вход блока 1, являющийся входом устройства, поступает сигнал, структурная помеха или их смесь. С выхода блока 1 сигнал поступает на вход блока 2, где через блок 3 подается на вход блока 4. С входа блока 4 и с его n-1 выходов сигнал через соответствующие последовательно соединенные блоки 51-5n и блоки 61-6n поступает на соответствующие n входы блока 7. При этом параметры блока 4, блоков 51-5n и блоков 61-6n выбираются таким образом, что на выходе блока 7 элементы сигнала складываются в фазе и дают значение автокорреляционной функции (АКФ) полезного сигнала, а на выходе блока 8 будет значение огибающей АКФ полезного сигнала. Превышение порога в блоке 9 приводит к тому, что на первый вход блока 12 поступит логическая единица.

Одновременно с выходов n/2 фазовращателей 6n/2+1-6n сигналы поступают на вторую группу n/2 входов блока 13 соответственно, а с выходов n/2 фазовращателей 61-6n/2 через соответствующие инверторы 101-10n/2 на соответствующую первую группу n/2 входов блока 13 поступают сигналы с противоположной фазой. Это приводит к тому, что значение АКФ сигнала на выходе блока 13 будет близко к нулю. Значит, значение огибающей АКФ на выходе блока 15 будет близкое к нулю. Соответственно, не будет превышен порог в блоке 16 и с выхода блока 14 на второй вход блока 12 поступит логическая единица. Следовательно, с выхода блока 12 выйдет логическая единица и поступит на первый, управляющий вход блока 11, что приведет к фиксации данного канала, так как формирование логической единицы на выходе блока 12 означает, что сигнал найден и поиск закончен.

Если на первый, сигнальный вход блока 1 поступит смесь полезного сигнала и мощной структурной помехи, то, как и в случае только с полезным сигналом, превышение порога суммой огибающих функций автокорреляции сигнала (АКФ) и функции взаимной автокорреляции сигнала и помехи (ВКФ) в блоке 9 приведет к поступлению на второй вход блока 12 логической единицы. Вероятность того, что в этот же момент значение ВКФ не превысит порог в блоке 16, достаточно мала. Таким образом, на первый вход элемента И 12 поступит логический нуль и на входе блока 11 будет логический нуль, означающий, что сигнал не найден, переключение каналов может быть продолжено, поиск полезного сигнала не закончен.

Но при большом уровне помехи не имеет смысла производить обнаружение полезного сигнала на данном канале, так как заведомо он не может быть принят, даже если удастся его обнаружить.

Недостатком устройства-прототипа является большое время поиска при воздействии помех естественного фона высокого уровня.

Для устранения указанного недостатка в устройство поиска широкополосных сигналов, содержащее генератор тактовых импульсов, линейную часть, первый, сигнальный вход которой является входом устройства, а выход линейной части соединен с входом согласованного фильтра, содержащего последовательно соединенные предварительный фильтр, вход которого является входом согласованного фильтра, и линию задержки, (n-1) выходов которой (где n - четное число) соединены соответственно с входами со второго по n-й аттенюаторов, выходы которых соединены соответственно с входами со второго по n-й фазовращателей, выходы которых соединены со второго по n-й входами первого сумматора соответственно, кроме того, вход линии задержки через последовательно соединенные первый аттенюатор и первый фазовращатель соединен с первым входом первого сумматора, выход которого, являющийся также и выходом согласованного фильтра, подключен к последовательно соединенным первому детектору, первому блоку сравнения с порогом и элементу И, выход которого является выходом устройства; кроме того, выходы с первого по n/2-й фазовращателей через соответствующие с первого по n/2-й инверторы соединены с первой группой n/2 входов второго сумматора соответственно, а выходы с (n/2+1)-го по n-й фазовращателей соединены соответственно со второй группой n/2 входов второго сумматора, выход которого через последовательно соединенные второй детектор, второй блок сравнения с порогом и элемент НЕ соединен со вторым входом элемента И, согласно изобретению введены блок анализа помеховой обстановки, логический блок и блок управления, при этом выход линейной части соединен с входом блока анализа помеховой обстановки, выход которого соединен с первыми входами логического блока и блока управления, второй, синхронизирующий вход которого соединен с выходом генератора тактовых импульсов; выход элемента И соединен с третьим, управляющим входом блока управления, выход которого соединен со вторым, управляющим входом логического блока, выход которого соединен со вторым, управляющим входом линейной части.

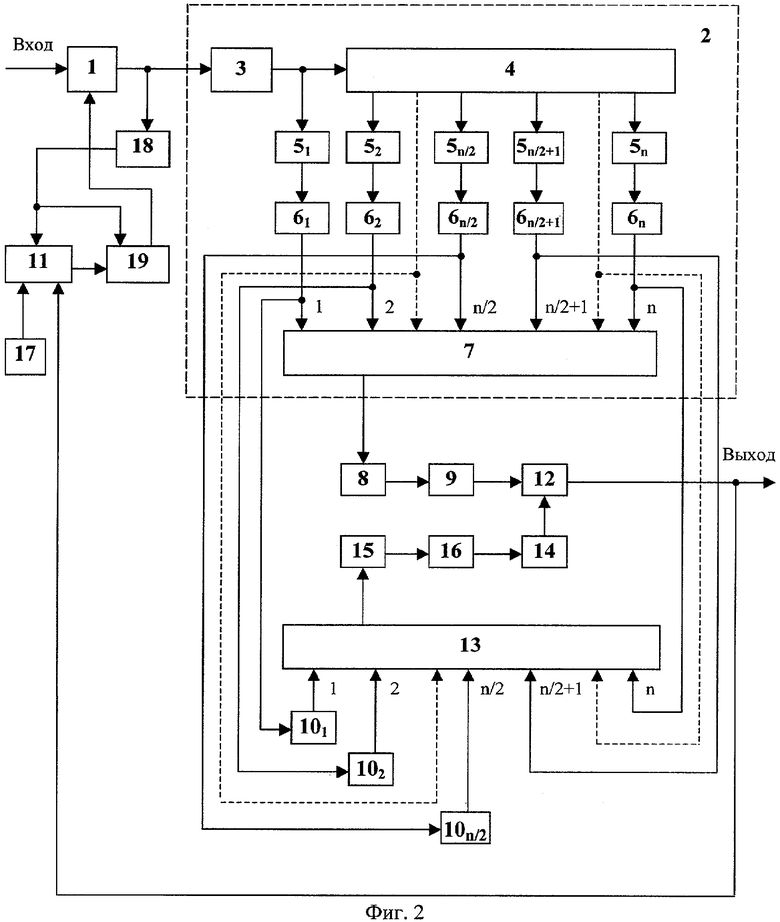

На фиг.2 изображена блок-схема предлагаемого устройства, где приведены следующие обозначения:

1 - линейная часть;

2 - согласованный фильтр;

3 - предварительный фильтр;

4 - линия задержки;

51-5n - первый, ..., n-й аттенюаторы;

61-6n - первый, ..., n-й фазовращатели;

7, 13, - первый и второй сумматоры;

8, 15 - первый и второй детекторы;

9, 16 - первый и второй блоки сравнения с порогом;

101-10n/2 - первый, ..., n/2-й инверторы;

11 - блок управления;

12 - элемент И;

14 - элемент НЕ;

17 - генератор тактовых импульсов;

18 - блок анализа помеховой обстановки;

19 - логический блок.

Предлагаемое устройство имеет следующие функциональные связи: последовательно соединенные линейную часть 1, первый, сигнальный вход которой является входом устройства, и согласованный фильтр 2, содержащий последовательно соединенные предварительный фильтр 3, вход которого является входом согласованного фильтра 2, и линию задержки 4, (n-1) выходов которой (где n - четное число) соединены соответственно с входами со второго по n-й аттенюаторов 52-5n, выходы которых соединены соответственно с входами со второго по n-й фазовращателей 62-6n, выходы которых соединены со второго по n-й входами первого сумматора 7 соответственно, а вход линии задержки 4 через последовательно соединенные первый аттенюатор 51 и первый фазовращатель 61 соединен с первым входом первого сумматора 7, выход которого является также и выходом согласованного фильтра 2, подключенным к последовательно соединенным первому детектору 8, первому блоку сравнения с порогом 9 и элементу И 12, выход которого является выходом устройства, соединенным с третьим, управляющим входом блока управления 11, выход которого соединен со вторым, управляющим входом логического блока 19, выход которого соединен со вторым, управляющим входом линейной части 1, выход которой через блок анализа помеховой обстановки 18 соединен с первыми входами логического блока 19 и блока управления 11, второй, синхронизирующий вход которого соединен с выходом генератора тактовых импульсов 17. Кроме того, выходы с первого по n/2-й фазовращателей 61-6n/2 соединены соответственно с входами с первого по n/2-й инверторов 101-10n/2, выходы которых соединены с первой группой n/2 входов второго сумматора соответственно, выходы с (n/2+1)-го по n-й фазовращателей 6n/2+1-6n соединены соответственно со второй группой n/2 входов второго сумматора 13, выход которого подключен к последовательно соединенным второму детектору 15, второму блоку сравнения с порогом 16 и элементу НЕ 14, выход которого соединен со вторым входом элемента И 12.

Предлагаемое устройство работает следующим образом. На вход устройства может поступать сигнал, смесь сигнала и структурной помехи или структурная помеха. Помехи естественного фона всегда присутствуют на входе устройства.

Рассмотрим случай, когда на первый, сигнальный вход блока 1, являющийся входом устройства, поступает сигнал при наличии помехи естественного фона. С выхода блока 1 сигнал поступает на вход блока 2, где через блок 3 подается на вход блока 4. С входа и с (n-1) выходов блока 4 сигналы через соответствующие последовательно соединенные блоки 51-5n и блоки 61-6n поступают на соответствующие n входов блока 7. При этом параметры блоков 4, 51-5n и 61-6n выбираются таким образом, что на выходе блока 7 элементы сигнала складываются в фазе и дают значение АКФ полезного сигнала, которая подается на вход блока 8, с выхода которого значение огибающей АКФ полезного сигнала подается на вход блока 9, где происходит сравнение с пороговым значением. Превышение порога в блоке 9 приводит к тому, что на первый вход блока 12 поступит логическая единица. Одновременно с выходов блоков 6n/2+1-6n сигналы поступают соответственно на вторую группу n/2 входов блока 13, а с выходов блоков 61-6n/2 через соответствующие блоки 101-10n/2 на первую группу n/2 входов блока 13 соответствующие сигналы поступают с противоположной фазой. Это приводит к тому, что значение АКФ сигнала на выходе блока 13 будет близко к нулю. Значит, значение огибающей АКФ на выходе блока 15 будет близко к нулю. Соответственно, не будет превышен порог в блоке 16, и с выхода блока 14 на второй вход блока 12 поступит логическая единица. Следовательно, с выхода блока 12 выйдет логическая единица и поступит на выход устройства, а также на третий, управляющий вход блока 11, что приведет к фиксации данного канала, так как формирование логической единицы на выходе блока 12 означает, что сигнал найден и поиск закончен. Кроме того, сигнал при наличии помехи естественного фона с выхода блока 1 поступает на вход блока 18, предназначенного для формирования управляющего сигнала для блока 19 и для сброса блока 11 в зависимости от уровня помехи естественного фона на входе устройства. Для этого с выхода блока 18 управляющий сигнал поступает на первый вход блока 11, на второй, синхронизирующий вход которого поступают тактовые импульсы с выхода блока 17. В блоке 11 формируется сигнал управления, который подается на второй, управляющий вход блока 19, на первый вход которого подается сигнал управления с выхода блока 18. В блоке 19 происходит формирование частоты, на которую настраивается канал в блоке 1. С выхода блока 19 сигнал новой канальной частоты подается на второй, управляющий вход блока 1.

Если на вход устройства поступит смесь сигнала и мощной структурной помехи при наличии помехи естественного фона, то, как и в случае только с сигналом, превышение порога суммой огибающих АКФ сигнала и ВКФ сигнала и помехи в блоке 9 приведет к поступлению на первый вход блока 12 логической единицы. Вероятность того, что в этот же момент значение ВКФ не превысит порог в блоке 16, достаточно мала. Таким образом, с выхода блока 14 на второй вход блока 12 поступит логический нуль. Следовательно, с выхода блока 12 на третий, управляющий вход блока 11 поступит логический нуль, означающий, что сигнал не найден, переключение каналов может быть продолжено, поиск полезного сигнала будет продолжен на других каналах.

Если на вход устройства поступит мощная структурная помеха при наличии помехи естественного фона, то вероятность того, что в момент отсчета будет превышен порог как в блоке 9, так и в блоке 16, достаточно велика. Это значит, что на первый вход блока 12 поступит логический нуль, а на второй вход блока 12 поступит логическая единица. С выхода блока 12 на третий, управляющий вход блока 11 поступит логический нуль, и поиск сигнала будет продолжен на других каналах.

Если на входе устройства присутствует высокий уровень помех естественного фона, то с выхода блока 18 на первые входы блоков 11 и 19 поступит логическая единица. Это приведет к переключению этих блоков, так что поиск сигнала сразу будет продолжен на других каналах, где, возможно, уровень помех естественного фона ниже, и это позволяет принять сигнал.

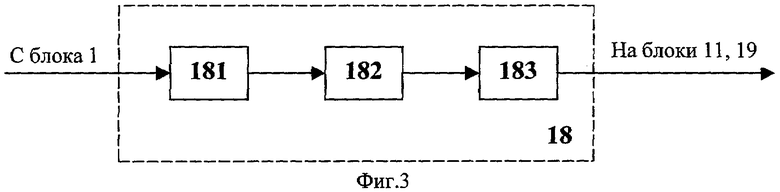

Функциональная схема блока анализа помеховой обстановки 18 приведена на фиг.3, где введены следующие обозначения:

181 - измеритель мощности;

182 - блок сравнения с порогом;

183 - формирователь.

Блок анализа помеховой обстановки 18 содержит последовательно соединенные измеритель мощности 181, вход которого является входом блока анализа помеховой обстановки 18, блок сравнения с порогом 182 и формирователь 183, выход которого является выходом блока анализа помеховой обстановки 18.

Блок анализа помеховой обстановки 18 работает следующим образом.

С выхода блока 1 входной сигнал поступает на блок 181, который измеряет суммарную мощность сигнала и помехи естественного фона. Блок 182 настроен на порог, определяемый предельным уровнем помех, при котором сигнал еще может быть принят. Если этот порог превышен, то блок 183 формирует логическую единицу для управления блоками 11 и 19, которая подается на первые входы блоков 11 и 19.

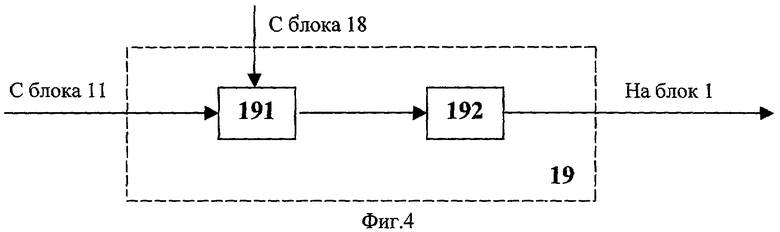

Функциональная схема логического блока 19 приведена на фиг.4, где введены следующие обозначения:

191 - элемент ИЛИ;

192 - перестраиваемый генератор.

Логический блок 19 содержит последовательно соединенные элемент ИЛИ 191 и перестраиваемый генератор 192, выход которого является выходом логического блока 19. При этом первый вход элемента ИЛИ 191 является первым входом логического блока 19, а второй вход элемента ИЛИ 191 - вторым входом логического блока 19.

Логический блок 19 работает следующим образом.

На первый вход блока 191 поступает сигнал логического уровня с выхода блока 18. Если уровень помехи превышает допустимое значение, то на первый вход блока 191 поступит логическая единица. На второй вход блока 191 поступает сигнал логического уровня с выхода блока 11. Логическая единица с выхода блока 11 поступает в том случае, если заданное время поиска на данном канале истекло и сигнал не найден. При поступлении логической единицы на вход блока 192 он перестраивается на другую частоту, сигнал которой с выхода блока 19 подается на второй, управляющий вход блока 1.

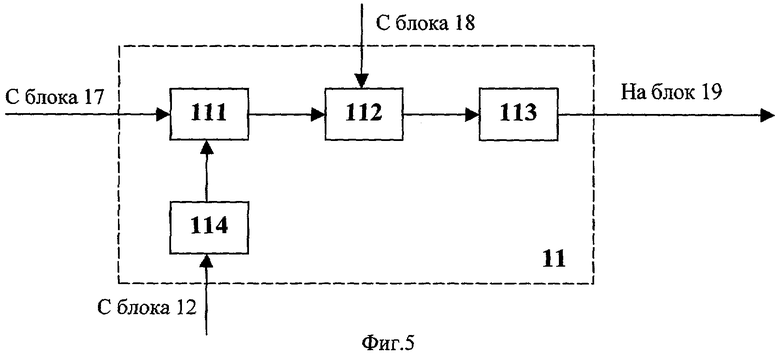

Функциональная схема блока управления 11 приведена на фиг.5, где введены следующие обозначения:

111 - ключ;

112 - счетчик фиксированных чисел;

113 - формирователь;

114 - бинарный счетчик.

Блок управления 11 содержит последовательно соединенные бинарный счетчик 114, вход которого также является третьим, управляющим входом блока управления 11, ключ 111, счетчик фиксированных чисел 112 и формирователь 113, выход которого является выходом блока управления 11. При этом второй вход ключа 111 является также и вторым, синхронизируемым входом блока управления 11, а второй вход счетчика фиксированных чисел 112 является также и первым входом блока управления 11.

Блок 11 работает следующим образом.

На вход блока 114 поступает сигнал логического уровня с выхода блока 12. В случае, если сигнал не найден, на вход блока 114 поступит логический нуль, который, пройдя через блок 114, поступит на управляющий вход блока 111 и откроет его, то есть тактовые импульсы с выхода блока 17 через блок 111 будут беспрепятственно поступать на первый вход блока 112, который рассчитан на определенное число тактовых импульсов. Это число определяется временем, в течение которого устройство поиска будет производить обнаружение полезного сигнала на данном канале. Когда поступит заданное число тактовых импульсов, на которое рассчитан счетчик 112, на его выходе сформируется логическая единица, которая, пройдя через блок 113, подается на второй, управляющий вход блока 19.

Если устройство поиска обнаружило полезный сигнал, то с выхода блока 12 на вход блока 114 поступит логическая единица и переведет его в другое состояние. С выхода блока 114 на первый, управляющий вход блока 111 поступит логическая единица и закроет его, то есть тактовые импульсы с выхода блока 17 не будут поступать на первый вход блока 112. Число тактовых импульсов не считается, и логический нуль с выхода блока 112 через блок 113 поступит на второй, управляющий вход блока 19.

Если уровень помех естественного фона на входе устройства превышает допустимый, то с выхода блока 18 на второй вход блока 112 поступит логическая единица, которая обнулит его, что приготовит его для дальнейшей работы на другом канале.

Структурная схема блока 192 и описание его работы приведено в заявке Великобритании №1473608.

Блоки 112, 114 и 182 имеют широкое применение. Описание структуры и принципов построения подобных блок-схем можно найти, например, в книге М.Мэндла "200 избранных схем электроники", пер. с англ. под редакцией Ицхоки Я.С., М.: Мир, 1980 г.: блок 182 - стр.176 - 181, рис.8.6 (б).

Блоки 112 и 114 описаны также в книге Р.Токхейма "Основы цифровой электроники", пер. с англ. под редакцией Е.К.Масловского, М.: Мир, 1988 г.: стр.163-184.

Реализация измерителя мощности (блок 181) не вызывает сомнений, в частности, он может быть реализован на квадратичном детекторе с конденсатором, другие методы построения измерителей мощности описаны в книге Г.Я.Мирского "Аппаратурное определение характеристик случайных процессов", М.-Л., Энергия, 1967, стр 432.

Таким образом, в заявляемом устройстве время поиска сигнала может быть значительно уменьшено за счет того, что время поиска существенно снижается в тех каналах, в которых отношение сигнал/шум малое и вероятность обнаружить сигнал и принять его достаточно мала. То есть введение дополнительных блоков в заявленное устройство обеспечивает уменьшение времени поиска по сравнению с прототипом.

Устройство применимо, в частности, для стационарных систем связи, где уровень полезного сигнала заранее известен, а суммарный уровень полезного сигнала и помехи можно измерить.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2004 |

|

RU2273953C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2004 |

|

RU2268549C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2008 |

|

RU2376703C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2244375C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2006 |

|

RU2311733C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2002 |

|

RU2223606C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2005 |

|

RU2302693C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2007 |

|

RU2364022C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ | 1988 |

|

SU1840158A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2012 |

|

RU2476923C1 |

Изобретение относится к области радиотехники и может быть использовано при построении систем радиосвязи, радионавигации и управления, использующих широкополосные сигналы. Технический результат - уменьшение времени поиска широкополосных сигналов в условиях воздействия помех высокого уровня. Для этого в устройстве поиска широкополосных сигналов, содержащем линейную часть, генератор тактовых импульсов, два детектора, два блока сравнения с порогом, элемент НЕ, элемент И, n/2 инверторов, второй сумматор, согласованный фильтр, содержащий предварительный фильтр, линию задержки, n аттенюаторов, n фазовращателей и первый сумматор, блок анализа помеховой обстановки естественного фона (БАПОЕФ), элемент ИЛИ, перестраиваемый генератор, ключ и счетчик фиксированных чисел, выход линейной части соединен с входом БАПОЕФ, выход которого соединен с первым входом элемента ИЛИ и входом обнуления счетчика фиксированных чисел, вход и управляющий вход ключа соединены соответственно с выходом генератора тактовых импульсов и выходом бинарного счетчика, вход которого подключен к выходу элемента И, выход счетчика фиксированных чисел соединен с вторым входом элемента ИЛИ, а выход подстраиваемого генератора подключен к линейной части для формирования частоты ее настройки. 5 ил.

Устройство поиска широкополосных сигналов, содержащее генератор тактовых импульсов, линейную часть, сигнальный вход которой является входом устройства, а выход линейной части соединен с входом согласованного фильтра, содержащего последовательно соединенные предварительный фильтр, вход которого является входом согласованного фильтра, и линию задержки, (n-1) выходов которой (где n - четное число) соединены соответственно с входами со второго по n-й аттенюаторов, выходы которых соединены соответственно с входами со второго по n-й фазовращателей, выходы которых соединены со второго по n-й входами первого сумматора соответственно, кроме этого, вход линии задержки через последовательно соединенные первый аттенюатор и первый фазовращатель соединен с первым входом первого сумматора, выход которого, являющийся также и выходом согласованного фильтра, подключен к последовательно соединенным первому детектору, первому блоку сравнения с порогом и элементу И, выход которого является выходом устройства, кроме того, выходы с первого по n/2-й фазовращателей через соответствующие с первого по n/2-й инверторы соединены с первой группой n/2 входов второго сумматора соответственно, а выходы с (n/2+1)-го по n-й фазовращателей соединены соответственно со второй группой n/2 входов второго сумматора, выход которого через последовательно соединенные второй детектор, второй блок сравнения с порогом и элемент НЕ соединен со вторым входом элемента И, отличающееся тем, что введены блок анализа помеховой обстановки естественного фона, последовательно соединенные элемент ИЛИ и перестраиваемый генератор, последовательно соединенные ключ и счетчик фиксированных чисел, при этом выход линейной части соединен с входом блока анализа помеховой обстановки естественного фона, выход которого соединен с первым входом элемента ИЛИ и входом обнуления счетчика фиксированных чисел, вход ключа соединен с выходом генератора тактовых импульсов, управляющий вход ключа подключен к выходу бинарного счетчика, вход которого подключен к выходу элемента И, выход счетчика фиксированных чисел соединен с вторым входом элемента ИЛИ, а выход подстраиваемого генератора подключен к линейной части для формирования частоты ее настройки.

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2002 |

|

RU2223606C1 |

| RU 2000664 C1, 07.09.1993 | |||

| US 4633426, 30.12.1986 | |||

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

Авторы

Даты

2007-12-20—Публикация

2004-11-22—Подача