Изобретение относится к области радиотехники и может найти применение в радиосредствах специальной радиосвязи для высоконадежной передачи данных по радиоканалу в условиях воздействия комплекса помех.

Известно устройство, описанное в [1], в котором за счет включения логических элементов в контур мажоритарного избирания устройство будет продолжать нормально функционировать и подавать сигнал на исполнительный элемент при выходе из строя одного любого функционального элемента.

Известно устройство, описанное в [2], в котором повышается надежность функционирования за счет снижения аппаратных затрат.

Недостатками вышеупомянутых устройств являются сложность реализации и низкая надежность.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в [3], принятое за прототип.

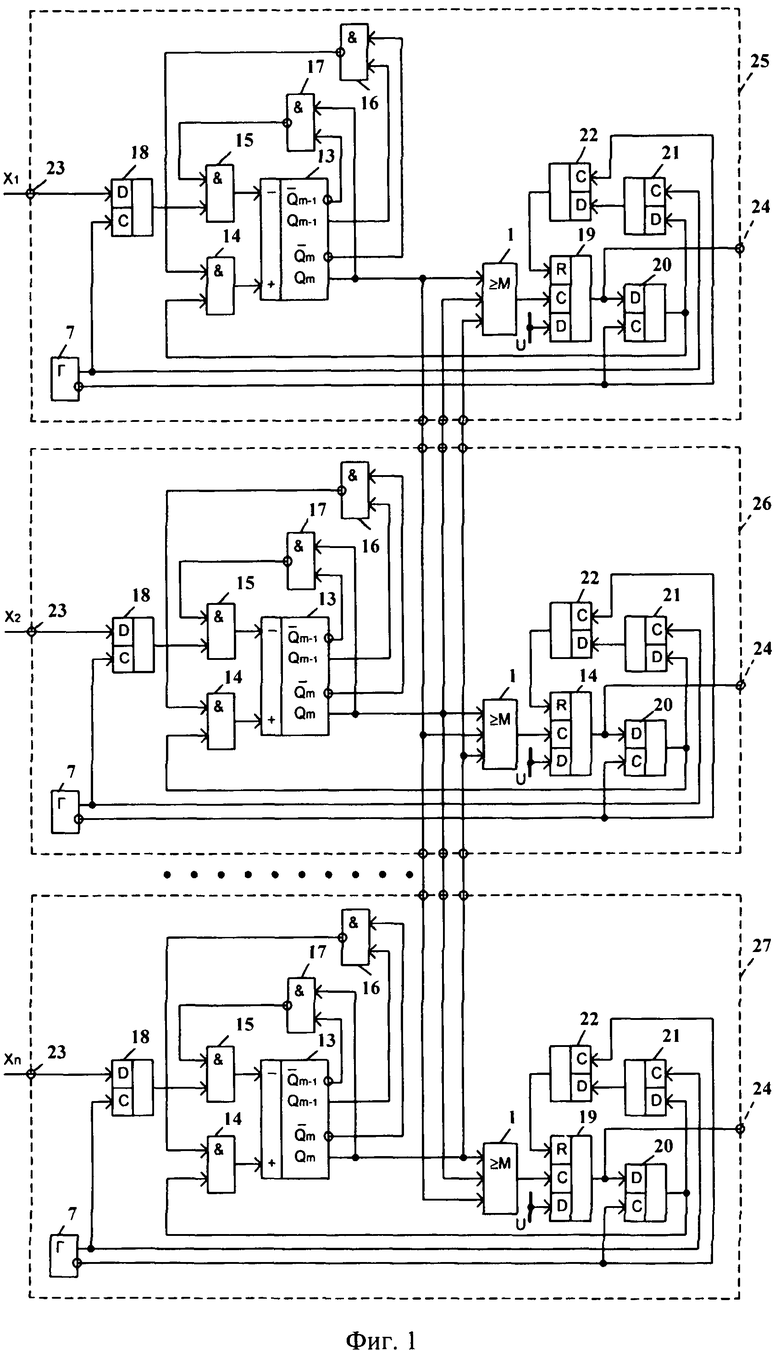

Функциональная схема устройства-прототипа приведена на фиг.1, где приняты следующие обозначения:

1 - мажоритарный элемент;

7 - генератор тактовых импульсов (ГТИ);

13 - реверсивный счетчик;

14 - первый элемент И;

15 - второй элемент И;

16 - первый элемент И-НЕ;

17 - второй элемент И-НЕ;

18 - первый D-триггер;

19 - второй D-триггер;

20 - третий D-триггер;

21 - четвертый D-триггер;

22 - пятый D-триггер;

23 - входная шина;

24 - выходная шина;

25 - первый канал;

26 - второй канал;

27 - n-й канал.

Устройство-прототип содержит выходы первого 16 и второго 17 элементов И-НЕ, подключенные к первым входам соответственно первого 14 и второго 15 элементов И, выходы которых соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 13. Первые входы первого 16 и второго 17 элементов И-НЕ соединены с прямым и инверсным выходами (m-1)-го разряда реверсивного счетчика 13, а вторые входы этих элементов И-НЕ соединены соответственно с инверсным и прямым выходом m-го разряда реверсивного счетчика 13. Выход реверсивного счетчика 13 соединен с первым входом мажоритарного элемента 1 и соответствующими входами мажоритарного элемента других каналов. Последовательно соединены второй 19, третий 20, четвертый 21 и пятый 22 D-триггеры, второй вход второго элемента И 15 соединен с выходом первого D-триггера 18, вход D которого подключен к входной шине 23, а вход С первого D-триггера 18 соединен с прямым выходом ГТИ 7 и входом С четвертого D-триггера 21, инверсный выход ГТИ 7 соединен с входом С третьего 20 и пятого 22 D-триггера, выход которого подключен к входу R второго D-триггера 19, вход D которого соединен с его высокопотенциальной шиной питания U, вход С второго D-триггера 19 подключен к выходу мажоритарного элемента 1, а выход второго D-триггера 19 соединен с выходной шиной канала 24, выход третьего D-триггера 20 соединен с вторым входом 14.

Устройство-прототип работает следующим образом.

Входные сигналы X1, Х2, ХП поступают на входы 23 (входы D первого D-триггера 18) соответствующих каналов устройства. Для наглядности примем, что n=3 и все реверсивные счетчики находятся в нулевом состоянии, а логической единице соответствует высокий уровень сигнала. В этом случае нулевые уровни с прямых выходов (m-1)-гo и m-го разрядов реверсивного счетчика 13 поступают на первый вход первого элемента И-НЕ 16 и второй вход второго элемента И-НЕ 17 соответственно. В результате на их выходах будет высокий уровень, который и поступит на первые входы первого 14 и второго 15 элементов И. Входной импульс, например X1, появляется на выходе D-триггера 18 по переднему фронту импульса с прямого выхода ГТИ 7 (период следования импульсов ТГ ГТИ 7 выбирается меньше длительности ТИ входного импульса X1). Импульс с выхода D-триггера 18 поступает на второй вход второго элемента И 15 и формирует на его выходе высокий уровень, который, поступая на вычитающий вход реверсивного счетчика 13, переводит его в состояние "минус единица" (во всех разрядах единицы). В результате высокий уровень с его прямого выхода старшего разряда m поступит на первый вход мажоритарного устройства 1 первого канала 25 и соответствующие входы остальных каналов.

Далее нулевые уровни сигналов с инверсных выходов (m-1)-гo и m-гo разрядов реверсивного счетчика 13 поступают на первый вход первого элемента И-НЕ 16 и второй вход второго элемента И-НЕ 17, в результате чего на их выходах останется высокий уровень. После того как на любой другой вход устройства, например на второй, поступит импульс Х2, он также будет воспринят реверсивным счетчиком второго канала 16. В результате высокий уровень сигнала с прямого выхода его старшего разряда попадает на вход мажоритарного устройства 1 своего канала и соответствующие входы мажоритарного устройства других каналов. При наличии двух высоких уровней на входах мажоритарного элемента 1 всех каналов на его выходе появится высокий уровень, который поступает на вход С второго D-триггера 19 всех каналов. На входе D этого триггера постоянно присутствует высокий уровень U, в результате чего D-триггер 19 устанавливается в единичное состояние по переднему фронту выходного импульса мажоритарного элемента 1.

Выходной сигнал второго D-триггера 19 всех каналов поступает на выходную шину 24 и вход D третьего D-триггера 20. Далее последовательно будут устанавливаться в единичное состояние третий D-триггер 20 по переднему фронту импульса с инверсного выхода ГТИ 7, четвертый D-триггер 21 по переднему фронту импульса с прямого выхода ГТИ 7, пятый D-триггер 22 по переднему фронту импульса с инверсного выхода ГТИ 7. Выходной импульс третьего D-триггера 20 всех каналов поступает на второй вход первого элемента И 14 и формирует на его выходе высокий уровень, который поступает на суммирующий вход реверсивного счетчика 13. В результате состояние всех реверсивных счетчиков увеличится на единицу - реверсивный счетчик 13 первого канала 25 и реверсивный счетчик 13 второго канала 26 будут обнулены, а реверсивный счетчик 13 третьего канала 27 перейдет в состояние "+1" (единица в младшем разряде). Если далее на вход третьего канала 27 поступит импульс Х3, то в соответствии с приведенным описанием этот импульс проходит на вычитающий вход реверсивного счетчика 13 своего канала и переводит реверсивный счетчик 13 третьего канала 27 в нулевое состояние.

После установки пятого D-триггера 22 в единичное состояние его выходной сигнал устанавливает второй D-триггер 19 в нулевое состояние, после чего происходит последовательная установка в нулевое состояние третьего 20, четвертого 21 и пятого 22 D-триггеров и схема приходит в исходное состояние.

Таким образом, устройство выбирает среднюю по числу импульсов последовательность и все выходные сигналы устройства формируются синхронно.

Недостатком устройства-прототипа является невозможность его применения в сетях связи, использующих структурную защиту передаваемой информации (например, использующих радиолинии с псевдослучайной перестройкой рабочей частоты). В таких сетях связи особенно актуальна синхронизация линии связи за счет периодически посылаемых от передатчика к приемнику синхропосылок с повторами. Структура же устройства-прототипа рассчитана на прием сигнала с высокой вероятностью ошибки первого рода: несмотря на отсутствие сигнала, под действием выбросов шума принимается неправильное решение о наличии сигнала. Как следствие этого, ошибочное принятие решения устройством-прототипом о наличие в шуме, например, битов синхропосылки, может привести к комплексу нежелательных последствий для сети связи в целом.

В связи с этим для повышения качества работы мажоритарного критерия необходима предварительная обработка принимаемой информации с целью минимизации ошибок мажоритарного выбора.

Таким образом, задачей предлагаемого устройства является введение адаптации приемника к изменениям помеховой обстановки и уменьшение потерь информации.

Достигаемый при этом технический результат - повышение помехоустойчивости за счет минимизации воздействия выбросов шума на аппаратуру связи, составной частью которой является данное устройство, и повышение достоверности приема информации.

Для реализации данного технического результата в устройство, содержащее генератор тактовых импульсов (ГТИ) и мажоритарный элемент, согласно изобретению введены n счетчиков-защелок, n демультиплексоров, n арифметико-логических устройств, (n+1) компараторов, n схем сравнения, решающее устройство, преобразователь, сумматор и блок управления, причем решающее устройство, вход которого является входом устройства, последовательно соединено с преобразователем и 1-м - n-м счетчиком-защелкой, причем первые выходы 1-го - n-го счетчиков-защелок соединены с последовательно соединенными сумматором, первым компаратором и блоком управления, l-й -n-й выходы которого соединены соответственно со вторыми входами 1-го - n-го демультиплексоров; вторые выходы 1-го - n-го счетчиков-защелок соединены соответственно с первыми входами 1-го - n-го демультиплексоров, первые выходы которых соединены с мажоритарным элементом, выход которого является выходом устройства; вторые выходы 1-го - n-го демультиплексоров соединены соответственно с 1-й - n-й схемами сравнения, выходы которых соединены соответственно с 1-м - n-м арифметико-логическими устройствами, выходы которых соединены соответственно с 2-м - (n+1)-м компараторами, выходы которых соединены соответственно с 2-м - (n+1)-м входами блока управления; синхровходы 1-го - n-го счетчиков-защелок, 1-го - n-го демультиплексоров, 1-го - n-го арифметико-логических устройств, 1-го - (n+1)-го компараторов, 1-й - n-й схем сравнения, мажоритарного элемента, решающего устройства, преобразователя, сумматора и блока управления соединены с выходом ГТИ.

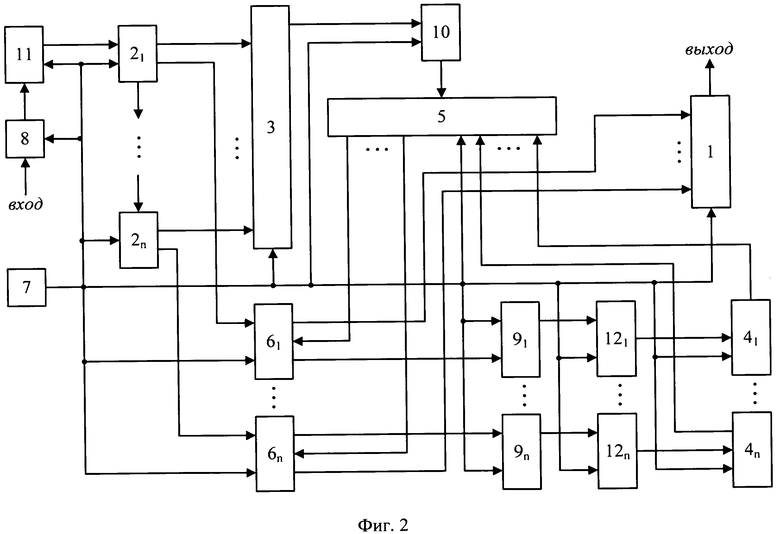

Функциональная схема предлагаемого устройства для мажоритарного выбора сигналов приведена на фиг.2, где приняты следующие обозначения:

1 - мажоритарный элемент;

21-2n - 1-й - n-й счетчики-защелки (СЗ1-СЗn);

3 - сумматор;

41-4n - 1-й - n-й компараторы;

5 - блок управления (БУ);

61-6n - 1-й - n-й демультиплексоры (Дм1-Дмn);

7 - генератор тактовых импульсов (ГТИ);

8 - решающее устройство (РУ);

91-9n - 1-я - n-я схемы сравнения (CC1-CCn);

10 - (n+1)-й компаратор;

11 - преобразователь;

121-12n - 1-е - n-е арифметико-логические устройства (АЛУ1-АЛУn).

Заявляемое устройство содержит последовательно соединенные решающее устройство 8, вход которого является входом устройства, преобразователь 11 и 1-й - n-й счетчики-защелки 21-2n, причем первые выходы 1-го - n-го счетчиков-защелок 21-2n соединены с последовательно соединенными сумматором 3, (n+1)-м компаратором 10 и блоком управления 5, 1-й - n-й выходы которого соединены соответственно со вторыми входами 1-го - n-го демультиплексоров 61-6n.

Вторые выходы 1-го - n-го счетчиков-защелок 21-2n соединены соответственно с первыми входами 1-го - n-го демультиплексоров 61-6n, первые выходы которых соединены с мажоритарным элементом 1, выход которого является выходом устройства.

Вторые выходы 1-го - n-го демультиплексоров 61-6n соединены соответственно с 1-й - n-и схемами сравнения 91-9n, выходы которых соединены соответственно с 1-м - n-м арифметико-логическими устройствами 121-12n, выходы которых соединены соответственно с 1-м - n-м компараторами 41-4n выходы которых соединены соответственно с 2-м - (n+1)-м входами блока управления 5.

Синхровходы 1-го - n-го счетчиков-защелок 21-2n, 1-го - n-го демультиплексоров 61-6n, 1-го - n-го арифметико-логических устройств 121-12n, 1-го - (n+1)-го компараторов 10, 41-4n, 1-й - n-й схем сравнения 91-9n, мажоритарного элемента 1, решающего устройства 8, преобразователя 11, сумматора 3 и блока управления 5 соединены с выходом ГТИ.

Устройство работает следующим образом.

Непрерывное радиочастотное колебание, переведенное в область видеочастот, поступает в РУ 8. В РУ 8 на основе дискретизации сигнала по времени и по амплитуде принимается решение о длине исследуемого вектора. Для увеличения точности последующих измерений результаты дискретизации в блоке 11 переводятся из формы числа с фиксированной точкой в форму числа с плавающей точкой.

Получаемые в блоках 8 и 11 векторы переменной длины загружаются последовательно в блоки 21-2n по следующему принципу (где β - порядковый номер получаемого в блоке 11 вектора):

При β<n:

- при получении β-го вектора запись производится только в блоки 2γ, где γ∈[1,β], причем для данного интервала в 2γ-й блок записывается (|γ-β-1|)-й вектор.

При β≥n:

- при получении β-го вектора в 2n-й блок записывается (β-n+1)-й вектор.

После записи в каждый из блоков 21-2n их значение длины поступает в сумматор 3, откуда вычисленное значение суммы поступает в блок 10, где происходит сравнение с имеющимся первым контрольным значением (КЗ1). КЗ1 соответствует числу, равному сумме длин векторов, содержащихся в блоках 21-2n, при условии, что их длины равны.

Результаты сравнения в блоке 10 поступают в БУ 5. При условии достижения равенства контрольному значению в блоке 10 БУ 5 вырабатывает управляющие сигналы для адресных входов демультиплексоров 61-6n, согласно которым входной сигнал из соответствующего блоку 6j (где j∈[1,n]) блока 2j поступает соответственно в блок 9j.

Схемы сравнения являются блоками хранения эталонного сигнала. И на выходах блоков 91-9n формируется результат сравнения с эталонным сигналом полученных в блоках 8 и 11 векторов. Данные результаты из блоков 91-9n поступают соответственно в АЛУ 121-12n, где на основе некоторых критериев (определяемых из условий оптимального соотношения вероятностей ложных тревог и правильного приема) определяется окончательное отклонение вектора от эталонного распределения.

Полученные величины отклонений из АЛУ 121-12n поступают соответственно в блоки 41-4n, где происходит сравнение с имеющимся вторым контрольным значением (КЗ2).

Результаты сравнения в блоках 41-4n поступают в БУ 5. На их основе (для тех из блоков 41-4n, где произошло превышение КЗ2) БУ 5 вырабатывает управляющие сигналы для адресных входов соответствующих демультиплексоров 61-6n, согласно которым входной сигнал из соответствующих блоков 21-2n поступает в блок 1, где на основании мажоритарных критериев происходит окончательное определение битов в принятых векторах.

С выхода ГТИ 7 на все блоки данного устройства подаются тактовые импульсы, определяющие начало каждой микрооперации, в результате чего обеспечивается синхронизация работы устройства в целом.

РУ может быть реализовано на основе схем, описанных в [4]. Регистры-защелки могут быть реализованы физически на базе элементов, описанных в [5]. СС 91-9n могут быть реализованы в виде дискретных согласованных фильтров. Блок 1 может быть выполнен в виде логических элементов [6].

Устройство в целом может быть реализовано в виде перепрограммируемого цифрового устройства, например XC3S400-4PQ208I [7].

Таким образом, введение в предлагаемом устройстве новых блоков и связей позволяет увеличить достоверность приема информации за счет адаптации к изменению помеховой обстановки, что позволяет применять его в спецсвязи в условиях воздействия комплекса помех.

Источники информации

1. Патент РФ на изобретение №2298823 "Устройство мажоритарного резервирования (варианты)". // Рабинович М.Д., Никифоров Б.Д., Абрамов В.М., 2005.

2. Патент РФ на изобретение №2110835 "Устройство для мажоритарного выбора сигналов". // Леденев Г.Я., Лаврищев А.Б., 1998.

3. Патент РФ на изобретение №2396591 "Устройство для мажоритарного выбора сигналов". // Леденев Г.Я., Сухов Б.М., Ефимов С.Н., 2008.

4. Шумоподобные сигналы в системах передачи информации. // Под ред. проф. Пестрякова В.Б. - М.: Сов. радио, 1973.

5. Искусство схемотехники. Хоровиц П., Хилл У. - М.: Мир, 1998, п.8.24.

6. Микросхемотехника: Учебное пособие для вузов. Изд. 2-е, перераб. и доп.// Алексеенко А.Г., Шакулин И.И. - М.: Радио и связь, 1990.

7. http://www.plis.ru/index.php

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2016 |

|

RU2628890C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ В МНОГОФАЗНЫХ СЕТЯХ С ЗАЩИТОЙ ОТ ХИЩЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ИХ ВАРИАНТЫ) | 1995 |

|

RU2094809C1 |

| Линейный аппроксиматор | 1983 |

|

SU1157548A1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК | 2003 |

|

RU2264690C2 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК | 2000 |

|

RU2174284C1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2011 |

|

RU2446559C1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| МНОГОКАНАЛЬНЫЙ РАДИОТЕРМОГРАФ | 1993 |

|

RU2085957C1 |

| Резервированный усилитель | 1987 |

|

SU1434568A1 |

Изобретение относится к области радиотехники и может найти применение в радиосредствах специальной радиосвязи для высоконадежной передачи данных по радиоканалу в условиях воздействия комплекса помех. Техническим результатом является повышение помехоустойчивости за счет минимизации воздействия выбросов шума на аппаратуру связи, составной частью которой является данное устройство, и повышение достоверности приема информации. Для достижения указанного результата устройство для мажоритарного выбора сигналов содержит: мажоритарный элемент (1), n счетчиков-защелок (21-2n), сумматор (3), n компараторов (41-4n), блок управления (5), n демультиплексоров (61-6n), генератор тактовых импульсов (7), решающее устройство (8), n схем сравнения (91-9n), (n+1) компаратор (10), преобразователь (11), n арифметико-логических устройств (121-12n). 2 ил.

Устройство для мажоритарного выбора сигналов, содержащее генератор тактовых импульсов (ГТИ) и мажоритарный элемент, отличающееся тем, что введены n счетчиков-защелок, n демультиплексоров, n арифметико-логических устройств, (n+1) компараторов, n схем сравнения, решающее устройство, преобразователь, сумматор и блок управления, причем решающее устройство, вход которого является входом устройства, последовательно соединено с преобразователем и 1-м - n-м счетчиками-защелками, причем первые выходы 1-го - n-го счетчиков-защелок соединены с последовательно соединенными сумматором, первым компаратором и блоком управления, 1-й - n-й выходы которого соединены соответственно со вторыми входами 1-го - n-го демультиплексоров; вторые выходы 1-го - n-го счетчиков-защелок соединены соответственно с первыми входами 1-го - n-го демультиплексоров, первые выходы которых соединены с мажоритарным элементом, выход которого является выходом устройства; вторые выходы 1-го - n-го демультиплексоров соединены соответственно с 1-й - n-й схемами сравнения, выходы которых соединены соответственно с 1-м - n-м арифметико-логическими устройствами, выходы которых соединены соответственно с 2-м - (n+1)-м компараторами, выходы которых соединены соответственно с 2-м - (n+1)-м входами блоков управления; синхровходы 1-го - n-го счетчиков-защелок, 1-го - n-го демультиплексоров, 1-го - n-го арифметико-логических устройств, 1-го - (n+1)-го компараторов, 1-й - n-й схем сравнения, мажоритарного элемента, решающего устройства, преобразователя, сумматора и блока управления соединены с выходом ГТИ.

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2008 |

|

RU2396591C1 |

| Устройство для мажоритарного выбора сигналов | 1984 |

|

SU1238278A1 |

| Устройство для мажоритарного выбора сигналов | 1987 |

|

SU1441402A1 |

| Устройство для мажоритарного выбора сигналов | 1977 |

|

SU739537A1 |

| US 6948098 B2, 20.09.2005. | |||

Авторы

Даты

2013-02-27—Публикация

2012-03-14—Подача