Область техники, к которой относится изобретение

Настоящее изобретение относится к технике прецизионного формирования интервалов времени.

Уровень техники

Устройства программируемой задержки импульсных сигналов широко применяются в измерительных генераторах для получения заданного значения времени задержки одного импульса относительно другого. Для этой цели в настоящее время используются большей частью цифровые устройства, обеспечивающие высокую точность задержки и простоту реализации.

Наиболее простым из известных цифровых устройств для генерирования задержки является синхронный одновибратор [1] на основе счетчика импульсов, снабженного тактовым входом, подключенным к входному зажиму опорных импульсов, а также входами загрузки параллельного кода и разрешения счета. С помощью входящих в устройство логических элементов в момент поступления входного импульса выполняется загрузка в счетчик импульсов кода начального состояния, после чего производится подсчет опорных импульсов. По достижении состоянием счетчика импульсов завершающего состояния вырабатывается выходной импульс, а работа устройства блокируется до поступления следующего входного импульса. Недостатком данного аналога является низкая точность времени задержки, так как из-за несинхронного запуска возможна ошибка, достигающая целого опорного периода.

Для преодоления указанного недостатка применяются устройства, использующие принцип интерполяции интервала времени.

Известен, например, матричный генератор, состоящий из множества связанных кольцевых мультифазных генераторов, который, будучи снабженным дешифраторами строки и столбца, позволяет осуществить генерирование заданной задержки путем программируемого выбора элемента матрицы [2]. Недостатком данного аналога является сложность структуры и дополнительная погрешность задержки ввиду множества возможных режимов колебаний матричного генератора.

Другим аналогом настоящего изобретения является интегральный времязадающий генератор на основе матрицы устройств автоподстройки задержки [3]. Упомянутая матрица представляет собой М основных N-секционных синхронизированных цифровых линий задержки и дополнительную синхронизированную цифровую линию задержки из М секций, выходы всех секций которой подключены к входам соответствующих основных цифровых линий задержки. Доступ к узлам обеспечивают входящие в устройство мультиплексоры. Выполнение условия М≠N обеспечивает получение временного кванта в узлах матрицы Δt=To/(M×N), где To период опорных сигналов дополнительной цифровой линии задержки. Поскольку время задержки секции цифровой линии задержки равно времени задержки одного логического вентиля, то в устройстве достигается субвентильное разрешение по времени. В то же время одновременное генерирование всех возможных времен задержки в узлах матрицы достигается за счет сложности устройства, что является его недостатком.

Наиболее близким по технической сущности к настоящему изобретению является устройство автоподстройки задержки для прецизионного генерирования тактовых сигналов с переменной фазой [4]. Данный аналог, принятый за прототип, построен на основе двух цифровых линий задержки (ЦЛЗ) в виде последовательной цепи управляемых элементов задержки, охваченных обратной связью по объединенным управляющим входам элементов задержки через блок фазового сравнения. В первой ЦЛЗ оставшийся вход блока фазового сравнения присоединен к входу ЦЛЗ, во второй ЦЛЗ оставшийся вход блока фазового сравнения служит вторым входом ЦЛЗ. Вход первой ЦЛЗ подключен к выходу опорного генератора импульсов, а два входа второй ЦЛЗ - к выходам соответственно первого и второго мультиплексоров, соответствующие информационные входы которых подключены к отводам первой ЦЛЗ. Отводы второй ЦЛЗ присоединены к соответствующим информационным входам третьего мультиплексора, выход которого служит выходом устройства. Объединенные одноименные адресные входы первого и второго мультиплексоров и адресные входы третьего мультиплексора служат входами старших и младших разрядов кода программирования задержки.

Принцип действия устройства заключается в двухэтапном образовании субквантов времени путем деления опорных интервалов времени сначала первой, а затем второй ЦЛЗ. Первая ЦЛЗ, включающая М элементов задержки, делит период То опорного генератора на М равных частей, в результате чего получается квант Δt1=Тo/М. Опорными сигналами второй ЦЛЗ служат импульсы со смежных выходов первой ЦЛЗ, которые выбираются первым и вторым мультиплексорами. Поскольку вторая ЦЛЗ состоит из N элементов задержки, то опорный интервал Δt1 разделяется еще до субкванта Δt2=Δt1/N=To/(M×N). Таким образом достигается повышение разрешающей способности генератора задержки.

Однако субквант времени в устройстве-прототипе не может быть меньше времени задержки распространения элемента задержки второй ЦЛЗ, то есть точность времени задержки ограничена. Это является недостатком прототипа.

Сущность изобретения

Целью настоящего изобретения является повышение точности времени задержки за счет уменьшения шага квантования времени. Указанная цель достигается путем замены второй цифровой линии задержки блоком фазовой интерполяции.

В соответствии с настоящим изобретением в генератор программируемой задержки, содержащий подключенную к выходу опорного генератора импульсов секционированную цифровую линию задержки, отводами подключенную к соответствующим информационным входам первого и второго мультиплексоров, а также третий мультиплексор, выход которого служит выходом генератора программируемой задержки, причем объединенные одноименные адресные входы первого и второго мультиплексоров и адресные входы третьего мультиплексора являются входами соответственно старших и младших разрядов управляющего задержкой цифрового кода, введен блок фазовой интерполяции, входами присоединенный к выходам соответственно первого и второго мультиплексоров, а выходами - к соответствующим информационным входам третьего мультиплексора.

В предпочтительном варианте осуществления изобретения секционированная ЦЛЗ состоит из последовательной цепи управляемых элементов задержки, управляющие входы которых присоединены к выходу блока фазового сравнения, входы которого подключены соответственно к входу и выходу последовательной цепи элементов задержки.

Блок фазовой интерполяции может состоять из последовательно соединенных каскадов интерполяции, каждый i-й каскад интерполяции имеет (2i-1+1) входов и (2i+1) выходов, выходы оконечного каскада интерполяции служат выходами блока фазовой интерполяции. Каждый каскад интерполяции в предпочтительном варианте исполнения включает (2i-1+1) элементов интерполяции, имеющих по два входа и одному выходу. При этом первый и второй входы элементов интерполяции с нечетными порядковыми номерами в каждом упомянутом каскаде объединены и служат входами каскада интерполяции, первый и второй входы элементов интерполяции с четными порядковыми номерами в каждом упомянутом каскаде подключены к объединенным входам соответствующих элементов интерполяции с нечетными порядковыми номерами, отличающимися от порядкового номера данного элемента интерполяции на ±1. Выходы всех элементов интерполяции в данном каскаде интерполяции составляют совокупность его выходов.

Принцип действия устройства состоит в двухэтапном разделении периода опорных импульсов Тo на кванты времени в секционированной ЦЛЗ, выборе пары смежных выходов ЦЛЗ с помощью первого и второго мультиплексоров, последующем разделении кванта времени на субкванты в блоке фазовой интерполяции и выборе одного из его выходов с помощью третьего мультиплексора в качестве выходного сигнала устройства.

Элементы фазовой интерполяции, из которых построен блок фазовой интерполяции, путем смешения двух своих входных сигналов образует третий сигнал, фронты которого располагаются точно между фронтами входных сигналов. Для компенсации задержки при формировании выходного сигнала оба входных сигнала перед передачей в следующий каскад также задерживаются дополнительными элементами задержки. Каскадирование элементов интерполяции позволяет последовательно уменьшать шаг времени вдвое с каждым новым каскадом, то есть сокращать субкванты времени, из которых складывается время задержки. Таким способом несложно получить субквант времени, много меньше времени задержки одного логического вентиля. Благодаря уменьшению шага квантования времени повышается точность времени задержки.

Перечень фигур чертежей

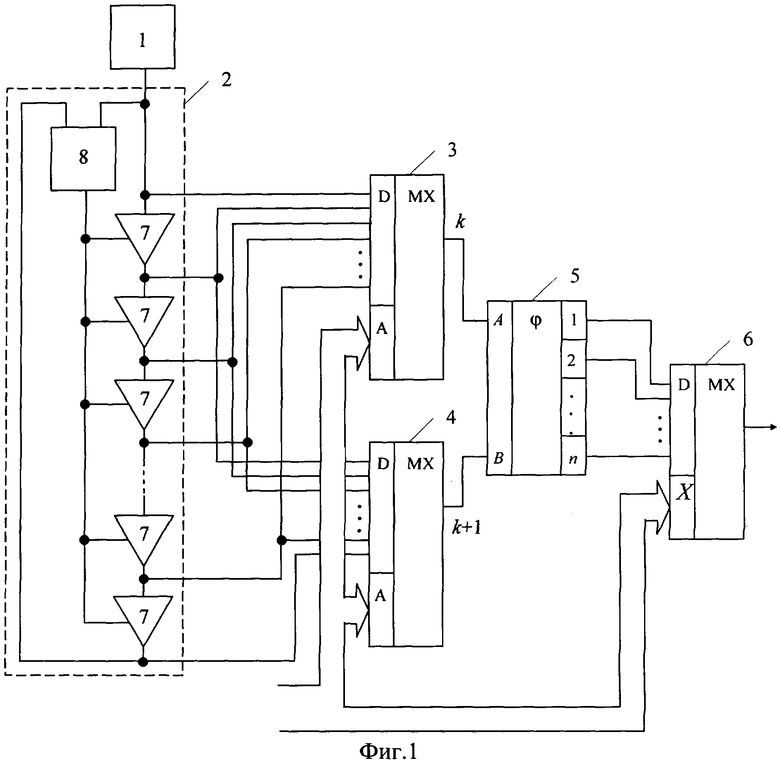

На фиг.1 представлена функциональная электрическая схема генератора программируемой задержки в соответствии с настоящим изобретением.

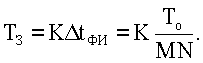

На фиг.2 изображена функциональная схема блока фазовой интерполяции, выполненного на элементах фазовой интерполяции.

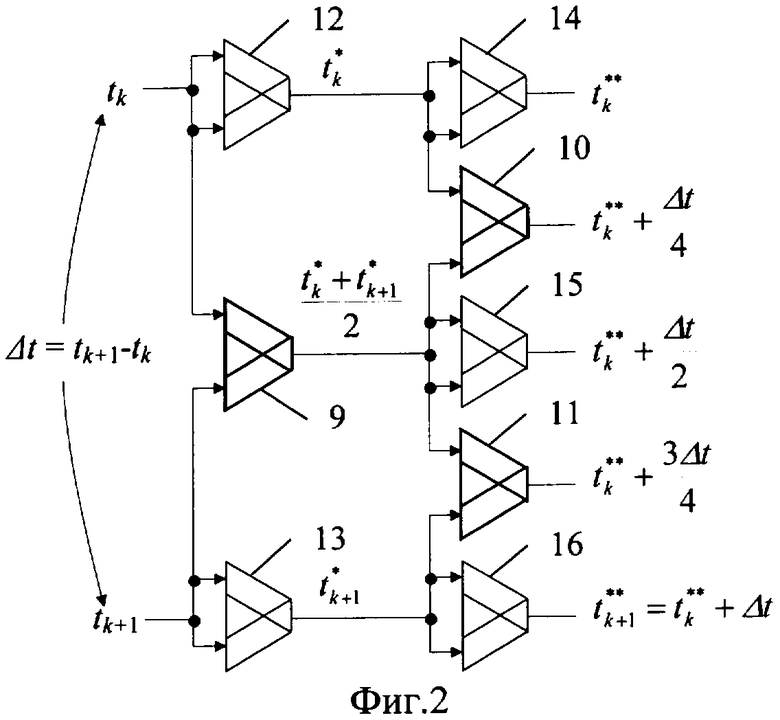

На фиг.3 показан вариант принципиальной схемы элемента фазовой интерполяции, являющегося базовым элементом блока фазовой интерполяции.

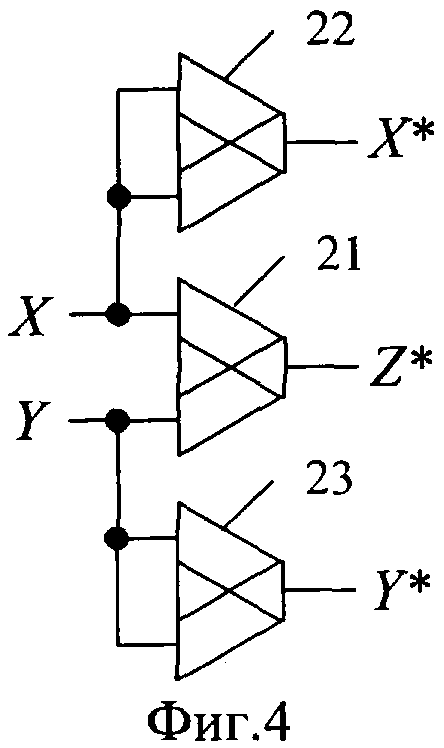

Фиг.4 иллюстрирует схему соединения трех элементов фазовой интерполяции для получения интерполирующего сигнала и задержанных входных сигналов.

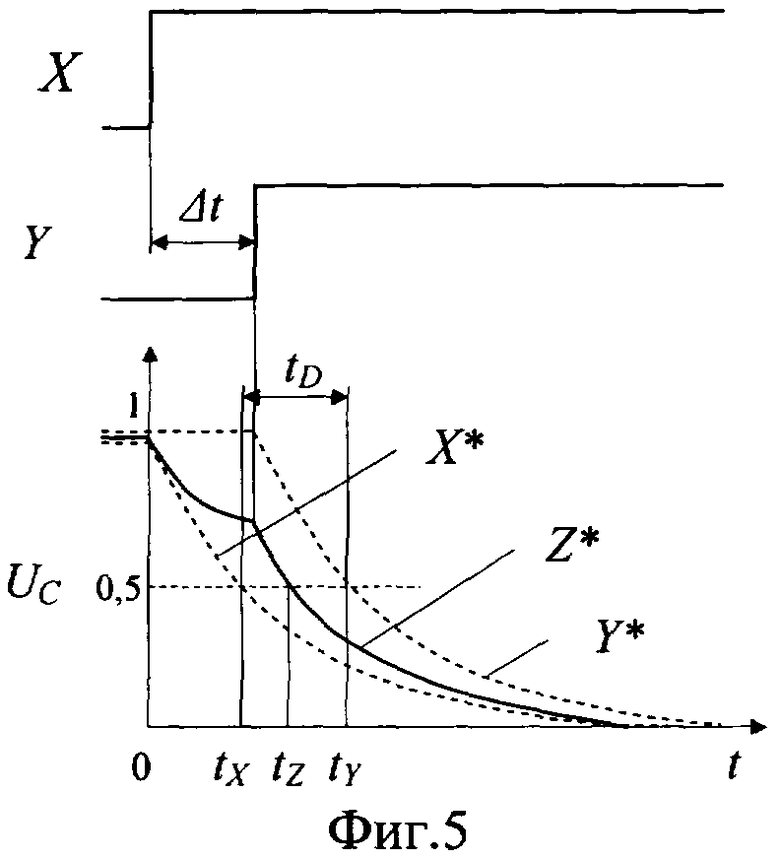

На фиг.5 изображены временные диаграммы напряжений, поясняющие принцип действия элемента фазовой интерполяции в схеме фиг.4.

Сведения, подтверждающие возможность осуществления изобретения

Представленная на фиг.1 схема генератора программируемой задержки содержит опорный генератор 1, нагруженный на секционированную цифровую линию 2 задержки, промежуточные отводы которой подключены к информационным входам первого 3 и второго 4 мультиплексоров. Блок 5 фазовой интерполяции своими двумя входами подключен к выходам соответственно первого 3 и второго 4 мультиплексоров, а множеством выходов - к соответствующим информационным входам третьего мультиплексора 6. Двоичный код управления задержкой подается на адресные входы мультиплексоров, причем объединенные одноименные адресные входы первого и второго мультиплексоров 3, 4 служат входами старших разрядов кода управления, а адресные входы третьего мультиплексора 6 - входами младших разрядов кода управления. Отводы ЦЛЗ 2 соединены с информационными входами первого 3 и второго 4 мультиплексоров со смещением на один разряд с тем, чтобы, когда первый мультиплексор 3 передает на свой выход сигнал с k-го отвода ЦЛЗ 2, второй мультиплексор 4 передает на свой выход сигнал со смежного (k+1)-го отвода ЦЛЗ 2.

Цифровая линия 2 задержки в предпочтительном варианте осуществления представляет собой систему автоподстройки задержки, которая включает последовательную цепь управляемых электронных элементов 7 задержки, объединенные управляющие входы которых соединены с выходом блока 8 фазового сравнения, у которого входы присоединены соответственно с входом и выходом цифровой линии 2 задержки. Структура блока 8 фазового сравнения подробно не описывается ввиду общеизвестности, отметим лишь, что она включает фильтр, преобразующий результат фазового сравнения в управляющее напряжение.

Блок 5 фазовой интерполяции может иметь произвольное число каскадов. Для примера на фиг.2 показана схема двухкаскадного блока интерполяции, состоящая из одинаковых элементов фазовой интерполяции, из которых основные элементы 9, 10, 11 выполняют собственно интерполяцию, а остальные элементы 12, 13, 14, 15, 16 служат для компенсации задержки основных элементов. Первый каскад, состоящий из элементов 9, 12, 13 фазовой интерполяции, имеет два входа, на которые с помощью первого 3 и второго 4 мультиплексоров подаются сигналы с k-го и (k+1)-го отводов секционированной ЦЛЗ 2, фронты упомянутых сигналов поступают в моменты времени tk и tk+1 разделенные квантом ЦЛЗ Δt. Первый каскад имеет три выхода, сигналы на которых задержаны относительно входных сигналов. На фиг.2 факт задержки для упрощения отражен звездочкой при символе, обозначающем момент времени. Основным выходом каскада является выход элемента 9, в то время, как элементы 12 и 13 с объединенными входами служат для простой задержки входных сигналов. Элемент 9 фазовой интерполяции формирует сигнал, фронты которого располагаются по центру между фронтами задержанных входных сигналов. Три выхода первого каскада служат входами второго каскада фазовой интерполяции, который включает элементы 10, 11, 14-16 фазовой интерполяции и имеет пять выходов. Тот факт, что сигналы второго каскада задержаны относительно входных сигналов блока 5 фазовой интерполяции на два времени задержки распространения элементов фазовой интерполяции, отображен на фиг.2 двумя звездочками при соответствующих символах. Как показано на фиг.2, выходные сигналы второго каскада - выходные сигналы блока 5 фазовой интерполяции равномерно распределены на отрезке времени t** k...t** k+1, что равноценно уменьшению в четыре раза исходного кванта времени Δt.

В описываемом варианте осуществления изобретения каждый элемент 9-16 фазовой интерполяции, являющийся базовым элементом блока 5 фазовой интерполяции, выполнен в виде КМОП инверторов 17, 18, объединенные выходы которых подключены к входу третьего КМОП инвертора 19 (фиг.3). Роль показанного на схеме времязадающего конденсатора 20 при интегральном исполнении устройства может исполнять суммарные паразитные емкости МОП транзисторов и емкости межсоединений, приведенные к точке объединения выходов первого 9 и второго 10 инверторов.

Принцип действия элемента фазовой интерполяции поясняется схемой первого каскада блока 5 фазовой интерполяции (фиг.4) и временными диаграммами напряжений в узлах этого фрагмента, изображенными на фиг.5. Амплитуда показанных на диаграммах напряжений для удобства описания условно принята за единицу. Схема содержит три элемента 21, 22, 23 фазовой интерполяции, один из которых 21 формирует интерполирующий сигнал Z*, а два других 22 и 23 с замкнутыми входами задерживают входные сигналы Х и Y, образуя сигналы Х* и Y*.

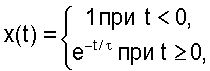

Режим интерполяции имеет место при перекрытии во времени фронтов или спадов импульсов на объединенных выходах инверторов 17, 18, то есть при постоянной времени цепи перезаряда конденсатора 20, соизмеримой с интервалом Δt между фронтами входных сигналов Х и Y, либо больше этого интервала. В моменты поступления фронтов входных сигналов Х и Y начинаются разряды емкостей 20 в элементах соответственно 22 и 23 фазовой интерполяции. Если считать, что в передаточной функции цепи разряда доминирует один полюс, то напряжения Х* и Y* (фиг.5) спадают по экспоненциальному закону:

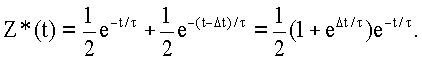

Одновременно происходит двухэтапный разряд емкости 20 в элементе 21 фазовой интерполяции. В соответствии с принципом суперпозиции напряжение Z* определяется взвешенным сложением Х* и Y*:

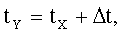

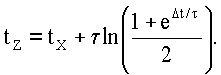

Сигналы Х*, Y* и Z* достигают уровня отсчета задержек 1/2 в моменты времени:

Из этих уравнений следует, что для центрированного расположения фронта (спада) сигнала Z* между фронтами (спадами) сигналов Х* и Y* необходимо подобрать емкость 20 так, чтобы постоянная времени отвечала трансцендентному уравнению

необходимо подобрать емкость 20 так, чтобы постоянная времени отвечала трансцендентному уравнению

Генератор программируемой задержки (фиг.1) работает в следующем порядке. Опорный генератор 1 непрерывно снабжает секционированную ЦЛЗ 2 импульсами со стабильным периодом To. Благодаря действию петли обратной связи через блок 8 фазового сравнения время задержки Δt всех элементов 7 задержки в ЦЛЗ 2 поддерживается точно равным Δt=Тo/М, где М - число элементов задержки в ЦЛЗ. В соответствии со старшими разрядами управляющего кода мультиплексоры 3 и 4 передают на входы блока 5 фазовой интерполяции сигналы со смежных отводов ЦЛЗ 2, разделенные интервалом Δt. Блок 5 фазовой интерполяции образует на множестве N=2n своих выходов, где n - число каскадов интерполяции, множество сигналов, сдвинутых друг относительно друга на субквант времени ΔtФИ=Δt/N.

Младшие разряды управляющего кода, поступающие на адресные входы третьего мультиплексора 6, определяют номер выхода блока 5 фазовой интерполяции, сигнал с которого передается на основной выход генератора программируемой задержки. Таким образом, если числовое значение управляющего кода равно К, то время задержки сигнала с выхода третьего мультиплексора 6 относительно сигнала опорного генератора 1 составит

Поскольку субквант времени ΔtФИ может быть много меньшим времени задержки логического вентиля, то устройство согласно настоящему изобретению обеспечивает повышенную по сравнению с прототипом точность времени задержки.

Литература

1. Титце У., Шенк К. Полупроводниковая схемотехника: Справочное руководство. - М.: Мир, 1982, с.361, рис.20.31.

2. Array oscillator circuit. Патент США №5717362, раздел V описания, фиг.11.

3. Christiansen J. An Integrated High Resolution CMOS Timing Generator Based on an Array of Delay Locked Loops. - IEEE Journal of Solid-State Circuits, Vol.31, July 1996, стр.956, фиг.9.

4. Segmented dual delay-locked loop for precise variable-phase clock generation. Патент США №6100735, МПК H03L 7/06, 8.08.2000 - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2014 |

|

RU2570116C1 |

| ИНТЕРПОЛИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ЦИФРОВОЙ КОД | 2014 |

|

RU2561999C1 |

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2005 |

|

RU2303803C2 |

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| ИНТЕРПОЛИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2008 |

|

RU2385479C2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| ИМИТАТОР ДЖИТТЕРА | 2005 |

|

RU2303852C2 |

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ | 2000 |

|

RU2173933C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ СЛУЧАЙНОЙ ДЛИТЕЛЬНОСТИ | 2004 |

|

RU2261525C1 |

Изобретение относится к технике цифрового преобразования информации, а именно к генераторам программируемой задержки импульсов. Технический результат - повышение точности времени задержки за счет улучшения разрешения по времени. Для достижения данного результата в устройство, содержащее синхронизированную с опорным генератором (1) цифровую линию задержки (2), множество выходов которой присоединено к соответствующим информационным входам первого и второго мультиплексоров (3, 4), дополнительно введен блок фазовой интерполяции (5). Выходы мультиплексоров (3, 4) подключены к соответствующим входам блока фазовой интерполяции (5), множество выходов которого присоединено к информационным входам третьего мультиплексора (6). Объединенные одноименные адресные входы первого и второго мультиплексоров (3, 4) и адресные входы третьего мультиплексора (6) служат соответственно старшими и младшими разрядами цифрового кода, программирующего время задержки. 2 з.п. ф-лы, 5 ил.

| US 6100735 А, 08.08.2000 | |||

| Управляемая линия задержки | 1984 |

|

SU1197068A1 |

| Управляемая линия задержки | 1988 |

|

SU1647863A1 |

| US 5604775 А, 18.02.1997 | |||

| US 4330750, 18.05.1982. | |||

Авторы

Даты

2008-02-20—Публикация

2006-05-16—Подача