Для генерирования синхросигналов, позволяющих различить битовые ячейки в процессе приема дискретной информации, применяются устройства фазовой синхронизации на основе многофазного генератора (Чулков В.А. Дискретно-фазовая автоподстройка в устройстве синхронизации данных. - Вопросы радиоэлектроники, сер. ЭВТ, 1990, вып. 13, с. 70 - 76). Такие устройства сочетают точность и высокую рабочую частоту аналоговых систем фазовой автоподстройки частоты (ФАПЧ) с высокой стабильностью и устойчивостью цифровых систем ФАПЧ.

Известно устройство коррекции фазы сигнала по заявке ФРГ N OS 3826717, кл. H 03 L 7/00. Это устройство состоит из стабильного генератора, нагруженного на многозвенный элемент задержки, регистра хранения, у которого информационные входы подключены к соответствующим выходам элемента задержки, а синхронизирующий вход служит входом информационного сигнала, а также выходной комбинационной схемы. В момент поступления информационного сигнала регистр хранения фиксирует текущую фазу многофазного опорного генератора, образованного стабильным генератором и элементом задержки, а комбинационная схема выбирает в качестве выходного синхросигнала сигнал элемента задержки, находящийся в заданном фазовом отношении к информационному сигналу. Данное устройство характеризуется значительной дисперсией фазы выходного синхросигнала ввиду ее жесткой связи с фазой информационного сигнала, претерпевающей искажения в процессе передачи этого сигнала.

Аналогичный принцип реализует устройство для синхронизации фазы по патенту Нидерландов N 183214, кл. H 03 L 7/00, включающее генератор тактового сигнала и соединенную с ним секционированную линию задержки, каждый вывод которой может подключаться к выходу устройства через мультиплексор. Мультиплексор управляется схемой обнаружения совпадений, оценивающей фазу входного сигнала. В этом устройстве также не предусмотрена фильтрация фазового дрожания выходного сигнала, что обуславливает низкую точность синхронизации.

Известна также цифровая петля фазовой автоподстройки по патенту ЕПВ N 0240232, кл. H 03 L 7/00, содержащая программируемую линию задержки, подключенную к выходу кварцевого генератора, и фазовый детектор, который управляет программируемой линией задержки с помощью реверсивного счетчика. Управление временем задержки осуществляется таким образом, что фазовая разность между входным сигналом данных и выходным сигналом программируемой линии задержки минимизируется. Недостаток данного аналога состоит в низкой точности и узком частотном диапазоне синхронизации, что обусловлено прямоугольной формой дискриминационной характеристики фазового сочетания с реверсивным счетчиком.

Из известных аналогов наиболее близким по технической сущности к настоящему изобретению является устройство синхронизации канала воспроизведения данных по авторскому свидетельству СССР N 1674245, кл. G 11 B 27/00, H 03 L 7/00, в котором блок фазовой автоподстройки состоит из соединенного с выходным зажимом мультиплексора, у которого группа информационных входов соединена с многофазным опорным генератором, а группа адресных входов - с выходами реверсивного счетчика. Функции фазового детектора в данном устройстве выполняет триггер, фиксирующий либо отставание выходного синхросигнала от входного информационного сигнала, либо опережение. Результат фазового сравнения представляет собой двоичную единицу, либо прибавляемую, либо вычитаемую реверсивным счетчиком. В процессе автоподстройки реверсивный счетчик последовательно изменяет адресный код мультиплексора, передающего на выходной зажим сигнал с одного из выходов опорного генератора. Изменение адреса происходит в направлении компенсации фазовой разности, которая в установившемся режиме составляет ± 2π/ N , где N - число выходов опорного генератора. Недостаток устройства-прототипа состоит в том, что фазовый детектор-триггер фиксирует лишь знак фазовой разности, что соответствует прямоугольной дискриминационной характеристике. В результате устройство-прототип обладает низким быстродействием в режиме установления синхронизма, узкой частотной полосой захвата и недостаточной динамической точностью синхронизации.

Целью настоящего изобретения является расширение частотной полосы синхронизации, уменьшение времени установления синхронизма и повышение точности синхронизации. Указанная цель достигается введением в устройство дополнительных цифровых блоков, обеспечивающих в совокупности пилообразную дискриминационную характеристику фазового сравнения и управляемую инерционность устройства.

Для этого в устройство фазовой синхронизации, содержащее опорный 2m-фазный генератор, подключенный к 2m-информационным входам мультиплексора, введены (m + 1)-разрядный сумматор-вычитатель, (m + 1)-разрядный сумматор, блок сдвига числа в разрядной сетке и два регистра хранения.

2m-фазный выход опорного генератора через первый регистр хранения присоединен к 2m выходам шифратора, выходами соединенного с m младшими входами первого операнда сумматора. Младшие m входов второго операнда сумматора через m-разрядный блок инверторов подключены к старшим m выходам второго регистра хранения и к адресным входам мультиплексора. Все (m + 1) выходы сумматора-вычитателя через второй регистр хранения присоединены к его же (m + 1) входам первого операнда, вход управления - к выходу старшего разряда сумматора, а (m + 1) входов второго операнда - к соответствующим выходам блока сдвига числа в разрядной сетке. Блок сдвига числа в разрядной сетке своими m входами соединен с оставшимися m выходами сумматора, 1 входами - с шиной логического нуля, а входами управления сдвигом - с k-разрядной шиной управления. Старшие входы первого и второго операндов сумматора подключены к шинам логического нуля и единицы соответственно, с шиной логической единицы соединен также его вход переноса. Синхронизирующий вход первого регистра хранения, соединенный через элемент задержки с синхронизирующим входом второго регистра хранения, является входом устройства, а выход мультиплексора - его выходом.

Устройство согласно настоящему изобретению является по существу устройством фазовой автоподстройки фазы, так как в нем в отличие от традиционных систем ФАПЧ осуществляется непосредственное регулирование фазы без изменения опорной частоты. Это позволяет, в частности, снизить порядок астатизма системы авторегулирования фазы и повысить на этой основе ее устойчивость.

В отличие от прототипа и большинства аналогов в устройстве согласно настоящему изобретению адресное слово, управляющее работой мультиплексора, изменяется с каждым входным сигналом не на единицу младшего разряда, а на величину, пропорциональную текущей фазовой ошибке. Благодаря этому становится возможным увеличение числа фаз опорного генератора и повышение точности синхронизации за счет уменьшения шага дискретизации. При этом достигается расширение частотной полосы синхронизации и ускорение процесса начального установления синхронизма.

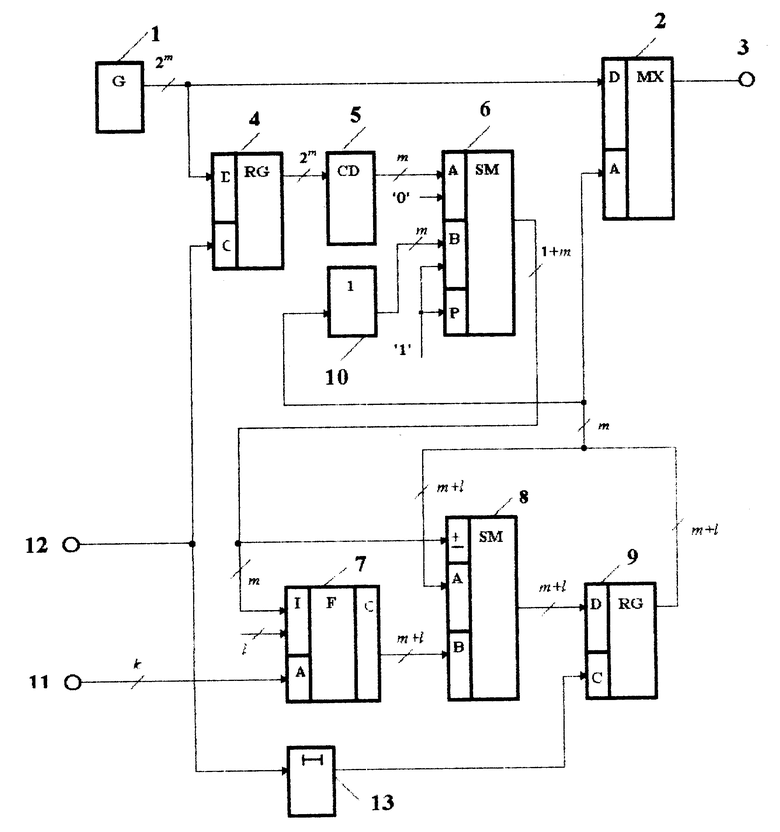

На чертеже приведена электрическая функциональная схема устройства фазовой синхронизации в соответствии с настоящим изобретением.

Показанная на чертеже функциональная схема устройства фазовой синхронизации включает 2m-фазный опорный генератор 1, нагруженный на информационные входы мультиплексора 2, связанного с выходным зажимом 3, и первого регистра 4 хранения. Выходы первого регистра 4 хранения подключены к входам шифратора 5, выходами соединенного с младшими m входами первого операнда (m + 1)-разрядного сумматора 6, старший вход первого операнда которого соединен с шиной логического нуля. Младшие m выходов сумматора 6 подключены к соответствующим информационным блокам 7 сдвига числа в разрядной сетке, а старший выход - к входу управления сумматора-вычитателя 8. Все выходы (m + l)-разрядного сумматора-вычитателя 8 соединены с его же (m + l) входами первого операнда через второй регистр 9 хранения, у которого старшие m выходов присоединены, кроме того, к адресным входам мультиплексора и через m-разрядный блок инверторов - с младшими m входами второго операнда сумматора 6. Старшие входы первого и второго операндов сумматора 6 подключены к шинам логического нуля и единицы соответственно, к шине логической единицы подключен также его вход переноса. Блок 7 сдвига числа в разрядной сетке присоединен своими l информационными входами к шине логического нуля, входами управления сдвигом - к k-разрядной шине 11 управления, а (m + l) выходами - к входам второго операнда сумматора-вычитателя 8. Входной зажим 12 устройства соединен с синхронизирующим входом первого регистра 4 хранения непосредственно, а с синхронизирующим входом второго регистра 9 хранения - через элемент 13 задержки.

Опорный генератор 1 вырабатывает на каждом из своих 2m выходов импульсы с одинаковой частотой, которая выбирается равной номинальной тактовой частоте входных сигналов цифровых данных на зажиме 12. Импульсы на смежных выходах генератора 1 отличаются по фазе на шаг дискретизации Δϕ = 2π/ 2m.

На эту же величину шага дискретизации различаются фазы импульсов на последнем и первом выходах опорного генератора 1, т.е. выходными импульсами опорный период T0 поделен на 2m равных интервалов Δt = T0/ 2m.

Шифратор 5 преобразует в двоичный m-разрядный код номер того из своих 2m входов, на котором присутствует уровень логической единицы при условии наличия на смежном младшем входе уровня логического нуля.

Блок 7 сдвига числа в разрядной сетке может быть выполнен в виде набора из (m + l) мультиплексоров, каждый из которых имеет 2k информационных входов, а адресные входы подключены к k-разрядной шине 11 управления. В зависимости от управляющего адресного кода m-разрядное двоичное слово, поступающее в блок 7 с выходов сумматора 6, занимает m определенных смежных позиций в выходном (m + l)-разрядном слове. Например, при k = 2, управляющему адресному коду 00 соответствует отсутствие сдвига числа, а управляющему адресному коду 11 - сдвиг на три позиции вправо. Оставшиеся l позиций выходного слова заполняются нулями. Очевидно, что l должно быть равным 2k. По существу блок 7 сдвига числа в разрядной сетке выполняет деление двоичного числа на целые степени двойки, так как делению числа на 2n соответствует его сдвиг на 2n разрядов вправо.

Элемент 13 задержки служит для компенсации задержки сигналов от момента поступления входного сигнала на зажим 12 до образования результата на выходе сумматора-вычитателя 8, т.е. для устранения состояний сигналов в схеме.

Многофазный опорный генератор 1 служит для получения эталонной шкалы фазы при измерении текущей фазы входного сигнала данных, поступающего на входной зажим 12 и при оценке фазовой разности входного и выходного сигналов устройства. Первый регистр 4 хранения и шифратор 5 служат для определения и запоминания фазы поступившего входного сигнала. Сумматор 6 с блоком 10 инверторов образуют цифровой фазовый детектор с пилообразной дискриминационной характеристикой. Блок 7 сдвига числа в разрядной сетке, сумматор-вычитатель 8 и второй регистр 9 хранения осуществляют цифровую фильтрацию фазового рассогласования в устройстве.

Работает устройство фазовой синхронизации в следующем порядке.

Опорный генератор 1 непрерывно вырабатывает на своих выходах 2m последовательностей сдвинутых по фазе друг относительно друга на шаг дискретизации импульсов. Старшие m разрядов сохраняемого в регистре 9 числа определяют номер того выхода опорного генератора 1, импульсы с которого через мультиплексор 2 проходят на выходной зажим 3 и служат выходными сигнальными устройствами.

Управляющий двоичный код, поступающий по k шинам 11 на блок 7 сдвига числа в разрядной сетке определяет, как будет показано ниже, инерционность устройства. Положим для определенности, что k = 2 и управляющий код равен 01, т.е. блок 7 осуществляет сдвиг входного числа на один разряд (делит это число на 2).

При поступлении очередного входного сигнала на входной зажим 12 регистр 4 хранения фиксирует в своих 2m разрядах двоичное число, соответствующее состояниям выходов опорного генератора 1 в момент поступления входного сигнала. На выходах регистра 4 появляется слово вида  где x может принимать значение 0 или 1. Шифратор 5 преобразует это слово в m-разрядный двоичный код, отражающий номер выхода опорного генератора 1, фронт импульса на котором совпадает с фронтом поступившего входного сигнала. Таким образом, по шкале фазы, формируемой опорным генератором, фиксируется фаза вновь поступившего входного сигнала. Как отмечалось, текущая фаза выходного синхросигнала устройства фазовой синхронизации на выходном зажиме 3 хранится в регистре 9 в виде двоичного числа на его m старших разрядах. Именно это число поступает по цепи обратной связи на вход m-разрядного блока 10 инверторов.

где x может принимать значение 0 или 1. Шифратор 5 преобразует это слово в m-разрядный двоичный код, отражающий номер выхода опорного генератора 1, фронт импульса на котором совпадает с фронтом поступившего входного сигнала. Таким образом, по шкале фазы, формируемой опорным генератором, фиксируется фаза вновь поступившего входного сигнала. Как отмечалось, текущая фаза выходного синхросигнала устройства фазовой синхронизации на выходном зажиме 3 хранится в регистре 9 в виде двоичного числа на его m старших разрядах. Именно это число поступает по цепи обратной связи на вход m-разрядного блока 10 инверторов.

Сумматор 6, на который первый операнд поступает в прямом коде с нулем в старшем разряде, второй операнд - в обратном коде с единицей в старшем разряде, а на вход переноса подается единица, выполняет операцию вычитания второго операнда из первого. Результат операции на выходе сумматора 6 получается в дополнительном коде, т. е. на его выходах образуется дополнительный код разности (см., например, Токхейм Р. Основы цифровой электроники. - М.: Мир, 1988, с. 247, рис. 9.31). Характерно, что этот дополнительный код разности представляет собой цифровой эквивалент фазовой ошибки в фазовом детекторе с пилообразной дискриминационной характеристикой, т.е. на младших m выходах образуется код фазовой ошибки, а на старшем выходе - знак этой разности. Преобразования дополнительного кода в прямой двоичный код при этом не требуется (см. пример сложения чисел в дополнительном коде, приведенный в том же источнике на стр. 244).

Код разности фаз с выхода сумматора 6 передается через блок 7 сдвига числа в разрядной сетке на вход второго операнда B сумматора-вычитателя 8, а значение знака разности со старшего разряда сумматора 6 - на вход управления сумматора-вычитателя 8. Режиму сложения соответствует значение 1 разности, а режиму вычитания - 0. На вход A первого операнда сумматора-вычитателя 8 подается число с выхода регистра 9 хранения, поэтому сумматор-вычитатель 8 в зависимости от знака фазовой разности либо прибавляет половину числа фазовой разности к содержимому регистра 9, либо вычитает ее. Пришедший с задержкой через элемент 13 задержки входной сигнал записывает результат суммирования-вычитания в регистр 9 хранения. Таким образом, сумматор-вычитатель 8 с регистром 9 хранения выполняет функции цифрового интегратора, корректируя управляющий код на адресном входе мультиплексора в направлении компенсации выявленной фазовой ошибки. Если в процессе суммирования возникает сигнал переноса, то он игнорируется. Это необходимо ввиду периодического характера процесса регулирования фазы. Непрерывному увеличению текущей фазы выходного синхросигнала соответствует в момент переполнения разрядной сетки сумматора-вычитателя 8 выбор младшего номера выхода опорного генератора 1 после того, как был выбран старший номер. Это является особенностью устройства согласно настоящему изобретению, позволяющей реализовать непосредственное регулирование фазы без воздействия на опорную частоту.

Аналогично устройство работает с поступлением каждого очередного входного сигнала на зажим 12. В итоге несколько циклов регулирования, количество которых определяется начальной разностью фаз и инерционностью устройства, задаваемой по управляющей шине 11. В устройстве фазовой синхронизации достигается установившийся режим синхронизма, для которого характерно совпадение фазы выходного синхросигнала на зажиме 3 с математическим ожиданием фазы входного сигнала.

Быстродействие и динамическая точность устройства фазовой синхронизации зависят от управляющего кода на k-разрядной шине 11. При управляющем коде 00 фаза выходного сигнала сразу устанавливается равной фазе входного сигнала, т.е. достигается предельное быстродействие, однако все искажения фазы входного сигнала переносятся в выходной синхросигнал - динамическая точность оказывается низкой. При управляющем коде 11 процесс начального установления синхронизма получается наиболее длительным, так как для корректировки фазы синхросигнала используется только часть фазовой разности. Однако в последнем случае динамическая прочность будет наиболее высокой. Таким образом, благодаря наличию управляющего входа устройство может быть приспособлено для работы в конкретных условиях без изменения структуры устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ | 2000 |

|

RU2173933C1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ ГЕНЕРАТОР ИМПУЛЬСОВ | 1997 |

|

RU2103816C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ С ЦИФРОВОЙ ПЕРЕСТРОЙКОЙ ПЕРИОДА | 2000 |

|

RU2170490C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ С НОРМИРОВАННЫМ ФАЗОВЫМ ШУМОМ | 1998 |

|

RU2133552C1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

Устройство фазовой синхронизации относится к технике синхронизации при приеме дискретной информации и реализует принцип непосредственной фазовой автоподстройки без воздействия на частоту местного генератора. Для расширения частотной полосы синхронизации, ускорения начального установления синхронизма и повышения динамической точности синхронизации в устройство, состоящее из многофазного опорного генератора, подключенного своими выходами к информационным входам мультиплексора, введены дополнительно сумматор-вычитатель, сумматор, блок сдвига числа в разрядной сетке и два регистра хранения. Один регистр хранения, снабженный шифратором, служит для измерения фазы входных сигналов. Другой регистр хранения совместно с сумматором-вычитателем и блоком сдвига в разрядной сетке выполняет функцию цифрового фильтра. Работающий в дополнительном коде сумматор выявляет текущую фазовую ошибку. По сравнению с обычной цифровой системой ФАПЧ устройство обладает повышенной рабочей частотой. Технический результат - расширение частотной полосы синхронизации, ускорение начального установления синхронизма и повышение динамической точности синхронизации. 1 ил.

Устройство фазовой синхронизации, содержащее опорный 2m-фазный генератор, подключенный к 2m информационным входам мультиплексора, отличающееся тем, что в него введены (m+l)-разрядный сумматор-вычитатель, (m+l)-разрядный сумматор, блок сдвига числа в разрядной сетке и два регистра хранения, при этом 2m-фазный выход опорного генератора через первый резистор хранения присоединен к 2m входам шифратора, выходами соединенного с младшими m входами первого операнда сумматора, все выходы сумматора-вычитателя подключены к его же входам первого операнда через (m+l)-разрядный второй регистр хранения, старше m выходов которого подключены к соответствующим адресным входам мультиплексора и через m-разрядный блок инверторов - к младшим m входам второго операнда сумматора, вход управления сумматора-вычитателя присоединен к выходу старшего разряда сумматора, (m+l) входов второго операнда сумматора-вычитателя подключены к соответствующим выходам блока сдвига числа в разрядной сетке, m входов которого соединены с оставшимися m выходами сумматора, l входов - с шиной логического нуля, а входы управления сдвигом - с k-разрядной шиной управления, старший вход первого операнда сумматора подключен к шине логического нуля, старший вход второго операнда и вход переноса - к шине логической единицы, причем синхронизирующий вход первого регистра хранения, соединенный через элемент задержки с синхронизирующим входом второго регистра хранения, является входом устройства, а выход мультиплексора - его выходом.

| DE 3826717 A1, 16.02.89 | |||

| DE 3444401 A, 20.06.85 | |||

| Устройство для синхронизации канала воспроизведения данных | 1989 |

|

SU1674245A1 |

| Устройство фазовой синхронизации | 1985 |

|

SU1332553A1 |

| Генератор с автоматической регулировкой фазы | 1980 |

|

SU1314967A3 |

| Устройство фазовой синхронизации | 1982 |

|

SU1116545A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1112578A1 |

| Устройство фазовой автоматической подстройки частоты для коротковолнового канала связи | 1976 |

|

SU582576A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ФАЗОВОЙ СИНХРОНИЗАЦИИ | 0 |

|

SU321961A1 |

| СПОСОБ ПРИДАНИЯ АНТИСТАТИЧЕСКИХ СВОЙСТВ КОМПОЗИЦИЯМ НА ОСНОВЕ ПОЛИВИНИЛХЛОРИДА | 0 |

|

SU240232A1 |

| Устройство для промывки труб переездных мостов через картовые канавы на торфяных предприятиях | 1961 |

|

SU140042A1 |

| Горный компас | 0 |

|

SU81A1 |

Авторы

Даты

1998-09-27—Публикация

1997-04-15—Подача