Изобретение относится к радиотехнике и может использоваться для формирования сетки стабильных частот с равномерным шагом в приемных и передающих устройствах с малым временем перестройки в широком диапазоне рабочих частот.

Широко известна схема синтезатора частот, включающая опорный генератор, делитель частоты с фиксированным коэффициентом деления, управляемый генератор, делитель частоты с переменным коэффициентом деления, частотно-фазовый детектор и фильтр нижних частот, образующих кольцо импульсно-фазовой автоподстройки частоты управляемого генератора (см. Левин В.А., Малиновский В.Н., Романов С.К., Синтезаторы частот с системой импульсно-фазовой автоподстройки. - М.: Радио и связь, 1989, стр.32-40).

Известна аналогичная схема синтезатора, в которой используется частотно-фазовый детектор с тремя устойчивыми состояниями (заряд, нейтральное состояние, разряд) и блоком генераторов тока заряда/разряда (см., например, Gardner F.M. Charge-Pump Phase-Lock Loops. // IEEE Transactions on Communications. Vol.com-28, №11 November, 1980, p.1849-1858, пат. US №5055803).

Такие схемы синтезаторов характеризуются простотой схемной реализации и обеспечивают достаточно высокие эксплуатационные параметры выходного сигнала. Применение частотно-фазового детектора совместно с блоком зарядовой накачки упрощает схему синтезатора, увеличивает ослабление паразитных гармоник частоты сравнения в спектре выходного сигнала и повышает качество автоподстройки управляемого генератора. В такой схеме синтезатора подстройка частоты управляемого генератора производится с точностью до фазы опорного генератора, т.е. система автоподстройки частоты имеет астатизм по фазе (см. Шахгильдян В.В., Ляховкин А.А. Системы фазовой автоподстройки частоты. М.: Связь, 1972, стр.278-280). Это расширяет область применения такого синтезатора в радиотехнической аппаратуре.

Однако существенным недостатком приведенных выше синтезаторов является довольно низкое быстродействие; так как оно определяется постоянными значениями коэффициента усиления и полосы эффективного регулирования кольца астатической фазовой автоподстройки.

Наиболее близким по физической сущности и технической реализации к предлагаемому синтезатору является синтезатор частот, описанный, в патенте US №4156855 «Phase-locked loop with variable gain and bandwidth», H03B 3/04, May, 29, 1979, принятый за прототип.

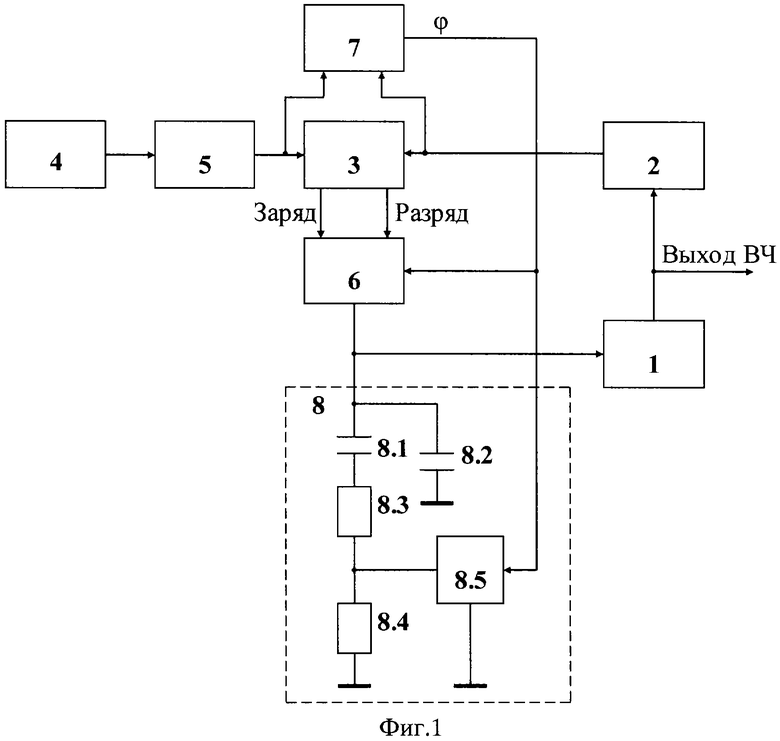

Функциональная схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

1 - управляемый генератор (УГ);

2 - делитель частоты с переменным коэффициентом деления (ДПКД);

3 - частотно-фазовый детектор (ЧФД);

4 - опорный генератор (ОГ);

5 - делитель частоты с фиксированным коэффициентом деления (ДФКД);

6 - блок управляемой зарядовой накачки (БУЗН);

7 - блок определения захвата по фазе (БОЗФ);

8 - фильтр нижних частот (ФНЧ);

8.1, 8.2 - первый и второй конденсаторы;

8.3, 8.4 - первый и второй резисторы;

8.5 - ключ.

Синтезатор частот содержит управляемый генератор (УГ) 1, делитель частоты с переменным коэффициентом деления (ДПКД) 2, частотно-фазовый детектор (ЧФД) 3, опорный генератор (ОГ) 4, делитель частоты с фиксированным коэффициентом деления (ДФКД) 5, блок управляемой зарядовой накачки (БУЗН) 6, блок определения захвата по фазе (БОЗФ) 7 и фильтр нижних частот (ФНЧ) 8. При этом выход УГ 1 является выходом высокой частоты (ВЧ) устройства и соединен с ВЧ входом ДПКД 2, выход которого соединен с синхронизируемыми входами ЧФД 3 и БОЗФ 7. Выход ДФКД 5 соединен со входами синхронизации ЧФД 3 и БОЗФ 7. Опорный вход ДФКД 5 соединен с выходом ОГ 4. Первый выход ЧФД 3 является выходом сигнала заряда и соединен с коммутационным входом заряда БУЗН 6. Второй выход ЧФД 3 является выходом сигнала разряда и соединен с коммутационным входом разряда БУЗН 6. При этом ФНЧ 8 содержит ключ 8.5, конденсатор 8.2, последовательно соединенные первый конденсатор 8.1, первый резистор 8.3 и второй резистор 8.4, второй вывод которого соединен с общей шиной. Первые выводы первого 8.1 и второго 8.2 конденсаторов соединены с выходом БУЗН 6, а также с управляющим входом УГ 1. Второй вывод второго конденсатора 8.2 соединен с общей шиной. Точка соединения первого 8.3 и второго 8.4 резисторов соединена с первым выводом ключа 8.5, второй вывод которого соединен с общей шиной. Выход ϕ БОЗФ 7 соединен со входом коммутации величины тока БУЗН 6 и коммутирующим входом ключа 8.5.

Устройство-прототип работает следующим образом.

Сигнал опорной частоты с выхода ОГ 4 подается на опорный вход ДФКД 5, где делится по частоте в нужное количество раз. При отклонении частоты выходного колебания УГ 1 от требуемого номинального значения ω0, соответствующего режиму захвата по фазе, на выходах ЧФД 3 появляются импульсные сигналы заряда или разряда, длительность которых равна разности времени прихода импульсов с ДПКД 2 и ДФКД 5 на входы ЧФД 3. При этом ЧФД 3, выполненный на триггерах, работает по принципу запоминания и хранения информации о поступлении входных сигналов, и на своих выходах формирует сигналы в форме трех состояний цифровой логики (заряд, нейтральное состояние, разряд). Состояния ЧФД 3 вызываются передними фронтами входных импульсов с ДФКД 5 и ДПКД 2. Когда импульсные сигналы на синхронизируемом входе ЧФД 3 опережают по времени импульсы на входе синхронизации, то на втором выходе ЧФД 3 появляются импульсы сигнала разряда, а если наоборот отстают по времени, то на первом выходе ЧФД 3 появляются импульсы сигнала заряда. В случае совпадения по времени передних фронтов этих сравниваемых импульсных последовательностей ЧФД 3 находится в нейтральном состоянии. При этом импульсы на выходах сигналов заряда и разряда отсутствуют. В результате БУЗН 6 также находится в пассивном нейтральном состоянии. Это состояние соответствует режиму захвата по фазе кольца фазовой автоподстройки (ФАП), и на выходе БОЗФ 7 появляется соответствующий сигнал «ϕ». БОЗФ 7 представляет собой триггерную схему. Входные сигналы предварительно проходят через формирователи импульсов, длительность которых составляет около 10% от периода импульсного сигнала синхронизации. В качестве формирователей импульсов используются ждущие мультивибраторы. При временном интервале между моментами прихода импульсов на входы БОЗФ 7, превышающем длительность импульсов на выходе триггерной схемы, появляется сигнал «ϕ» с уровнем логической «1», а при временном интервале, попадающем в 10% зону - сигнал с уровнем логического «0», который соответствует состоянию синхронизма по фазе. Для преобразования логических состояний ЧФД 3 в аналоговый сигнал, подходящий для подстройки УГ 1, используется БУЗН 6. БУЗН 6 представляет собой устройство, состоящее из двух последовательно соединенных генераторов тока заряда и разряда [см., например, Gardner F.M. Charge-Pump Phase-Lock Loops. // IEEE Transactions on Communications. Vol.com-28, №11 November, 1980, p.1849-1858, пат. US №5055803]. Точка соединения этих генераторов служит для подключения последних к ФНЧ 8. Управление генераторами тока заряда/разряда, т.е. перевод в активное состояние, осуществляется подачей соответствующих сигналов заряда и разряда с ЧФД 3. Генераторы тока имеют одинаковую, но с противоположным знаком величину тока, которую можно изменять с помощью сигнала на входе коммутации (в данном случае сигнал захвата по фазе «ϕ»). БУЗН 6 применяется для преобразования сигнала рассогласования сравниваемых входных сигналов ЧФД 3 в аналоговый сигнал подстройки УГ 1 через ФНЧ 8, от параметров которого в значительной степени зависят динамические и статические параметры кольца ФАП. Под воздействием выходных сигналов заряда или разряда ЧФД 3 через БУЗН 6 напряжение подстройки УГ 1 на выходе ФНЧ 8 меняется до тех пор, пока частота УГ 1 не достигнет требуемого номинального значения ω0. Длительность выходных импульсов сигналов заряда или разряда с ЧФД 3 в установившемся режиме захвата по фазе кольца ФАП стремится к нулю, т.е. ЧФД 3 переходит в режим нейтрального состояния. Использование в замкнутом кольце ФАП ЧФД 3 и БУЗН 6 позволяет получить нулевую статическую фазовую ошибку, т.е. астатизм по фазе (система типа 2) [см., например, Gardner P.M. Charge-Pump Phase-Lock Loops. // IEEE Transactions on Communications. Vol.com-28, №11 November, 1980, p.1849-1858]. В этой схеме синтезатора, на время переходного процесса перестройки, кольцо ФАП переводится в режим с увеличенным значением тока заряда и разряда БУЗН 6 с помощью БОЗФ 7. Кроме того, предлагается использование ФНЧ 8 с переменной полосой пропускания по сигналу «ϕ» с БОЗФ 7: с широкой - в момент переходного процесса и узкой - в условиях захвата по фазе с помощью ключа 8.5. С помощью ключа 8.5 изменяются постоянные времени ФНЧ 8 и, следовательно, его полоса пропускания.

В результате этого, кольцо ФАП в зависимости от величины фазового рассогласования по сигналу захвата по фазе с выхода БОЗФ 7 работает в режиме широкой полосы эффективного регулирования с увеличенным коэффициентом для ускорения переходного процесса перестройки частоты, а при достижении захвата по фазе переводится в режим номинального значения полосы эффективного регулирования и усиления для достижения приемлемых статических параметров качества выходного сигнала синтезатора частот.

Существенным недостатком устройства-прототипа является то, что в нем не увязываются моменты времени изменения значений токов заряда и разряда БУЗН 6 со значениями полосы пропускания ФНЧ 8. Это приводит к резким броскам управляющего напряжения УГ 1 и, как следствие, к потере устойчивости кольца ФАП, а это в свою очередь ведет к замедленному характеру переходного процесса перестройки частоты.

Задачей, которую решает предлагаемое изобретение, является применение в синтезаторе частот астатического кольца ФАП, близкого к оптимальному по быстродействию.

Для решения поставленной задачи в синтезатор частот с астатическим кольцом адаптивной частотно-фазовой автоподстройки, содержащий управляемый генератор, делитель частоты с переменным коэффициентом деления, частотно-фазовый детектор, опорный генератор, делитель частоты с фиксированным коэффициентом деления, блок управляемой зарядовой накачки, блок определения захвата по фазе и фильтр нижних частот, содержащий первый ключ, первый и второй конденсаторы, первый и второй резисторы, при этом выход управляемого генератора, являющийся выходом высокой частоты устройства, соединен с высокочастотным входом делителя частоты с переменным коэффициентом деления, выход которого соединен с первыми, синхронизируемыми входами частотно-фазового детектора и блока определения захвата по фазе, выход делителя частоты с фиксированным коэффициентом деления соединен со вторыми входами частотно-фазового детектора и блока определения захвата по фазе, которые, также, является входами синхронизации, выход опорного генератора соединен с опорным входом делителя частоты с фиксированным коэффициентом деления, первый и второй выходы частотно-фазового детектора, которые являются соответственно выходами сигналов заряда и разряда, соединены соответственно с первым и вторым коммутационными входами блока управляемой зарядовой накачки, которые являются соответственно входами заряда и разряда, выход блока управляемой зарядовой накачки соединен с управляющим входом управляемого генератора и первым выводом первого конденсатора, второй вывод которого соединен с первым выводом первого резистора, причем вторые выводы второго конденсатора и первого ключа соединены с общей шиной, согласно изобретению введены микроконтроллер, вход управления которого является управляющим входом устройства, блок определения захвата по частоте, а в состав фильтра нижних частот введен второй ключ, причем первый, синхронизируемый вход блока определения захвата по частоте соединен с выходом делителя частоты с переменным коэффициентом деления, второй вход блока определения захвата по частоте, который является входом синхронизации, соединен с выходом делителя частоты с фиксированным коэффициентом деления, выход блока определения захвата по частоте соединен с первым информационным входом микроконтроллера, выход блока определения захвата по фазе соединен со вторым информационным входом микроконтроллера, первый выход микроконтроллера является выходом сигнала захвата по частоте и соединен с коммутационным входом второго ключа, второй выход микроконтроллера является выходом сигнала захвата по фазе и соединен с коммутационным входом первого ключа, третий выход микроконтроллера является выходом сигнала сброса и соединен с дополнительно введенными входами установки исходного состояния делителя частоты с переменным коэффициентом деления, делителя частоты с фиксированным коэффициентом деления и частотно-фазового детектора, четвертый выход микроконтроллера, который является управляющим выходом, соединен с дополнительно введенным третьим входом блока управляемой зарядовой накачки, который является входом коммутации величины тока, кроме того, второй вывод первого конденсатора соединен с объединенными первыми выводами второго конденсатора, второго резистора и второго ключа, второй вывод которого соединен с общей шиной, второй вывод второго конденсатора соединен со вторым выводом первого резистора, второй вывод второго резистора соединен с первым выводом первого ключа.

Графические материалы, представленные в материалах заявки:

Фиг.1 - функциональная схема устройства-прототипа.

Фиг.2 - функциональная схема предлагаемого устройства.

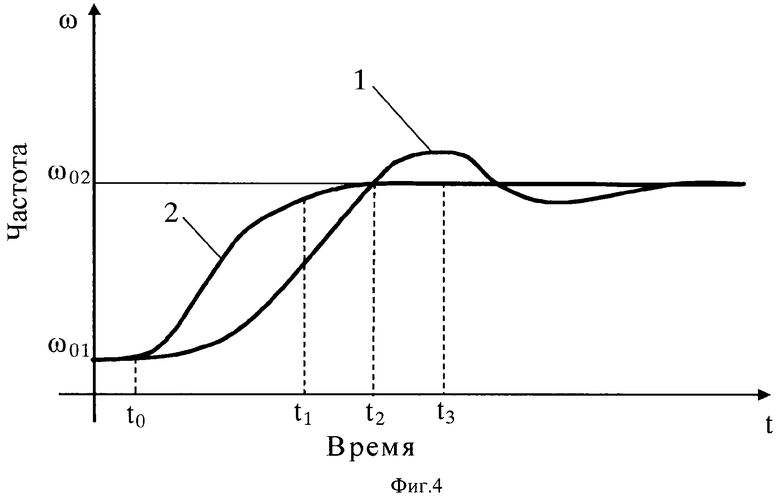

Фиг.3 - временные диаграммы состояний коммутирующих сигналов.

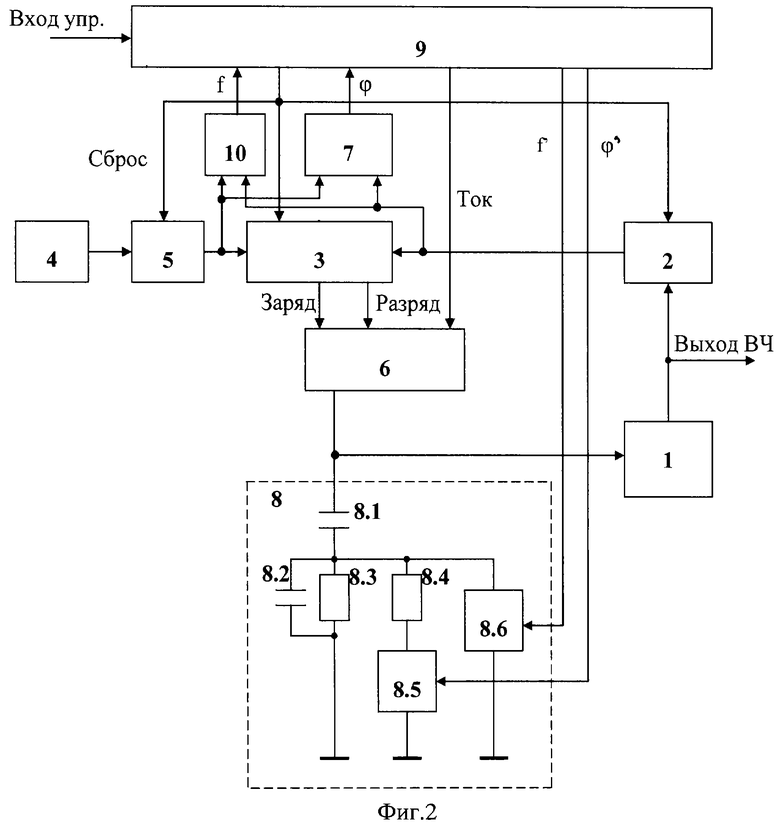

Фиг.4 - график переходного процесса при смене частоты.

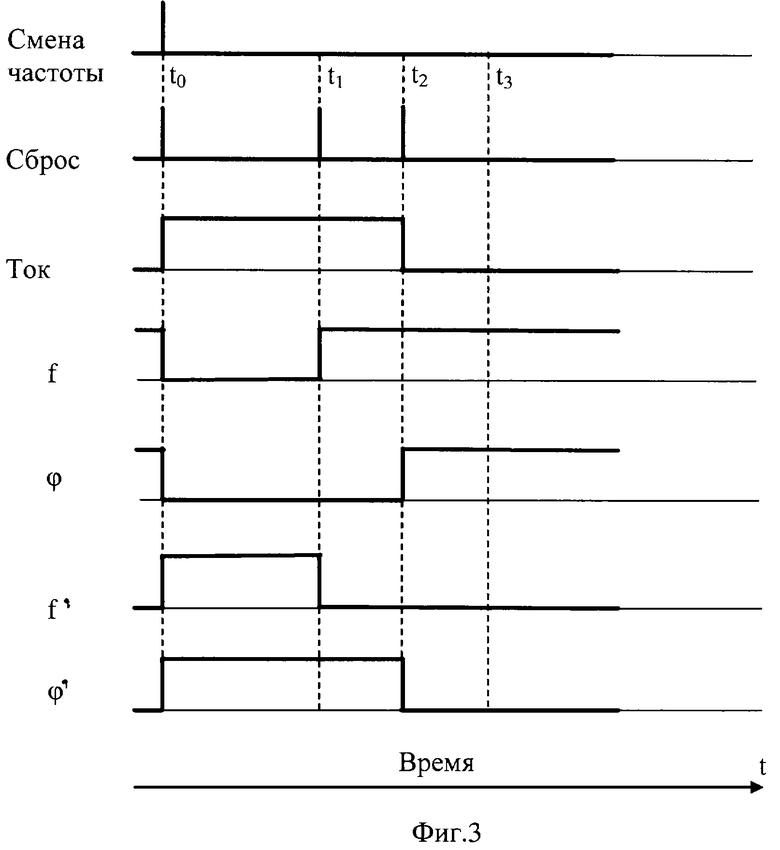

Функциональная схема предлагаемого устройства приведена на фиг.2, где введены следующие обозначения:

1 - управляемый генератор (УГ);

2 - делитель частоты с переменным коэффициентом деления (ДПКД);

3 - частотно-фазовый детектор (ЧФД);

4 - опорный генератор (ОГ);

5 - делитель частоты с фиксированным коэффициентом деления (ДФКД);

6 - блок управляемой зарядовой накачки (БУЗН);

7 - блок определения захвата по фазе (БОЗФ);

8 - фильтр нижних частот (ФНЧ);

8.1, 8.2 - первый и второй конденсаторы;

8.3, 8.4 - первый и второй резисторы;

8.5, 8.6 - первый и второй ключи;

9 - микроконтроллер;

10 - блок определения захвата по частоте (БОЗЧ).

Предлагаемое устройство содержит управляемый генератор (УГ) 1, делитель частоты с переменным коэффициентом деления (ДПКД) 2, частотно-фазовый детектор (ЧФД) 3, опорный генератор (ОГ) 4, делитель частоты с фиксированным коэффициентом деления (ДФКД) 5, блок управляемой зарядовой накачки (БУЗН) 6, блок определения захвата по фазе (БОЗФ) 7, фильтр нижних частот (ФНЧ) 8, микроконтроллер 9, вход управления которого является управляющим входом устройства, блок определения захвата по частоте (БОЗЧ) 10. ФНЧ 8 содержит первый 8.1 и второй 8.2 конденсаторы, первый 8.3 и второй 8.4 резисторы и первый 8.5 и второй 8.6 ключи. При этом выход УГ 1, являющийся выходом высокой частоты устройства, соединен с ВЧ входом ДПКД 2, выход которого соединен с первыми, синхронизируемыми входами ЧФД 3, БОЗФ 7 и БОЗЧ 10. Выход ДФКД 5 соединен со вторыми входами ЧФД 3, БОЗФ 7 и БОЗЧ 10, которые являются входами синхронизации. Выход ОГ 4 соединен с опорным входом ДФКД 5. Первый выход ЧФД 3, который является выходом сигнала заряда, соединен с первым входом БУЗН 6, который является коммутационным входом заряда, а второй выход ЧФД 3, который является выходом сигнала разряда, соединен со вторым входом БУЗН 6, который является коммутационным входом разряда. Выход БОЗЧ 10 (выход «f») является выходом сигнала захвата по частоте и соединен с первым информационным входом микроконтроллера 9, выход БОЗФ 7 (выход «ϕ») является выходом сигнала захвата по фазе и соединен со вторым информационным входом микроконтроллера 9. Первый выход микроконтроллера 9 (выход «f'») является выходом сигнала захвата по частоте и соединен с коммутационным входом второго ключа 8.6, второй выход микроконтроллера 9 (выход «ϕ'») является выходом сигнала захвата по фазе и соединен с коммутационным входом первого ключа 8.5.

Третий выход микроконтроллера 9 является выходом сигнала сброса и соединен со входами установки исходного состояния ДПКД 2, ДФКД 5 и ЧФД 3. Четвертый выход микроконтроллера 9, который является управляющим выходом, соединен с входом коммутации величины тока БУЗН 6, выход которого соединен с управляющим входом УГ 1. В ФНЧ 8 первый вывод первого конденсатора 8.1 объединен с выходом БУЗН 6. Второй вывод первого конденсатора 8.2 соединен с первыми объединенными выводами первого 8.3 и второго 8.4 резисторов, второго конденсатора 8.2 и второго ключа 8.6. Второй вывод второго конденсатора 8.2 объединен со вторым выводом первого резистора 8.1 и соединен с общей шиной. Второй вывод второго резистора 8.4 соединен с первым выводом первого ключа 8.5, второй вывод которого соединен с общей шиной. Второй вывод второго ключа 8.6 также соединен с общей шиной.

Предлагаемое устройство работает следующим образом.

Сигнал опорной частоты с выхода ОГ 4 подается на опорный вход ДФКД 5, где делится по частоте в нужное количество раз. Частота выходного колебания УГ 1 равна требуемому номинальному значению ω0, соответствующему режиму захвата по фазе выходного сигнала ДПКД 2 с выходным сигналом ДФКД 5. При поступлении на вход управления микроконтроллера 9 внешней команды («Смена частоты») на установку вместо ω01 новой частоты ω02 в момент времени t0 (см. фиг.3) с третьего выхода микроконтроллера 9 выдается короткий сигнал с уровнем логической «1» («Сброс») на входы установки в исходное состояние ДПКД 2, ДФКД 5 и ЧФД 3. Исходным состоянием ДПКД 2 и ДФКД 5, выполненных на принципе счета входных импульсов, является сброс счетчиков в нулевое состояние. Исходным состоянием ЧФД 3 является перевод его в нейтральное состояние. Длительность сигнала сброса небольшая, но достаточная для установки ДПКД 2, ДФКД 5 и ЧФД 3 в начальное состояние. После окончания действия сигнала сброса счетчики ДПКД 2 и ДФКД 5 начинают свой счет одновременно, а на одном из выходов ЧФД 3 появляется сигнал заряда или разряда в зависимости от знака рассогласования сравниваемых на его входах сигналов. Тем самым переходной процесс стартует с «нулевой» фазовой разностью на ЧФД 3 (нейтральное состояние), т.е. осуществляется привязка фаз на ЧФД 3 и синхронный счет ДПКД 2 и ДФКД 5. БОЗФ 7 представляет собой цифровой фильтр и вырабатывает логический уровень, поступающий на его выход. На выходе БОЗФ 7 присутствует сигнал с уровнем логического «0», когда временное рассогласование между сигналом синхронизации и синхронизируемым сигналом меньше 15 нс в течение пяти периодов частоты сравнения, равной частоте следования импульсного сигнала синхронизации с выхода ДФКД 5 и поступающего на вход синхронизации ЧФД 3. На выходе БОЗФ 7 устанавливается сигнал с уровнем логической «1», когда временное рассогласование сравниваемых сигналов больше 30 нс в течение одного периода частоты сравнения [см., например, «Lock detect digital filter» в составе микросхемы LMX2485E фирмы National Semiconductor].

БОЗЧ 10 может быть реализован как в виде цифрового фильтра, так и в виде триггерной схемы, аналогичной схеме определения захвата в патенте US №4156855. При достижении рассогласования по частоте менее 5-10% на входах БОЗЧ 10, на его выходе появляется сигнал с уровнем логической «1», а при более существенном рассогласовании (свыше 5-10%) по частоте - сигнал с уровнем логического «0». В стартовый момент времени t0 с выходов БОЗФ 7 и БОЗЧ 10 на микроконтроллер 9 поступают сигналы с уровнем логического «0» отсутствия захвата по частоте и захвата по фазе. В этот же момент с первого выхода микроконтроллера 9 сигнал захвата по частоте с уровнем логической «1» поступает на коммутационный вход второго ключа 8.6, а со второго выхода микроконтроллера 9 сигнал захвата по фазе с уровнем логической «1» поступает на коммутационный вход первого ключа 8.5. Под действием этих сигналов ключи 8.5 и 8.6 замыкаются, изменяя структуру и порядок ФНЧ 8. Сигналом логической «1» с четвертого, управляющего выхода («Ток») микроконтроллера 9 на вход коммутации величины тока БУЗН 6 последний переводится в режим увеличенного значения тока заряда и разряда. С момента времени t0 ЧФД 3 совместно с БУЗН 6 в результате заземления (подключения к общей шине) второго вывода первого конденсатора 8.1 начинает обладать свойствами двухпозиционного электронного ключа, который имеет только два устойчивых состояния для быстрого заряда или разряда второго конденсатора 8.1.

В результате коэффициент усиления в кольце ФАП существенно увеличивается, а постоянные времени ФНЧ 8 уменьшаются после заземления второго вывода первого конденсатора 8.1 и первых объединенных выводов второго конденсатора 8.2 и первого 8.3 и второго 8.4 резисторов с помощью второго ключа 8.6, что в целом приводит к увеличению полосы эффективного регулирования кольца фазовой автоподстройки.

Таким образом, в промежутке времени t0 и t1 реализуется режим широкой полосы эффективного регулирования с увеличенным коэффициентом усиления кольца ФАП. В промежутке времени t0 и t1 кольцо автоподстройки теряет астатизм по фазе, но сохраняет астатизм по частоте. При этом достигается максимальная скорость изменения напряжения на управляющем входе УГ 1. В момент времени t1 достигается равенство сравниваемых частот выходных импульсных последовательностей с ДПКД 2 и ДФКД 5 на ЧФД 3, и поэтому с выхода БОЗЧ 10 на микроконтроллер 9 проходит сигнал захвата по частоте, и с первого выхода микроконтроллера 9 на коммутационный вход второго ключа 8.6 подается сигнал захвата по частоте с уровнем логического «0», который размыкает второй ключ 8.6. В момент t1 на выходе сигнала сброса микроконтроллера 9 появляется короткий импульс с уровнем логической «1» для обнуления счетчиков ДПКД 2 и ДФКД 5 и установки ЧФД 3 в нейтральное состояние, т.е. осуществляется привязка по фазе сравниваемых входных сигналов ЧФД 3 для устранения нежелательных бросков управляющего напряжения с выхода ФНЧ 8 на управляющем входе УГ 1 в момент переключения второго ключа 8.6. Первый резистор 8.3 вновь подключается, но при этом остается «зашунтированным» вторым резистором 8.4, замкнутым первым ключом 8.5. БУЗН 6 остается пока в режиме увеличенного значения тока заряда и разряда. В это время эффект демпфирования в системе автоподстройки возрастает при сохраненном увеличенном значении тока заряда и разряда БУЗН 6. С момента времени t1 переходного процесса система вновь приобретает свойства астатизма по фазе и стремится устранить рассогласование по фазе, имеющееся на момент достижения захвата по частоте. При восстановлении астатизма по фазе в системе ФАП по истечении некоторого времени (порядка пяти периодов частоты сравнения), необходимого для устранения фазового рассогласования, БОЗФ 7 устанавливает факт состояния захвата по фазе в момент времени t2, и на его выходе устанавливается сигнал с уровнем логической «1», поступающий на второй информационный вход микроконтроллера 9. В момент t2 на выходе сигнала сброса микроконтроллера 9 появляется короткий импульс с уровнем логической «1» для очередного обнуления счетчиков ДПКД 2 и ДФКД 5, установки ЧФД 3 в нейтральное состояние и привязки по фазе, а со второго выхода микроконтроллера 9 на коммутационный вход первого ключа 8.5 подается сигнал захвата по фазе с уровнем логического «0», который размыкает первый ключ 8.5, устраняя шунтирование первого резистора 8.3 вторым резистором 8.4. В течение промежутка времени t1 и t2 кольцо ФАП находится в режиме узкой полосы эффективного регулирования для замедления скорости переходного процесса при приближении к установившемуся состоянию. С этого же момента t2 БУЗН 6 переводится в режим номинального значения тока заряда и разряда, т.к. на четвертом, управляющем выходе («Ток») микроконтроллера 9 устанавливается уровень логического «0». При этом эффект демпфирования в системе автоподстройки еще больше возрастает, т.к. значение сопротивления первого резистора 8.3 значительно больше сопротивления второго резистора 8.4. После чего система ФАП синтезатора очень быстро до момента времени t3 производит дерегулирование для последних нескольких сотен герц выходной частоты УГ 1.

Использование ФНЧ 8, переменной величины тока заряда и разряда в БУЗН 6, переменного демпфирования в ФНЧ, синхронного управления ДПКД 2 и ДФКД 5 позволяет системе ФАП синтезатора адаптировать параметры, влияющие на скорость перестройки частоты УГ 1 к новому значению. При этом характер переходного процесса при смене частоты стремится к оптимальному (см. кривую 2 на фиг.4), быстро затухает и не имеет перерегулирования (см. кривую 1 на фиг.4).

Новизна предлагаемого изобретения заключается в том, что для реализации адаптивного режима работы системы в цепи управления управляемого генератора используется ФНЧ с переменной структурой:

- При этом ФНЧ имеет широкую полосу, а кольцо автоподстройки выполняет слежение по частоте (имеет астатизм по частоте). Таким образом, до момента времени t1 система ФАП работает в режиме частотной автоподстройки. В этом случае без лишних аппаратурных затрат (например, как при методе предварительной зарядки с помощью цифроаналогового преобразователя) реализуется ускоренная настройка УГ 1.

- С момента времени t1 система ФАП становится астатической по фазе за счет увеличения порядка ФНЧ 8. Полоса эффективного регулирования кольца при этом устанавливается ниже стартового значения, а увеличенное значение тока зарядовой накачки сохраняется. Переходный процесс с момента t1 до момента t2 происходит с малым демпфированием. Уменьшение демпфирования реализуется шунтированием основного первого резистора 8.3 вспомогательным вторым резистором 8.4.

- В момент времени t2 переходный процесс практически закончен, но для того чтобы получить необходимые характеристики по шумам в статическом режиме, в синтезаторе частот производится оптимизация полосы эффективного регулирования кольца с помощью перехода на оптимальное значение тока зарядовой накачки и значение демпфирующего первого резистора 8.3. Момент времени t3 является началом статического режима фазовой автоподстройки. Промежуток времени между t2 и t3 зависит от точности установки новой частоты (например, ±100 Гц, ±1 кГц и т.д.). При достижении захвата (синхронизма) по частоте производится обнуление счетчиков, входящих в состав ДПКД 2 и ДФКД 5. Это позволяет избежать скачков по фазе на ЧФД при переключении в момент времени t1, и тем самым избежать колебательных процессов, замедляющих переходные процессы.

Таким образом, в предлагаемом синтезаторе частот характер переходного процесса при смене выходных частот существенно улучшается, и сокращается его длительность за счет изменения в определенные моменты времени структуры фильтра нижних частот и параметров блока управляемой зарядовой накачки в течение времени протекания переходного процесса. В результате этого достигается стабилизация передаточной характеристики кольца частотно-фазовой автоподстройки, что позволяет оптимизировать систему по заданному качеству динамических и спектральных характеристик во всем диапазоне синтезируемых колебаний.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2440668C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2416158C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2024 |

|

RU2827940C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Широкодиапазонный синтезатор с фазовой автоподстройкой частоты управляемого генератора с переключаемыми резонаторами | 2023 |

|

RU2804407C1 |

Изобретение относится к радиотехнике и может использоваться для формирования сетки стабильных частот с равномерным шагом в приемных и передающих устройствах с малым временем перестройки в широком диапазоне рабочих частот. Достигаемый технический результат - адаптивная стабилизация передаточной характеристики кольца частотно-фазовой автоподстройки синтезатора частот, что позволяет оптимизировать его по заданному качеству динамических и спектральных характеристик во всем диапазоне синтезируемых колебаний. Устройство содержит управляемый генератор, делитель частоты с переменным коэффициентом деления, частотно-фазовый детектор, опорный генератор, делитель частоты с фиксированным коэффициентом деления, блок управляемой зарядовой накачки, блок определения захвата по фазе, микроконтроллер, блок определения захвата по частоте и фильтр нижних частот, который состоит из двух конденсаторов, двух резисторов и двух ключей. 4 ил.

Синтезатор частот с астатическим кольцом адаптивной частотно-фазовой автоподстройки, содержащий управляемый генератор, делитель частоты с переменным коэффициентом деления, частотно-фазовый детектор, опорный генератор, делитель частоты с фиксированным коэффициентом деления, блок управляемой зарядовой накачки, блок определения захвата по фазе и фильтр нижних частот, содержащий первый ключ, первый и второй конденсаторы, первый и второй резисторы, при этом выход управляемого генератора, являющийся выходом высокой частоты устройства, соединен с высокочастотным входом делителя частоты с переменным коэффициентом деления, выход которого соединен с первыми, синхронизируемыми входами частотно-фазового детектора и блока определения захвата по фазе, выход делителя частоты с фиксированным коэффициентом деления соединен со вторыми входами частотно-фазового детектора и блока определения захвата по фазе, которые также являются входами синхронизации, выход опорного генератора соединен с опорным входом делителя частоты с фиксированным коэффициентом деления, первый и второй выходы частотно-фазового детектора, которые являются соответственно выходами сигналов заряда и разряда, соединены соответственно с первым и вторым коммутационными входами блока управляемой зарядовой накачки, которые являются соответственно входами заряда и разряда, выход блока управляемой зарядовой накачки соединен с управляющим входом управляемого генератора и первым выводом первого конденсатора, второй вывод которого соединен с первым выводом первого резистора, причем вторые выводы второго конденсатора и первого ключа соединены с общей шиной, отличающийся тем, что введены микроконтроллер, вход управления которого является управляющим входом устройства, блок определения захвата по частоте, а в состав фильтра нижних частот введен второй ключ, причем первый, синхронизируемый вход блока определения захвата по частоте соединен с выходом делителя частоты с переменным коэффициентом деления, второй вход блока определения захвата по частоте, который является входом синхронизации, соединен с выходом делителя частоты с фиксированным коэффициентом деления, выход блока определения захвата по частоте соединен с первым информационным входом микроконтроллера, выход блока определения захвата по фазе соединен со вторым информационным входом микроконтроллера, первый выход микроконтроллера является выходом сигнала захвата по частоте и соединен с коммутационным входом второго ключа, второй выход микроконтроллера является выходом сигнала захвата по фазе и соединен с коммутационным входом первого ключа, третий выход микроконтроллера является выходом сигнала сброса и соединен с дополнительно введенными входами установки исходного состояния делителя частоты с переменным коэффициентом деления, делителя частоты с фиксированным коэффициентом деления и частотно-фазового детектора, четвертый выход микроконтроллера, который является управляющим выходом, соединен с дополнительно введенным третьим входом блока управляемой зарядовой накачки, который является входом коммутации величины тока, кроме того, второй вывод первого конденсатора соединен с объединенными первыми выводами второго конденсатора, второго резистора и второго ключа, второй вывод которого соединен с общей шиной, второй вывод второго конденсатора соединен со вторым выводом первого резистора, второй вывод второго резистора соединен с первым выводом первого ключа.

| US 4156855, 29.05.1979 | |||

| ЗАПУСКАЕМЫЙ ЦИФРОВЫМ СИНТЕЗАТОРОМ С ПРЯМЫМ СИНТЕЗОМ ЧАСТОТ СИНТЕЗАТОР ЧАСТОТ С ОЧИЩАЮЩЕЙ СХЕМОЙ ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1996 |

|

RU2176431C2 |

| RU 22140043 C2, 10.10.2003 | |||

| US 5559475 A, 24.09.1996. | |||

Авторы

Даты

2008-07-20—Публикация

2007-04-10—Подача