Предлагаемое изобретение относится к радиотехнике и может использоваться в качестве малошумящего, быстро переключаемого по частоте гетеродина приемника и в других устройствах, где требуется быстрая перестройка по частоте при высокой чистоте спектра выходного сигнала.

Известен синтезатор частот (СЧ), построенный на основе системы фазовой автоподстройки частоты (ФАПЧ) с делителем частоты с переменным коэффициентом деления (ДПКД) в цепи обратной связи (см. Шапиро Д.Н., Паин А.А. Основы теории синтеза частот. - М.: Радио и связь. 1981., с.39, рис.1.7. А также Манассевич В. Синтезаторы частот (Теория и проектирование): Пер. с англ. М.: Связь, 1979 г., с.33, рис.1.15).

Достоинством такого СЧ с применением современных микросхем является возможность формирования на выходе его большого числа дискретных частот со стабильностью, равной стабильности одного опорного кварцевого генератора (ОКГ) при малых габаритах и малой потребляемой мощности постоянного тока.

Недостаток этого однокольцевого СЧ состоит в том, что невозможно получить одновременно высокую чистоту спектра выходного высокочастотного (ВЧ) сигнала при перестройке в широком диапазоне частот с малым шагом сетки частот и высокое быстродействие при переключении с одной частоты на другую.

Известен двухкольцевой СЧ с частотной модуляцией (ЧМ) с последовательным включением колец ФАПЧ, в котором функции частотообразования разделены между первым и вторым кольцами, что уменьшает отмеченные выше противоречия (см. патент на ПМ №63996 от 29 декабря 2006 г.). В этом СЧ первое кольцо узкополосное и является опорным для второго широкополосного выходного кольца. Во втором кольце с использованием делителя частоты с дробным переменным коэффициентом деления (ДДПКД) вместо целочисленного ДПКД можно получить высокое быстродействие, которое в настоящее время необходимо в системах связи на основе быстрого переключения частот по заданной программе. Однако в этом синтезаторе даже с использованием современных микросхем СЧ с ΣΔ-модуляторами (см., например, микросхему ADF4252 фирмы Analog Devices) есть так называемые «помехи дробности», которые на 15-25 дБ ухудшают спектральную чистоту генератора, управляемого напряжением (ГУН) по сравнению с СЧ на основе целочисленного ДПКД, что проверено экспериментально.

Наиболее близким по технической сущности к предложенному является синтезатор частот (см. патент на изобретение RU №2329595 C1, H03L 7/18 от 20.07.2008 г., Бюл. №20), который принят за прототип.

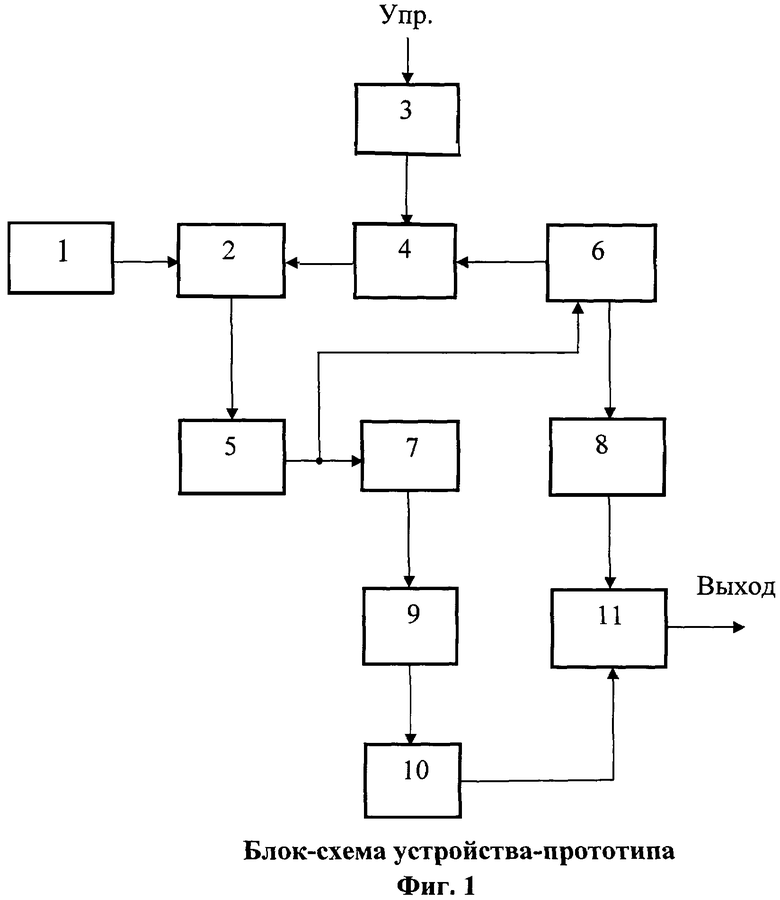

Блок-схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

1 - источник сигнала эталонной частоты (ИСЭЧ);

2 - частотно-фазовый детектор (ЧФД);

3 - блок управления (БУ);

4 - делитель частоты с переменным коэффициентом деления (ДПКД);

5 и 10 - первый и второй фильтры нижних частот (ФНЧ);

6 - генератор, управляемый напряжением (ГУН);

7 - усилитель постоянного тока (УПТ);

8 - делитель напряжения (ДН);

9 - схема сопряжения (ССп);

11 - двухрежимный автогенератор (ДА);

Устройство-прототип содержит последовательно соединенные источник сигнала эталонной частоты ИСЭЧ 1, частотно-фазовый детектор ЧФД 2, первый фильтр нижних частот ФНЧ 5, усилитель постоянного тока УПТ 7, схему сопряжения ССп 9 и второй ФНЧ 10, выход которого соединен с управляющим входом двухрежимного автогенератора ДА 11; последовательно соединенные генератор, управляемый напряжением ГУН 6 и делитель напряжения ДН 8, выход которого соединен с высокочастотным (ВЧ) входом ДА 11, выход которого является выходом устройства. Кроме того, выход первого ФНЧ 5 соединен с управляющим входом ГУН 6, второй выход которого через делитель частоты с переменным коэффициентом деления ДПКД 4 соединен со вторым входом ЧФД 2. Управляющим входом устройства является вход блока управления БУ 3, выход которого соединен с управляющим входом ДПКД 4.

Устройство-прототип работает следующим образом.

Управляющая команда на включение поступает на вход БУ 3, выходной сигнал которого является командой на установление задаваемого (например, равного N) коэффициента деления ДПКД 4. Сигнал с первого выхода ГУН 6 через ДПКД 4 подается на второй вход ЧФД 2, на первый вход которого подается сигнал от ИСЭЧ 1.

При этом выходное напряжение ЧФД 2 через первый ФНЧ 5 подается на управляющий вход ГУН 6. И через определенный отрезок времени Т3, равный времени вхождения в синхронизм кольца ФАПЧ, на выходах ГУН 6 обеспечивается получение частоты, точно равной эталонной частоте, умноженной на N - коэффициент деления ДПКД 4. Таким образом, работает кольцо ФАПЧ, в которое входит ГУН 6.

В то же время выходное напряжение с первого ФНЧ 5 через цепочку, состоящую из последовательно соединенных УПТ 7, ССп 9 и второго ФНЧ 10, подается на управляющий вход ДА 11. Причем коэффициенты передачи блоков 7, 9 и 10 выбраны таким образом, что частота автоколебаний (собственных колебаний) ДА 11 близка к частоте колебаний ГУН 6. Под воздействием этого управляющего напряжения частота автоколебаний ДА 11 устанавливается близкой к частоте колебаний ГУН 6, с первого выхода которого через ДН 8 гармонический ВЧ сигнал подается на ВЧ вход ДА 11.

Под воздействием этого ВЧ напряжения (внешнего) ДА 11 переходит в режим захвата, при котором частота колебаний ДА 11 становится равной частоте колебаний ГУН 6.

Такое построение позволяет иметь на выходе устройства (к которому подключается нагрузка) напряжение с частотой, равной синтезированной в ГУН 6, который охвачен кольцом ФАПЧ, а шумы - соответствующие шумам ДА 11, который работает в режиме автоколебаний.

Эти шумы автогенератора без кольца ФАПЧ значительно ниже, чем у синтезаторов с кольцом ИФАПЧ на основе целочисленного ДПКД (примерно на 20-30 дБ согласно данным, приведенным в описании синтезатора-прототипа на стр.2).

Недостаток рассмотренного синтезатора-прототипа состоит в следующем.

1. Двухрежимный автогенератор ДА 11 постоянно подключен к кольцу ФАПЧ (и в переходном режиме, и в режиме синхронизма) с двух сторон: со стороны выхода петлевого ФНЧ 5 через цепочку из УПТ 7, ССп 9 и ФНЧ 10 поступает управляющее напряжение Uупр и со стороны ВЧ выхода ГУН 6 через ДН 8 поступает ВЧ напряжение внешнего возбуждения. Это приводит к тому, что в переходном режиме при переключении частот захват на новой частоте в ДА 11 происходит с большой задержкой, поскольку на ДА 11 действуют подстройки одновременно с двух сторон с разными частотами и разным фазовым набегом (возможно и в противофазе).

А в режиме синхронизма из-за того, что управляющий вход ДА 11 через цепочку из УПТ 7, ССп 9 и ФНЧ 10 постоянно подключен к выходу петлевого ФНЧ 5, побочные составляющие и шумы, имеющиеся на выходе ФНЧ 5 и ухудшающие шумовые характеристики ГУН 6 в кольце ФАПЧ, воздействуют и на ДА 11, модулируя соответственно его частоту в режиме захвата. Иначе говоря, в этом СЧ «шумы» на выходе ДА 11 гораздо больше, чем если бы ДА 11 работал в автономном режиме (без кольца ФАПЧ).

2. Быстродействию мешает и то, что по цепочке из последовательно соединенных УПТ 7, ССп 9 и второго ФНЧ 10 невозможно подстроить ДА 11 по частоте и фазе так же точно, как ГУН 6. Управляющие напряжения для двух автогенераторов (ГУН 6 и ДА 11) при одной и той же частоте всегда отличаются. Тем более это отличие будет сильно выражено при перестройке в диапазоне частот.

Известно (см., например, Бокк О.А. Теория воздействия на автогенератор шума и внешних колебаний. // Теория и техника радиосвязи, Научно-технический сборник, ОАО «Концерн «Созвездие», Воронеж, 2006 г., №1, с.106-112), что при захвате частоты переходный процесс в автогенераторе зависит от амплитуды и начальной фазы внешнего колебания. При этом длительность процесса установления (захвата) частоты в автогенераторе возрастает с уменьшением значения напряжения внешнего возбуждения Еос и увеличением начальной разности фаз внешнего колебания относительно автоколебаний. Иначе говоря, значение напряжения внешнего возбуждения Еос при захвате частоты в переходном процессе в автогенераторе ДА 11 должно быть большим, а после установления частоты уменьшится до минимально возможного уровня.

3. В синтезаторе-прототипе ВЧ напряжение (внешнее возбуждение Еос по отношению к ДА 11) с первого выхода ГУН 6 через постоянный делитель напряжения ДН 8 подается в колебательную цепь ДА 11. Тогда "шум" в составе напряжения внешнего возбуждения Еос будет фильтроваться контуром автогенератора ДА 11. Чтобы этот "шум" в стационарном режиме был минимальный, предусмотрен делитель ДН 8, с помощью которого уровень внешнего ВЧ напряжения устанавливается немного больше минимально необходимого для осуществления захвата частоты в ДА 11. Но при этом длительность процесса захвата частоты в автогенераторе возрастает.

Таким образом, недостатками синтезатора-прототипа являются ухудшение чистоты спектра выходного сигнала ДА 11 (из-за побочных составляющих и шума, которые поступают постоянно на управляющий вход ДА 11 с выхода ФНЧ 5 через цепочку из УПТ 7, ССп 9 и ФНЧ 10) и невысокое быстродействие при переключении частот и захвате частоты в ДА 11.

Для устранения указанных недостатков в синтезатор частот, содержащий последовательно соединенные генератор, управляемый напряжением, первый делитель частоты с переменным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, выход которого соединен с управляющим входом генератора, управляемого напряжением, второй фильтр нижних частот, выход которого соединен с управляющим входом двухрежимного автогенератора, первый выход которого является выходом устройства, а также источник сигнала эталонной частоты, введены первый делитель частоты с фиксированным коэффициентом деления, второй делитель частоты с фиксированным коэффициентом деления, второй частотно-фазовый детектор, первый выход которого соединен с входом второго фильтра нижних частот, последовательно соединенные логическая схема совпадения, D-триггер и микроконтроллер, на второй вход которого поступает управляющая команда «Упр»; последовательно соединенные управляемый аттенюатор и ключ, выход которого соединен с высокочастотным входом двухрежимного автогенератора, второй выход которого соединен с сигнальным входом второго делителя частоты с переменным коэффициентом деления, выход которого соединен со вторым входом второго частотно-фазового детектора; первый индикатор синхронизма, вход которого соединен со вторым выходом первого частотно-фазового детектора; второй индикатор синхронизма, вход которого соединен со вторым выходом второго частотно-фазового детектора; выход первого делителя частоты с фиксированным коэффициентом деления соединен со вторым входом первого частотно-фазового детектора; выход второго делителя частоты с фиксированным коэффициентом деления соединен со вторым входом второго частотно-фазового детектора, входы первого и второго делителей частоты с фиксированным коэффициентом деления соединены с выходом источника сигнала эталонной частоты, выход первого индикатора синхронизма соединен с первым входом логической схемы совпадения, со вторым входом которой соединен выход второго индикатора синхронизма; второй выход генератора, управляемого напряжением соединен с входом управляемого аттенюатора, при этом первый выход микроконтроллера соединен со вторым входом D-триггера, второй выход микроконтроллера соединен с управляющим входом ключа, третий выход микроконтроллера по первой управляющей шине соединен с управляющими входами первого делителя частоты с фиксированным коэффициентом деления, первого частотно-фазового детектора, первого делителя частоты с переменным коэффициентом деления, образующими цифровую часть первого кольца фазовой автоподстройки частоты; четвертый выход микроконтроллера по второй управляющей шине соединен с управляющим входом управляемого аттенюатора, пятый выход микроконтроллера по третьей управляющей шине соединен с управляющими входами второго делителя частоты с фиксированным коэффициентом деления, второго частотно-фазового детектора, второго делителя частоты с переменным коэффициентом деления, образующими цифровую часть второго кольца фазовой автоподстройки частоты.

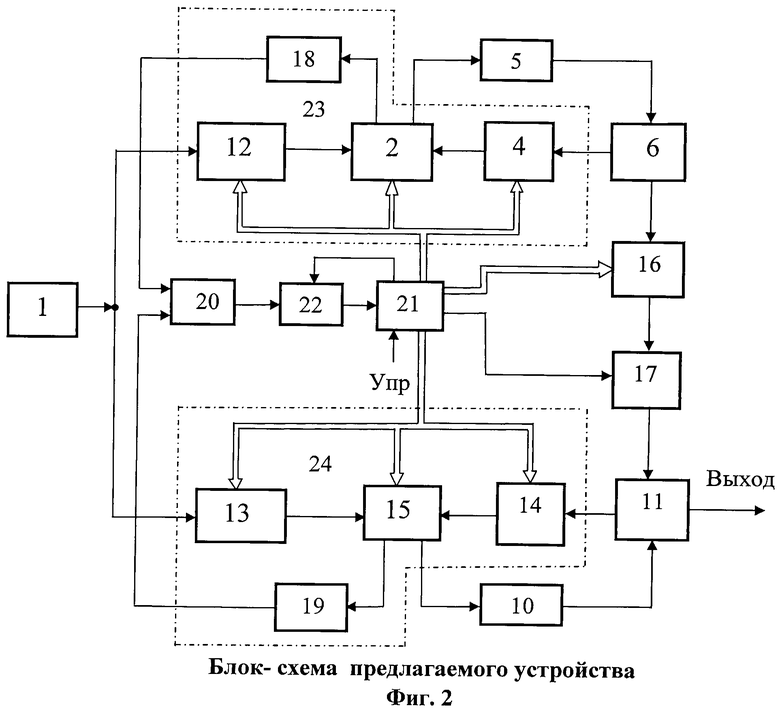

Блок-схема предлагаемого устройства приведена на фиг.2, где введены следующие обозначения:

1 - источник сигнала эталонной частоты (ИСЭЧ);

2 и 15 - первый и второй частотно-фазовые детекторы (ЧФД);

4 и 14 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

5 и 10 - первый и второй фильтры нижних частот (ФНЧ);

6 - генератор, управляемый напряжением (ГУН);

11 - двухрежимный автогенератор (ДА);

12 и 13 - первый и второй делители частоты с фиксированным коэффициентом деления (ДФКД);

16 - управляемый аттенюатор (УА);

17 - ключ (Кл);

18 и 19 - первый и второй индикаторы синхронизма (ИС);

20 - логическая схема совпадения (СС);

21 - микроконтроллер (МК);

22 - D-триггер.

Предлагаемое устройство построено на основе двух параллельно включенных колец ФАПЧ с общим источником сигнала эталонной частоты ИСЭЧ 1. В первом кольце ФАПЧ в качестве управляемого генератора используется ГУН 6, а во втором - ДА 11. Первое кольцо ФАГГЧ содержит последовательно соединенные ГУН 6, первый ДПКД 4, первый ЧФД 2, первый ФНЧ 5, выход которого соединен с управляющим входом ГУН 6. Второе кольцо ФАПЧ содержит последовательно соединенные ДА 11, второй ДПКД 14, второй ЧФД 15, второй ФНЧ 10, выход которого соединен с управляющим входом ДА 11, первый выход которого является выходом устройства.

Кроме того, имеется первый ДФКД 12, выход которого соединен со вторым входом первого ЧФД 2, второй ДФКД 13, выход которого соединен со вторым входом второго ЧФД 15, а входы первого ДФКД 12 и второго ДФКД 13 соединены с выходом ИСЭЧ 1. Предлагаемое устройство содержит также последовательно соединенные схему совпадений СС 20, Д-триггер 22 и микроконтроллер МК 21; последовательно соединенные УА 16 и ключ Кл 17, выход которого соединен с ВЧ входом ДА 11; первый ИС 18 и второй ИС 19, входы которых соединены соответственно со вторыми выходами первого ЧФД 2 и второго ЧФД 15, а выходы первого ИС 18 и второго ИС 19 соединены соответственно с первым и вторым входами СС 20. Сигнальный вход УА 16 соединен со вторым выходом ГУН 6.

При этом первый выход МК 21 соединен со вторым входом D-триггера 22 (входом сброса D-триггера 22), второй выход МК 21 соединен с управляющим входом Кл 17. Третий выход МК 21 соединен с первой управляющей шиной, которая соединена с управляющими входами первого ДФКД 12, первого ЧФД 2, первого ДПКД 4. Четвертый выход МК 21 соединен со второй управляющей шиной, которая соединена с управляющим входом УА 16. Пятый выход МК 21 соединен с третьей управляющей шиной, которая соединена с управляющими входами второго ДФКД 13, второго ЧФД 15, второго ДПКД 14. На второй вход МК 21 поступает управляющая команда «Упр» на включение заданной частоты СЧ.

Выделенные пунктирной рамкой блоки: первый ДФКД 12, первый ЧФД 2, первый ДПКД 4 и первый ИС 18 представляют собой цифровую часть 23 первого кольца ФАПЧ и входят в состав первой микросхемы цифрового синтезатора частот, а выделенные пунктирной рамкой блоки: второй ДФКД 13, второй ЧФД 15, второй ДПКД 14 и второй ИС 19 представляют собой цифровую часть 24 второго кольца ФАПЧ и входят в состав второй микросхемы СЧ (см., например, микросхемы синтезаторов частот LMX2364 фирмы National Semiconductor, микросхемы ADF4001, ADF4252 фирмы Analog Devices).

Предлагаемое устройство работает следующим образом.

Управляющая команда «Упр» на включение одной из n частот предлагаемого синтезатора частот поступает на второй вход микроконтроллера МК 21, который оснащен встроенной оперативной памятью данных и адресов программы (см., например, О.Николайчук. х51-совместимые микроконтроллеры фирмы Silicon Laboratories (Cygnal). - М.: ООО «ИД СКИМЕН», 2004 г., с.50). Все микроконтроллеры фирмы Silicon Laboratories имеют встроенную Flash-память программ-данных (объемом от 8 до 128К), встроенную дополнительную оперативную память (объемом от 1 до 8К), стандартное количество портов ввода/вывода (4 порта - 32 линии ввода/вывода) и многое другое.

Управление работой двух микросхем СЧ и других блоков предлагаемого устройства осуществляется от МК 21, который выполняет не только те функции, что и БУ 3 в прототипе, но гораздо более широкие. Применяемый в предлагаемом устройстве микроконтроллер МК 21 типа C8051F220 фирмы Silicon Laboratories (см. вышеназванную книгу О.Николайчук, с.311) формирует на своих выводах управляющие импульсные сигналы, которые поступают на соответствующие блоки 1 и 2 колец ФАПЧ, а также в УА 16, Кл 17 по заданному алгоритму работы, определяемому заложенной в МК 21 программой, а также обратной связью, поступающей на его первый вход с D-триггера 22.

В память программ МК 21 предварительно записывается определенный порядок действий (алгоритм) после поступления внешней управляющей команды «Упр». А в памяти данных записаны кодограммы, по которым в обоих кольцах ФАПЧ, т.е. в обоих параллельно включенных синтезаторах частот, включаются заданные частоты, формируются необходимые величины токов в генераторах тока первого ЧФД 2 и второго ЧФД 15, коэффициенты передачи УА 16 и т.д.

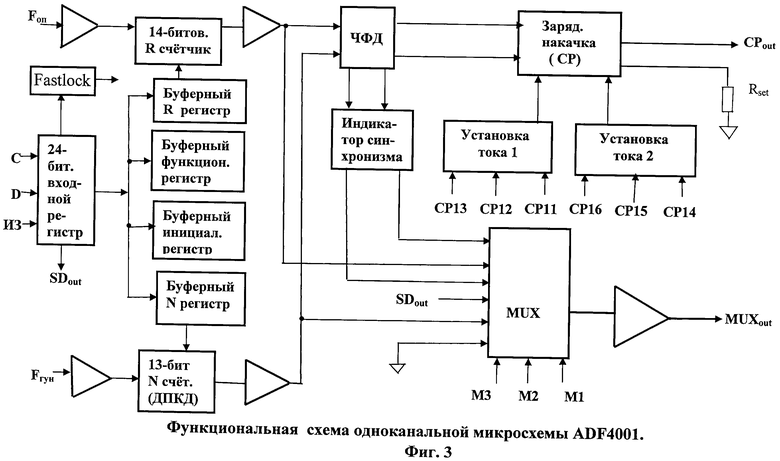

Порядок формирования и прохождения кодограмм управления рассмотрим на примере применяемой в предлагаемом устройстве микросхемы синтезатора частот типа ADF4001 фирмы Analog Devices. От микроконтроллера МК 21 информация (данные) в виде последовательного двоичного кода поступает по первой и третьей управляющей шине на управляющие входы 1 и 2 микросхемы синтезатора частот ADF4001 (на цифровые части 23 и 24), в регистры соответствующих блоков.

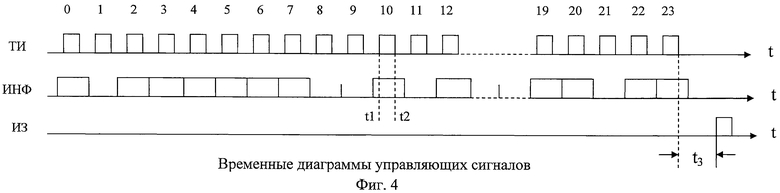

Управляющая шина с выхода микроконтроллера МК 21 представляет собой стандартный трехпроводный интерфейс, где по трем проводам поступают в последовательном двоичном коде импульсные сигналы: 1) тактовые импульсы (ТИ), 2) информационный сигнал (ИНФ), 3) импульс разрешения записи передаваемой информации (ИЗ) в один из регистров синтезатора. Причем для всех регистров общими проводами являются ТИ и ИНФ, а импульс разрешения записи информации ИЗ поступает по отдельному проводу только в каждый предназначенный для этого регистр.

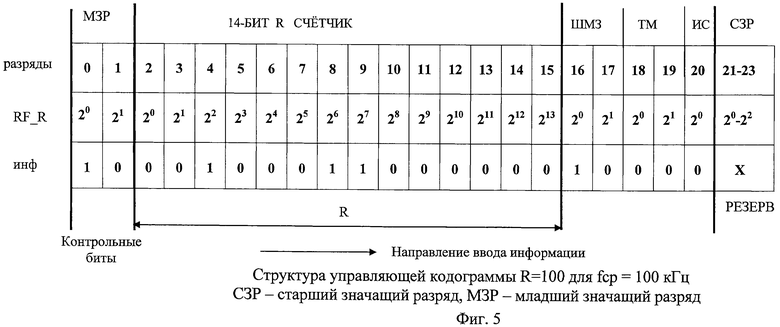

В микросхеме синтезатора частот ADF4001 имеется 24 разрядный входной регистр, с выхода которого информация в виде последовательного двоичного кода поступает на 4 сдвиговых регистра по 24 разряда (бита) каждый. В первый регистр записывается кодограмма для 14 разрядного опорного R-счетчика (для ДФКД), во второй регистр записывается кодограмма для 13 разрядного N-счетчика (для ДПКД), в третий регистр записывается информация для установки токов в ЧФД, сброса счетчиков, различных выходов внутреннего мультиплексора и т.д. В четвертом регистре инициализации записывается информация, аналогичная третьему регистру (см. функциональную схему ЦСЧ на микросхеме ADF4001 на фиг.3)

Адресация каждой кодограммы заданному регистру СЧ определяется первыми двумя контрольными битами кодограммы С1 и С2. Иначе говоря, информация, поступающая с выхода МК 21 по управляющей шине на информационный вход микросхемы синтезатора частот ADF4001, проходит только в тот регистр, для которого заданы определенные контрольные первые два бита кодограммы. Окончание входной кодограммы определяется импульсом разрешения записи ИЗ ее в регистр после 24 тактового импульса. В качестве примера на фиг.4 показаны временные диаграммы управляющих сигналов в виде одной группы, состоящей из 24 разрядной последовательности тактовых импульсов ТИ, информационных импульсов ИНФ и импульса записи ИЗ. На фиг.5 приведена в качестве примера структура управляющей кодограммы для R-счетчика (ДФКД).

Таким образом, информация ИНФ в виде определенной кодограммы и сопровождающих ее тактовых импульсов ТИ и импульса разрешения записи ИЗ ее в регистр передается с выхода МК 21 по управляющей шине на управляющий вход микросхемы СЧ последовательными группами по числу регистров в каждом СЧ. Между каждой группой импульсов есть небольшой разделительный временной интервал. Конкретно для одной микросхемы синтезатора частот ADF4001 по управляющей шине проходит 4 группы импульсов по трем проводам (для 4 регистров). Порядок прохождения этих групп (т.е. какая группа проходит первой, второй и т.д.) выбирает разработчик для получения максимального быстродействия.

Построение микроконтроллера МК 21 на основе микросхемы типа C8051F220 фирмы Silicon Laboratories с 4 портами и 32 линиями вход/выход позволяет создать различные управляющие шины и отдельные провода для полного управления различными блоками предлагаемого устройства.

Аналогично происходит прохождение управляющих сигналов и для других микросхем синтезаторов частот.

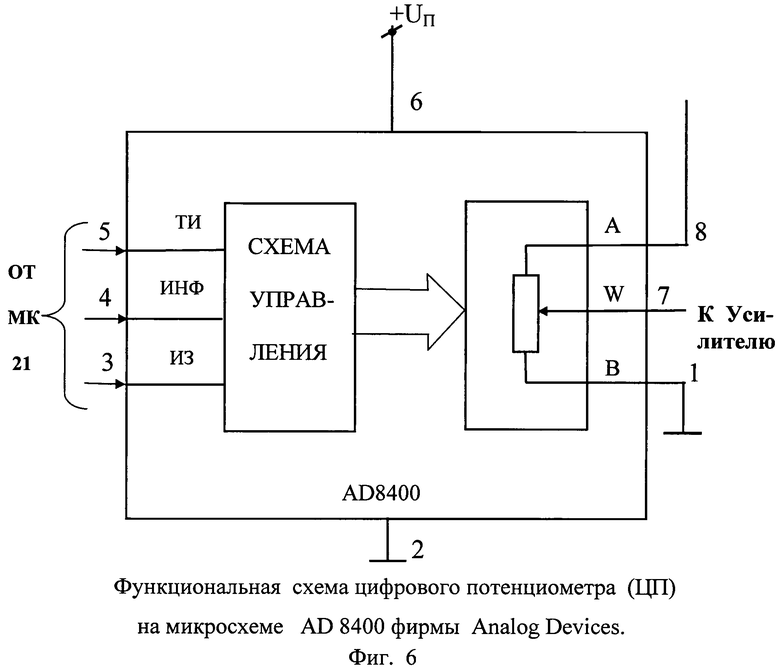

Управляемый аттенюатор УА 16 построен на основе цифрового потенциометра (ЦП) типа AD8400 фирмы Analog Devices и ВЧ транзисторного усилителя, через который проходит ВЧ сигнал с выхода ГУН 6 через открытый ключ Кл 17 на ВЧ вход ДА 11.

Цифровой потенциометр AD8400 представляет собой устройство для декодирования входных величин, выраженных в двоичном коде, в соответствующие им значения сопротивлений на выходе и может выполнять в аппаратуре разные функции, в том числе и функцию обычного переменного сопротивления. В УА 16 это переменное сопротивление является частью сопротивления в цепи эмиттера ВЧ усилителя. При изменении эмиттерного сопротивления ВЧ усилителя соответственно изменяется его коэффициент усиления.

На выходе ЦП могут устанавливаться 256 программируемых дискретных значений номинального сопротивления. Это выходное переменное сопротивление ЦП является в данном случае частью сопротивления в цепи обратной связи ВЧ усилителя (см. функциональную схему ЦП на фиг.6).

Цифровой потенциометр AD8400 состоит из 10 разрядного сдвигового регистра, схемы выбора адреса регулируемого сопротивления, восьмиразрядной ключевой схемы с фиксацией состояния на выходе каждого разряда и переменного сопротивления, принимающего значения от 50 до 10 кОм (через 390 м).

Управляющие входные числа поступают на ЦП от микроконтроллера МК 21 по второй управляющей шине в последовательном коде по трехпроводному стандартному интерфейсу, в котором имеется

1) информация о коде числа,

2) тактовые импульсы,

3) импульс разрешения записи информации в микросхему.

В зависимости от кода числа, приходящего от МК 21, устанавливается определенное значение переменного сопротивления ЦП и соответствующий коэффициент передачи УА 16.

Второй выход МК 21 соединен с управляющим входом Кл 17 одним проводом, по которому передаются сигналы Лог.0 и Лог.1 для выключения и включения Кл 17.

При включении предлагаемого устройства на первом этапе работы с первого и второго выхода МК 21 и по трем управляющим шинам поступают управляющие сигналы на соответствующие входы блоков первого и второго кольца ФАПЧ, D-триггер 22, УА 16 и Кл 17, который при этом отключается, а D-триггер 22 сбрасывается в исходное состояние. В результате ВЧ сигнал с выхода ГУН 6 не поступает на ВЧ вход ДА 11 и оба кольца ФАПЧ работают автономно и синхронно. В обоих кольцах записываются одинаковые коэффициенты деления N в ДПКД 4 и в ДПКД 14 и цифровые ЧФД 2 и 15 работают на равных опорных частотах сравнения FCP1=FCP2, формируемых от ИСЭЧ 1 с помощью соответственно первого ДФКД 12 и второго ДФКД 13. В генераторах тока на выходах ЧФД 2 и 15 устанавливается повышенное значение токов заряда и разряда конденсаторов в петлевых ФНЧ 2 и 10 для повышения быстродействия в переходном режиме. Синхронность начала счета в первом ДФКД 12 и втором ДФКД 13 после переключения на заданную частоту обеспечивается по сигналу управления (по импульсу сброса «Reset», точнее по заднему фронту импульса сброса «Reset»), поступающему по управляющей шине с выхода МК 21 на регистры опорных R-счетчиков (для ДФКД). При этом на выходах первого ДФКД 12 и второго ДФКД 13 формируются опорные частоты сравнения FCP1 и FCP2, равные не только по частоте, но и по фазе. В каждом кольце ФАПЧ используются цифровые ЧФД с тремя состояниями, известный принцип работы которых состоит в том, что в режиме синхронизма на обоих входах такого ЧФД формируются сигналы, равные не только по частоте, но и практически по фазе (см., например, микросхемы синтезаторов частот LMX2364 фирмы National Semiconductor, микросхемы синтезаторов частот ADF4001, ADF4252 фирмы Analog Devices). Эти цифровые ЧФД обеспечивают в режиме синхронизма в кольце ФАПЧ астатизм второго порядка по частоте, т.е. синфазность системы.

В результате в каждом кольце ФАПЧ происходит быстрое и одновременное вхождение в синхронизм.

После вхождения в синхронизм на выходах ГУН 6 и ДА 11 образуются колебания с одинаковой частотой с точностью до фазы общего опорного сигнала, а на выходах первого ИС 18 и второго ИС 19 формируются перепады уровней сигналов из Лог.0 в Лог.1, обозначающие наличие синхронизма в кольцах ФАПЧ. Эти перепады логических уровней поступают соответственно на первый и второй входы схемы совпадения СС 20, на выходе которой также формируется перепад из Лог.0 в Лог.1, который поступает на вход D-триггера 22, а с его выхода - на первый вход МК 21.

В результате на выходах МК 21 теперь формируются управляющие сигналы, которые поступают на соответствующие входы УА 16, Кл 17, первого ЧФД 2 и второго ЧФД 15.

Иначе говоря, по заданному алгоритму работы начинается второй этап работы устройства. При этом Кл 17 открывается и на ВЧ вход ДА 11 проходит ВЧ напряжение с выхода ГУН 6, а управляемый аттенюатор УА 16 переключается в режим, когда через него проходит сигнал, гораздо больший, чем в установившемся состоянии после захвата частоты в ДА 11. Этот режим необходим для ускорения процесса захвата частоты в ДА 11 и по времени он не больше времени захвата частоты. После захвата частоты в ДА 11 происходит переключение коэффициента передачи УА 16 по сигналу управления с МК 21, когда на ВЧ вход ДА 11 поступает от ГУН 6 ВЧ напряжение по уровню, лишь немного превышающем минимально необходимый для захвата по частоте в ДА 11.

После вхождения в синхронизм синтезаторов частот ток в генераторах тока на выходе ЧФД 2 уменьшается по сигналу с МК 21 до минимального, при котором обеспечивается необходимое подавление побочных составляющих и шумов в выходном сигнале ГУН 6. По сигналу от МК 21 происходит переключение ЧФД 15 в третье состояние, второе кольцо ФАПЧ разрывается и на выходе ФНЧ сохраняется постоянное управляющее напряжение ("подставка"), которое в режиме синхронизма поступало на управляющий вход ДА 11. Третье состояние ЧФД характеризуется тем, что его выход внутри микросхемы отключается от всех цепей и имеет очень высокое выходное сопротивление (см., например, описание микросхем синтезаторов ADF4252, ADF4001, ADF4153 фирмы Analog Devices, LMX2364, LMX2470 фирмы National Semiconductor). Поэтому петлевой ФНЧ (обычно активный ФНЧ на операционном усилителе), соединенный с таким выходом ЧФД, сохраняет то управляющее напряжение, которое было перед отключением ЧФД. При этом второе кольцо ФАПЧ разомкнуто и происходит быстрый захват частоты в ДА 11 от ВЧ сигнала, поступающего через открытый Кл 17 со второго выхода ГУН 6. Поскольку ДА 11 теперь работает как в автономном режиме, то получается высокая чистота спектра выходного сигнала.

Для переключения на другую частоту на второй вход МК 21 подается соответствующий сигнал «Упр» и все повторяется, как описано выше.

В каждом кольце при переключении частот по сигналам от МК 21 происходит сброс D-триггера 22 в исходное состояние, синхронный сброс и пуск обоих счетчиков кольца (ДФКД и ДПКД), когда оба счетчика начинают счет одновременно. Это позволяет значительно увеличить быстродействие по сравнению с тем, если бы оба счетчика срабатывали случайно в разное время - при этом получалось бы затягивание времени вхождения в синхронизм.

Основное достоинство предложенного технического решения в том, что с помощью введенных новых элементов, объединенных соответствующими связями с остальными узлами схемы, в переходном режиме осуществляется синхронная работа двух одинаковых колец ФАПЧ с установлением в них одинаковых частот с точностью до фазы общего источника эталонной частоты. Это дает возможность значительного уменьшения времени вхождения в синхронизм в каждом кольце при переключении с одной частоты на другую, быстрого последующего перехода двухрежимного автогенератора ДА 11 в автономный режим и затем максимально быстрого захвата его частоты от ГУН 6 (т.к. частоты ДА 11 и ГУН 6 перед этим были равны с точностью до фазы). Одновременно с высоким быстродействием осуществляется получение высокой чистоты спектра выходного сигнала.

Доказательством возможности осуществления предлагаемого устройства является то, что вводимые блоки типовые и могут быть выполнены на широко известных микросхемах. Цифровая часть синтезаторов выполняется на микросхемах ЦСЧ с ФАПЧ разных фирм. При этом в одной микросхеме могут быть один или два независимых ЦСЧ с целочисленным ДПКД (Integer-N) или с дробным (Fractional-N). Например, микросхемы LMX2364, LMX2470 фирмы National Semiconductor, микросхемы ADF4252 фирмы Analog Devices представляют собой двойной синтезатор с двумя раздельными контурами регулирования: один с дробным ДПКД (ДДПКД), другой с целочисленным ДПКД. Микросхема ADF4001 фирмы Analog Devices имеет только один целочисленный ДПКД, прецизионный ЧФД и ультранизкий фазовый шум. Индикаторы синхронизма ИС обычно входят в состав этих микросхем на выходе ЧФД и бывают двух типов: цифровой и аналоговый. Цифровой ИС работает так, что, если в трех (или пяти) последовательных циклах измерения фазовое рассогласование между импульсами двух потоков импульсов на входах ЧФД меньше 15 нсек, то имеется синхронизм в кольце ФАПЧ и на выходе цифрового ИС формируется уровень Лог.1. Если фазовая ошибка больше 25 нсек в одном цикле измерения, то синхронизма нет, и на выходе цифрового ИС формируется уровень Лог.0. Логическая схема совпадения на два входа может быть выполнена на микросхеме 564 ЛА7. Управляемый аттенюатор УА 16 может быть выполнен на основе цифрового потенциометра на микросхеме AD8400 фирмы Analog Devices и ВЧ усилителя. Через усилитель проходит ВЧ сигнал от ГУН 6 на вход КЛ 16, а коэффициент усиления усилителя регулируется с помощью цифрового потенциометра на микросхеме AD8400, на который от МК 21 (микроконтроллер типа C8051F221 фирмы SILABS) поступает управляющий сигнал по управляющей шине.

Таким образом, в предложенном синтезаторе частот решена противоречивая проблема одновременного получения высокой чистоты спектра выходного сигнала и высокого быстродействия при переключении частот.

Это позволяет использовать предложенный синтезатор частот с высокой чистотой спектра выходного сигнала в современных системах радиосвязи с быстрой перестройкой частоты по заданной программе.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2416158C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2394367C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2440668C1 |

| СИСТЕМА СВЯЗИ СВЕРХШИРОКОПОЛОСНЫМИ СИГНАЛАМИ С ПОВЫШЕННОЙ ТОЧНОСТЬЮ И СТАБИЛЬНОСТЬЮ СИНХРОНИЗАЦИИ | 2010 |

|

RU2441320C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Синтезатор частот с широкополосной модуляцией | 2019 |

|

RU2713569C1 |

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

Предлагаемое изобретение относится к радиотехнике и может использоваться в качестве малошумящего быстро переключаемого по частоте гетеродина приемника и в других устройствах, где требуется быстрая перестройка по частоте при высокой чистоте спектра выходного сигнала. Техническим результатом является повышение быстродействия и чистоты спектра выходного сигнала синтезатора частот. Синтезатор частот содержит генератор, управляемый напряжением, два делителя частоты с переменным коэффициентом деления, два фильтра нижних частот, источник сигнала эталонной частоты, два делителя частоты с фиксированным коэффициентом деления, два частотно-фазовых детектора, управляемый аттенюатор, ключ, два индикатора синхронизма, логическая схема совпадения, D-триггер, двухрежимный автогенератор и микроконтроллер. 6 ил.

Синтезатор частот, содержащий последовательно соединенные генератор, управляемый напряжением, первый делитель частоты с переменным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, выход которого соединен с управляющим входом генератора, управляемого напряжением, второй фильтр нижних частот, выход которого соединен с управляющим входом двухрежимного автогенератора, первый выход которого является выходом устройства, а также источник сигнала эталонной частоты, отличающийся тем, что введены первый делитель частоты с фиксированным коэффициентом деления, второй делитель частоты с фиксированным коэффициентом деления, второй частотно-фазовый детектор, первый выход которого соединен с входом второго фильтра нижних частот, последовательно соединенные логическая схема совпадения, D-триггер и микроконтроллер, выполненный с возможностью переключения режимов работы управляемых им блоков после поступления на второй его вход сигнала «Упр» на смену частоты, последующего управления одновременным установлением синхронизма на одинаковых частотах с точностью до фазы в обоих кольцах фазовой автоподстройки частоты и переключения двухрежимного автогенератора в автономный режим с захватом частоты от генератора, управляемого напряжением, достижения затем высокой спектральной чистоты выходного сигнала на новой захваченной частоте; последовательно соединенные управляемый аттенюатор и ключ, выход которого соединен с высокочастотным входом двухрежимного автогенератора, второй выход которого соединен с сигнальным входом второго делителя частоты с переменным коэффициентом деления, выход которого соединен со вторым входом второго частотно-фазового детектора; первый индикатор синхронизма, вход которого соединен со вторым выходом первого частотно-фазового детектора; второй индикатор синхронизма, вход которого соединен со вторым выходом второго частотно-фазового детектора; выход первого делителя частоты с фиксированным коэффициентом деления соединен со вторым входом первого частотно-фазового детектора; выход второго делителя частоты с фиксированным коэффициентом деления соединен со вторым входом второго частотно-фазового детектора, входы первого и второго делителей частоты с фиксированным коэффициентом деления соединены с выходом источника сигнала эталонной частоты, выход первого индикатора синхронизма соединен с первым входом логической схемы совпадения, со вторым входом которой соединен выход второго индикатора синхронизма; второй выход генератора, управляемого напряжением, соединен с входом управляемого аттенюатора, при этом первый выход микроконтроллера соединен со вторым входом D-триггера, второй выход микроконтроллера соединен с управляющим входом ключа, третий выход микроконтроллера по первой управляющей шине соединен с управляющими входами первого делителя частоты с фиксированным коэффициентом деления, первого частотно-фазового детектора, первого делителя частоты с переменным коэффициентом деления, образующими цифровую часть первого кольца фазовой автоподстройки частоты; четвертый выход микроконтроллера по второй управляющей шине соединен с управляющим входом управляемого аттенюатора, пятый выход микроконтроллера по третьей управляющей шине соединен с управляющими входами второго делителя частоты с фиксированным коэффициентом деления, второго частотно-фазового детектора, второго делителя частоты с переменным коэффициентом деления, образующими цифровую часть второго кольца фазовой автоподстройки частоты.

| СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2329595C1 |

| Цепное пильное полотно | 1944 |

|

SU63996A1 |

| Переточное устройство | 1973 |

|

SU557799A1 |

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

Авторы

Даты

2011-11-20—Публикация

2010-06-23—Подача