Изобретение относится к технике машинного зрения и может быть использовано в видеокамерах и фотоаппаратах, предназначенных для регистрации изображений.

Известны схемы считывания сигналов из ячеек матрицы фотодетекторов, содержащих истоковые повторители, подключенные стоками к шине постоянного потенциала, а истоками через транзисторы адресации к сигнальной шине, нагруженной на генератор тока, задающий рабочий режим истоковому повторителю при включенном транзисторе адресации. См., например: IEEE Journal of solid-state circuits, v.31, NO 12, december 1996, R.H.Nixon и др. "256×256 CMOS active pixel sensor camera-on-chip"; IEEE Journal of solid-state circuits, v.41, NO 12, december 2006, pp. 2998-3006, Satoshi Yoshihara и др. "A 1/1.8-inch 6.4 Mpixel 60 frames/s CMOS image sensor with seamless mode change"; US Patent 7180544 B2, Feb.20 2007, Takumi Yamaguchi и др. "Solid state image sensor". Недостатком этих схем является небольшой линейный диапазон выходного сигнала и невысокая точность коэффициентов передачи.

В US Patent 7157682 B2, Jan. 2007, Kevin E.Brehmer "Method and apparatus for a CMOS image sensor with a distributed amplifier" устранены указанные недостатки, но линейный диапазон в динамике при работе на емкостную нагрузку меньше напряжения источника питания на величину порогового напряжения транзистора плюс напряжения двух или трех последовательно включенных транзисторов, работающих в режиме генератора тока, т.е. на величину около 1,5 В. Это при субмикронных транзисторах и питании 2,5 В и менее значительно снижает динамический диапазон фотоприемного устройства.

Наиболее близким аналогом к заявленному изобретению является схема, описанная в US Patent 6717616 B1, Apr.6, 2004, Morteza Afghahi и др. "Amplifier assisted active pixel read out structure". Приведенная в этом источнике схема считывания сигналов с активной ячейки, содержащая расположенные в ячейке транзисторный ключ восстановления потенциала на интегрирующем конденсаторе, истоковый повторитель, подключенный стоком к шине постоянного потенциала, истоком через транзистор адресации к сигнальной шине, нагруженной вне ячеек на генератор тока, включенный вместе с включенным транзистором адресации, сигнальной шиной, шиной постоянного потенциала и генератором тока в схему дифференциального усилителя, в которой истоковый повторитель, подключенный шиной постоянного потенциала ко входу токового зеркала, образует входную часть усилителя с положительным входом, а входную часть с отрицательным входом образует транзистор, соединенный истоком с генератором тока, стоком с выходом токового зеркала - выходом усилителя и с затвором, образуя стопроцентную отрицательную обратную связь, имеет даже с повышенным напряжением управления включением транзистора восстановления потенциала столь же низкий диапазон линейности в динамике, что и у предыдущего аналога.

Техническим результатом настоящего изобретения является расширение диапазона линейности выходного сигнала, считываемого с фотодетектора в динамике.

Указанный результат достигается за счет того, что в известном устройстве схемы считывания сигналов с активной ячейки фотодетектора, содержащей расположенные в ячейке транзисторный ключ восстановления потенциала на интегрирующем конденсаторе, истоковый повторитель, подключенный стоком к шине постоянного потенциала, истоком через транзистор адресации к сигнальной шине, нагруженной вне ячеек на генератор тока, включенный вместе с включенным транзистором адресации, сигнальной шиной, шиной постоянного потенциала и генератором тока в схему дифференциального усилителя, в которой истоковый повторитель, подключенный шиной постоянного потенциала ко входу токового зеркала, образует входную часть усилителя с положительным входом, а входную часть с отрицательным входом образует транзистор, соединенный истоком с генератором тока, стоком с выходом токового зеркала - выходом усилителя и с затвором, образуя стопроцентную отрицательную обратную связь, предложено:

- параллельно указанному первому дифференциальному усилителю включить комплементарный ему усилитель, соединенный входом со входом, а выходом с выходом первого усилителя, идентичный ему по конфигурации, но в котором каждый соответствующий транзистор выполнен с противополжным типом проводимости, а соответствующие шины питания подключены к источнику питания инверсно,

- транзистор транзисторного ключа восстановления потенциала выполнить с таким типом проводимости, чтобы шина восстановления потенциала была соединена с его истоком,

- генераторы тока обоих усилителей выполнить управляемыми, включаемыми схемой адресации на время считывания выбранной для считывания ячейки.

Перечень графических материалов, иллюстрирующих устройство, реализующее заявляемое изобретение:

Фиг.1 иллюстрирует известное устройство схемы считывния (прототип).

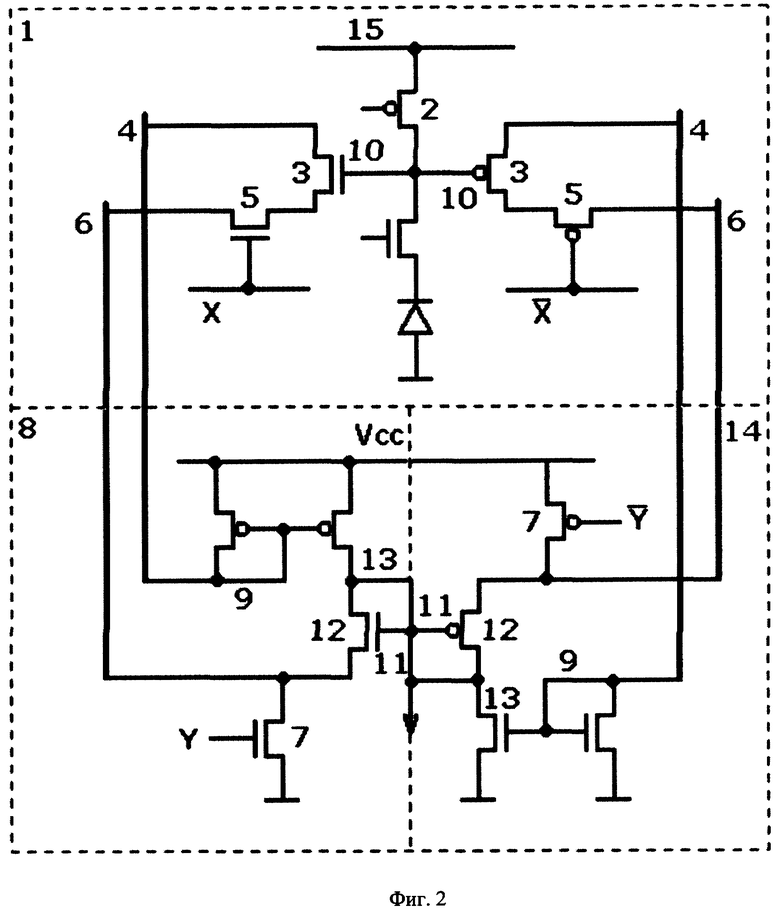

Фиг.2 показывает электрическую схему предлагаемой схемы считывания.

Схема считывания сигналов из ячеек матрицы фотодетекторов состоит из расположенного в ячейке (1) транзисторного ключа восстановления потенциала (2) на интегрирующем конденсаторе, истокового повторителя (3), подключенного стоком к шине постоянного потенциала (4), истоком через транзистор адресации (5) к сигнальной шине (6), нагруженного вне ячеек на генератор тока (7), включенный вместе с включенным транзистором адресации (5), сигнальной шиной (б), шиной постоянного потенциала (4) и генератором тока (7) в схему дифференциального усилителя (8), в которой истоковый повторитель (3), подключенный шиной постоянного потенциала (4) ко входу токового зеркала (9), образует входную часть усилителя с положительным входом (10), а входную часть с отрицательным входом (11) образует транзистор (12), соединенный истоком с генератором тока (7), стоком с выходом токового зеркала (13) - выходом усилителя и с затвором, образуя стопроцентную отрицательную обратную связь, включенного параллельно указанному первому дифференциальному усилителю (8) комплементарного ему усилителя (14), соединенного входом со входом, а выходом с выходом первого усилителя (8), идентичного ему по конфигурации, но в котором каждый соответствующий транзистор выполнен с противополжным типом проводимости, а соответствующие шины питания подключены к источнику питания инверсно, причем расположенный в ячейке транзистор транзисторного ключа восстановления потенциала (2) выполнен с таким типом проводимости, чтобы шина восстановления потенциала (15) была соединена с его истоком, а генераторы тока (7) обоих усилителей (8) и (14) выполнены управляемыми и включаются схемой адресации на время считывания выбранной для считывания ячейки.

Схема работает следующим образом.

После восстановления потенциала на емкости входа (10) через транзисторный ключ (2), который благодаря подключению шины восстановления потенциала (15) к его истоку передается на емкость входа без потерь, и периода накопления включаются транзисторы адресации (5). Истоковые повторители (3) оказываются включенными в схему дифференциальных усилителей (8) и (14), в которых включены схемой адресации генераторы тока (7). Включение на короткое время только одной пары усилителей из многих сокращает среднюю потребляемую ими мощность и, следовательно, предотвращает локальные разогревы. Выходы усилителей - стоки (13) транзисторов (12), соединенные с отрицательными входами (11) - их затворами, будут в точности повторять входной потенциал (10) в диапазоне работоспособности усилителей вследствие стопроцентной отрицательной обратной связи. В стационарном режиме линейная зависимость напряжения на выходе одиночного усилителя от входного напряжения будет простираться в пределах напряжения источника питания. Однако в динамике при работе на емкостную нагрузку напряжение на его выходе (11) будет отставать от входного (10) из-за экспоненциального уменьшения тока через транзисторы (3) и (12) при их переходе в подпороговый режим, когда входное напряжение становится меньше порогового. В сдвоенных комплементарных усилителях в динамике на протяжении диапазона, крайние точки которого отстоят от потенциалов источника питания на минимальное напряжение генератора тока (около 0,25 В), выходное напряжение формируется суммарным током транзисторов (12) усилителей (8) и (14), который слабо меняется во всем диапазоне входного напряжения. Использование данного изобретения обеспечит диапазон линейности в динамике около 1 В при источнике питания 1,5 В. В одиночном усилителе этот диапазон равен нулю.

Настоящее описание изобретения, в т.ч. состава и работы устройства, включая предлагаемый вариант его исполнения, предполагает его дальнейшее возможное совершенствование специалистами и не содержит каких-либо ограничений в части реализаций. Все притязания сформулированы исключительно в формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА СЧИТЫВАНИЯ СИГНАЛОВ ИЗ МАТРИЦЫ ЯЧЕЕК ФОТОДЕТЕКТОРОВ | 2007 |

|

RU2342802C1 |

| СХЕМА СЧИТЫВАНИЯ СИГНАЛОВ ИЗ ЯЧЕЕК МАТРИЦЫ ФОТОДЕТЕКТОРОВ | 2008 |

|

RU2356177C1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| ОБНАРУЖЕНИЕ ЗАРЯДА ИЛИ ЧАСТИЦЫ | 2003 |

|

RU2339973C2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛОВ РЕЗИСТИВНЫХ ФОТОСЕНСОРОВ | 2004 |

|

RU2263374C1 |

| Устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения (варианты) | 2018 |

|

RU2688953C1 |

| НИЗКОВОЛЬТНОЕ КМОП ТОКОВОЕ ЗЕРКАЛО | 2013 |

|

RU2544780C1 |

| ВИДЕОПРЕОБРАЗОВАТЕЛЬ ОПТИЧЕСКОГО ИЗЛУЧЕНИЯ | 2004 |

|

RU2262207C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2536671C1 |

| МАТРИЧНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2016 |

|

RU2727767C1 |

Схема считывания сигналов из ячеек матрицы фотодетекторов, содержащая расположенные в ячейке транзисторный ключ восстановления потенциала на интегрирующем конденсаторе, истоковый повторитель, подключенный стоком к шине постоянного потенциала, истоком через транзистор адресации к сигнальной шине, нагруженной вне ячеек на генератор тока, включенный вместе с включенным транзистором адресации, сигнальной шиной, шиной постоянного потенциала и генератором тока в схему дифференциального усилителя, в которой истоковый повторитель, подключенный шиной постоянного потенциала ко входу токового зеркала, образует входную часть усилителя с положительным входом, а входную часть с отрицательным входом образует транзистор, соединенный истоком с генератором тока, стоком с выходом токового зеркала - выходом усилителя и с затвором, образуя стопроцентную отрицательную обратную связь. 2 ил.

Схема считывания сигналов из ячеек матрицы фотодетекторов, содержащая расположенные в ячейке транзисторный ключ восстановления потенциала на интегрирующем конденсаторе, истоковый повторитель, подключенный стоком к шине постоянного потенциала, истоком через транзистор адресации к сигнальной шине, нагруженной вне ячеек на генератор тока, включенный вместе с включенным транзистором адресации, сигнальной шиной, шиной постоянного потенциала и генератором тока в схему дифференциального усилителя, в которой истоковый повторитель, подключенный шиной постоянного потенциала ко входу токового зеркала, образует входную часть усилителя с положительным входом, а входную часть с отрицательным входом образует транзистор, соединенный истоком с генератором тока, стоком с выходом токового зеркала - выходом усилителя и с затвором, образуя стопроцентную отрицательную обратную связь, отличающаяся тем, что параллельно указанному первому дифференциальному усилителю включен комплементарный ему усилитель, соединенный входом со входом, а выходом с выходом первого усилителя, идентичный ему по конфигурации, но в котором каждый соответствующий транзистор выполнен с противоположным типом проводимости, а соответствующие шины питания подключены к источнику питания инверсно, причем расположенный в ячейке транзистор транзисторного ключа восстановления потенциала выполнен с таким типом проводимости, чтобы шина восстановления потенциала была соединена с его истоком, а генераторы тока обоих усилителей выполнены управляемыми и включаются схемой адресации на время считывания выбранной для считывания ячейки.

| US 6717616 А, 06.04.2004 | |||

| US 2002011554 A, 31.01.2002 | |||

| JP 2003101006 A, 04.04.2003 | |||

| JP 62159459 A, 15.07.1987 | |||

| Устройство для вывода заряда с фотоприемной матрицы | 1981 |

|

SU1104688A1 |

Авторы

Даты

2009-01-10—Публикация

2007-06-18—Подача