Уровень техники

Это изобретение относится к усилителям мощности, например, к усилителям мощности, которые включают в себя по меньшей мере двухмерную матрицу транзисторов и могут быть настроены для согласования импеданса антенны или другой нагрузки.

Транзисторы представляют собой устройства, которые могут усиливать управляющий сигнал, подаваемый на управляющий электрод. Транзисторы могут быть сделаны из множества различных материалов, могут иметь множество различных геометрических конфигураций и могут работать в соответствии с множеством различных физических механизмов. Иллюстративные материалы включают в себя кремний, арсенид галлия, нитрид галлия и карбид кремния. Эти и другие материалы могут использоваться, чтобы сформировать такие устройства, как биполярные транзисторы и полевые транзисторы, которые содержат либо изолированные управляющие электроды (например, биполярные транзисторы с изолированным затвором (БТИЗ; IGBT), полевые транзисторы со структурой металл-оксид-полупроводник (МОП-транзисторы; MOSFET), транзисторы с высокой подвижностью электронов (ВПЭ-транзисторы; HEMT) или гетероструктурные полевые транзисторы (HFET)), либо управляющие электроды, сделанные из p-n переходов (например, биполярные плоскостные транзисторы (BJT) или полевые транзисторы с управляющим p-n переходом (JFET)).

Независимо от материалов и структур устройств все отдельные транзисторы имеют фундаментальные ограничения относительно их безопасных рабочих диапазонов. Например, если на основные электроды подано чрезмерно большое напряжение, то может возникнуть пробой диэлектрика, и транзистор может быть поврежден или разрушен. В качестве другого примера, если между основными электродами текут чрезмерно большие токи, то транзистор также может быть поврежден или разрушен.

Хотя рабочие диапазоны отдельных транзисторов могут быть подходящими для некоторых применений, они могут быть недостаточными, чтобы отвечать требованиям других. Например, некоторые применения могут потребовать напряжений, превосходящих напряжения пробоя, или токов, превосходящих пиковый ток даже надлежащим образом спроектированных транзисторов. Примеры таких применений включают в себя управление антеннами для передачи, например, радиолокационных сигналов и сигналов связи (например, для спутниковой связи и наземных широковещательных передач как для военной, так и для гражданской специфики).

В таких применениях отдельные транзисторы могут быть сгруппированы, чтобы манипулировать большими напряжениями и/или токами как группа. Например, отдельные транзисторы могут быть сложены в стеки (или "сложены в последовательные стеки") таким образом, что почти весь ток, который течет через основные электроды первого транзистора в стеке, также течет через основные электроды следующего транзистора (транзисторов) в стеке. Каждый из транзисторов в стеке поддерживает некоторую часть напряжения, которое управляет этим током. Общее напряжение, поддерживаемое стеком транзисторов, может превышать напряжение пробоя отдельных транзисторов.

В качестве другого примера отдельные транзисторы могут быть соединены параллельно таким образом, что по существу одинаковое напряжение подключено к основным электродам нескольких транзисторов. Когда несколько транзисторов находятся в проводящем состоянии, весь электрический ток через группу может превысить максимальный ток отдельных составляющих транзисторов.

В идеализированных моделях с малым сигналом передача мощности от источника сигнала к нагрузке может быть улучшена посредством согласования выходного импеданса источника (также известного как "импеданс источника") с импедансом нагрузки. В таких моделях максимальная возможная мощность передается, когда импеданс нагрузки точно равен комплексному сопряжению импеданса источника по бесконечному диапазону частот.

Однако в реальных приложениях с большими сигналами "импеданс источника" должным образом не определен или, строго говоря, не существует вследствие отсутствия линейности или недостающего закона суперпозиции. Тем не менее, теория и практика показывают, что для некоторых значений импеданса нагрузки передается достаточно большая часть мощности (т.е., коэффициент полезного действия (КПД) суммирования мощности достаточно высок). Термин "оптимальный импеданс нагрузки" использован в настоящем документе, чтобы охарактеризовать обстоятельства, в которых достаточно большая часть мощности передается в рассматриваемом диапазоне рабочих частот.

Сущность изобретения

Описаны усилители мощности, которые включают в себя по меньшей мере двухмерную матрицу активных ячеек. Активные ячейки в общем случае представляют собой отдельные транзисторы. Двухмерная матрица транзисторов сформирована стеками из нескольких активных ячеек, которые соединены параллельно, тем самым формируя "двухмерную матрицу". Каждый стек в матрице может поддерживать относительно большое напряжение, проводя заданный ток. Таким образом, каждый стек можно считать источником, который имеет свой собственный относительно большой оптимальный импеданс нагрузки. Однако, поскольку стеки соединены параллельно, двухмерная матрица имеет общий импеданс, который является долей импеданса составляющих стеков. Таким образом, импеданс матрицы в целом может быть адаптирован таким образом, что он согласован с импедансом нагрузки, и передает относительно большую часть мощности по рассматриваемому диапазону рабочих частот.

Более подробно импеданс входного порта (Zin_port) и выходного порта (Zout_port) - и импеданс соответствующих шин распределения и сбора мощности - матричного усилителя мощности в значительной мере независимы от количества активных ячеек в усилителе. Вместо этого Zin_port и Zout_port зависят только от соотношения количества строк N и количества столбцов M, а также входного и выходного импеданса отдельных активных ячеек (т.е., Zcell_in and Zcell_out, соответственно). В частности,

Уравнение 1

Уравнение 1

и

Уравнение 2

Уравнение 2

В общем случае целом Zcell_in и Zcell_out можно адаптировать по относительно ограниченному диапазону (например, посредством адаптации геометрии устройства активной ячейки и других свойств). Однако отношение количества строк к количеству столбцов (N/M) в матричном усилителе мощности регулировать намного легче. Таким образом, посредством управления всеми этими параметрами могут быть достигнуты матричные усилители мощности с произвольными импедансами портов ввода и вывода.

Ширина полосы матричного усилителя мощности ограничена только шириной полосы отдельных ячеек и согласованием комплекснозначных импедансов портов ввода/вывода Zin_port и Zout_port с (действительнозначным) системным импедансом Z0. Поскольку отношение N/M не ограничено никаким конкретным количеством активных ячеек (например, матрица размером 10×10 из 100 активных ячеек имеет такое же отношение N/M как матрица размером 4×4 из 16 активных ячеек), достижимая выходная мощность не ограничена количеством активных ячеек. Вместо этого достижимая выходная мощность ограничена реальными соображениями, описанными выше (в том числе, например, разностными ошибками магнитуды и фазы, финитными потерями цепей согласования мощности в матричном усилителе мощности). В отсутствие такой не идеальности теоретическая выходная мощность увеличивалась бы пропорционально размеру матрицы N x M.

Матричные усилители мощности, описанные в настоящем документе, могут использовать активные или пассивные входные управляющие структуры, которые индивидуально и синхронно управляют активными ячейками двухмерного матричного усилителя мощности. В идеальной двухмерной матрице каждая из активных ячеек принимала бы отдельный, но идентичный сигнал управления на своем соответствующем управляющем электроде. Кроме того, никакой ток не был бы потерян при подаче сигнала управления на управляющие электроды. Хотя такого идеального поведения невозможно достигнуть вследствие множества физических факторов (например, небольших несоответствий физических характеристик компонентов, паразитных емкостей и индуктивностей и т.д.), управление активными ячейками в усилителях мощности, описанных в настоящем документе, является достаточно синхронным, чтобы обеспечить общую выходную мощность, которая приблизительно в N x M раз больше эффективной выходной мощности отдельной ячейки в матрице, где N - количество строк в матрице, и M - количество столбцов.

В некоторых реализациях усилители мощности, описанные в настоящем документе, могут включать в себя "активный истоковый повторительʺ. В частности, активный истоковый повторитель может быть реализован парой матричных усилителей, которыми управляют сигналы управления противоположной полярности. Два матричных усилителя собраны по комплементарной или квазикомплементарной топологии, чтобы соответственно "вытягивать" и "сбрасывать" выход. В некоторых реализациях активные истоковые повторители могут быть реализованы как (монолитное) устройство сверхвысокочастотной (СВЧ) интегральной схемы (MIC). В таких случаях активный истоковый повторитель может выдавать сигналы высокого напряжения и тока, сохраняя другие преимущества устройств интегральных схем.

В некоторых реализациях управляющие электроды активных ячеек матричных усилителей мощности соединены вместе в строках, в столбцах, или и в строках, и в столбцах, с использованием линий передачи, которые подходят для передачи сигналов управления в микроволновом и миллиметровом диапазонах частот, и (почти) синхронного управления активными ячейками. В общем случае характеристический импеданс линий передачи может быть выбран равным 50 Ом. Однако при некоторых обстоятельствах (например, большие транзисторные ячейки), может быть выгодно выбрать более низкое значение импеданса (например, 20 Ом или даже 10 Ом) для согласования входа и выхода активных ячеек в матричном усилителе, особенно если требуется высокая абсолютная или относительная ширина полосы. В качестве другого примера длины линий передачи не являются нулевыми (т.е., управляющие электроды активных ячеек не соединены непосредственно), и длины могут быть выбраны таким образом, что распределение сигналов управления на разные управляющие электроды является почти идентичным и может быть достигнуто почти синхронное управление активными ячейками. При наличии длин линий передачи, отличных от нуля, соседние активные ячейки могут быть физически отделены друг от друга, и тепловое сцепление между активными ячейками существенно сокращается, позволяя усиливать даже относительно большие мощности.

Все матричные усилители мощности, описанные в настоящем документе, усиливают вывод радиочастотного сигнала по радиочастотному источнику. Радиочастотный сигнал может быть подан в матричные усилители мощности множеством различных методов. Например, в некоторых реализациях радиочастотный сигнал может быть подан:

- непосредственно в активные ячейки в нижней строке матричного усилителя мощности (т.е., без вмешательства активного компонента управления (но факультативно с пассивной цепью согласования импедансов) между радиочастотным источником и активными ячейками, и

- в другие активные ячейки матричного усилителя мощности посредством вмешательства активного компонента управления в основании компонента управления столбца.

Примеры таких матричных усилителей мощности показаны, например, на фиг. 9, 10, 11. В этих реализациях, если предположить, что выходная мощность от всех активных ячеек в нижней строке (т.е., Pout,BC) является идентичной (как имело бы место, если бы эти активные ячейки и распределение мощности на эти ячейки являлись идентичными), то выходная мощность матричного усилителя мощности (т.е., Pout) приблизительно равна произведению выходной мощности отдельных ячеек в нижней строке и общего количества активных ячеек, или

Pout=N*M*Pout,BC Уравнение 3.

Кроме того, усиление каждой активной ячейки (т.е., GBC) задано выходной мощностью этой активной ячейки (т.е., Pout,BC) для данной входной мощности в эту активную ячейку. В предположении, что мощность равномерно разделена между активными ячейками в нижней строке и активном компоненте управления в основании компонента управления столбца, тогда входная мощность в каждую активную ячейку в нижней строке задана полной входной мощностью (т.е., Pin), разделенной на сумму количества столбцов (т.е., M)+1, чтобы учесть активный драйвер в основании компонента управления столбца, или

Pin=(M+1)* Pout,BC/GBC Уравнение 4.

Таким образом, полное усиление мощности матричного усилителя (т.е., G2D) задано как:

Pin=(M+1)* Pout,BC/GBC Уравнение 5.

В качестве другого примера, в некоторых реализациях радиочастотный сигнал может быть подан:

- непосредственно в активные ячейки в нижней строке матричного усилителя мощности (т.е., без вмешательства активного компонента управления (но факультативно с пассивной цепью согласования импедансов) между радиочастотным источником и активными ячейками), и

- непосредственно в другие активные ячейки матричного усилителя мощности (т.е., без вмешательства активного компонента управления (но факультативно с пассивной цепью согласования импедансов) между радиочастотным источником и активными ячейками).

Примеры таких матричных усилителей мощности показаны, например, на фиг. 4-8. В этих реализациях выходная мощность матричного усилителя мощности и полное усиление мощности матричного усилителя являются такими же, как заданы в уравнениях 3, 4, 5.

Однако в этих реализациях эффективное усиление мощности матричного усилителя и максимальная выходная мощность отдельных активных ячеек мощности в матрице уменьшаются с увеличением частоты, поскольку входная мощность, необходимая для каждой ячейки, не может быть передана на выход.

В качестве другого примера, в некоторых реализациях радиочастотный сигнал может быть подан:

- во все активные ячейки - в том числе в нижней строке - матричного усилителя мощности посредством вмешательства активного компонента управления.

Пример такого матричного усилителя мощности показан, например, на фиг. 3. В таких матричных усилителях мощности входная мощность в каждую активную ячейку в матричном усилителе мощности задана полной входной мощностью (т.е., Pin), разделенной на общее количество активных ячеек. Другими словами, входная мощность в каждую активную ячейку является полной входной мощностью (т.е., Pin), разделенной на размер матрицы N x M. Таким образом, предполагая идентичные активные ячейки,

Pin=(N*M)* Pout,BC/GBC Уравнение 6.

Таким образом, полное усиление мощности матричного усилителя (т.е., G2D) задано как:

G2D=Pout/Pin=GBC Уравнение 7.

Такие матричные усилители мощности не имеют никакого увеличения усиления в результате размеров матрицы.

В качестве еще одного примера, в некоторых реализациях радиочастотный сигнал может быть подан:

- в единственный компонент управления нижней ячейки компонента управления столбца матричного усилителя мощности.

Активными ячейками в нижней строке и верхних строках матричного усилителя мощности могут управлять цепь или стек активных симметрирующих трансформаторов или дифференциальных усилителей. Каждое активное устройство может управлять всеми активными ячейками в соответствующей строке.

Примеры такого матричного усилителя мощности показаны, например, на фиг. 12. В таких матричных усилителях мощности вся входная мощность в матричный усилитель мощности обеспечивается нижней активной ячейке. Таким образом,

Pin=Pout,BC/GSBC Уравнение 8

и полное усиление мощности матричного усилителя (т.е., G2D) задано как:

G2D=Pout/Pin=N*M * GSBC Уравнение 9.

Это теоретический идеальный случай идеального двухмерного матричного усилителя мощности со столбцом активного компонента управления, в котором радиочастотный входной источник управляет только нижней ячейкой этого компонента управления.

В свете этого могут быть описаны различные аспекты матричного усилителя мощности. В первом аспекте усилитель мощности включает в себя вход усилителя и выход усилителя, множество M x N активных ячеек, где N и M оба ≥ 2, и активные ячейки соединены как матрица размером M x N, и по меньшей мере одну управляющую структуру для управления активными ячейками. Применяется одно из a), b) или c), причем когда применяется a), каждый из столбцов матрицы включает в себя N активных ячеек, соединенных последовательно и управляемых как стек, причем стеки соединены параллельно, когда применяется b), каждая из строк матрицы включает в себя M активных ячеек, соединенных таким образом, чтобы быть управляемыми параллельно, причем по меньшей мере две строки матрицы соединены последовательно, и когда применяется c), каждый из столбцов матрицы включает в себя N активных ячеек, соединенных последовательно и управляемых как стек. Стеки соединены параллельно, и каждая из строк матрицы включает в себя M активных ячеек, соединенных таким образом, чтобы быть управляемыми параллельно. По меньшей мере две строки матрицы соединены последовательно. Управляющий электрод каждой активной ячейки присоединен ко входу усилителя через путь прохождения сигнала, который включает в себя управляющую входную структуру, причем все активные ячейки выполнены с возможностью управления электрическим сигналом, подаваемым на вход усилителя.

Первый и любой другой аспект могут включать в себя один или более из следующих признаков. Управляющая структура включает в себя множество активных управляющих элементов, и путь прохождения сигнала, который присоединяет управляющий электрод каждой активной ячейки к входу усилителя, включает в себя управляющие элементы. Путь прохождения сигнала, который присоединяет управляющий электрод по меньшей мере некоторых из активных ячеек к входу усилителя, включает в себя другие из активных ячеек. Управляющий электрод каждой активной ячейки присоединен к входу усилителя, чтобы принимать по существу равную входную мощность. Выходы активных ячеек присоединены таким образом, что выходные напряжения активных ячеек вдоль столбца складываются, и выходные токи столбцов складываются на выходе усилителя. Выходы активных ячеек присоединены таким образом, что выходные токи активных ячеек вдоль строки складываются, и выходные напряжения строк складываются в выходе усилителя. Входные сигналы в управляющие электроды транзисторов в активных ячейках в самой нижней строке активных ячеек являются несбалансированными. Входные сигналы в управляющие электроды транзисторов в активных ячейках в верхних строках активных ячеек являются сбалансированными. Усилитель мощности включает в себя активный симметрирующий трансформатор, присоединенный для преобразования несбалансированных сигналов в сбалансированные входные сигналы для активных ячеек в верхних строках. Сбалансированные входные сигналы активных ячеек в верхних строках имеют такие ток и напряжение, что выходные токи и напряжения активных ячеек в верхних строках совпадают с выходными токами и напряжениями активных ячеек в самой нижней строке. Разность между выходным током первой из активных ячеек и выходным током второй, непосредственно следующей активной ячейки в том же самом столбце составляет менее 10% выходного тока первой из активных ячеек. Разность между выходным током самой нижней из активных ячеек в столбце и выходным током самой верхней активной ячейки в столбце составляет менее 10% выходного тока самой нижней из активных ячеек. Выходная мощность каждой из активных ячеек по существу равная. Выходная мощность усилителя мощности по существу равна N x M выходных мощностей каждой из активных ячеек. По меньшей мере одна управляющая структура включает в себя схему соединения с компенсационной связью для распределения сигнала управления с основного электрода одной активной ячейки на управляющий электрод другой активной ячейки, причем схема соединения с компенсационной связью включает в себя делитель напряжения или делитель тока, чтобы подавать часть выходного напряжения или тока первой активной ячейки на управляющий электрод второй активной ячейки. Схема соединения с компенсационной связью распределяет сигнал управления с основного электрода первой активной ячейки в столбце на управляющий электрод второй активной ячейки в том же столбце. По меньшей мере одна управляющая структура включает в себя активный дифференциальный управляющий усилитель. По меньшей мере одна управляющая структура включает в себя один или более пассивных симметрирующих трансформаторов. Усилитель мощности c включает в себя a) цепь согласования входного импеданса, b) цепь согласования выходного импеданса или c) и цепь согласования входного импеданса, и цепь согласования выходного импеданса. По меньшей мере некоторые активные ячейки включают в себя a) цепь согласования входного импеданса, b) цепь согласования выходного импеданса или c) и цепь согласования входного импеданса, и цепь согласования выходного импеданса. Например, все активные ячейки могут включать в себя цепь согласования входного импеданса и/или все активные ячейки могут включать в себя цепь согласования выходного импеданса. Усилитель мощности включает в себя один или более элементов распределения для распределения сигнала со входа усилителя на управляющие электроды M самых нижних транзисторов с практически одинаковой задержкой. Усилитель мощности включает в себя один или более элементов распределения для распределения сигналов управления на управляющие электроды активных ячеек в каждой строке, в каждом столбце, или и в каждой строке, и в каждом столбце с практически одинаковыми задержками. Усилитель мощности включает в себя один или более элементов сбора для сбора выходных сигналов активных ячеек в каждой строке, в каждом столбце, или и в каждой строке, и в каждом столбце, выходные сигналы находятся в фазе. Усилитель мощности включает в себя элементы распределения для распределения сигналов управления на управляющие электроды активных ячеек в каждой строке, в каждом столбце, или и в каждой строке, и в каждом столбце с разными задержками, и один или более элементов сбора для сбора выходных сигналов активных ячеек в каждой строке, в каждом столбце, или и в каждой строке, и в каждом столбце, выходные сигналы находятся не в фазе, причем элементы сбора включают в себя задержки для компенсации задержек элементов распределения таким образом, чтобы мощность, обеспеченная на выход усилителя от активных ячеек, находилась в фазе. Усилитель мощности реализован в интегральной схеме, например, в монолитной сверхвысокочастотной интегральной схеме, в гибридной сверхвысокочастотной интегральной схеме или в многокристальном модуле. Каждая активная ячейка включает в себя, например, управляемый зарядом полупроводниковый четырехполюсный транзистор, причем каждая активная ячейка включает в себя полевой транзистор или биполярный транзистор. Каждая активная ячейка включает в себя транзистор на основе полупроводника типа III-V, например, транзистор на основе AlGaN/GaN или транзистор на основе GaAs. Каждая активная ячейка включает в себя транзистор на основе кремния, например, гетероструктурный транзистор SiGe. Множество активных ячеек является частью двухтактного каскада. Двухтактный каскад представляет собой двухтактный каскад на комплементарных или квазикомплементарных транзисторах, который включает в себя второе множество активных ячеек. Усилитель мощности включает в себя соединение между выходом усилителя и основным электродом первого транзистора в активной ячейке в одной из множества активных ячеек и соединение между выходом усилителя и управляющим электродом первого транзистора. Эти соединения вместе предназначены для того, чтобы поместить первый транзистор в проводящее состояние в противофазе с сигналом на входе усилителя и тем самым обеспечить работу второго множества активных ячеек в противофазе относительно первого множества активных ячеек. Соединение между выходом усилителя и управляющим электродом первого транзистора включает в себя проводящий путь между основным электродом транзистора в управляющем элементе и выходом усилителя и проводящий путь между управляющим электродом транзистора в управляющем элементе и управляющим электродом первого транзистора. Соединение между выходом усилителя и управляющим электродом первого транзистора состоит из пассивных компонентов. Каждая активная ячейка включает в себя множество транзисторов, которые соединены параллельно. Каждая активная ячейка включает в себя матрицу транзисторов. Усилитель мощности включает в себя первые соединения между транзисторами, формирующие матрицу транзисторов каждой активной ячейки, и вторые соединения между самими активными ячейками. Первые соединения объединены в полупроводниковом устройстве на уровне, отличающемся от вторых соединений. Усилитель мощности включает в себя сепаратор питания, который имеет высокочастотный порт, присоединенный к нагрузке на выходе усилителя, комбинированный порт присоединен к стекам двухмерной матрицы, и низкочастотный порт, присоединенный к источнику DC.

Во втором аспекте устройство включает в себя антенный блок, имеющий входной импеданс, и усилитель мощности первого аспекта с любыми из признаков первого или третьего аспекта или без них, причем N и M сконфигурированы таким образом, что оптимальный импеданс нагрузки усилителя мощности по существу совпадает со входным импедансом антенного блока.

Второй и любой другой аспект могут включать в себя один или более из следующих признаков. Коэффициент отражения -12 дБ или меньше может быть достигнут по ширине полосы, ограниченной антенным блоком.

В третьем аспекте усилитель мощности включает в себя двухмерную матрицу размером N x M активных ячеек, сформированную посредством последовательной укладки в стек основных электродов нескольких активных ячеек, причем стеки соединены параллельно, чтобы сформировать двухмерную матрицу. Усилитель мощности включает в себя управляющую структуру для координации управления активными ячейками таким образом, что эффективная выходная мощность двухмерной матрицы составляет приблизительно N x M выходных мощностей каждой из активных ячеек.

Третий и любой другой аспект могут включать в себя один или более следующих признаков. Усилитель мощности включает в себя сепаратор питания, который имеет высокочастотный порт, присоединенный к нагрузке, управляемый двухмерной матрицей, комбинированный порт, присоединенный к стекам двухмерной матрицы, и низкочастотный порт, присоединенный к источнику DC. Усилитель мощности включает в себя вторую двухмерную матрицу активных ячеек, сформированную посредством последовательной укладки в стек основных электродов нескольких активных ячеек, причем стеки соединены параллельно, чтобы сформировать вторую двухмерную матрицу. Двухмерная матрица и вторая двухмерная матрица соединены, чтобы сформировать каскад на комплементарных или квазикомплементарных транзисторах. Усилитель мощности включает в себя вторую управляющую структуру для координации управления активными ячейками второй двухмерной матрицы в противофазе с управлением активными ячейками в двухмерной матрице. Усилитель мощности включает в себя контур управления, включающий в себя усилитель ошибки для выдачи сигнала ошибки, представляющего разность между желаемым выходным напряжением DC и фактическим выходным напряжением. Вторая управляющая структура присоединена для регулировки фактического выходного напряжения DC в ответ на сигнал ошибки. Двухмерная матрица и вторая двухмерная матрица соединены, чтобы сформировать каскад на комплементарных или квазикомплементарных транзисторах. Усилитель мощности включает в себя вторую управляющую структуру для координации управления активными ячейками второй двухмерной матрицы в фазе с управлением активными ячейками в двухмерной матрице. Управляющая структура включает в себя схему соединения с компенсационной связью для распределения сигнала управления с основного электрода одной активной ячейки на управляющий электрод другой активной ячейки в том же стеке. Управляющая структура включает в себя множество пассивных компонентов управления матрицы симметрирующего трансформатора для преобразования несбалансированных сигналов в сбалансированные. Управляющая структура включает в себя компонент управления строками для распределения сигнала управления на управляющие электроды множества активных ячеек во множестве стеков. Компонент управления строками содержит множество линий распределения для присоединения частей сигнала управления к управляющим электродам множества активных ячеек с подходящими задержками для координации проводимости тока посредством активных ячеек. Каждая из активных ячеек включает в себя множество транзисторов, соединенных параллельно. Каждая из активных ячеек включает в себя двухмерную матрицу транзисторов. Усилитель мощности включает в себя первые соединения между транзисторами, формирующие двухмерную матрицу каждой активной ячейки, и вторые соединения между самими активными ячейками. Первые соединения объединены в полупроводниковом устройстве на уровне, отличающемся от вторых соединений. N не обязательно должно быть равно M. По меньшей мере некоторые активные ячейки включают в себя цепь согласования входного импеданса. По меньшей мере некоторые активные ячейки включают в себя цепь согласования выходного импеданса.

В четвертом аспекте устройство включает в себя антенный блок, имеющий входной импеданс, и усилитель мощности третьего аспекта с любыми из признаков третьего или первого аспекта или без них, причем N и M сконфигурированы таким образом, что оптимальный импеданс нагрузки усилителя мощности по существу совпадает со входным импедансом антенного блока.

Четвертый и любой другой аспект могут включать в себя один или более из следующих признаков. Коэффициент отражения -12 дБ или меньше достигается по ширине полосы, ограниченной антенным блоком.

Подробности одной или более реализаций изложены ниже в прилагаемых чертежах и описании. Другие признаки и преимущества будут очевидны из описания и чертежей, и из формулы изобретения.

Описание чертежей

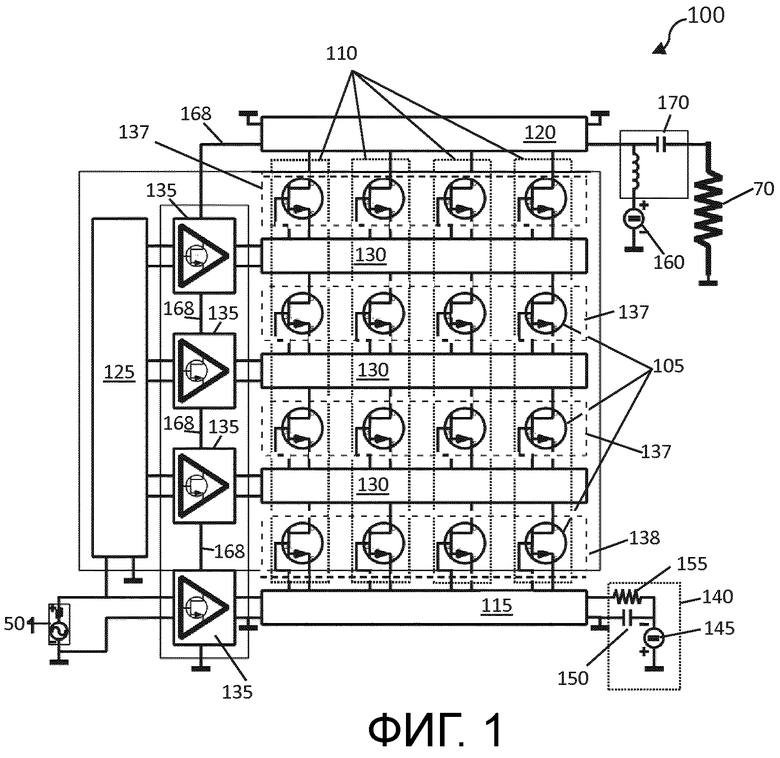

Фиг. 1 - схематическое представление матричного усилителя мощности.

Фиг. 2 - схематическое представление матричного усилителя мощности.

Фиг. 3 - схематическое представление согласованного по столбцам матричного усилителя мощности.

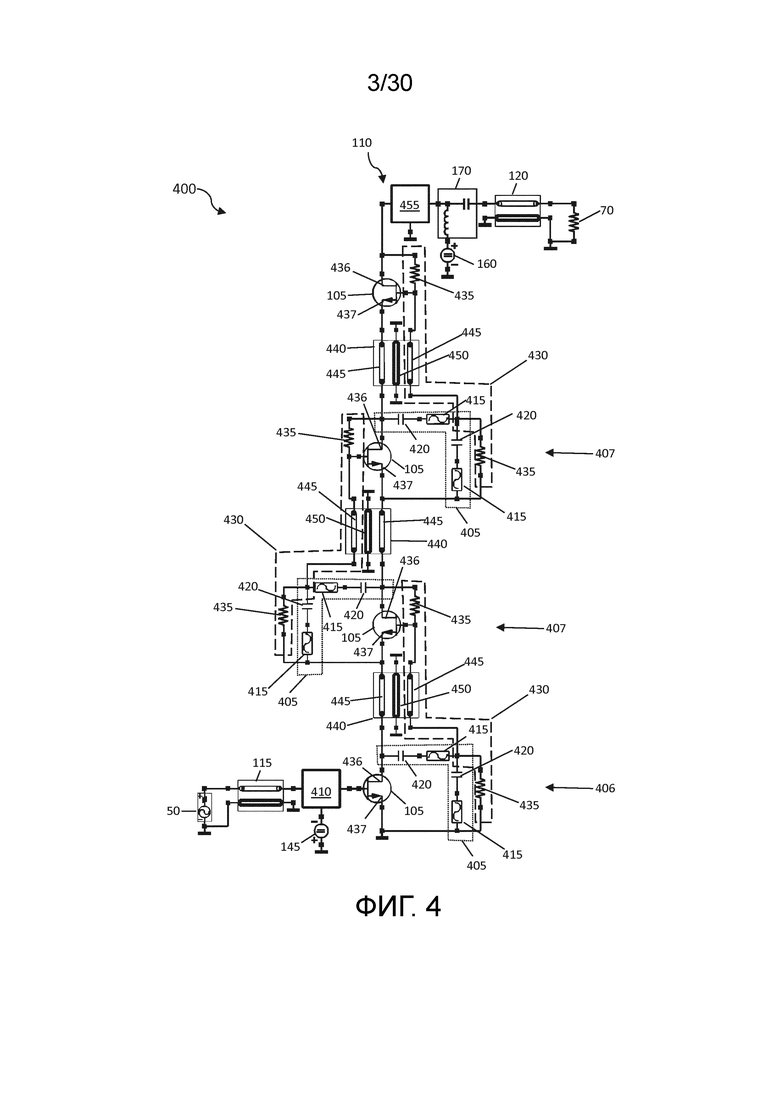

Фиг. 4 - схематическое представление согласованного по столбцам матричного усилителя мощности.

Фиг. 5 - схематическое представление согласованного по столбцам матричного усилителя мощности.

Фиг. 6 - схематическое представление согласованного по столбцам матричного усилителя мощности.

Фиг. 7 показывает схематическое представление трех реализаций симметрирующего трансформатора.

Фиг. 8 - схематическое представление согласованного по столбцам матричного усилителя мощности.

Фиг. 9 - схематическое представление сбалансированного активного компонента управления матрицы для согласованного по строкам матричного усилителя мощности.

Фиг. 10 - схематическое представление дифференциального усилителя с согласованием импедансов.

Фиг. 11 - схематическое представление сбалансированного активного компонента управления матрицы для согласованного по строкам матричного усилителя мощности.

Фиг. 12 - схематическое представление сбалансированного активного компонента управления матрицы для согласованного по строкам матричного усилителя мощности.

Фиг. 13 - схематическое представление согласованного по строкам матричного усилителя мощности.

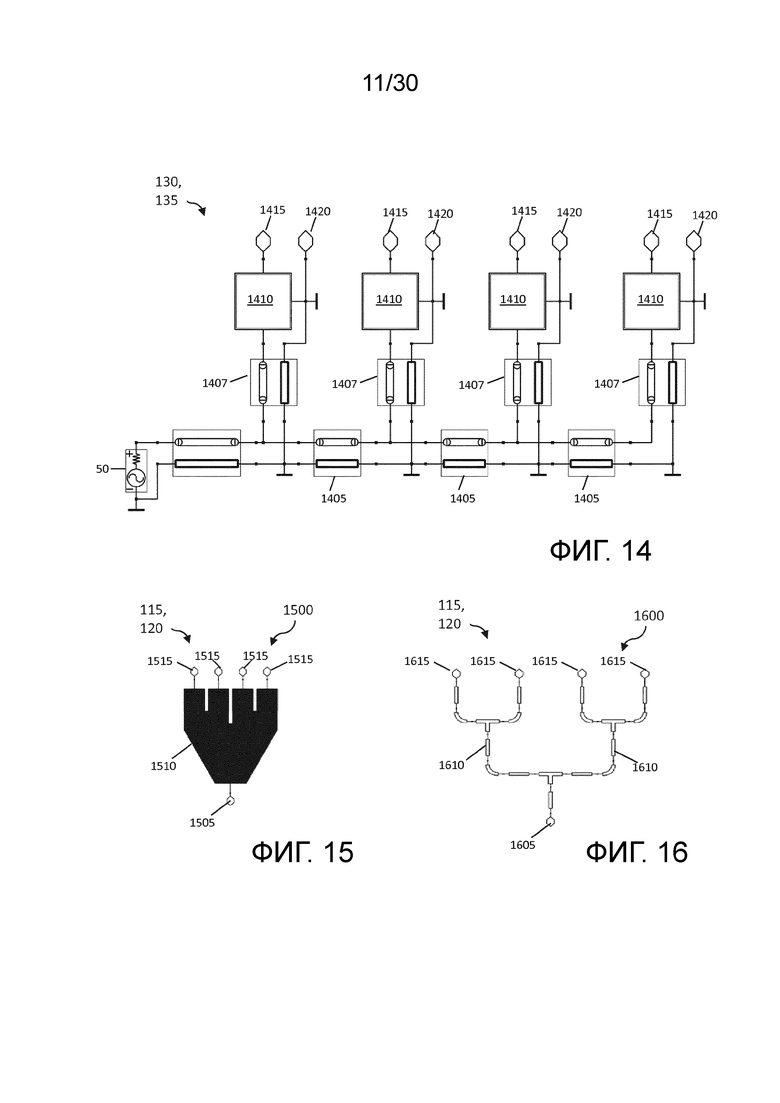

Фиг. 14 - схематическое представление линии распределения и элемента согласования импедансов, которые могут быть присоединены для распределения сигнала от источника сигнала к строке транзисторов.

Фиг. 15 и 16 - схематические представления пассивных модулей разделения/объединения, которые могут использоваться для реализации всей или части шины распределения и общей шины сбора.

Фиг. 17 - схематическое представление линии распределения и элемента согласования импедансов, которые могут быть присоединены для распределения сигнала от источника сигнала к строке транзисторов.

Фиг. 18 - схематическое представление линии распределения и элемента согласования импедансов, которые могут быть присоединены для распределения сигнала от источника сигнала к строке транзисторов.

Фиг. 19 - схематическое представление линии распределения и элемента согласования импедансов, которые могут быть присоединены для распределения сигнала от источника сигнала к строке транзисторов.

Фиг. 20 - схематическое представление линии распределения и элемента согласования импедансов, которые могут быть присоединены для распределения сигналов от пары источников сигналов к строке транзисторов.

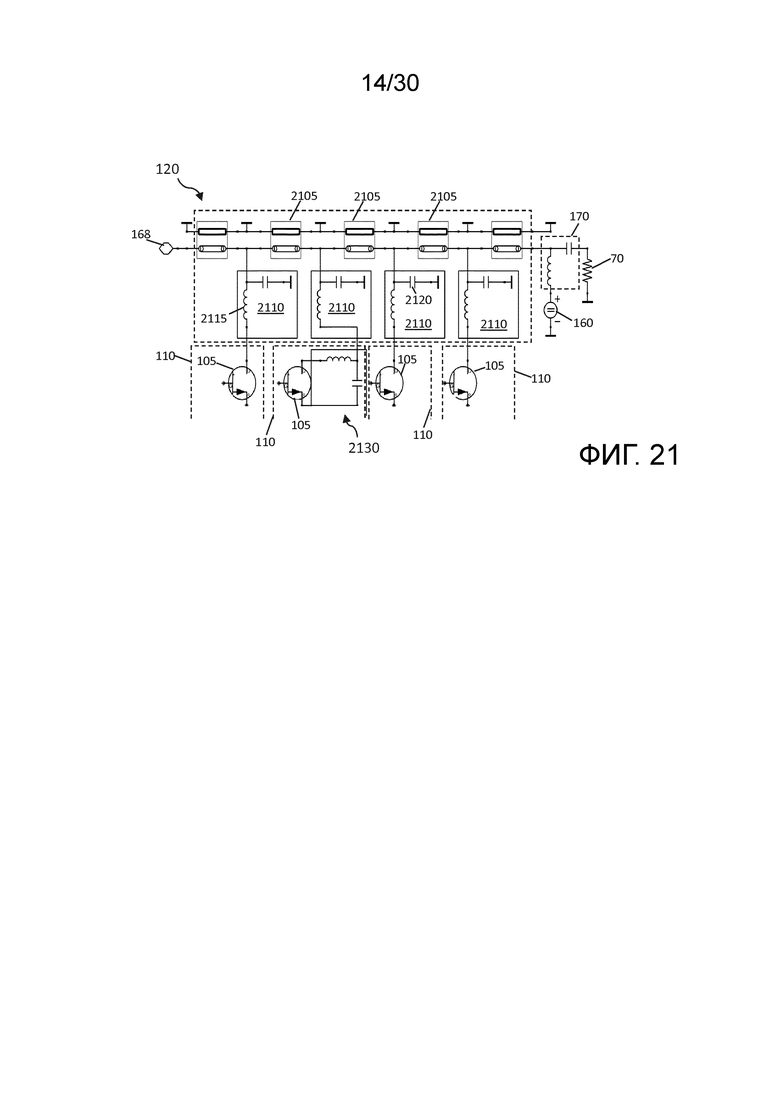

Фиг. 21 - схематическое представление несбалансированной шины сбора, которая присоединена для сбора сигналов, проходящих через M столбцов матричного усилителя мощности, и направления их на нагрузку.

Фиг. 22 и 23 - схематические представления пары строк в матричном усилителе мощности.

Фиг. 24 - схематическое представление матричного усилителя мощности.

Фиг. 25 - схематическое представление матричного усилителя мощности.

Фиг. 26 - схематическое представление матричного усилителя мощности.

Фиг. 27 - схематическое представление матричного усилителя мощности.

Фиг. 28 - схематическое представление матричного усилителя мощности.

Фиг. 29 - схематическое представление матричного усилителя мощности.

Фиг. 30a - схематическое представление матричного усилителя мощности.

Фиг. 30b - схематическое представление дифференциального усилителя согласования импедансов.

Фиг. 31 - схематическое представление матричного усилителя мощности.

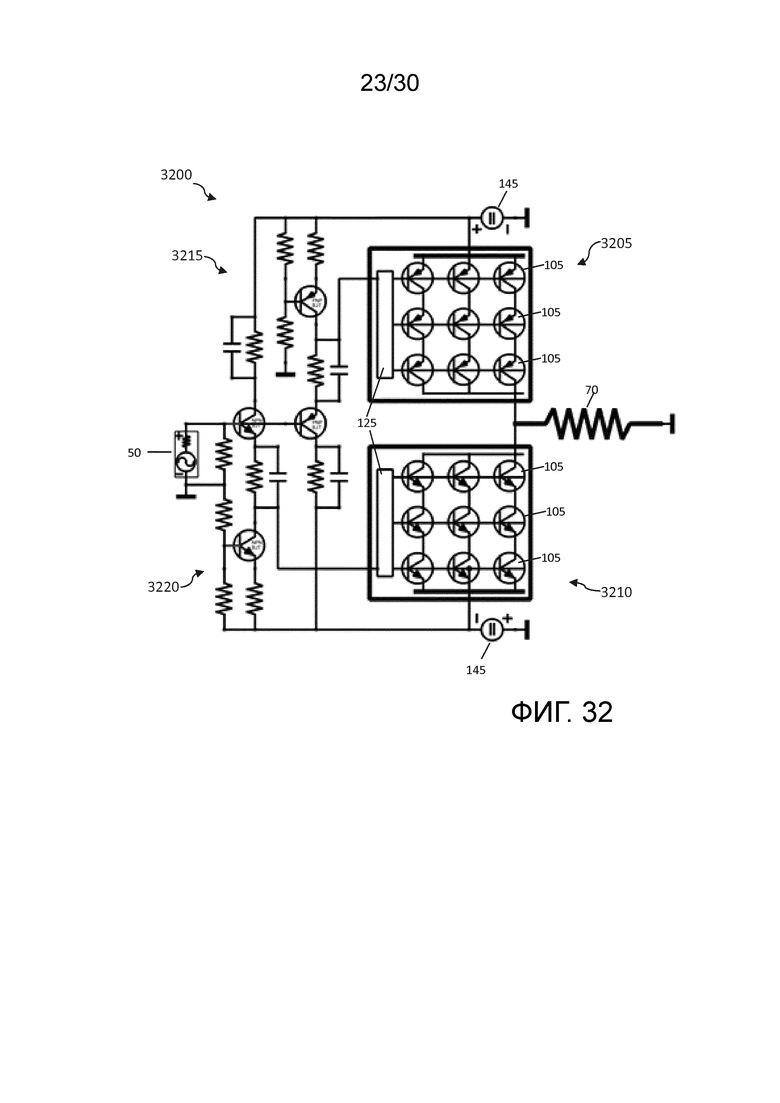

Фиг. 32 - схематическое представление двухмерного матричного усилителя мощности.

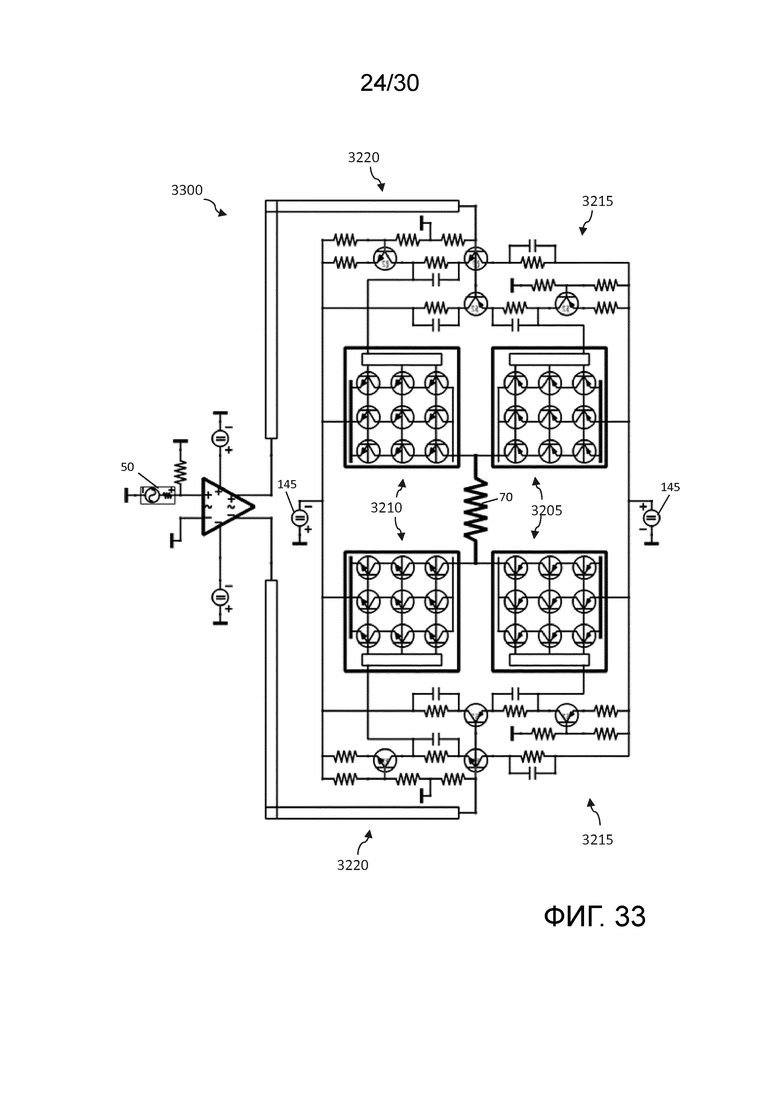

Фиг. 33 - схематическое представление двухмерного матричного усилителя мощности.

Фиг. 34 - схематическое представление матричного усилителя мощности.

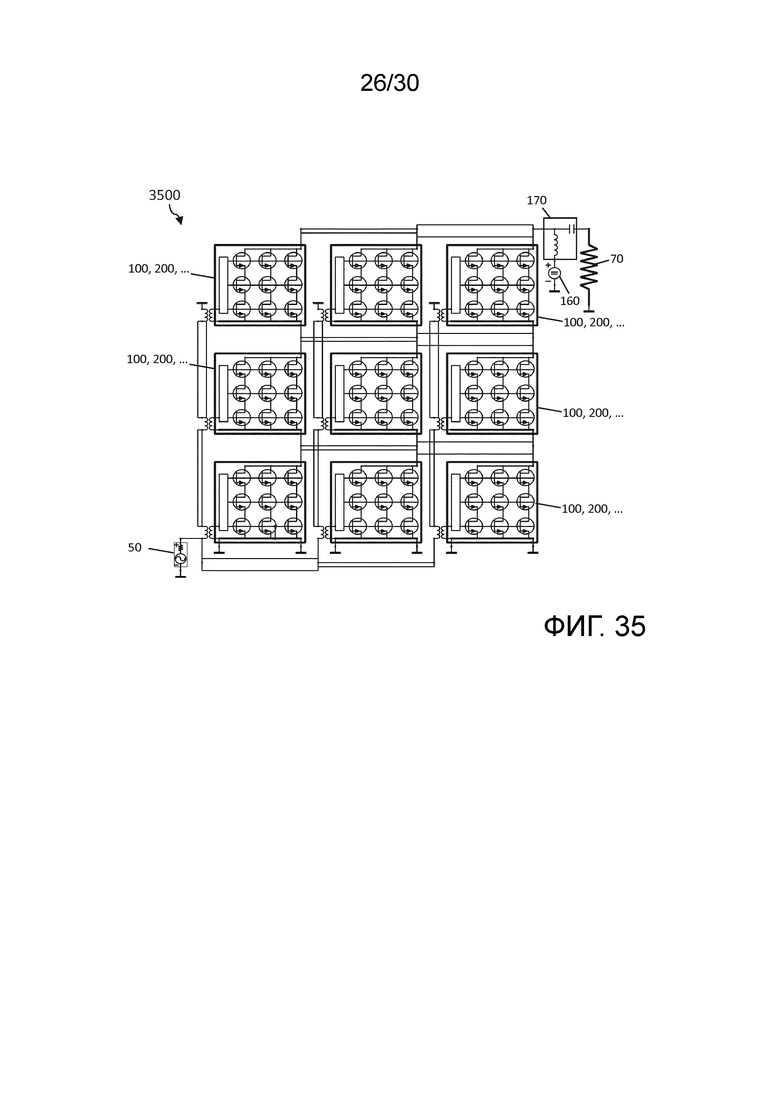

Фиг. 35 - схематическое представление матричного усилителя мощности.

Фиг. 36 - схематическое представление двухтактного каскада 3600, который включает в себя пару матричных усилителей.

Фиг. 37 - схематическое представление двухтактного каскада, который включает в себя пару матричных усилителей.

Фиг. 38 - схематическое представление двухмерного матричного усилителя мощности, который включает в себя пару двухтактных каскадов, соединенных в конфигурации "H-моста".

Фиг. 39 - схематическое представление двухтактного каскада 3900, который включает в себя пару матричных усилителей.

Одинаковые символы для ссылок на различных чертежах указывают одинаковые элементы.

Подробное описание

Фиг. 1 является схематическим представлением матричного усилителя 100 мощности, например, для усиления сигналов в микроволновом и миллиметровом диапазонах частот. Матричный усилитель 100 мощности включает в себя коллекцию активных ячеек, сформированных отдельными транзисторами 105. Транзисторы 105 соединены в нескольких стеках 110. Сами стеки 110 соединены параллельно между несбалансированной шиной 115 распределения и несбалансированной шиной 120 сбора. Шина 115 распределения присоединена для распределения сигнала от источника 50 сигнала на самые нижние транзисторы 105 в каждом из стеков 110. Шина 120 сбора присоединена для сбора сигналов, проходящих через стеки, и направления их к нагрузке 70. Компонент 125 управления матрицы может представлять собой пассивный элемент, который распределяет сигналы управления, сформированные источником 50 сигнала, или активную ячейку, которая формирует сигналы управления на основе вывода источника 50 сигнала. В любом случае сигналы управления распределяются на управляющие электроды отдельных транзисторов 105 через множество сбалансированных согласованных по строкам структур. В ответ на сигнал управления транзисторы 105 переключаются из более проводящего состояния в менее проводящее состояние и обратно, чтобы поочередно формировать несколько путей с более высокой и более низкой проводимостью между шинами 115, 120 и между источником 50 сигнала и нагрузкой 70. Поскольку стеки 110 соединены параллельно, матричный усилитель 100 мощности имеет оптимальный импеданс нагрузки, который может быть адаптирован таким образом, чтобы он был согласован с импедансом нагрузки 70 и, следовательно, передавал ей относительно большую часть максимально возможной мощности.

Матричный усилитель 100 мощности представляет собой "согласованный по строкам" усилитель мощности в том смысле, что он включает в себя множество компонентов управления строк, которые соединены для распределения сигнала управления к строкам к транзисторам 105 в разных стеках 110. В проиллюстрированной реализации транзисторы 105 матричного усилителя 100 мощности можно рассматривать как находящиеся в четырех разных "строках" 137 матрицы. Хотя транзисторы 105 в каждой строке 137 находятся в разных стеках 110, транзисторы 105 в каждой строке 137 присоединены к соответствующей согласованной по строкам структуре, которая в проиллюстрированной реализации включает в себя линию 130 распределения и элемент 135 согласования импедансов. В проиллюстрированной реализации элемент 135 согласования импедансов показан как усилитель с активным компонентом управления. Однако элемент 135 согласования импедансов также может быть сформирован пассивной цепью согласования импедансов. Некоторая часть каждого сигнала управления присоединяется к управляющим электродам на транзисторах 105 в каждой строке 137 посредством линии 130 распределения и элемента 135 согласования импедансов. Линия 130 распределения и элемент 135 согласования импедансов подают части сигналов управления на управляющие электроды с подходящими задержками, чтобы скоординировать проводимость тока посредством транзисторов 105 в каждой строке 137, тем самым усиливая сигналы управления. Сигнал управления, присоединенный к управляющему электроду каждого транзистора 105, подается на потенциал основного электрода истока/эмиттера. Сигналы управления "не заземлены" в том смысле, что любой управляющий ток, входящий в управляющий электрод данного транзистора 105, также выходит из транзистора 105 через основной электрод истока/эмиттера, но не вносит вклад в ток стока/коллектора "предыдущего" транзистора 105 в этом же стеке 110. Для ясности в проиллюстрированном схематическом представлении транзистор 105, который находится непосредственно под любым данным транзистором 105 в этом же стеке 110, является "предыдущим" транзистором 105. Следует понимать, что ориентация и расположение компонентов в проиллюстрированном схематическом представлении являются произвольными, и "предыдущий" транзистор останется "предыдущим" несмотря на другое физическое расположение в реальном устройстве (например, сверху, слева или позади "следующего" транзистора). Вместо этого "предыдущие" и "следующие" транзисторы могут быть идентифицированы их относительным расположением на проводящем пути между источником 50 сигнала и нагрузкой 70. В любом случае, вместо того чтобы вносить вклад в ток стока/коллектора предыдущего транзистора 105, ток, выходящий из транзистора 105 через основной электрод истока/эмиттера, возвращается в элемент 135 согласования импедансов посредством линии 130 распределения, которая расположена непосредственно под этим транзистором 105.

В проиллюстрированной реализации источник 50 сигнала является радиочастотным (RF) источником, который выдает сигнал, достигающий желаемого электрического тока между основными электродами активных ячеек в матричном усилителе 100 мощности. Например, источник 50 сигнала может выдавать сигнал, который представляет желаемую передачу связи. В некоторых реализациях источник 50 сигнала может выдавать сигнал, имеющий несущую или центральную частоту между почти постоянным током (DC) (в общем случае, несколько 100 МГц, вследствие чего разные транзисторы разъединены по емкости) и приблизительно 1/3 fT, где fT - переходная частота единичного усиления транзисторов 105. Например, в некоторых полевых транзисторах типа III-V fT может составлять около 30 ГГц. Некоторая часть сигнала, выдаваемого входным источником 50 сигнала, присоединяется к шине 115 посредством элемента 135 согласования импедансов. В проиллюстрированной реализации элемент 135 согласования импедансов показан как усилитель с активным компонентом управления. Таким образом, в проиллюстрированной реализации источник 50 сигнала непосредственно не выдает сигнал управления, который возбуждает управляющие электроды транзисторов 105. Вместо этого источник 50 сигнала выдает сигнал, который усиливается элементом 135 согласования импедансов, чтобы сформировать такой сигнал управления. В других реализациях элемент 135 согласования импедансов может быть сформирован посредством пассивной цепи согласования импедансов. В таких реализациях источник 50 сигнала может непосредственно выдавать сигнал управления, который возбуждает управляющие электроды транзисторов 105.

Шина 115 распределения присоединена для распределения части сигнала связи и сигнала DC на управляющие электроды и на основные электроды истока/эмиттера транзисторов 105 в первой строке 138. В некоторых реализациях элемент 135 согласования импедансов может действовать как симметрирующий трансформатор, и шина 115 распределения может быть реализована как две проводных линии передачи, которые симметричны относительно земли. Шина 115 распределения заканчивается в радиочастотной нагрузке и цепи 140 смещения затвора 140. В проиллюстрированной реализации радиочастотная нагрузка и цепь 140 смещения затвора включают в себя источник 145 DC, который выдает сигнал DC, который управляет электрическим током через стеки 110 посредством управляющих электродов транзисторов 105 в первой строке 138. В частности, как только ток начинает течь через транзисторы 105 в первой строке 138, за ним следует электрический ток в следующей строке 137. В проиллюстрированной реализации выходной потенциал из источника 145 DC является отрицательным относительно земли и сбрасывает потенциал на шине 120 сбора, когда стеки 110 являются проводящими. Выходной потенциал источника 145 DC изолирован от заземленного провода двух проводных линий передачи шины 115 распределения посредством емкости 150 и присоединен к другому проводу посредством импеданса 155. В проиллюстрированной реализации импеданс 155 является действительным импедансом, который обеспечивает часть нагрузки, которая согласована элементом 135 согласования импедансов.

Шина 120 сбора собирает выходную мощность из каждого стека 110 и направляет его к нагрузке 70. Шина 120 сбора также может быть реализована как две проводных линии передачи, которые симметричны относительно земли. В любом случае провода шины 120 сбора присоединены к комбинированному порту сепаратора 170 питания высокого напряжения. Нагрузка 70 присоединена к высокочастотному порту сепаратора 170 питания, и источник 160 DC присоединен к низкочастотному порту. Потенциал не заземленных проводов, таким образом, смещаются источником 160 DC на потенциал DC, подходящий для питания матричного усилителя 100 мощности. В проиллюстрированной реализации, в которой элементы 135 согласования импедансов реализованы как усилители с активным компонентом управления, выходной потенциал DC источника 160 DC проводится одной или более линиями 160 электропередачи к этим усилителям с активным компонентом управления.

В проиллюстрированной реализации усилитель 100 мощности включает в себя коллекцию отдельных транзисторов 105. Транзисторы 105 могут представлять собой любые из полупроводниковых устройств многих различных типов, например, полевые транзисторы (FET) или биполярные транзисторы (BJT), с наличием или без наличия какого-либо индивидуального согласования или предварительного согласования. В некоторых реализациях активные ячейки матрицы усилителя 100 мощности не являются отдельными транзисторами, а вместо этого представляют собой множественные транзисторы, например, собранные в модули усилителя.

Фиг. 2 является схематическим представлением матричного усилителя 200 мощности. Матричный усилитель 200 мощности также включает в себя отдельные транзисторы 105, которые соединены в нескольких стеках 110. Сами стеки 110 соединены параллельно между несбалансированной шиной 115 распределения и несбалансированной шиной 120 сбора. В отличие от усилителя 100 мощности (фиг. 1), шина 115 распределения обязательно является несбалансированной, поскольку матричный усилитель 200 мощности не включает в себя элемент 135 согласования импедансов, который может потенциально действовать как симметрирующий трансформатор между источником 50 сигнала и шиной 115 распределения.

Матричный усилитель 200 мощности является "согласованным по столбцам" усилителем мощности в том смысле, что матричный усилитель 200 мощности включает в себя множество компонентов 205 управления столбцов, которые соединены для распределения сигнала управления на столбцы к транзисторам 105 по соответствующим стекам 110. В проиллюстрированной реализации транзисторы 105 матричного усилителя 200 мощности можно рассматривать как находящиеся в четырех разных "столбцах" 237 матрицы. Транзисторы 105 в каждом столбце 237 находятся в одном и том же стеке 110 и соединены с компонентом 205 управления отдельного столбца. Компоненты 205 управления столбцов могут быть реализованы множеством различных методов, в том числе как (пассивные) компоненты управления столбцов с компенсационной связью и (активные) компоненты управления столбцов, которые включают в себя, например, дифференциальные усилители, в том числе описанные ниже. Компоненты 205 управления столбцов могут являться активными или пассивными элементами.

Каждый компонент 205 управления столбца включает в себя контакт 210 управляющего электрода и контакт 215 основного электрода. Контакты 210 управляющего электрода присоединяют компоненты 205 управления столбцов к управляющим электродам соответствующих транзисторов 105. Контакты 215 основного электрода присоединяют компоненты 205 управления столбцов к основным электродам истока/эмиттера соответствующих транзисторов 105. Сигнал управления, присоединенный к управляющему электроду каждого транзистора 105, подается на потенциал основного электрода истока/эмиттера. Кроме первой строки 138 (поясняется ниже), контакты 210, 215 электродов формируют сбалансированное соединение для управляющих транзисторов 105. В действительности сигналы управления не заземлены, и любой управляющий ток, входящий в управляющий электрод данного транзистора 105, также покидает транзистор 105 через основной электрод истока/эмиттера, но не вносит вклад в ток стока/коллектора предыдущего транзистора 105 в том же самом стеке 110.

В первой строке 138 матричного усилителя 200 мощности основные электроды истока/эмиттера всех транзисторов 105 соединены с землей. Как следствие, контакты 215 основных электродов к основным электродам истока/эмиттера транзисторов 105 в первой строке 138 также соединены с землей и, таким образом, формируют несбалансированное соединение. Как и в случае матричного усилителя 100 мощности (фиг. 1), источник 145 DC 145 управляет током, который должен течь через стеки 110, посредством управляющих электродов транзисторов 105 в первой строке 138.

Фиг. 3 является схематическим представлением согласованного по столбцам матричного усилителя 300 мощности. Для удобства проиллюстрирован только один стек 110 (и, следовательно, один столбец) матричного усилителя 300 мощности. Однако следует понимать, что матричный усилитель 300 мощности может включать в себя много строк и столбцов, которые учитывают индивидуальные операционные требования, в том числе выходной импеданс и усиление.

Матричный усилитель 300 мощности включает в себя несбалансированный пассивный компонент 305 управления матрицы, который распределяет сигналы, cформированные источником 50 сигнала, на коллекцию сбалансированных линий 310 распределения. Каждая линия 310 распределения присоединяет соответствующую часть сигнала управления к транзисторам 105 в разных стеках 110. Снова напомним, что только один стек 110 проиллюстрирован в схематическом представлении матричного усилителя 300 мощности, хотя операционный матричный усилитель 300 мощности будет включать в себя множество стеков 110.

Несбалансированный пассивный компонент 305 управления матрицы присоединен к каждой из сбалансированных линий 310 распределения симметрирующим трансформатором 315. Симметрирующие трансформаторы 315 не только преобразовывают несбалансированный сигнал на пассивном компоненте 305 управления матрицы в сбалансированный сигнал на линиях 310 распределения, но симметрирующие трансформаторы 315 также действуют как элементы согласования импедансов, чтобы подать сигнал управления к транзисторам 105 в разных стеках 110.

Каждая сбалансированная линия 310 распределения включает в себя проводящий путь 320, который присоединяет первый электрод обмотки симметрирующего трансформатора 315 к основным электродам истока/эмиттера транзисторов 105, проводящий путь 325 присоединяет другой, второй электрод обмотки симметрирующего трансформатора 315 к управляющим электродам транзисторов 105, и проводящий путь 330 между либо средней точкой 345 соответствующего симметрирующего трансформатора 315, либо вторым электродом соответствующего симметрирующего трансформатора 315, к источнику 335 DC относительно земли. Каждый источник 335 DC смещает потенциал управляющего электрода соответствующего транзистора 105. Каждый проводящий путь 320 истока/эмиттера включает в себя емкость 340, которая изолирует остаток линии 310 распределения от потенциала DC на соответствующем истоке/эмиттере электродов транзисторов 105. Каждый из проводящих путей 330 источника DC включает в себя индуктивность 350, которая изолирует радиочастотный сигнал от источников 335 DC.

Фиг. 4 является схематическим представлением согласованного по столбцам матричного усилителя 400 мощности. Для удобства проиллюстрирован только один стек 110 (и, следовательно, один столбец) матричного усилителя 400 мощности. Однако следует понимать, что матричный усилитель 400 мощности может включать в себя много строк и столбцов, которые учитывают индивидуальные операционные требования, в том числе выходной импеданс и усиление.

Матричный усилитель 400 мощности использует параллельные управляющие схемы 405 с компенсационной связью для распределения сигналов, сформированных источником 50 сигнала, на транзисторы 105 в стеке 110. Параллельные управляющие схемы 405 с компенсационной связью переносят часть выходного напряжения, например, напряжения стока/коллектора каждого соответствующего транзистора 105 (например, транзистора 105 k-ого звена), чтобы подавать сигнал управления на управляющий электрод соответствующего "следующего" транзистора 105 (например, транзистора (k+1)-ого звена) в стеке 110.

Каждая параллельная управляющая схема 405 с компенсационной связью включает в себя элементы 415 импеданса и емкости 420. Элементы 415 импеданса представляют собой произвольные пассивные комплексные импедансы и могут включать в себя одну или более индуктивностей, конденсаторов и/или пассивных элементов, имеющих сопротивление. Элементы 415 импеданса управляющей схемы 405 формируют схему делителя напряжения AC, которая передает часть выходного напряжения каждого соответствующего предыдущего транзистора (например, k-ого звена) управляющему электроду соответствующего следующего транзистора 105 ((k+1)-ого звена) в стеке 110. Например, элементы 415 импеданса управляющей схемы 405 k-ого звена формируют делитель напряжения между напряжением на верхнем основном электроде 436 (например, на стоке/коллекторе) транзистора 105 k-ого звена и напряжением на нижнем основном электроде 437 (например, на истоке/эмиттере) транзистора 105 k-ого звена. Вывод управляющей схемы 405 k-ого звена (например, электрод между элементами 415 импеданса) подается на входной электрод (например, на затвор) транзистора 105 (k+1)-ого звена.

"Верхними" основными электродами транзисторов 105 являются электроды, которые расположены по направлению к выходному концу стека 110 (т.е., к ближайшей шине 120 сбора) на проводящем пути между источником 50 сигнала и нагрузкой 70. В проиллюстрированных схематических представлениях все верхние основные электроды являются электродами стока/коллектора, хотя это не обязательно имеет место. "Нижнимиʺ основными электродами транзисторов 105 являются электроды, которые расположены по направлению ко входному концу стека 110 (т.е., к ближайшей шине 115 распределения). В проиллюстрированных схематических представлениях все нижние основные электроды являются электродами истока/эмиттера, хотя это не обязательно имеет место.

Емкости 420 изолируют сигнал управления для каждого следующего транзистора 105 от потенциалов DC на соответствующем электродах истока/эмиттера и электродах стока/коллектора предыдущего транзистора 105. Общая выходная мощность стека110 увеличивается по мере увеличения частоты сигналов, сформированных источником 50 сигнала, поскольку часть энергии, произведенной каждым транзистором 105 в стеке, используется для возбуждения соответствующего следующего транзистора 105.

Шина 115 распределения и элемент 410 согласования импедансов проводят часть сигнала, сформированного источником 50 сигнала, на нижнюю строку 406 транзисторов 105 в разных стеках 110, но верхняя строка 407 транзисторов 105 подвергается возбуждению входными сигналами от делителей напряжения или управляющих схем 405. Аналогичным образом, элементы 455 согласования выходного импеданса присоединяют выходной сигнал каждого стека 110 к шине 120 сбора. Снова напомним, что только один стек 110 проиллюстрирован в схематическом представлении матричного усилителя 400 мощности, хотя операционный матричный усилитель 400 мощности будет включать в себя множество стеков 110.

Потенциал управляющего электрода каждого транзистора 105 k-ого звена (за исключением первого звена) смещается схемой 430 делителя напряжения DC. Каждая схема 430 делителя напряжения DС включает в себя сопротивления 435, которые делят напряжение между верхним основным электродом 436 (например, стоком/коллектором) этого транзистора 105 k-го звена и верхним основным электродом 437 каждого "предыдущего" транзистора 105 (например, (k-1)-го звена). Потенциал транзистора первого (наиболее нижнего) звена смещается источником 145 DC.

Линии 440 распределения подают сигнал управления с компенсационной связью и ток стека между транзисторами 105 в стеке. Линии 440 распределения представляют собой линии передачи с тремя линиями, включающими в себя две сигнальных линии 445 и одну линию 450 заземления. В каждой линии 440 распределения одна сигнальная линия 445 несет сигнал управления с компенсационной связью, и другая сигнальная линия 445 несет ток стека между транзисторами 105.

Фиг. 5 является схематическим представлением согласованного по столбцам матричного усилителя 500 мощности. Для удобства проиллюстрирован только один стек 110 (и, следовательно, один столбец) матричного усилителя 500 мощности. Однако следует понимать, что матричный усилитель 500 мощности может включать в себя много строк и столбцов и учитывать индивидуальные операционные требования, в том числе выходной импеданс и усиление. Матричный усилитель 500 мощности подобен матричному усилителю 400 мощности (фиг. 4) за исключением того, что потенциал управляющего электрода каждого транзистора 105 смещается источником 505 напряжения DC схемы 430 делителя напряжения DC.

Кроме того, каждый источник DC изолирован от радиочастотных сигналов индуктивностью 510.

Как и в случае матричного усилителя 400, линии 440 распределения матричного усилителя 500 присоединяют оба сигнала управления с компенсационной связью и ток стека между транзисторами 105 в стеке.

Линии 440 распределения представляют собой линии передачи с тремя линиями, включающими в себя две сигнальных линии 445 и одну линию 450 заземления. В каждой линии 440 распределения одна сигнальная линия 445 несет сигнал управления с компенсационной связью, и другая сигнальная линия 445 несет ток стека между транзисторами 105.

Управляющие схемы 405 с компенсационной связью матричных усилителей 400 и 500 считаются имеющими параллельную компенсационную связь, поскольку сигнал управления с компенсационной связью получен через делитель напряжения, который соединен параллельно с транзисторным стеком. Кроме того, каждый из сигнала управления с компенсационной связью и тока стека соединен между транзисторами 105 в стеке через разные сигнальные линии 445 в линиях 440 распределения.

Фиг. 6 является схематическим представлением согласованного по столбцам матричного усилителя 600 мощности. Для удобства проиллюстрирован только один стек 110 (и, следовательно, один столбец) матричного усилителя 600 мощности. Однако следует понимать, что матричный усилитель 600 мощности может включать в себя много строк и столбцов, которые учитывают индивидуальные операционные требования, в том числе выходной импеданс и усиление.

Матричный усилитель 600 мощности использует последовательную компенсационную связь для распределения сигналов, сформированных источником 50 сигнала на транзисторы 105 в стеке 110. Симметрирующие трансформаторы 605 передают часть выходного тока (например, тока стока/коллектора) от каждого транзистора 105 в нижних строках 606, 607 матричного усилителя 600 мощности для подачи сигнала управления на управляющий электрод соответствующих следующих транзисторов 105 в стеке 110. Симметрирующие трансформаторы 605 представляют собой устройства с тремя электродами, которые подают часть выходного тока от транзистора в одной из нижних строк 606, 607 как сигнал управления управляющего электрода для соответствующего следующего транзистора 105 в следующем более высокой строке, а также преобразовывают несбалансированный выходной ток в сбалансированный сигнал управления.

Фиг. 7 показывает схематическое представление трех реализаций симметрирующего трансформатора 605. Первая реализация представляет собой трансформатор 605a. Трансформатор 605a включает в себя первичную катушку 705, вторичную катушку 710 и общий электрод 715, присоединенный и к первичной катушке 705, и к вторичной катушке 710. В некоторых реализациях номинальное значение коэффициента трансформации трансформаторов 605a выбирается таким образом, чтобы оно соответствовало усилению по току транзисторов 105. Когда трансформатор 605a используется в качестве симметрирующего трансформатора 605 в матричном усилителе 600 мощности, электрод 705 первичной катушки присоединен к верхнему основному электроду 636 (например, стоку/коллектору) транзистора 105, общий электрод 715 присоединен к нижнему основному электроду 637 (например, истоку/ эмиттеру) соответствующего следующего транзистора 105, и электрод 710 вторичной катушки присоединен к управляющему электроду соответствующего следующего транзистора 105. Таким образом, выходной сигнал вторичной катушки 710 подает входной сигнал управления на управляющий электрод соответствующего следующего транзистора 105.

Второй реализацией симметрирующего трансформатора 605 является T-образная схема 605b, включающая в себя три элемента 720 проводимости, сконфигурированные как T-образная цепь (или соединение "звездой"). Третья реализация симметрирующего трансформатора 605 представляет собой пи-образную цепь 605c, включающую в себя три импедансных элемента 730, сконфигурированных как пи-образная цепь (или соединение треугольником). Разные реализации симметрирующего трансформатора 605 могут использоваться в разных реальных реализациях матричных усилителей мощности. Например, элементы 720 проводимости T-образной цепи 605b могут иметь преимущество в некоторых устройствах сверхвысокочастотных интегральных схем, тогда как импедансные элементы 730 пи-образной цепи 605c могут иметь преимущество в других случаях в зависимости от таких факторов, как технология обработки и конструкция других компонентов в матричном усилителе мощности.

Снова обратимся к фиг. 6, на которой показано, что емкости 620 включены в проводящий путь между симметрирующими трансформаторами 605 и управляющими электродами транзисторов 105. Емкости 620 изолируют сигнал управления для каждого транзистора 105 от потенциала DC на соответствующем истоке/эмиттере и электродах стока/коллектора транзисторов 105. Кроме того, общая выходная мощность стека 110 уменьшается по мере увеличения частоты сигналов, сформированных источником 50 сигнала, поскольку часть энергии, произведенной каждым транзистором 105 в стеке, используется для управления соответствующим следующим транзистором 105.

Шина 115 распределения несет соответствующую часть сигналов, сформированных источником 50 сигнала, на нижнюю строку 606 транзисторов 105 в разных стеках 110. Элементы 610 согласования импедансов подают сигнал источника на шине 115 распределения к нижней строке 606 транзисторов 105 в разных стеках 110. Аналогичным образом, элементы 655 согласования выходного импеданса присоединяют выходной сигнал каждого стека 110 к шине 120 сбора. Снова напомним, что только один стек 110 проиллюстрирован в схематическом представлении матричного усилителя 600 мощности, хотя операционный матричный усилитель 600 мощности будет включать в себя множество стеков 11.

Потенциал управляющего электрода каждого транзистора 105 смещается посредством схемы 630 делителя напряжения DC. Каждая из схем 630 делителя напряжения DC включает в себя сопротивления 635, которые делят напряжение между верхним основным электродом 636 (например, стоком/коллектором) транзистора 105 и нижним основным электродом 637 (например, истоком/эмиттером) предыдущего транзистора 105. Каждая из схем 630 делителя напряжения DC обеспечивает плавающее смещение на входе управления соответствующего транзистора 105. Исключением является схема 630 делителя напряжения DC, соединенная с нижним основным электродом транзистора 105 в нижней строке 606, который заземлен.

Линии 640 распределения соединяют транзисторы в стеке. Линии 640 распределения представляют собой несбалансированные линии передачи с тремя линиями, включающими в себя две сигнальные линии 645 и одну линию 650 заземления. Обычно схемы 630 делителя напряжения DC соединены c одной из сигнальных линий 645, и соответствующие верхние и нижние основные электроды транзистора 105 соединены с другой сигнальной линией 645. Линия 660 распределения, присоединяющая транзистор 105 в нижней строке 606 к первой следующей строке 607, является несбалансированной линией передачи с двумя линиями. Линия 660 распределения включает в себя одну сигнальную линию 645 и одну линию 650 заземления. Сигнальная линия 645 в линии 660 распределения присоединена к верхнему основному электроду транзистора 105 в нижней строке 606 и нижнему основному электроду транзистора 105 в следующей (второй) строке. Схема 630 делителя напряжения DC, которая соединена с нижним выходом транзистора в нижней строке 606, присоединена к линии 650 заземления в линии распределения 660.

Фиг. 8 является схематическим представлением согласованного по столбцам матричного усилителя 800 мощности. Для удобства проиллюстрирован только один стек 110 (и, следовательно, один столбец) матричного усилителя 800 мощности. Однако следует понимать, что матричный усилитель 800 мощности может включать в себя много строк и столбцов, которые учитывают индивидуальные операционные требования, в том числе выходной импеданс и усиление. Матричный усилитель 800 мощности подобен матричному усилителю 600 мощности, описанному выше со ссылкой на фиг. 6 и 7, за исключением того, что потенциал управляющего электрода каждого транзистора 105 смещается источником 805 напряжения DC вместо схемы 630 делителя напряжения DC. Кроме того, каждый источник DC изолирован от радиочастотных сигналов индуктивностью 810. Кроме того, линии 660 распределения с тремя линиями матричного усилителя 600 мощности могут быть заменены сбалансированными линиями 815 распределения с двумя линиями, которые включают в себя две сбалансированных сигнальных линии 645 и не включают в себя линию заземления.

Фиг. 9 является схематическим представлением активного сбалансированного компонента 905 управления матрицы для согласованного по строкам матричного усилителя 900 мощности. Для удобства проиллюстрирован только один стек 110 (и, следовательно, один столбец) матричного усилителя 900 мощности. Однако следует понимать, что матричный усилитель 900 мощности может включать в себя много строк и столбцов, которые учитывают индивидуальные операционные требования, в том числе выходной импеданс и усиление.

Сбалансированный активный компонент 905 управления матрицы распределяет сигналы, сформированные источником 50 сигнала, на коллекцию сбалансированных линий 910 распределения. Каждая линия 910 распределения присоединяет соответствующую часть сигнала управления к транзисторам 105 в разных стеках 110. Снова напомним, что только один стек 110 проиллюстрирован в схематическом представлении матричного усилителя 900 мощности, хотя операционный матричный усилитель 900 мощности будет включать в себя множество стеков 110.

Сбалансированный активный компонент 905 управления матрицы включает в себя множество сложенных в стек дифференциальных усилителей 915 с согласованием импедансов. Сбалансированный активный компонент 905 управления матрицы содержит на один меньше дифференциальных усилителей 915 с согласованием импедансов, чем транзисторов 105 в каждом стеке 110. Например, в показанном примере активный компонент 905 управления матрицы включает в себя три дифференциальных усилителя 915 с согласованием импедансов, чтобы управлять стеком 110 из четырех транзисторов 105. Первым дифференциальным усилителем 915 и транзистором 105 в нижней строке (строка 1) стека одновременно управляет источник 50 сигнала. Каждый k-ый дифференциальный усилитель 915 в активном компоненте 905 управления матрицы затем управляет (k+1)-ым транзистором 105 в стеке 110.

Более подробно, фиг. 10 является схематическим представлением дифференциального усилителя 915 с согласованием импедансов, который может использоваться в сбалансированных активных компонентах управления матрицы. Дифференциальный усилитель 915 включает в себя входной электрод 1080 с инвертированием, входной электрод 1082 без инвертирования, выходной электрод 1084 высокого уровня и выходной электрод 1086 низкого уровня. Дифференциальный усилитель 915 выдает сигнал на выходных электродах 1084, 1086, который представляет разность между сигналом на входных электродах 1080, 1082.

Снова обратимся к фиг. 9, на которой показано, что дифференциальные усилители 915 сложены в стек, и выходные электроды 1084, 1086 каждого дифференциального усилителя 915 (k-ого дифференциального усилителя 915) присоединены к входным электродам 1080, 1082 следующего дифференциального усилителя 915 ((k+1)-ого дифференциального усилителя 915) в активном компоненте 905 управления матрицы. В некоторых реализациях цепь согласования импедансов (не показана) может быть присоединена между каждым из дифференциальных усилителей 915. Кроме того, выходные электроды 1084, 1086 каждого дифференциального усилителя 915 присоединены к сбалансированной линии 910 распределения, которая обеспечивает сигнал управления соответствующему транзистору 105 в строках с 2 до N стека 110.

Каждая сбалансированная линия 910 распределения включает в себя проводящий путь 920, который присоединяет первый выходной электрод 1084, 1086 дифференциального усилителя 915 к основному электроду истока/эмиттера транзистора 105, и проводящий путь 325, который присоединяет другой выходной электрод 1084, 1086 дифференциального усилителя 915 к управляющим электродам транзистора 105. Каждый проводящий путь 920 истока/эмиттера включает в себя емкость 940, которая изолирует остаток линии 910 распределения от потенциала DC на соответствующем истоке/эмиттере электродов транзисторов 105. Более конкретно, выходной электрод 1086 без инвертирования со второго по N-ый дифференциальный усилитель 910 присоединен к проводящему пути управляющего электрода 925, и выходной электрод 1084 с инвертированием со второго по N-ый дифференциальный усилитель 910 присоединен к проводящему пути 920 истока/эмиттера. Однако у соединений выходных электродов 1084, 1086 первого дифференциального усилителя 915 с линией 910 распределения выполнен обмен местами. Таким образом, выходной электрод 1084 c инвертированием первого дифференциального усилителя 910 присоединен к проводящему пути управляющего электрода 925, и выходной электрод 1086 без инвертирования первого дифференциального усилителя 910 присоединен к проводящему пути 920 истока/эмиттера.

Кроме того, в некоторых реализациях, линии 910 распределения могут включать в себя цепь согласования импедансов (не показана) для согласования импеданса выходных электродов 1084, 1086 дифференциального усилителя 915 с входным импедансом транзисторов 105.

Дифференциальные усилители 915 снабжаются напряжением DC от двух отдельных путей DC: путей ODD и EVEN. Дифференциальные усилители 915 с нечетными номерами (от 1 до N) снабжаются от пути ODD, и дифференциальные усилители 915 с четными номерами (от 1 до N) снабжаются от пути EVEN. Каждый путь DC снабжается схемой 950, 955 истокового повторителя и присоединен к электроду 1090 снабжения высокого порядка дифференциального усилителя 915 высокого порядка (N или N-1) на соответствующем пути ODD или EVEN. Более конкретно, электрод 1090 снабжения высокого порядка N-ого дифференциального усилителя 915 присоединен к схеме истокового повторителя 950 (путь DC ODD). Тогда как электрод 1090 снабжения высокого порядка (N-1)-ого дифференциального усилителя 915 присоединен к схеме истокового повторителя 955 (путь DC EVEN).

Проводящий путь 956 присоединяет электрод снабжения низкого порядка N-ого дифференциального усилителя 915 к электроду снабжения высокого порядка следующего дифференциального усилителя 915 низкого порядка на пути ODD в активном компоненте 905 управления матрицы, в частности, первого дифференциального усилителя 915 в показанном примере. Электрод снабжения низкого порядка первого дифференциального усилителя 915 присоединен к отрицательному источнику DC.

Электрод снабжения низкого порядка (N-1)-ого (здесь второго) дифференциального усилителя 915 присоединен к земле в показанном примере. Однако в более крупном стеке активного компонента 905 управления матрицы электрод снабжения низкого порядка (N-1)-ого дифференциального усилителя 915 может быть присоединен к электроду снабжения высокого порядка следующего нечетного дифференциального усилителя 915 более низкого порядка посредством проводящего пути.

Истоковый повторитель 950 включает в себя пару согласованных транзисторов 952, каждый из которых присоединен между высоким потенциалом стороны стока и низким потенциалом стороны истока. Высокий потенциал стороны стока (электрод 960) присоединен к радиочастотной шине 120 сбора. Низкий потенциал стороны истока присоединен между импедансами 965a и 965b схемы делителя напряжения. Схема делителя напряжения создана импедансами 965a, 965b и 965c и также присоединена к электроду 960 и радиочастотной шине 120 сбора. Импедансы 965a, 965b и 965c делят радиочастотное выходное напряжение от шины 120 сбора, чтобы сместить потенциал управляющих электродов транзисторов 952, которые присоединены к схеме делителя напряжения между импедансами 965a и 965b. Электроды истоков транзисторов 952 присоединены к схеме разделителя напряжения между импедансами 965a и 965b через емкость 954a и к электроду снабжения низкого порядка N-ого дифференциального усилителя 915. Емкость 954a изолирует электрод снабжения низкого порядка N-ого дифференциального усилителя 915 от потенциала DC на радиочастотной шине 120 сбора.

Истоковый повторитель 955 включает в себя транзистор 953, который присоединен между высоким потенциалом стороны стока и низким потенциалом стороны истока. Высокий потенциал стороны стока присоединен к схеме разделителя напряжения между импедансами 965a и 965b и к электродам истока транзисторов 952. Низкий потенциал стороны истока присоединен между импедансами 965b и 965c схемы разделителя напряжения. Электрод истока транзистора 953 присоединен к схеме разделителя напряжения между импедансами 965b и 965c через емкость 954b и к электроду снабжения низкого порядка (N-1)-ого дифференциального усилителя 915. Емкость 954b изолирует электрод снабжения низкого порядка (N-1)-ого дифференциального усилителя 915 от потенциала DC на радиочастотной шине 120 сбора.

Истоковые повторители 950, 955 снабжаются от радиочастотных выходных сигналов матричного усилителя 900 мощности через радиочастотную шину 120 сбора. Таким образом, все электроды снабжения высокого и низкого порядка дифференциальных усилителей 915 находятся под действием плавающего потенциала AC и могут вместить полный размах колебаний выходного радиочастотного напряжения транзисторов 105 в стеке 110.

Фиг. 11 является схематическим представлением сбалансированного активного компонента 905 управления матрицы для согласованного по строкам матричного усилителя 1100 мощности. Для удобства проиллюстрирован только один транзисторный стек 110 из фиг. 1 (и, следовательно, единственный столбец транзисторов 105) матричного усилителя 1100 мощности. Однако следует понимать, что матричный усилитель 1100 мощности может включать в себя много строк и столбцов, которые учитывают индивидуальные операционные требования, в том числе выходной импеданс и усиление.

Сбалансированный активный компонент 1105 управления матрицы распределяет сигналы, сформированные источником 50 сигнала, на коллекцию сбалансированных линий 1110 распределения. Каждая линия 1110 распределения присоединяет соответствующую часть сигнала управления к транзисторам 105 в разных стеках 110. Снова напомним, что только один стек 110 проиллюстрирован в схематическом представлении матричного усилителя 1100 мощности, хотя операционный матричный усилитель 1100 мощности будет включать в себя множество стеков 110.

Сбалансированный активный компонент 1105 управления матрицы включает в себя множество сложенных в стек дифференциальных усилителей 1115. Первым дифференциальным усилителем 1115 и транзистором 105 в нижней строке (в первой строке) стека одновременно управляет источник 50 сигнала. Каждый k-ый дифференциальный усилитель 1115 в активном компоненте 1105 управления матрицы затем управляет (k+1)-ым транзистором 105 в стеке 110.

Каждый дифференциальный усилитель 1115 включает в себя пару согласованных транзисторов 1194, каждый из которых присоединен между высоким потенциалом стороны стока и низким потенциалом стороны истока. Только первый дифференциальный усилитель 1115 включает в себя источник 1188 тока. За исключением N-ого дифференциального усилителя 1115 высоким потенциалом стороны стока каждый k-ый дифференциальный усилитель 1115 снабжается посредством низкого потенциала стороны истока (k+1)-ого дифференциального усилителя 1115. Высоким потенциалом стороны стока N-ый дифференциальный усилитель 1115 снабжается посредством радиочастотной шины 120 сбора. Аналогичным образом, за исключением первого дифференциального усилителя 1115 низким потенциалом стороны истока каждый k-ый дифференциальный усилитель 1115 снабжается посредством высокого потенциала стороны истока (k-1)-ого дифференциального усилителя 1115. Низким потенциалом стороны истока первый дифференциальный усилитель 1115 снабжается посредством источника 1150 DC. Таким образом, дифференциальные усилители 1115 сложены в стек таким образом, что ток DC через первый дифференциальный усилитель 1115 снова используется каждым дифференциальным усилителем в активном компоненте 1105 управления матрицы.

Дифференциальные усилители 1115 в активном компоненте 1105 управления матрицы соединены вместе через сбалансированные линии 1135 распределения. В некоторых реализациях цепь согласования импедансов (не показана) также может быть присоединена между каждым дифференциальным усилителем 1115. Кроме того, выходные электроды 1184 каждого дифференциального усилителя 1115 (кроме N-ого дифференциального усилителя 1115) присоединены к сбалансированной линии 1110 распределения, которая обеспечивает сигнал управления соответствующему транзистору 105 в строках со второго по N стека 110.

Каждая сбалансированная линия 1110 распределения включает в себя проводящий путь 1120, который присоединяет первый выходной электрод 1184 дифференциального усилителя 1115 к основному электроду истока/эмиттера транзистора 105, и проводящий путь 1125, который присоединяет другой выходной электрод 1184 дифференциального усилителя 1115 к управляющему электроду транзистора 105. Каждый проводящий путь 1120 истока/эмиттера включает в себя емкость 1140, которая изолирует остаток линии 1110 распределения от потенциала DC на соответствующем истоке/эмиттере электродов транзисторов 105. Кроме того, в некоторых реализациях линии 1110 распределения могут включать в себя цепь согласования импедансов (не показана), чтобы согласовать импеданс выходные электроды 1084, 1086 дифференциального усилителя 1115 с входным импедансом транзисторов 105.

Кроме того, управляющие электроды транзисторов 1194 (входные электроды 1182 дифференциальных усилителей 1115) присоединены к выходным электродам 1184 каждого предыдущего, (k-1)-ого дифференциального усилителя 1115. Падение потенциала на каждом множестве импедансов 1196 используется для управления входом (управляющими электродами транзисторов 1194) каждого дифференциального усилителя 1115, за исключением первого дифференциального усилителя 1115. Управляющим электродом первого из транзисторов 1194 в первом дифференциальном усилителе 1115 управляет радиочастотный источник 50, и управляющий электрод второго из транзисторов 1194 смещается потенциалом DC из источника 145 DC. Управляющий электрод первого из транзисторов 1194 в первом дифференциальном усилителе 1115 присоединен к радиочастотному источнику 50 через цепь 1130 согласования импедансов.

Как показано, истоки транзисторов 1194 первого дифференциального усилителя 1115 соединены вместе и имеют общий путь к источнику 1188 тока. Импеданс между обоими выходными электродами 1184 и источником 1188 тока, таким образом, почти идентичен за исключением относительно небольших различий в импедансе транзисторов 1194. Первый дифференциальный усилитель 1115, таким образом, может действовать как симметрирующий трансформатор и преобразовывать несбалансированный радиочастотный сигнал источника в сбалансированный вывод.

Кроме того, управляющий электрод одного из транзисторов 1194 каждого из дифференциальных усилителей 1115 со второго по N смещается посредством части радиочастотного выходного сигнала от радиочастотной шины 120 сбора. Схема 1160 делителя напряжения, созданная цепью импедансов 1162, делит напряжение радиочастотного выходного сигнала.

Источник 1188 тока обеспечивает ток DC для всех дифференциальных усилителей 1115 в активном компоненте 1105 управления матрицы. Источник 1188 тока включает в себя транзистор 1189, который подает ток через дифференциальные усилители 1115. Потенциал управляющего электрода транзистора 1189 смещается посредством источника 1150 DC через импеданс 1191. Кроме того, электрод истока транзистора 1189 присоединен к источнику 1150 DC через импеданс.