Техническое решение (варианты) относится к области интегральной микроэлектроники и может быть использовано в системах обработки оптической информации.

Известно устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения (Very wide dynamic range SWIR sensors for very low background applications / Roberts F. Cannata, Randal J. Hansen, Adrienne N. Costello, William J. Parrish // Proc. SPIE 3698, Infrared Technology and Application XXV, July 1999), содержащее входную ячейку, столбцовую шину, источник тока, столбцовый буферный усилитель. Входная ячейка выполнена в составе емкостного трансимпедансного усилителя (ТИУ), который образован инвертирующим усилителем с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором и ключом сброса, а также в составе ограничивающего полосу пропускания ТИУ конденсатора, ключа выборки/хранения, конденсатора выборки/хранения результата интегрирования, истокового повторителя для перезарядки паразитной емкости столбцовой шины, адресного ключа. Вход ТИУ выполнен с возможностью соединения с анодом фотодиода посредством индиевого столба. К выходу ТИУ подсоединены один конец ключа выборки/хранения и одна обкладка ограничивающего полосу пропускания ТИУ конденсатора, вторая обкладка которого закорочена на «землю». Второй конец ключа выборки/хранения соединен с входом (затвором) истокового повторителя и одной обкладкой конденсатора выборки/хранения результата интегрирования, вторая обкладка которого закорочена на «землю». Выход истокового повторителя выполнен с возможностью коммутации на столбцовую шину через адресный ключ. Со столбцовой шиной соединены источник тока, обеспечивающий работу истокового повторителя, столбцовый буферный усилитель.

Устройство разработано для фотоприемников на основе HgCdTe и InGaAs коротковолнового инфракрасного (ИК) диапазона формата 320×256 с шагом 30 мкм. Устройство выполнено на полупроводниковой подложке по КМОП (комплементарная структура металл-оксид-полупроводник) технологии с проектной нормой 0,6 мкм.

Входная ячейка обеспечивает работу в режиме «Моментального снимка» в двух вариантах - «интегрирование, затем считывание» (Integrate Then Read - ITR) и «интегрирование во время считывания» (Integrate While Read - IWR).

Стабилизация напряжения смещения (рабочей точки) на фотодиоде достигается за счет возникающего в емкостном ТИУ эффекта Миллера, в результате которого эффективная входная емкость увеличивается пропорционально величине емкости накопительного конденсатора, установленного в цепи обратной связи инвертирующего усилителя, образующего ТИУ, и его коэффициента усиления по напряжению.

Принцип работы устройства состоит в следующем. В начале кадра осуществляется сброс емкостей входной ячейки. В результате сброса происходит установка постоянного напряжения на входе и выходе ТИУ. После сброса начинается процесс интегрирования фототока. ТИУ преобразует накопленный во время интегрирования фотозаряд в напряжение. Величина выходного напряжения ТИУ пропорциональна интенсивности падающего на фотодиод потока излучения, что, таким образом, позволяет судить об интенсивности излучения. В режиме IWR по окончанию акта интегрирования ключ выборки/хранения открывается, ТИУ перезаряжает конденсатор выборки/хранения результата интегрирования, с которого происходит дальнейшее считывание информации при вновь закрытом ключе выборке/хранения. Одновременно со считыванием информации со всего массива входных ячеек в режиме IWR начинается новый акт интегрирования. При считывании информации с входной ячейки адресный ключ коммутирует выход истокового повторителя на столбцовую шину. В результате на входе столбцового буферного усилителя обеспечивается установка напряжения величиной, приблизительно равной величине напряжения на конденсаторе выборки/хранения результата интегрирования с учетом смещения на величину порогового напряжения истокового повторителя. Столбцовый буферный усилитель усиливает устанавливаемый на входе сигнал по мощности (повторяет напряжение) для осуществления дальнейшего мультиплексирования.

Разработкой данного устройства не решается техническая проблема получения устройства считывания сигналов с фотоприемной матрицы инфракрасного излучения, обеспечивающего снижение энергопотребления и повышение качества фотоэлектрических характеристик, поскольку не устраняет ряд недостатков.

К недостаткам рассмотренного технического решения относится высокое энергопотребление, неудовлетворительная линейность передаточной характеристики устройства считывания, низкая зарядовая емкость входной ячейки, неоднородность выходного сигнала.

Причины приведенных недостатков заключаются в следующем.

Для столбцовой шины присуща большая паразитная емкость. Необходимость ее перезарядки обеспечивает значительное энергопотребление во время считывания. Следует также отметить, что в момент полноформатного сброса происходит перезарядка накопительного конденсатора, ограничивающего полосу пропускания ТИУ конденсатора и емкости обратно смещенного p-n-перехода фотодиода во всем массиве входных ячеек устройства считывания, каждая из которых соединена с индивидуальным фоточувствительным элементом фотоприемной матрицы. Указанная перезарядка приводит к броску тока в цепи питания.

Неудовлетворительная линейность передаточной характеристики может быть связана с использованием в составе ТИУ схемотехнических решений, для которых характерен малый коэффициент усиления по напряжению. Кроме того, использование истокового повторителя из-за наличия эффекта влияния подложки ослабляет амплитуду выходного сигнала и вносит нелинейные искажения.

В целях минимизации вклада технологического разброса характеристик истокового повторителя в общий геометрический шум устройства считывания существует необходимость избегать использования минимальных топологических размеров. Это обстоятельство приводит к увеличению части площади входной ячейки, занимаемой повторителем, и, как следствие, не позволяет использовать максимум площади для размещения электрической схемы емкостного ТИУ с высоким коэффициентом усиления по напряжению, также не позволяет увеличивать величину зарядовой емкости.

Неоднородность выходных напряжений со всех ячеек устройства считывания обеспечивается технологическим разбросом электрической емкости накопительного конденсатора и разбросом напряжений смещения инвертирующих усилителей в составе ТИУ. При реализации емкостного ТИУ на базе инвертирующего усилителя без дифференциального входа отсутствует возможность точной подстройки напряжения смещения на фотодиоде. В результате технологического разброса однородность смещения снижается. Напряжение смещения может изменяться в зависимости от температуры и рабочего тока ТИУ. Кроме того, технологический разброс порогового напряжения истоковых повторителей, паразитного сопротивления столбцовых шин, опорного тока истоковых повторителей приводит к увеличению геометрического шума устройства считывания - увеличению неоднородности выходных напряжений.

Известно устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения (An uncooled 1280×1024 InGaAs focal plane array for small platform, shortwave infrared imaging / J. Battaglia, M. Blessenger, M. Enriquez, M. Ettenberg, M. Evans, K. Flynn, M. Lin, J. Passe, M. Stern, T. Sudol // Proc. SPIE 7298, Infrared Technology and Application XXXV, 729883C, 7 May 2009), содержащее входную ячейку, столбцовую шину, попарно переключаемые столбцовые усилители и конденсаторы выборки/хранения. Входная ячейка выполнена в составе емкостного трансимпедансного усилителя (ТИУ), который образован операционным усилителем (ОУ) с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором, а также параллельно подключенными в цепь обратной связи ключом сброса, транзистором для реализации функции «антиблюминга», дополнительным накопительным конденсатором с активирующими его ключами. Кроме того, в составе входной ячейки выполнены ограничивающий полосу пропускания ТИУ конденсатор, адресный ключ, ключ компенсации смещения при сбросе. ТИУ выполнен с возможностью соединения с анодом фотодиода посредством индиевого столба инвертирующим входом и с возможностью подачи опорного напряжения на неинвертирующий вход. Выход ТИУ соединен с одним концом адресного ключа и одной обкладкой ограничивающего полосу пропускания ТИУ конденсатора, вторая обкладка которого закорочена на «землю». Адресный ключ выполнен с возможностью коммутации при считывании выхода ТИУ на столбцовую шину. К столбцовой шине подключены попарно переключаемые столбцовые усилители и конденсаторы выборки/хранения. ТИУ реализован с возможностью регулирования тока потребления (нагрузочной способности) посредством управления напряжения смещения программно-аппаратным комплексом.

Устройство разработано для фотоприемников на основе InGaAs для коротковолнового ИК-диапазона формата 1280×1024 с шагом 15 мкм. Устройство выполнено на полупроводниковой подложке по КМОП технологии с проектной нормой 0,35 мкм.

Принцип работы устройства состоит в следующем. В начале кадра осуществляется сброс емкостей входной ячейки. В результате сброса происходит установка постоянного напряжения на входе и выходе ТИУ, поданного на неинвертирующий вход. Напряжение смещения на фотодиоде при этом определяется разностью между опорным напряжением ТИУ и напряжением на общем катоде фотодиодов фотоприемной матрицы. После сброса начинается процесс интегрирования фототока. ТИУ преобразует накопленный во время интегрирования фотозаряд в напряжение. После акта интегрирования адресный ключ коммутирует выход ТИУ на столбцовую шину. ТИУ перезаряжает паразитную емкость столбцовой шины и конденсатор выборки/хранения. В то время как на первом наборе конденсаторов выборки/хранения происходит формирование сигнальной информации с входных ячеек определенной строки, дублирующие столбцовые усилители осуществляют дальнейший вывод сигнальной информации для мультиплексирования со второго набора конденсаторов выборки/хранения, на которых сформирована сигнальная информация с предыдущей строки.

Данный подход позволяет снизить ток потребления ТИУ во время считывания и уменьшить время вывода сигнальной информации. Также для минимизации энергопотребления напряжение смещения ТИУ в строках матрицы входных ячеек варьируется в зависимости от стадии процесса считывания, в которой находится строка - сброс, или интегрирование, или считывание. Минимальный ток в ячейках строки протекает во время интегрирования, во время считывания и сброса рабочий ток подбрасывается.

Приведенный аналог не решает технической проблемы разработки устройства считывания сигналов с фотоприемной матрицы инфракрасного излучения, обеспечивающего снижение энергопотребления и повышение качества фотоэлектрических характеристик, поскольку у него имеются недостатки.

К недостаткам приведенного второго аналога относится высокое энергопотребление, неудовлетворительная линейность передаточной характеристики устройства считывания, неоднородность выходного сигнала.

Причины приведенных недостатков заключаются в следующем.

Минимизация энергопотребления достигнута не в полной мере. Во время считывания и сброса происходит подброс рабочего тока ТИУ. Кроме того, режим «конвейерного считывания», реализуемый устройством, обуславливает размытие изображения при экспонировании в условиях быстро меняющейся сцены, причем в течение всего времени кадра во всем массиве входных ячеек ТИУ остаются активными и рассеивают дополнительную мощность.

Использование в составе ТИУ схемотехнических решений с малым коэффициентом усиления по напряжению обеспечивает ухудшение линейности передаточной характеристики. Неоднородность выходного сигнала вызывает технологический разброс электрической емкости накопительного конденсатора и напряжений смещений ОУ в составе ТИУ.

В качестве ближайшего аналога выбрано устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения (Design of readout circuit for microcantilever infrared focal plane array with snapshot integration // Ke Lei, Zhongjian Chen, Junmin Cao, Yaciong Zhang, Wengao Lu, Lijiu Till Proc. SPIE 7383, International Symposium on Photoelectronic Detection and Imaging 2009: Advances in Infrared Imaging and Application, 73833L, 5 August 2009). Устройство реализовано для считывания информации с матриц ИК-микрокантилеверов с входной схемой на основе емкостного ТИУ. Устройство содержит входную ячейку, столбцовую шину, зарядочувствительный усилитель (ЗЧУ).

Входная ячейка выполнена в составе емкостного трансимпедансного усилителя (ТИУ), который образован операционным усилителем (ОУ) с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором и ключом сброса, ключа выборки/хранения, конденсатора выборки/хранения результата интегрирования, адресного ключа. Емкостной ТИУ выполнен с инвертирующим и неинвертирующим входами. Инвертирующий вход предназначен для соединения с кантилевером, а неинвертирующий вход - для подачи опорного напряжения. Выход ТИУ связан с одним концом ключа выборки/хранения, второй конец которого соединен с одним концом адресного ключа и одной обкладкой конденсатора выборки/хранения результата интегрирования, вторая обкладка которого закорочена на «землю». Второй конец адресного ключа соединен со столбцовой шиной. ЗЧУ образован вторым ОУ с конденсатором и столбцовым ключом сброса, параллельно включенным в цепь отрицательной обратной связи второго ОУ. ЗЧУ выполнен с инвертирующим и неинвертирующим входами. Столбцовая шина соединена с инвертирующим ЗЧУ, а неинвертирующий вход предназначен для подачи опорного напряжения.

Входная ячейка обеспечивает работу в режиме «Моментального снимка» в варианте «интегрирование, затем считывание» - ITR.

Устройство разработано для фотоприемников на основе ИК-микрокантилеверов формата 160×120 с шагом 50 мкм, выполнено на полупроводниковой подложке по технологии КМОП с проектной нормой 0,35 мкм.

Принцип работы устройства состоит в следующем. В начале кадра осуществляется сброс емкостей входной ячейки. В результате сброса происходит установка опорного напряжения на входе и выходе ТИУ, поданного на неинвертирующий вход. После сброса начинается процесс интегрирования фототока. ТИУ преобразует накопленный в течение времени интегрирования фотозаряд в напряжение. Во время интегрирования ключ выборки/хранения открыт, и конденсатор выборки/хранения результата интегрирования выполняет также функцию ограничения полосы пропускания ТИУ. После окончания акта интегрирования ключ выборки/хранения закрывается, запирая информационный сигнальный заряд на конденсаторе выборки/хранения результата интегрирования. Выходной сигнал входной ячейки обусловлен зарядом. При считывании информации с входной ячейки адресный ключ (транзистор) коммутирует выходной сигнал, обусловленный зарядом, хранящимся на конденсаторе выборки/хранения результата интегрирования, на столбцовую шину. Установленный на столбцовой шине ЗЧУ осуществляет преобразование его в напряжение. В крупноформатных устройствах считывания использование ЗЧУ на столбце позволяет избежать необходимости установки истокового повторителя на выходе ячейки, использующегося в целях перезарядки паразитной емкости столбцовой шины. При высоком коэффициенте усиления ОУ, образующего ЗЧУ, влияние паразитной емкости столбцовой шины пренебрежительно мало. ЗЧУ «удерживает» постоянное напряжение на шине в процессе считывания, препятствуя тем самым процессам перераспределения и передачи заряда. Для минимизации энергопотребления во время стадии считывания сигнальной информации ТИУ во всем массиве входных ячеек находятся в выключенном состоянии.

Ближайший аналог не решает технической проблемы разработки устройства считывания сигналов с фотоприемной матрицы инфракрасного излучения, обеспечивающего снижение энергопотребления и повышение качества фотоэлектрических характеристик, поскольку он обладает недостатками.

К недостаткам ближайшего аналога относится высокое энергопотребление, неудовлетворительная линейность передаточной характеристики устройства считывания, низкая зарядовая емкость входной ячейки, неоднородность выходного сигнала.

Причины приведенных недостатков заключаются в следующем.

Минимизация энергопотребления достигнута не в полной мере. В момент полноформатного сброса происходит перезарядка накопительного конденсатора и емкости сенсора во всем массиве ячеек фотоприемного устройства, что вызывает бросок тока в цепи питания.

Использование схемотехнических решений с малым коэффициентом усиления по напряжению в составе ТИУ обуславливает ухудшение линейности передаточной характеристики.

Конденсатор выборки/хранения результата интегрирования занимает значительную часть площади входной ячейки, не позволяя использовать по возможности максимум площади под расположение электрической схемы емкостного ТИУ с высоким коэффициентом усиления по напряжению, а также увеличивать величину зарядовой емкости.

Высокая неоднородность выходного сигнала (выходных напряжений со всех ячеек) связана с технологическим разбросом величин электрической емкости накопительного конденсатора и напряжений смещения ОУ в составе ТИУ.

Разработка предлагаемого устройства направлена на решение технической проблемы получения устройства считывания сигналов с фотоприемной матрицы инфракрасного излучения, обеспечивающего снижение энергопотребления и повышение качества фотоэлектрических характеристик.

Техническим результатом решения является:

- снижение энергопотребления;

- улучшение линейности передаточной характеристики устройства считывания;

- увеличение зарядовой емкости входной ячейки;

- улучшение однородности выходного сигнала.

Технический результат достигается в устройстве считывания сигналов с фотоприемной матрицы инфракрасного излучения, содержащем входную ячейку с емкостным трансимпедансным усилителем с инвертирующим и неинвертирующим входами, выполненным на основе операционного усилителя с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором, столбцовую шину, столбцовый зарядочувствительный усилитель со вторым операционным усилителем и включенным параллельно в цепь отрицательной обратной связи конденсатором, причем устройство содержит вторую столбцовую шину, при этом одна столбцовая шина реализована в виде сигнальной столбцовой шины, а вторая столбцовая шина реализована в виде опорной столбцовой шины, емкостной трансимпедансный усилитель выполнен также с входом включения, в составе входной ячейки также выполнены транзистор начала интегрирования, транзистор сброса, первый и второй адресные транзисторы, транзистор начала интегрирования соединен своим истоком с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя, и первой обкладкой накопительного конденсатора, своим стоком транзистор начала интегрирования соединен с катодом фотодиода, затвор транзистора начала интегрирования соединен с входом включения емкостного трансимпедансного усилителя, являющимся входом включения операционного усилителя, при этом указанные затвор и вход выполнены с возможностью подачи на них управляющего сигнала начала интегрирования, транзистор сброса своим стоком соединен с истоком транзистора начала интегрирования и первой обкладкой накопительного конденсатора, истоком транзистор сброса соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя, и второй обкладкой накопительного конденсатора, затвор транзистора сброса выполнен с возможностью подачи на него сигнала сброса входной ячейки, первый адресный транзистор своим стоком соединен с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя, первой обкладкой накопительного конденсатора, истоком транзистора начала интегрирования, стоком транзистора сброса, исток первого адресного транзистора соединен с сигнальной столбцовой шиной, затвор первого адресного транзистора соединен с затвором второго адресного транзистора, причем затворы первого и второго адресного транзисторов выполнены с возможностью подачи на них сигнала считывания, второй адресный транзистор своим стоком соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя, со второй обкладкой накопительного конденсатора, с истоком транзистора сброса, а исток второго адресного транзистора соединен с опорной столбцовой шиной, неинвертирующий вход емкостного трансимпедансного усилителя, являющийся неинвертирующим входом операционного усилителя, выполнен с возможностью подачи на него опорного напряжения, в составе столбцового зарядочувствительного усилителя выполнен второй транзистор сброса, при этом столбцовый зарядочувствительный усилитель выполнен с инвертирующим и неинвертирующим входами, являющимися, соответственно, инвертирующим и неинвертирующим входами второго операционного усилителя, неинвертирующий вход столбцового зарядочувствительного усилителя соединен с опорной столбцовой шиной, выполненной с возможностью подачи на нее опорного напряжения, инвертирующий вход столбцового зарядочувствительного усилителя соединен с первой обкладкой включенного параллельно в цепь отрицательной обратной связи конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, с сигнальной столбцовой шиной, со стоком второго транзистора сброса, исток второго транзистора сброса соединен со второй обкладкой включенного параллельно в цепь отрицательной обратной связи конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, с выходом столбцового зарядочувствительного усилителя, являющегося выходом второго операционного усилителя, а затвор второго транзистора сброса выполнен с возможностью подачи на него сигнала сброса столбцового зарядочувствительного усилителя.

Устройство считывания дополнительно содержит во входной ячейке конденсатор для ограничения полосы пропускания емкостного трансимпедансного усилителя, который соединен одной обкладкой с выходом емкостного трансимпедансного усилителя, являющегося выходом операционного усилителя, а вторая обкладка закорочена на «землю».

В устройстве считывания в емкостном трансимпедансном усилителе выполнены также вход подачи напряжения питания и общий вход, закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», операционного усилителя, в столбцовом зарядочувствительном усилителе выполнен также вход подачи напряжения питания и общий вход, закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», второго операционного усилителя.

Технический результат достигается в устройстве считывания сигналов с фотоприемной матрицы инфракрасного излучения, содержащем входную ячейку с емкостным трансимпедансным усилителем с инвертирующим и неинвертирующим входами, выполненным на основе операционного усилителя с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором, столбцовую шину, столбцовый зарядочувствительный усилитель, причем устройство содержит вторую столбцовую шину, при этом одна столбцовая шина реализована в виде инверсной столбцовой шины, а вторая столбцовая шина реализована в виде прямой столбцовой шины, емкостной трансимпедансный усилитель выполнен также с входом включения, в составе входной ячейки также выполнены транзистор начала интегрирования, транзистор сброса, первый и второй адресные транзисторы, транзистор начала интегрирования соединен своим истоком с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя, и первой обкладкой накопительного конденсатора, своим стоком транзистор начала интегрирования соединен с катодом фотодиода, затвор транзистора начала интегрирования соединен с входом включения емкостного трансимпедансного усилителя, являющимся входом включения операционного усилителя, при этом указанные затвор и вход выполнены с возможностью подачи на них управляющего сигнала начала интегрирования, транзистор сброса своим стоком соединен с истоком транзистора начала интегрирования и первой обкладкой накопительного конденсатора, истоком транзистор сброса соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя, и второй обкладкой накопительного конденсатора, затвор транзистора сброса выполнен с возможностью подачи на него сигнала сброса входной ячейки, первый адресный транзистор своим стоком соединен с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя, первой обкладкой накопительного конденсатора, истоком транзистора начала интегрирования, стоком транзистора сброса, исток первого адресного транзистора соединен с инверсной столбцовой шиной, затвор первого адресного транзистора соединен с затвором второго адресного транзистора, причем затворы первого и второго адресного транзисторов выполнены с возможностью подачи на них сигнала считывания, второй адресный транзистор своим стоком соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя, со второй обкладкой накопительного конденсатора, с истоком транзистора сброса, а исток второго адресного транзистора соединен с прямой столбцовой шиной, неинвертирующий вход емкостного трансимпедансного усилителя, являющийся неинвертирующим входом операционного усилителя, выполнен с возможностью подачи на него опорного напряжения, столбцовый зарядочувствительный усилитель выполнен полностью дифференциальным в составе конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, второго конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, второго и третьего транзисторов сброса и полностью дифференциального операционного усилителя с инвертирующим входом, являющимся инвертирующим входом столбцового зарядочувствительного усилителя, соединенным с инверсной столбцовой шиной, с неинвертирующим входом, являющимся неинвертирующим входом столбцового зарядочувствительного усилителя, соединенным с прямой столбцовой шиной, с инверсным и прямым выходами, являющимися, соответственно, инверсным и прямым выходами столбцового зарядочувствительного усилителя, при этом с инвертирующим входом полностью дифференциального операционного усилителя соединена первая обкладка конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и сток второго транзистора сброса, вторая обкладка конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и исток второго транзистора сброса соединены с прямым выходом полностью дифференциального операционного усилителя, являющегося прямым выходом столбцового зарядочувствительного усилителя, с неинвертирующим входом полностью дифференциального операционного усилителя соединена первая обкладка второго конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и сток третьего транзистора сброса, вторая обкладка второго конденсатора, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и исток третьего транзистора сброса соединены с инверсным выходом полностью дифференциального операционного усилителя, являющегося инверсным выходом столбцового зарядочувствительного усилителя, затворы второго и третьего транзисторов сброса выполнены соединенными друг с другом и с возможностью подачи на них управляющего сигнала сброса столбцового зарядочувствительного усилителя.

В устройстве считывания в емкостном трансимпедансном усилителе выполнены также вход подачи напряжения питания и общий вход, закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», операционного усилителя, в полностью дифференциальном столбцовом зарядочувствительном усилителе выполнен также вход подачи напряжения питания и общий вход, закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», полностью дифференциального операционного усилителя.

Сущность технического решения поясняется нижеследующим описанием и прилагаемыми фигурами.

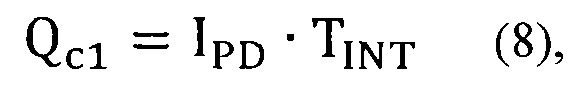

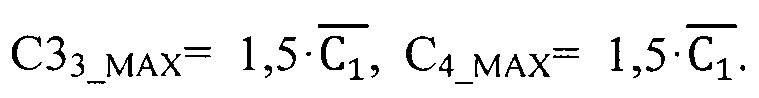

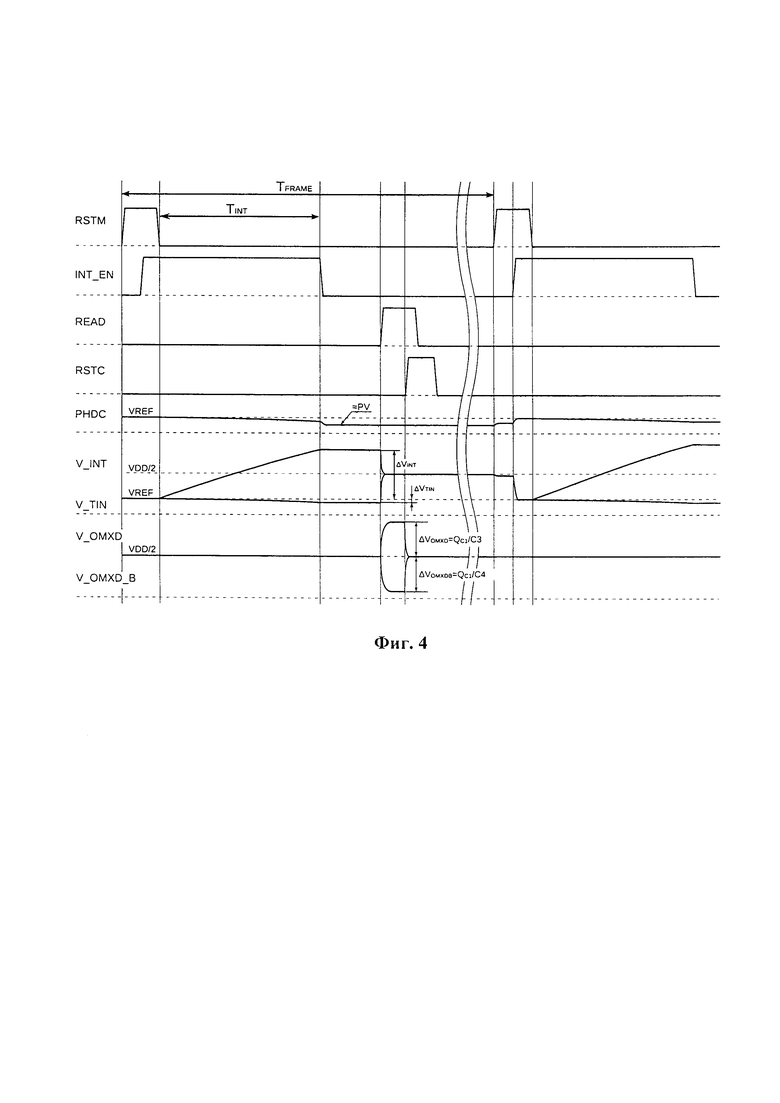

На Фиг. 1 показана электрическая принципиальная схема устройства считывания сигналов с фотоприемной матрицы инфракрасного (ИК) излучения в первом варианте выполнения с входной ячейкой, сигнальной столбцовой шиной, опорной шиной и зарядочувствительным усилителем, где: DA1 - операционный усилитель (ОУ); DA2 -операционный усилитель (ОУ); С1 - накопительный конденсатор; С2 - ограничивающий полосу пропускания трансимпедансного усилителя (ТИУ) конденсатор; С3 - линейный конденсатор с дискретным набором значений емкости; VD1 - фотодиод; VT1 - транзистор начала интегрирования; VT2 - транзистор сброса; VT3 - первый адресный транзистор; VT4 - второй адресный транзистор; VT5 - второй транзистор сброса; VDD - напряжение питания; GND - общая линия («земля»); RSTM - сигнал сброса входной ячейки; PHDC - напряжение на катоде фотодиода; RSTC - сигнал сброса столбцового зарядочувствительного усилителя (ЗЧУ); VREF - опорное напряжение; READ - сигнал считывания; INT_EN - сигнал начала интегрирования; V_OMX - напряжение на выходе столбцового зарядочувствительного усилителя (ЗЧУ).

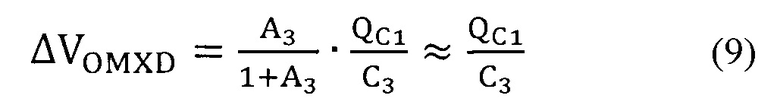

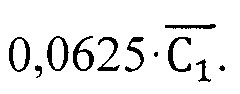

На Фиг. 2 показана электрическая принципиальная схема устройства считывания сигналов с фотоприемной матрицы инфракрасного (ИК) излучения во втором варианте выполнения с входной ячейкой, дифференциальными сигнальными столбцовыми шинами и полностью дифференциальным зарядочувствительным усилителем, где: DA1 - операционный усилитель (ОУ); DA3 - полностью дифференциальный операционный усилитель (ОУ); С1 - накопительный конденсатор; С3 - линейный конденсатор с дискретным набором значений емкости; С4 - линейный конденсатор с дискретным набором значений емкости; VD1 - фотодиод; VT1 - транзистор начала интегрирования; VT2 - транзистор сброса; VT3 - первый адресный транзистор; VT4 - второй адресный транзистор; VT5 - второй транзистор сброса; VT6 - третий транзистор сброса; VDD - напряжение питания; GND - общая линия («земля»); PHDC - напряжение на катоде фотодиода; RSTM - сигнал сброса входной ячейки; RSTC - сигнал сброса столбцового зарядочувствительного усилителя (ЗЧУ); VREF - опорное напряжение; READ - сигнал считывания; INT_EN - сигнал интегрирования; V_OMXD - напряжение на прямом выходе полностью дифференциального столбцового зарядочувствительного усилителя (ЗЧУ); V_OMXD_B - напряжение на инверсном выходе полностью дифференциального столбцового зарядочувствительного усилителя (ЗЧУ).

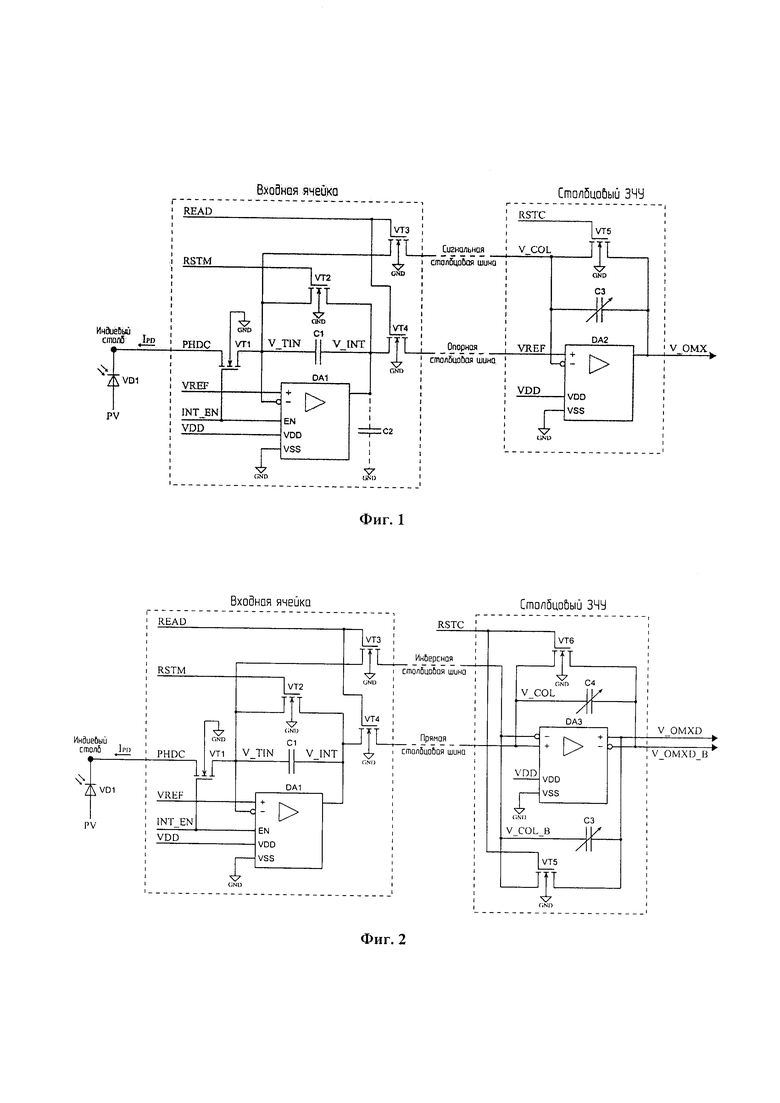

На Фиг. 3 показана временная диаграмма, отражающая работу устройства считывания сигналов с фотоприемной матрицы инфракрасного (ИК) излучения в первом варианте выполнения с входной ячейкой, сигнальной столбцовой шиной, опорной шиной и зарядочувствительным усилителем, где: TFRAME - время кадра; TINT - время интегрирования; RSTM - сигнал сброса входной ячейки; INT_EN - сигнал интегрирования; READ - сигнал считывания; RSTC - сигнал сброса столбцового зарядочувствительного усилителя (ЗЧУ); PHDC - напряжение на катоде фотодиода; V_INT - напряжение на выходе трансимпедансного усилителя (ТИУ); V_TIN - напряжение на входе трансимпедансного усилителя (ТИУ); V_OMX - напряжение на выходе столбцового зарядочувствительного усилителя (ЗЧУ); VREF - опорное напряжение; VDD - напряжение питания; QC1 - заряд, накопленный на накопительном конденсаторе С1 в течение времени интегрирования.

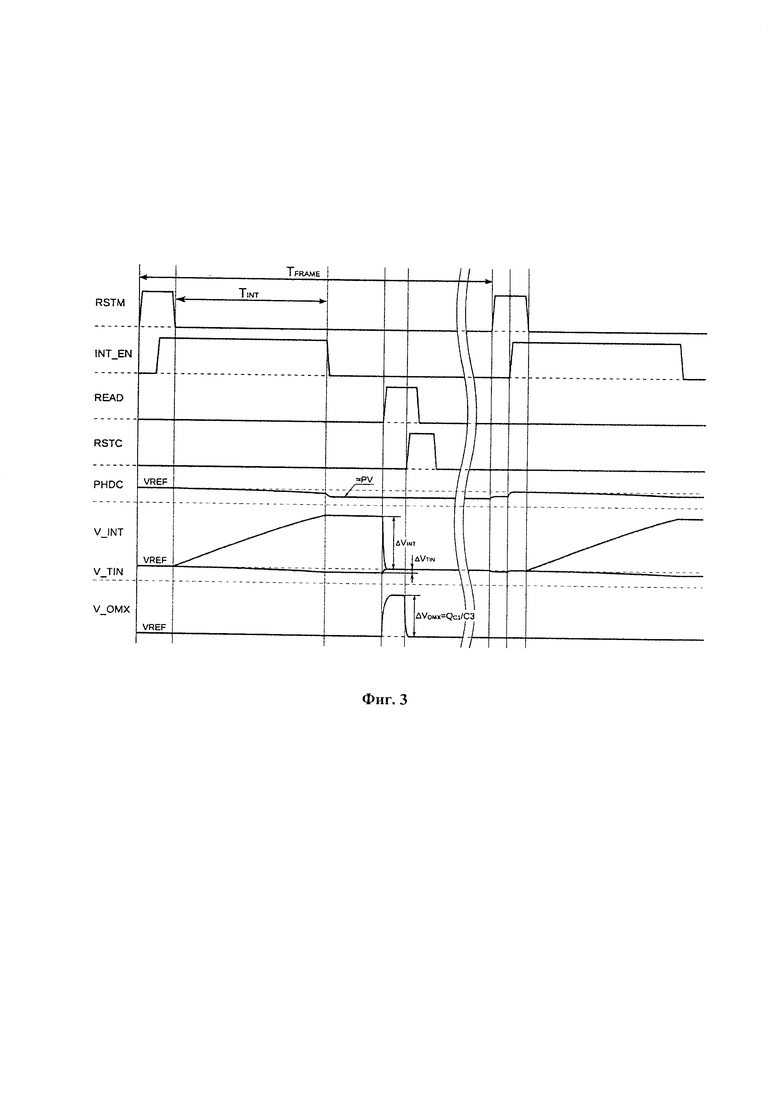

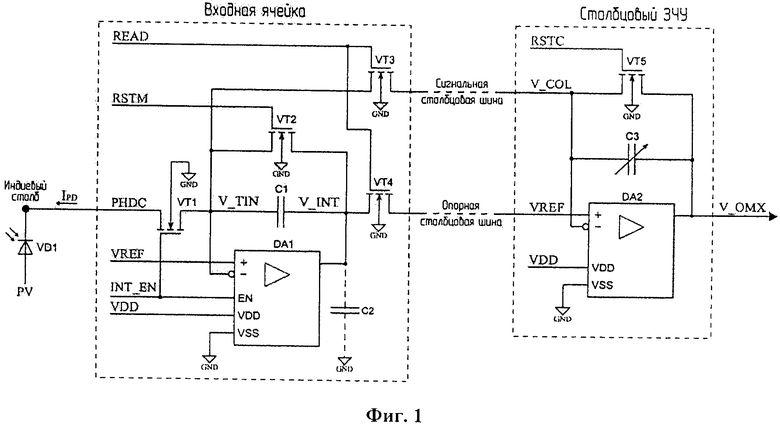

На Фиг. 4 показана временная диаграмма, отражающая работу устройства считывания сигналов с фотоприемной матрицы инфракрасного (ИК) излучения во втором варианте выполнения с входной ячейкой, дифференциальными сигнальными столбцовыми шинами и полностью дифференциальным зарядочувствительным усилителем, где: TFRAME - время кадра; TINT - время интегрирования; RSTM - сигнал сброса входной ячейки; INT_EN - сигнал интегрирования; READ - сигнал считывания; RSTC - сигнал сброса столбцового зарядочувствительного усилителя (ЗЧУ); PHDC - напряжение на катоде фотодиода; V_INT - напряжение на выходе трансимпедансного усилителя (ТИУ); V_OMXD - напряжение на прямом выходе полностью дифференциального столбцового зарядочувствительного усилителя (ЗЧУ); V_OMXD_B - напряжение на инверсном выходе полностью дифференциального столбцового зарядочувствительного усилителя (ЗЧУ); VREF - опорное напряжение; VDD- напряжение питания; QC1 - заряд, накопленный на накопительном конденсаторе С1 в течение времени интегрирования.

Главная функция устройства считывания - регистрация фотозарядов, являющихся информационными сигналами, возникающих в результате накопления фототоков в течение заданного времени интегрирования, со всех элементов фотоприемной матрицы и осуществление последующего последовательного вывода сформированных информационных сигналов. К основным узлам аналогового устройства считывания, обеспечивающим требуемое качество фотоэлектрических характеристик, относятся входная ячейка, столбцовый усилитель. В функцию входной ячейки входит накопление фототока в течение заданного времени интегрирования и осуществление стабилизации рабочей точки в отношении фоточувствительного элемента фотоприемной матрицы - фотодиода. Сформированный посредством входной ячейки в течение времени интегрирования электрический сигнал передается по шине передачи данных - столбцовой шине столбцовому усилителю, затем мультиплексируется на выходной усилитель.

Необходимость регистрации слабых потоков ИК-излучения при работе, в частности, в коротковолновом спектральном диапазоне требует интеграции емкостного ТИУ непосредственно во входную ячейку устройства считывания. Как правило, реализация емкостного ТИУ базируется на основе ОУ с накопительным конденсатором, включенным в цепь отрицательной обратной связи. Традиционно, как например, в вышеприведенных аналогах, характеристики используемого ОУ в емкостном ТИУ определяют энергопотребление, линейность передаточной характеристики устройства считывания и разброс уровня выходного напряжения (однородность).

Уменьшение шага входных ячеек сужает ряд пригодных схемотехнических решений ОУ в целях интеграции емкостного ТИУ во входную ячейку. Кроме того, уменьшение площади ячейки зачастую препятствует реализации необходимого требования по увеличению величины зарядовой емкости, определяемой электрической емкостью накопительного конденсатора и размахом выходного напряжения емкостного ТИУ. Для сохранения линейности преобразования емкостного ТИУ в цепь отрицательной обратной связи необходимо устанавливать конденсаторы, емкость которых не зависит от приложенного напряжения, что не позволяет использовать конденсаторы на основе МОП-структур, обладающие более высокой удельной емкостью.

Тенденция к увеличению числа фоточувствительных элементов (формата) матрицы накладывает повышенные требования к уровню энергопотребления входных ячеек на основе емкостного ТИУ. Кроме того, увеличение линейных размеров кристалла приводит к усилению влияния паразитных составляющих шин передачи данных.

С учетом вышесказанного в предлагаемых вариантах устройства считывания (см. Фиг. 1 и 2) достижение указанного технического результата обеспечивается конструкцией, которая позволяет осуществлять считывание заряда непосредственно с накопительного конденсатора С1, установленного в цепи обратной связи ТИУ, находящегося при считывании в отключенном состоянии.

Конструкция, как и в приведенных аналогах, выполнена на основе емкостного трансимпедансного усилителя и столбцового усилителя, являющегося, как и в ближайшем аналоге, зарядочувствительным. Емкостной ТИУ в составе входной ячейки выполняет функции стабилизации напряжения на фотодиоде, интегрирование фототока и преобразования накопленного фотозаряда в выходное напряжение. В приведенных первым и третьим (ближайшем) аналогах емкостной ТИУ перезаряжает конденсатор выборки/хранения результата интегрирования, с которого в дальнейшем осуществляет вывод сигнальной информации. В приведенном втором аналоге вывод сигнальной информации с входной ячейки (в виде напряжения) осуществляется непосредственно с выхода ТИУ. В предлагаемых вариантах технического решения считывание заряда осуществляется непосредственно с накопительного конденсатора С1 (см. Фиг. 1 и 2), установленного в цепи отрицательной обратной связи ТИУ. В период считывания ТИУ отключен. При таком подходе ТИУ выполняет функции стабилизации напряжения на фотодиоде и интегрирования фототока. Преобразование фотозаряда в напряжение происходит на столбцовом ЗЧУ. За счет нового распределения функций обеспечивается достижение технического результата.

В отношении линейности передаточной характеристики указанное распределение функций приводит к тому, что линейность передаточной характеристики устройства считывания определяется доминирующим образом не ОУ емкостного ТИУ, как было отмечено выше, а характеристиками столбцового ЗЧУ.

Достижение улучшения в линейности передаточной характеристики вариантов предлагаемого устройства достигается за счет снижения влияния коэффициента усиления ОУ в составе ТИУ на линейность преобразования. В отношении предлагаемых вариантов устройства считывания линейность главным образом определяется коэффициентом усиления ОУ, образующего столбцовый ЗЧУ. Реализация топологического размещения ОУ с высоким коэффициентом усиления, а также с линейным конденсатором в отрицательной обратной связи, в области под столбцом значительно проще, чем во входной ячейке. Как правило, под размещение столбцового ЗЧУ отводится область шириной, равной двум шагам ячеек, при этом длина указанной области не ограничена. Таким образом, ЗЧУ размещают с противоположных сторон матрицы входных ячеек, либо друг над другом.

Необходимо отметить, что амплитудная характеристика реальных ОУ содержит нелинейные участки, снижающие рабочий размах выходного напряжения ТИУ. Соответственно, вблизи данных областей начинается значительное отклонение от прямолинейной зависимости. В предлагаемых вариантах устройства считывание заряда осуществляется непосредственно с накопительного конденсатора, выполненного в цепи отрицательной обратной связи ТИУ. Поэтому входной диапазон значений может быть увеличен вплоть до перехода фотодиода в вольтаический режим (при условии высокого динамического сопротивления фотодиода).

Относительно достижения технического результата в части снижения энергопотребления отметим следующее. В предлагаемых вариантах устройства в отличие от приведенных первого и второго аналогов отсутствует процесс перезарядки паразитной емкости столбцовой шины в момент считывания. Кроме того, в отличие от приведенных первого и третьего аналогов, в которых в момент полноформатного сброса происходит перезарядка накопительного конденсатора и ограничивающего полосу пропускания ТИУ конденсатора во всем массиве входных ячеек, приводящая к броску тока в цепи питания, в предлагаемых вариантах устройства перезарядка накопительного конденсатора и ограничивающего полосу пропускания ТИУ конденсатора, если последний предусмотрен в схеме, осуществляется в момент считывания входной ячейки, тем самым снижая требования к линии и источнику питания.

Достижение технического результата в части увеличения зарядовой емкости входной ячейки обеспечивается за счет возможности использования в цепи отрицательной обратной связи емкостного ТИУ нелинейных конденсаторов, как правило, имеющих большую удельную емкость.

Технический результат в части улучшения однородности выходного сигнала достигается за счет нивелирования (сглаживания) влияния технологического разброса размера накопительного конденсатора, установленного в цепи отрицательной обратной связи емкостного ТИУ. Традиционно, как например, в вышеприведенных известных технических решениях, изменение напряжения на выходе ТИУ, являющееся выходным сигналом, обратно пропорционально величине накопительного конденсатора. В предлагаемых вариантах устройства считывания в приближении высокого коэффициента усиления накапливаемый и впоследствии считываемый сигнальный заряд определяется произведением значений фототока и времени интегрирования и не зависит от величины накопительного конденсатора. В связи с этим разброс величины накопительного конденсатора не приведет к разбросу наклона передаточной характеристики, хотя по-прежнему будет вносить вклад в разброс величины зарядовой емкости. Разброс напряжений смещения ОУ в составе емкостного ТИУ также не оказывает влияния в предлагаемых вариантах устройства, так как считывается с входной ячейки заряд, сбрасываемый до нуля вне зависимости от напряжения смещения ОУ.

Предлагаемое вариантами устройство считывания разработано для n-на-р HgCdTe фотоприемников коротковолнового и средневолнового ИК-диапазонов и выполнено на полупроводниковой подложке по КМОП технологии. В устройстве считывания имеется N×М входных ячеек (N, М≥1) - N строк матрицы, М столбцовых зарядочувствительных усилителей (М≥1) - М столбцов матрицы, М (М≥1) пар столбцовых шин - сигнальная и опорная столбцовые шины в случае устройства в реализации первым вариантом, инверсная и прямая солбцовые шины в случае устройства в реализации вторым вариантом (см. Фиг. 1 и 2). N входных ячеек приходится на один столбец - один столбцовый ЗЧУ. Входные ячейки, принадлежащие к одному и тому же столбцу, по очереди коммутируются на одну и ту же пару столбцовых шин.

На Фиг. 1 приведена электрическая принципиальная схема предлагаемого устройства считывания в соответствии с первым вариантом его выполнения.

Устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения содержит входную ячейку с емкостным трансимпедансным усилителем с инвертирующим и неинвертирующим входами, который образован операционным усилителем DA1 с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором С1, столбцовую шину, столбцовый зарядочувствительный усилитель со вторым операционным усилителем DA2 и включенным параллельно в цепь отрицательной обратной связи конденсатором.

Предлагаемое устройство считывания в соответствии с первым вариантом его выполнения в отличие от ближайшего аналога имеет следующие особенности.

Кроме упомянутой столбцовой шины устройство содержит вторую столбцовую шину. При этом одна столбцовая шина реализована в виде сигнальной столбцовой шины, а вторая столбцовая шина реализована в виде опорной столбцовой шины (см. Фиг. 1).

Входная ячейка с емкостным трансимпедансным усилителем, образованным операционным усилителем DA1 с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором С1, содержит также транзистор начала интегрирования VT1, транзистор сброса VT2, первый и второй адресные транзисторы, соответственно, VT3 и VT4 (см. Фиг. 1). Транзистор начала интегрирования VT1 обеспечивает запуск процесса интегрирования фототока и накапливание на накопительном конденсатора С1 заряда. Транзистор сброса VT2 обеспечивает сброс входной ячейки перед интегрированием. Первый и второй адресные транзисторы, соответственно, VT3 и VT4 необходимы для организации считывания накопленного заряда с накопительного конденсатора С1 столбцовым зарядочувствительным усилителем, через первый адресный транзистор VT3 происходит считывание, посредством второго адресного транзистора VT4 происходит закорачивание второй обкладки накопительного конденсатора С1 на столбцовую опорную шину.

Емкостной трансимпедансный усилитель выполнен с инвертирующим и неинвертирующим входами, с входом включения «EN», являющимися, соответственно, инвертирующим и неинвертирующим входами, входом включения операционного усилителя DA1. Неинвертирующий вход емкостного трансимпедансного усилителя, являющийся неинвертирующим входом операционного усилителя DA1, выполнен с возможностью подачи на него опорного напряжения «VREF». Кроме того, в емкостном трансимпедансном усилителе так же, как и в приведенных известных аналогах, выполнены вход подачи напряжения питания «VDD» и общий вход «VSS», закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», операционного усилителя DA1.

Транзистор начала интегрирования VT1 соединен своим истоком с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя DA1, первой обкладкой накопительного конденсатора С1, стоком транзистора сброса VT2, стоком первого адресного транзистора VT3. Стоком транзистор начала интегрирования VT1 соединен с катодом фотодиода VD1. Затвор транзистора начала интегрирования VT1 соединен с входом включения «EN» емкостного трансимпедансного усилителя, являющимся входом включения операционного усилителя DA1. При этом затвор транзистора начала интегрирования VT1 и вход включения «EN» выполнены с возможностью подачи на них управляющего сигнала начала интегрирования - «INT_EN». Транзистор сброса VT2 стоком соединен с истоком транзистора начала интегрирования VT1 и первой обкладкой накопительного конденсатора С1. Исток транзистор сброса VT2 соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя DA1, и второй обкладкой накопительного конденсатора С1. Затвор транзистора сброса VT2 выполнен с возможностью подачи на него сигнала сброса входной ячейки - «RSTM». Первый адресный транзистор VT3 своим стоком соединен с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя DA1, первой обкладкой накопительного конденсатора С1, истоком транзистора начала интегрирования VT1, стоком транзистора сброса VT2. Исток первого адресного транзистора VT3 соединен с сигнальной столбцовой шиной. Затвор первого адресного транзистора VT3 соединен с затвором второго адресного транзистора VT4. Причем затворы первого и второго адресного транзисторов, соответственно, VT3 и VT4 выполнены с возможностью подачи на них сигнала считывания «READ». Второй адресный транзистор VT4 своим стоком соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя DA1, со второй обкладкой накопительного конденсатора С1, с истоком транзистора сброса VT2. Исток второго адресного транзистора VT4 соединен с опорной столбцовой шиной.

Во входной ячейке может быть выполнен конденсатор С2 для ограничения полосы пропускания емкостного трансимпедансного усилителя. Конденсатор С2 соединен одной обкладкой с выходом емкостного трансимпедансного усилителя, являющегося выходом операционного усилителя DA1. Вторая обкладка конденсатора С2 закорочена на «землю». Назначение указанного дополнительного конденсатора С2 - снижение уровня шума при работе устройства считывания. Данный конденсатор препятствует заметному увеличению вклада теплового шума емкостного ТИУ в общий шум устройства считывания при повышении рабочих температур, в частности, более 150 К. Это способствует увеличению отношения сигнал/шум фотоприемного устройства.

Столбцовый зарядочувствительный усилитель со вторым операционным усилителем DA2 и включенным параллельно в цепь отрицательной обратной связи конденсатором С3 дополнительно содержит второй транзистор сброса VT5 (см. Фиг. 1).

Столбцовый зарядочувствительный усилитель выполнен с инвертирующим и неинвертирующим входами, являющимися, соответственно, инвертирующим и неинвертирующим входами второго операционного усилителя DA2. Кроме того, в столбцовом зарядочувствительном усилителе так же, как и в приведенных известных аналогах, выполнены вход подачи напряжения питания «VDD» и общий вход «VSS», закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», второго операционного усилителя DA2. Неинвертирующий вход столбцового зарядочувствительного усилителя соединен с опорной столбцовой шиной, выполненной с возможностью подачи на нее опорного напряжения «VREF». Инвертирующий вход столбцового зарядочувствительного усилителя соединен с первой обкладкой включенного параллельно в цепь отрицательной обратной связи конденсатора С3, с сигнальной столбцовой шиной, со стоком второго транзистора сброса VT5.

Второй транзистора сброса VT5 обеспечивает сброс столбцового ЗЧУ перед считыванием заряда с накопительного конденсатора С1. Исток второго транзистора сброса VT5 соединен со второй обкладкой включенного параллельно в цепь отрицательной обратной связи конденсатора С3, с выходом столбцового зарядочувствительного усилителя, являющегося выходом второго операционного усилителя DA2. Затвор второго транзистора сброса VT5 выполнен с возможностью подачи на него сигнала сброса «RSTC» столбцового зарядочувствительного усилителя.

Конденсатор С3 выполнен в виде линейного конденсатора с дискретным набором значений емкости. Назначение данного конденсатора С3 обеспечить возможность максимального размаха выходного напряжения столбцового ЗЧУ при любой степени заполнения накопительного конденсатора С1, исходя из его дискретного набора значений емкости.

Транзистор начала интегрирования VT1, транзистор сброса VT2, первый адресный транзистор VT3, второй адресный транзистор VT4, второй транзистор сброса VT5 - полевые транзисторы, выполненные n-МОП-транзисторами. Подложки указанных транзисторов закорочены на «землю».

Функционирование устройства считывания, реализованного первым вариантом его выполнения, с достижением указанного технического результата поясняется с помощью временных диаграмм (см. Фиг. 3), иллюстрирующих качественное изменение управляющих и результирующих потенциалов на элементах устройства считывания (см. Фиг. 1).

Время кадра «TFRAME» складывается из времени интегрирования «TINT» и времени, затрачиваемого на считывание сигнальной информации с массива входных ячеек. В начале кадра по сигналу «RSTM», подаваемому на затвор транзистора сброса VT2, осуществляют сброс каждой из входных ячеек в массиве, которых как указано выше, в нем N×М (N≥1, М≥1). В течение импульса «RSTM», с запаздыванием относительно момента подачи последнего, начинают подавать импульс «INT_EN», которым осуществляют включение емкостного трансимпедансного усилителя и открывают транзистор начала интегрирования VT1. В результате сброса входной ячейки происходит перезарядка емкости фотодиода и балансировка напряжения на инвертирующем входе и выходе емкостного трансимпедансного усилителя вблизи уровня опорного напряжения «VREF» в результате влияния напряжения смещения DA1. Процесс интегрирования фототока IPD начинается с прекращением подачи импульса «RSTM» и длится до окончания подачи импульса «INT_EN».

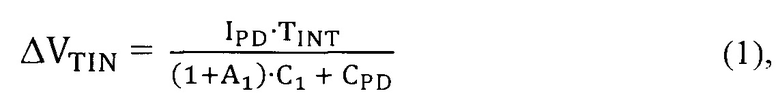

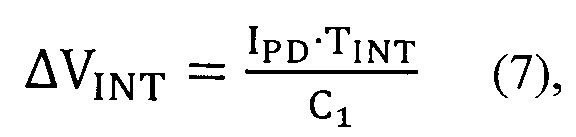

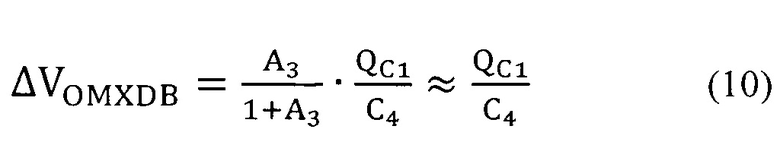

Изменение напряжения на инвертирующем входе емкостного трансимпедансного усилителя за время интегрирования определяется выражением

где: IPD - ток фотодиода VD1;

TINT - время интегрирования;

А1 - коэффициент усиления ОУ DA1 по напряжению;

С1 - емкость накопительного конденсатора С1;

CPD - емкость фотодиода VD1.

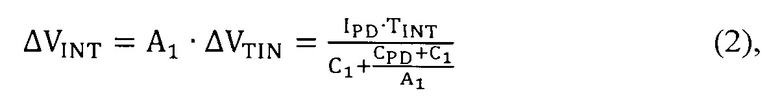

Соответственно изменение напряжения на выходе емкостного трансимпедансного усилителя за время интегрирования равно

где: А1 - коэффициент усиления ОУ DA1 по напряжению;

ΔVINT - изменение напряжения на инверсном входе емкостного ТИУ;

IPD - ток фотодиода VD1;

TINT - время интегрирования;

С1 - емкость накопительного конденсатора С1;

CPD - емкость фотодиода VD1.

Заряд, накопленный конденсатором С1 за время интегрирования задается выражением

где: A1 - коэффициент усиления ОУ DA1 по напряжению;

C1 - емкость накопительного конденсатора С1;

ΔVINT - изменение напряжения на инверсном входе емкостного ТИУ;

IPD - ток фотодиода VD1;

TINT - время интегрирования;

CPD - емкость фотодиода VD1.

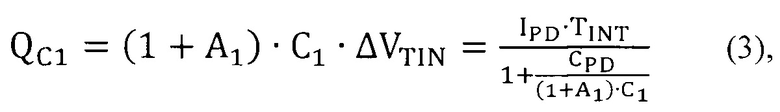

Выражения (1)-(3) справедливы в предположении высокого динамического сопротивления фотодиода RPD, при котором можно пренебречь снижением эффективности инжекции фототока в процессе интегрирования (Wei Zhang, SongLei Huang, ZhangCheng Huang, Jiaxpong Fang, Analysis and design of a low-noise ROIC for hybrid InGaAs infrared FPA // Proc. SPIE 8193, International Symposium on Photoelectronic Detection and Imaging 2011: Advances in Infrared Imaging and Applications, 81933Q, 8 September 2011). В этом приближении динамическое сопротивление фотодиода RPD должно удовлетворять условию

где: TINT - время интегрирования;

A1 - коэффициент усиления ОУ DA1 по напряжению;

С1 - емкость накопительного конденсатора С1;

CPD - емкость фотодиода VD1.

Даже при малом коэффициенте усиления ОУ DA1 по напряжению А1=25 и значениях времени интегрирования TINT=30 мс, емкости конденсатора С1 С1=150 фФ, емкости фотодиода VD1 CPD=30 фФ из выражения (4) следует необходимое условие RPD>>1010 Ом, что легко реализуется в фотодиодах на основе твердого раствора теллурида кадмия и ртути для коротковолнового и средневолнового ИК-диапазонов.

Стабилизация рабочей точки «PHDC» обеспечивается за счет возникающего в емкостном трансимпедансном усилителе эффекта Миллера, в результате которого происходит увеличение эффективной входной емкости пропорционально величине накопительного конденсатора С1 и коэффициента усиления ОУ DA1 по напряжению.

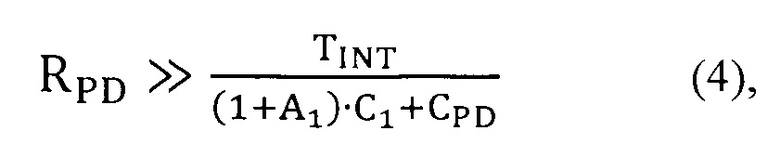

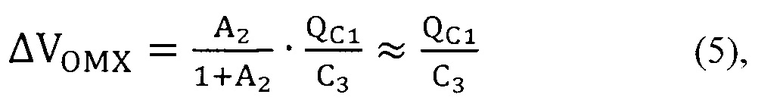

Подачей импульса считывания «READ» открывают первый и второй адресные транзисторы, соответственно, VT3 и VT4. Операционный усилитель DA1 к моменту подачи сигнала считывания «READ» находится уже в выключенном состоянии. Вторая обкладка накопительного конденсатора С1 (а также обкладка конденсатора С2 для ограничения полосы пропускания емкостного трансимпедансного усилителя, если устройство считывания снабжено им) закорачивается на опорную столбцовую шину через второй адресный транзистор VT4 (при наличии в устройстве конденсатора С2 для ограничения полосы пропускания емкостного трансимпедансного усилителя происходит перезарядка С2 до опорного напряжения «VREF»). Столбцовый зарядочувствительный усилитель через первый адресный транзистор VT3 считывает накопленный сигнальный заряд с накопительного конденсатора С1. Изменение напряжения на выходе столбцового зарядочувствительного усилителя определяется выражением

где: А2 - коэффициент усиления ОУ DA2 по напряжению;

QC1 - заряд накопительного конденсатора С1 за время интегрирования;

С3 - емкость линейного конденсатора с дискретным набором значений емкости.

При А2>>1 разностью потенциалов между обкладками накопительного конденсатора С1 после считывания можно пренебречь. Таким образом, во время сброса входной ячейки по сигналу «RSTM» перезарядка накопительного конденсатора С1 (а также конденсатора С2 для ограничения полосы пропускания емкостного трансимпедансного усилителя, если устройство считывания снабжено им) отсутствует. Также при высоких значениях коэффициента усиления ОУ DA2 по напряжению А2 отсутствуют процессы перераспределения и передачи заряда по сигнальной столбцовой шине.

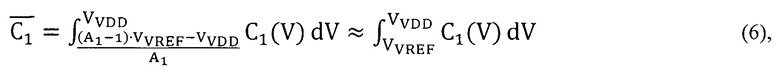

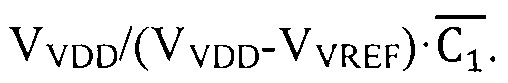

Поскольку учитывается, что накопительный конденсатор С1, в частности, может быть нелинейным, определим среднюю величину его электрической емкости в рабочем диапазоне  Полагая, что выходное напряжение ОУ DA1 достигает напряжения питания «VDD» и напряжение смещение ОУ DA1 равно нулю, средняя величина электрической емкости накопительного конденсатора С1 в рабочем диапазоне определяется

Полагая, что выходное напряжение ОУ DA1 достигает напряжения питания «VDD» и напряжение смещение ОУ DA1 равно нулю, средняя величина электрической емкости накопительного конденсатора С1 в рабочем диапазоне определяется

где: VVDD - величина напряжения питания;

А1 - коэффициент усиления ОУ DA1 по напряжению;

VVREF - величина опорного напряжения;

C1 - емкость накопительного конденсатора С1.

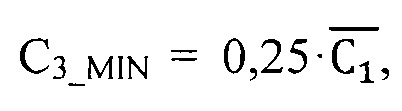

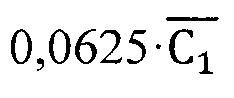

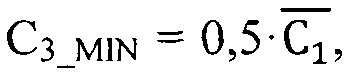

Конденсатор С3 реализован, например, таким образом, что его электрическая емкость  а

а  причем в промежутке указанных значений емкость конденсатора С3 принимает значения с дискретностью

причем в промежутке указанных значений емкость конденсатора С3 принимает значения с дискретностью  (шестнадцать значений емкости). Подбирая величину емкости линейного конденсатора с дискретным набором значений емкости С3 из заданного дискретного набора значений, можно добиться максимального размаха выходного напряжения столбцового зарядочувствительного усилителя ΔVOMX даже при малом коэффициенте заполнения накопительного конденсатора С1, в данном случае величина емкости линейного конденсатора с дискретным набором значений

(шестнадцать значений емкости). Подбирая величину емкости линейного конденсатора с дискретным набором значений емкости С3 из заданного дискретного набора значений, можно добиться максимального размаха выходного напряжения столбцового зарядочувствительного усилителя ΔVOMX даже при малом коэффициенте заполнения накопительного конденсатора С1, в данном случае величина емкости линейного конденсатора с дискретным набором значений  В предлагаемом устройстве считывания линейность передаточной характеристики в значительной степени определяется характеристиками операционного усилителя DA2. При использовании в качестве его операционного усилителя с полнодиапазонным размахом выходного сигнала и высоким коэффициентом усиления (А2>1000) отсутствуют заметные искажения сигнала даже вблизи линий питания. В этом случае величина емкости линейного конденсатора с дискретным набором значений емкости С3 равна величине

В предлагаемом устройстве считывания линейность передаточной характеристики в значительной степени определяется характеристиками операционного усилителя DA2. При использовании в качестве его операционного усилителя с полнодиапазонным размахом выходного сигнала и высоким коэффициентом усиления (А2>1000) отсутствуют заметные искажения сигнала даже вблизи линий питания. В этом случае величина емкости линейного конденсатора с дискретным набором значений емкости С3 равна величине  емкости накопительного конденсатора С1.

емкости накопительного конденсатора С1.

Сброс столбцового зарядочувствительного усилителя осуществляют подачей сигнала «RSTC» к затвору второго транзистора сброса VT5. Начало подачи импульса «RSTC» может быть во время импульса «READ». Однако данное условие является необязательным.

Относительно достижения технического результата в части линейности передаточной характеристики отметим следующее.

В известных устройствах считывания с входной ячейкой на основе емкостного трансимпедансного усилителя - приведенных аналогах - напряжение, описанное уравнением (2), принимается за основу для дальнейшего считывания информации. Так, в устройстве, указанном в качестве первого аналога (Very wide dynamic range SWIR sensors for very low background applications / Roberts F. Cannata, Randal J. Hansen, Adrienne N. Costello, William J. Parrish // Proc. SPIE 3698, Infrared Technology and Application XXV, July 1999), данное напряжение, дополнительно искажаясь, выводится с помощью истокового повторителя. В устройстве, указанном в качестве ближайшего аналога (Design of readout circuit for microcantilever infrared focal plane array with snapshot integration / Ke Lei, Zhongjian Chen, Junmin Cao, Yaciong Zhang, Wengao Lu, Lijiu Ji // Proc. SPIE 7383, International Symposium on Photoelectronic Detection and Imaging 2009: Advances in Infrared Imaging and Application, 73833L, 5 August 2009), данное напряжение сохраняется на конденсаторе выборки/хранения результата интегрирования, затем считывается в виде заряда. В предлагаемом устройстве преобразование накопленного на накопительном конденсаторе С1 фотозаряда в напряжение происходит на столбцовом зарядочувствительном усилителе.

Амплитудная характеристика реального ОУ отклоняется от прямолинейной, вблизи области насыщения наблюдается существенное снижение коэффициента усиления. Нелинейные искажения ОУ в составе емкостного ТИУ приводят к снижению линейного динамического диапазона устройства считывания. Из анализа уравнений (2) и (3) ясно видно, что в предлагаемом устройстве снижение коэффициента усиления вносит значительно меньшие нелинейные искажения в передаточную характеристику устройства считывания.

При условии A1>>CPD/C1 уравнения (2) и (3) упрощаются, соответственно, до

где: C1 - емкость накопительного конденсатора С1;

TINT - время интегрирования;

IPD - ток фотодиода VD1.

Таким образом, если электрическая емкость накопительного конденсатора С1 зависит от приложенного напряжения, то напряжение на выходе емкостного трансимпедансного усилителя в процессе интегрирования также будет отклоняться от прямолинейной зависимости. Предполагая отсутствие влияния малых изменений напряжения смещения на фотодиоде VD1 на величину фототока, из выражения (8) можно заключить, что при значениях A1>>CPD/C1 имеет место линейный процесс накопления заряда при интегрировании вне зависимости от линейности емкости накопительного конденсатора С1.

Относительно достижения превосходства в части однородности выходного сигнала при технологическом разбросе электрической емкости накопительного конденсатора С1 правомерны аналогичные рассуждения.

В известных устройствах считывания, приведенных при описании уровня техники, разброс емкости накопительного конденсатора С1 приведет к разбросу наклона передаточной характеристики согласно уравнению (7). В предлагаемом устройстве считывания разброс емкости накопительного конденсатора С1 в соответствии с уравнением (8) не оказывает никакого влияния относительно наклона передаточной характеристики, хотя и вносит разброс в величину зарядовой емкости входной ячейки и, соответственно, в максимальное время интегрирования. Данный разброс будет проявляться лишь в области насыщения входных ячеек.

Также известно, что к разбросу уровня выходного сигнала приводит разброс напряжений смещения операционного усилителя емкостного ТИУ (Dong Yang, Hang-yu Zhou, Jian Wang, Design of a low noise and high accuracy readout integrated circuit for infrared detectors // Proc. SPIE 8193, International Symposium on Photoelectronic Detection and Imaging 2011: Advances in Infrared Imaging and Applications, 81932H, 8 September 2011; Wei Zhang, SongLei Huang, ZhangCheng Huang, Jiaxpong Fang, Analysis and design of a low-noise ROIC for hybrid InGaAs infrared FPA // Proc. SPIE 8193, International Symposium on Photoelectronic Detection and Imaging 2011: Advances in Infrared Imaging and Applications, 81933Q, 8 September 2011). В предлагаемом техническом решении выходным сигналом входной ячейки является заряд, сбрасываемый до нуля перед актом интегрирования вне зависимости от напряжения смещения операционного усилителя DA1. Напряжение на выходе устройства считывания, соответствующее «нулевой» засветке фотоприемного устройства, будет варьироваться лишь от столбца к столбцу, межстрочная вариация будет отсутствовать. Разброс будет определяться характеристиками операционного усилителя DA2 столбцового зарядочувствительного усилителя.

На Фиг. 2 приведена электрическая принципиальная схема предлагаемого устройства считывания в соответствии со вторым вариантом его выполнения.

Устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения содержит входную ячейку с емкостным трансимпедансным усилителем с инвертирующим и неинвертирующим входами, который образован операционным усилителем DA1 с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором С1, столбцовую шину, столбцовый зарядочувствительный усилитель.

Предлагаемое устройство считывания в соответствии со вторым вариантом его выполнения в отличие от ближайшего аналога имеет следующие особенности.

Устройство содержит помимо упомянутой столбцовой шины вторую столбцовую шину. При этом одна столбцовая шина реализована в виде инверсной столбцовой шины, а вторая столбцовая шина реализована в виде прямой столбцовой шины (см. Фиг. 2).

Входная ячейка с емкостным трансимпедансным усилителем, образованным операционным усилителем DA1 с включенным параллельно в цепь отрицательной обратной связи накопительным конденсатором С1, содержит также транзистор начала интегрирования VT1, транзистор сброса VT2, первый и второй адресные транзисторы, соответственно, VT3 и VT4 (см. Фиг. 2). Аналогично первому варианту предлагаемого устройства указанные элементы выполняют следующие функции.

Транзистор начала интегрирования VT1 обеспечивает запуск процесса интегрирования фототока и накапливание на накопительном конденсаторе С1 заряда. Транзистор сброса VT2 обеспечивает сброс входной ячейки перед интегрированием. Первый и второй адресные транзисторы, соответственно, VT3 и VT4 необходимы для организации считывания накопленного заряда с накопительного конденсатора С1 столбцовым зарядочувствительным усилителем, через первый адресный транзистор VT3 происходит считывание столбцовым зарядочувствительным усилителем за счет соединения первого адресного транзистора VT3 со столбцовой инверсной шиной, соединенной с инвертирующим входом ЗЧУ, посредством второго адресного транзистора VT4 происходит закорачивание второй обкладки накопительного конденсатора С1 на столбцовую прямую шину.

Емкостной трансимпедансный усилитель выполнен с инвертирующим и неинвертирующим входами, с входом включения «EN», являющимися, соответственно, инвертирующим и неинвертирующим входами, входом включения операционного усилителя DA1. Неинвертирующий вход емкостного трансимпедансного усилителя, являющийся неинвертирующим входом операционного усилителя DA1, выполнен с возможностью подачи на него опорного напряжения «VREF». В емкостном трансимпедансном усилителе так же, как и в приведенных известных аналогах, выполнены вход подачи напряжения питания «VDD» и общий вход «VSS», закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», операционного усилителя DA1.

Транзистор начала интегрирования VT1 соединен своим истоком с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя DA1, первой обкладкой накопительного конденсатора С1, стоком транзистора сброса VT2, стоком первого адресного транзистора VT3. Стоком транзистор начала интегрирования VT1 соединен с катодом фотодиода VD1. Затвор транзистора начала интегрирования VT1 соединен с входом включения «EN» емкостного трансимпедансного усилителя, являющимся входом включения операционного усилителя DA1. При этом затвор транзистора начала интегрирования VT1 и вход включения «EN» выполнены с возможностью подачи на них управляющего сигнала начала интегрирования - «INT_EN». Транзистор сброса VT2 стоком соединен с истоком транзистора начала интегрирования VT1 и первой обкладкой накопительного конденсатора С1. Исток транзистор сброса VT2 соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя DA1, и второй обкладкой накопительного конденсатора С1. Затвор транзистора сброса VT2 выполнен с возможностью подачи на него сигнала сброса входной ячейки - «RSTM». Первый адресный транзистор VT3 своим стоком соединен с инвертирующим входом емкостного трансимпедансного усилителя, являющимся инвертирующим входом операционного усилителя DA1, первой обкладкой накопительного конденсатора С1, истоком транзистора начала интегрирования VT1, стоком транзистора сброса VT2. Исток первого адресного транзистора VT3 соединен с инверсной столбцовой шиной. Затвор первого адресного транзистора VT3 соединен с затвором второго адресного транзистора VT4. Причем затворы первого и второго адресного транзисторов, соответственно, VT3 и VT4 выполнены с возможностью подачи на них сигнала считывания «READ». Второй адресный транзистор VT4 своим стоком соединен с выходом емкостного трансимпедансного усилителя, являющимся выходом операционного усилителя DA1, со второй обкладкой накопительного конденсатора С1, с истоком транзистора сброса VT2. Исток второго адресного транзистора VT4 соединен с прямой столбцовой шиной (см. Фиг. 2).

Столбцовый зарядочувствительный усилитель выполнен полностью дифференциальным (см. Фиг. 2). В его состав входят конденсатор С3 и второй конденсатор С4, которые выполнены в виде линейных конденсаторов с дискретным набором значений емкости.

Также в состав столбцового зарядочувствительного усилителя входят второй и третий транзисторы сброса, соответственно, VT5 и VT6, полностью дифференциальный операционный усилитель DA3.

Полностью дифференциальный операционный усилитель DA3 выполнен с инвертирующим входом, являющимся инвертирующим входом столбцового зарядочувствительного усилителя, соединенным с инверсной столбцовой шиной, с неинвертирующим входом, являющимся неинвертирующим входом столбцового зарядочувствительного усилителя, соединенным с прямой столбцовой шиной, с инверсным и прямым выходами, являющимися, соответственно, инверсным и прямым выходами столбцового зарядочувствительного усилителя. В полностью дифференциальном столбцовом зарядочувствительном усилителе выполнен также вход подачи напряжения питания «VDD» и общий вход «VSS», закороченный на «землю», являющиеся, соответственно, входом подачи напряжения питания и общим входом, закороченным на «землю», полностью дифференциального операционного усилителя DA3, наличие которых для ОУ является общеизвестным.

С инвертирующим входом полностью дифференциального операционного усилителя DA3 соединена первая обкладка конденсатора С3, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и сток второго транзистора сброса VT5. Вторая обкладка конденсатора С3, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и исток второго транзистора сброса VT5 соединены с прямым выходом полностью дифференциального операционного усилителя DA3, являющегося прямым выходом столбцового зарядочувствительного усилителя. С неинвертирующим входом полностью дифференциального операционного усилителя DA3 соединена первая обкладка второго конденсатора С4, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и сток третьего транзистора сброса VT6. Вторая обкладка второго конденсатора С4, выполненного в виде линейного конденсатора с дискретным набором значений емкости, и исток третьего транзистора сброса VT6 соединены с инверсным выходом полностью дифференциального операционного усилителя DA3, являющегося инверсным выходом столбцового зарядочувствительного усилителя. Затворы второго и третьего транзисторов сброса, соответственно, VT5 и VT6 выполнены соединенными друг с другом и с возможностью подачи на них управляющего сигнала сброса столбцового зарядочувствительного усилителя «RSTC».

Назначение конденсаторов С3 и С4 обеспечить возможность максимального размаха выходного напряжения столбцового ЗЧУ при любой степени заполнения накопительного конденсатора С1, исходя их дискретных наборов значений. Назначение второго и третьего транзисторов сброса, соответственно, VT5 и VT6 обеспечить сброс полностью дифференциального столбцового зарядочувствительного усилителя.

Транзистор начала интегрирования VT1, транзистор сброса VT2, первый адресный транзистор VT3, второй адресный транзистор VT4, второй транзистор сброса VT5, третий транзистор сброса VT6 - полевые транзисторы, выполненные n-МОП-транзисторами. Подложки указанных транзисторов закорочены на «землю».

Функционирование устройства считывания, реализованного вторым вариантом его выполнения, с достижением указанного технического результата поясняется с помощью временных диаграмм (см. Фиг. 4), иллюстрирующих качественное изменение управляющих и результирующих потенциалов на элементах устройства считывания (см. Фиг. 2).

Так же, как и при функционировании устройства по первому варианту реализации, время кадра «TFRAME» складывается из времени интегрирования «TINT» и времени, затрачиваемого на считывание сигнальной информации с массива входных ячеек. В начале кадра по сигналу «RSTM», подаваемому на затвор транзистора сброса VT2, осуществляют сброс массива входных ячеек. После подачи, в течение импульса «RSTM» начинают подавать импульс «INT_EN», чем осуществляют включение емкостного трансимпедансного усилителя и открывают транзистор начала интегрирования VT1. В результате сброса входной ячейки происходит перезарядка емкости фотодиода и балансировка напряжения на инверсном входе и выходе емкостного трансимпедансного усилителя вблизи уровня опорного напряжения «VREF» в результате влияния напряжения смещения DA1. Процесс интегрирования фототока IPD начинается с прекращением подачи импульса «RSTM» и длится до окончания подачи импульса «INT_EN».

Изменение напряжения на инверсном входе емкостного трансимпедансного усилителя за время интегрирования определяется также выражением (1), как и при функционировании устройства по первому варианту реализации.

Также, соответственно изменение напряжения на выходе емкостного трансимпедансного усилителя за время интегрирования при функционировании устройства при его реализации по второму варианту определяется выражением (2).

Заряд, накопленный накопительным конденсатором С1 за время интегрирования, задается вышеприведенным выражением (3).

По сигналу считывания «READ» полностью дифференциальный столбцовый зарядочувствительный усилитель через открывшиеся первый и второй адресные транзисторы, соответственно, VT3 и VT4 осуществляет считывание сигнального заряда, накопленного накопительным конденсатором С1 за время интегрирования, задаваемого вышеприведенным выражением (3), по дифференциальным столбцовым шинам - инверсной и прямой столбцовым шинам. При считывании операционный усилитель DA1, как и при функционировании устройства по первому варианту реализации, находится в выключенном состоянии. Изменение напряжений на дифференциальных выходах операционного усилителя DA3 - прямом и инверсном выходах, соответственно, «V_OMXD» и «V_OMXD_B» (см. Фиг. 2) определяются выражениями

где: A3 - коэффициент усиления ОУ DA3 по напряжению;

QC1 - заряд накопительного конденсатора С1 за время интегрирования;

С3 - емкость линейного конденсатора с дискретным набором значений емкости;

С4 - емкость второго линейного конденсатора с дискретным набором значений емкости.

Выходным сигналом устройства считывания, реализованного вторым вариантом, является дифференциальное напряжение ΔVOMXD+ΔVOMXDB, пропорциональное интенсивности излучения, падающего на фотодиод в течение времени интегрирования TINT.

Напряжение на дифференциальных столбцовых шинах - инверсной и прямой столбцовых шинах - удерживается вблизи значения, равного половине значения напряжения питания «VDD». Во время импульса сброса входных ячеек «RSTM» первый и второй адресные транзисторы, соответственно, VT3 и VT4 будут закрыты. Следовательно, до момента включения операционного усилителя DA1 состояние на обкладках накопительного конденсатора С1 соответствует высокоимпедансному состоянию. При включении операционного усилителя DA1 по сигналу «INT_EN» на обкладках накопительного конденсатора С1 установится напряжение по значению близкое к опорному напряжению «VREF». При А3>>1 после считывания заряда разность потенциалов между обкладками накопительного конденсатора С1 можно считать равной нулю. В связи, с чем процесс перезарядки накопительного конденсатора С1 в момент сброса входной ячейки отсутствует.

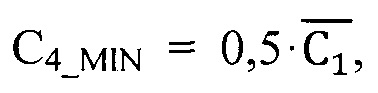

Емкости конденсатора С3 и второго конденсатора С4, которые выполнены в виде линейных конденсаторов с дискретным набором значений емкости, должны быть равны. Величина их емкости выбирается из заданного дискретного набора значений емкости.

В предлагаемом устройстве считывания по второму варианту линейность передаточной характеристики в значительной степени определяется характеристиками операционного усилителя DA3. При использовании в качестве его операционного усилителя с полнодиапазонным размахом выходного сигнала (от 0 до VDD) и высоким коэффициентом усиления (A3>1000) отсутствуют заметные искажения сигнала даже вблизи линий питания. Выходное напряжение DA1 изменяется в диапазоне от «VREF» до «VDD», подбирая величины емкости линейных конденсаторов с дискретным набором значений С3 и С4 из заданного дискретного набора значений емкости, можно добиться максимального размаха выходного напряжения столбцового зарядочувствительного усилителя при величинах емкостей С3 и С4 соответствующих линейных конденсаторов С3 и С4 приблизительно равных  При слабых потоках ИК-излучения (малом коэффициенте заполнения накопительного конденсатора С1) величина емкости конденсаторов С3 и С4 с дискретным набором значений емкости

При слабых потоках ИК-излучения (малом коэффициенте заполнения накопительного конденсатора С1) величина емкости конденсаторов С3 и С4 с дискретным набором значений емкости  Тогда конденсаторы С3 и С4 можно реализовать, например, таким образом, что

Тогда конденсаторы С3 и С4 можно реализовать, например, таким образом, что

а

а  В промежутке указанных значений емкости конденсаторов С3 и С4 принимают шестнадцать значений, меняясь с дискретностью

В промежутке указанных значений емкости конденсаторов С3 и С4 принимают шестнадцать значений, меняясь с дискретностью

Вышеприведенные рассуждения относительно линейности передаточной характеристики и однородности выходного сигнала при пояснении сущности предлагаемого устройства считывания в первом варианте реализации правомерны в отношении предлагаемого устройства считывания во втором варианте реализации.

Дифференциальное считывание заряда и дальнейшая передача сигнала в дифференциальном виде, реализованные во втором варианте предлагаемого устройства считывания, обеспечивают следующие преимущества.

Во-первых, полностью дифференциальные столбцовый ЗЧУ обеспечивает большую чувствительность при регистрации сигналов с фотоприемной матрицы по сравнению с однофазным ЗЧУ в первом варианте предлагаемого устройства, обеспечивает более высокое отношение сигнал/шум (размах выходного напряжения во втором варианте реализации предлагаемого устройства достигает напряжения питания).

Во-вторых, полностью дифференциальный столбцовый ЗЧУ обеспечивает подавление синфазного шума, возможность возникновения которого существует при реализации предлагаемого устройства по первому варианту.

В-третьих, использование дифференциального сигнала, что характерно для предлагаемого устройства по второму варианту реализации, обеспечивает лучшую помехозащищенность и устойчивость к наводкам по цепям питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ ДЛЯ МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2013 |

|

RU2529768C1 |

| ЗАРЯДОЧУВСТВИТЕЛЬНЫЙ ПРЕДУСИЛИТЕЛЬ | 2013 |

|

RU2526756C1 |

| ИЗМЕРИТЕЛЬ ЭЛЕКТРИЧЕСКИХ ЗАРЯДОВ | 2003 |

|

RU2260245C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПИКОВЫХ ЗНАЧЕНИЙ | 2014 |

|

RU2556327C1 |

| Интегратор | 1978 |

|

SU748439A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПИКОВЫХ ЗНАЧЕНИЙ | 2007 |

|

RU2343429C1 |

| Устройство для записи информации в блоки памяти с произвольной выборкой | 1984 |

|

SU1156136A1 |

| ИЗМЕРИТЕЛЬ ВИБРАЦИЙ ДЛЯ ЭКСТРЕМАЛЬНЫХ УСЛОВИЙ ЭКСПЛУАТАЦИИ | 2010 |

|

RU2456555C2 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |