Изобретение относится к электронике, а именно к источникам стабильного и температурно-независимого напряжения постоянного тока, и может быть использовано в качестве источника опорного напряжения при построении аналоговых интегральных схем (ИС), например, операционных усилителей, усилителей мощности, ИС драйверов двигателей, аналого-цифровых преобразователей (АЦП), цифроаналоговых преобразователей (ЦАП) и т.п.

Необходимость в хорошем источнике опорного напряжения часто возникает во многих схемах, особенно в тех схемах, которые питаются от однополярного источника напряжения питания. К ним относятся, в частности, мощные ИС драйверов двигателей постоянного тока для оптических накопителей.

Простейшим видом источников опорного напряжения является стабилитрон. В сущности, это диод, работающий при обратном смещении на участке, соответствующем напряжению пробоя, где ток пробоя очень быстро возрастает при дальнейшем росте напряжения. Чтобы использовать этот диод в качестве источника опорного напряжения надо просто обеспечить прохождение через него постоянного тока. Это обычно делается с помощью резистора, подключенного к достаточно высокому напряжению, и, таким образом, строится наиболее простой стабилизированный источник (см. П.Хоровиц, У.Хилл. «Искусство схемотехники», М.: Мир, 1984 г., с.314-325).

Недостатками такого источника опорного напряжения являются: большой ток потребления, повышенный уровень шумов, большое значение выходного импеданса, сложность реализации в интегральной схемотехнике.

Известен параметрический стабилизатор постоянного напряжения, содержащий балластный резистор, опорные диоды, дифференциальный усилитель, усилитель мощности и резистор отрицательной обратной связи, в который последовательно с опорными диодами включен дополнительный резистор, величина которого равна суммарному динамическому сопротивлению упомянутых диодов, при этом общая точка соединения дополнительного резистора и диодов подключена к неинвертирующему входу дифференциального усилителя (см. авт. свид. SU №313263, МКИ: H02M 5/00, опубл. 31.08.1971 г.).

Известен источник опорного напряжения (см. авт. свид. SU №1053093, МКИ: G05F 3/18, опубл. 07.11.1983 г.), который содержит последовательно соединенные образцовый резистор, прямо смещенный р-n-переход диода и стабилитрон, свободный электрод которого соединен с общей шиной, и операционный усилитель с двумя резисторами обратной связи, общая точка которых соединена с инвертирующим входом операционного усилителя, а свободный вывод одного из резисторов соединен с выходом операционного усилителя. В данном источнике опорного напряжения точка соединения диода и стабилитрона подключена к свободному выводу другого резистора обратной связи, анод диода соединен с неинвертирующим входом операционного усилителя, выход которого соединен со свободным выводом образцового резистора и с выходным выводом источника.

Недостатками данного устройства являются большой ток потребления и повышенный уровень шумов.

Для получения низковольтных опорных напряжений с низким уровнем шумов, малым током потребления используются источники опорных напряжений на «запрещенной зоне». К тому же, если речь идет о создании микросхемы, использующей внутренний источник опорного напряжения, то не все современные технологии представляют возможность создания стабилитронов. Существует усовершенствованная схема параметрического источника опорного напряжения, где обычный стабилитрон замещен на стабилитрон с напряжением запрещенной зоны» (см. П.Хоровиц, У.Хилл. «Искусство схемотехники», М.: Мир, 1984 г., с.319-320).

В технологиях изготовления микросхем, которые используют только CMOS-процесс, построение схемы стабилизации, основанной на принципе «запрещенной зоны», вызывает технологические трудности. В таких случаях используют либо источник опорного напряжения на CMOS-транзисторах, работающих в особых режимах (с нулевым температурным коэффициентом напряжения - ТКН), либо схемы источника опорного напряжения на диодах, резисторах и операционных усилителях. В первом случае можно получить очень хорошие источники опорного напряжения, но величина выходного напряжения будет сильно зависеть от технологических разбросов транзисторов. Во втором случае, если строить источник опорного напряжения на соотношениях резисторов, можно получить хороший источник со слабой чувствительностью к технологическому разбросу параметров элементов.

Схем, построенных по второму варианту, существует достаточно много. Один из примеров - это генератор опорного напряжения, описанный в патенте US №7119528, МКИ: G05F 3/16, опубл. 10.10.2006 г., в котором на основе применения принципа «запрещенной зоны» используют две системы обратной связи, поддерживающие напряжение с помощью источников тока. Эти системы обратных связей обеспечивают независимость величины опорного напряжения от технологического разброса, температуры и питающего напряжения. Точность опорного напряжения поддерживается даже при низком напряжении питания. Кроме того, обратные связи увеличивают выходной импеданс источников тока, уменьшающий влияние шумов от источника питания.

Наиболее близким аналогом - прототипом к заявляемому техническому решению является источник опорного напряжения, описанный в патенте US №5955873, МКИ: G05F 3/16, опубл. 21.09.1999 г., в котором источник опорного напряжения содержит первый операционный усилитель и второй операционный усилитель, первый резистор и второй резистор, первую цепь, состоящую из третьего резистора, четвертого резистора и первого диода, вторую цепь, состоящую из пятого резистора и второго диода, два источника тока и дополнительные два устройства для оперативного включения и выключения. Выход первого операционного усилителя соединен с первым контактом первого резистора. Инвертирующий вход первого операционного усилителя соединен со вторым контактом первого резистора и с первым контактом второго резистора. Второй контакт второго резистора соединен с общим проводом. Неинвертирующий вход первого операционного усилителя соединен с выходом второго операционного усилителя, с первым контактом третьего резистора и с первым контактом пятого резистора. Второй контакт третьего резистора соединен с инвертирующим входом второго операционного усилителя и с первым контактом четвертого резистора. Второй контакт четвертого резистора соединен с анодом первого диода. Второй контакт пятого резистора соединен с неинвертирующим входом второго операционного усилителя и с анодом второго диода. Катод первого диода и катод второго диода соединены с общим проводом.

Недостатком данного источника опорного напряжения является влияние технологического разброса параметров элементов на величину выходного напряжения.

Сущность изобретения заключается в следующем. Задача, на решение которой направлено заявляемое изобретение, заключается в уменьшении влияния технологических разбросов элементов на величину выходного напряжения и улучшение термостабильности в диапазоне рабочих температур.

Указанные технические результаты при осуществлении изобретения достигаются тем, что в известный источник опорного напряжения, содержащий первый операционный усилитель, выход которого соединен с первым контактом первого резистора, а инвертирующий вход первого операционного усилителя соединен со вторым контактом первого резистора и с первым контактом второго резистора, второй контакт которого соединен с общим проводом, второй операционный усилитель, первую цепь, состоящую из третьего резистора, четвертого резистора и первого диода, вторую цепь, состоящую из пятого резистора и второго диода, выход второго операционного усилителя соединен с первым контактом пятого резистора и с первым контактом третьего резистора, второй контакт которого соединен с первым контактом четвертого резистора, второй контакт четвертого резистора соединен с анодом первого диода, катод первого диода и катод второго диода соединены с общим проводом, дополнительно введены третий операционный усилитель, шестой резистор во второй цепи, четвертый операционный усилитель, петля обратной связи для второго операционного усилителя с седьмым резистором и с восьмым резистором, пятый операционный усилитель, девятый резистор, десятый резистор, одиннадцатый резистор, двенадцатый резистор, тринадцатый резистор, четырнадцатый резистор, выход второго операционного усилителя соединен с первым контактом седьмого резистора, а инвертирующий вход второго операционного усилителя соединен со вторым контактом седьмого резистора и с первым контактом восьмого резистора, второй контакт которого соединен с общим проводом, неинвертирующий вход второго операционного усилителя соединен с неинвертирующим входом четвертого операционного усилителя и подключен к точке соединения третьего резистора и четвертого резистора, а инвертирующий вход четвертого операционного усилителя соединен с выходом четвертого операционного усилителя (со своим выходом) и с первым контактом десятого резистора, неинвертирующий вход третьего операционного усилителя подключен ко второму контакту пятого резистора и к первому контакту шестого резистора, второй контакт которого соединен с анодом второго диода, а инвертирующий вход третьего операционного усилителя соединен с выходом третьего операционного усилителя (со своим выходом), с первым контактом одиннадцатого резистора и с неинвертирующим входом первого операционного усилителя, выход которого соединен с первым контактом четырнадцатого резистора, при этом неинвертирующий вход пятого операционного усилителя соединен со вторым контактом одиннадцатого резистора и с первым контактом двенадцатого резистора, второй контакт которого соединен с общим проводом, а инвертирующий вход пятого операционного усилителя соединен со вторым контактом десятого резистора и с первым контактом девятого резистора, причем выход пятого операционного усилителя соединен со вторым контактом девятого резистора и с первым контактом тринадцатого резистора, второй контакт которого соединен со вторым контактом четырнадцатого резистора, место соединения тринадцатого резистора и четырнадцатого резистора является выходом источника опорного напряжения.

Сущность изобретения поясняется графическими материалами.

На фиг.1 представлена функциональная схема источника опорного напряжения.

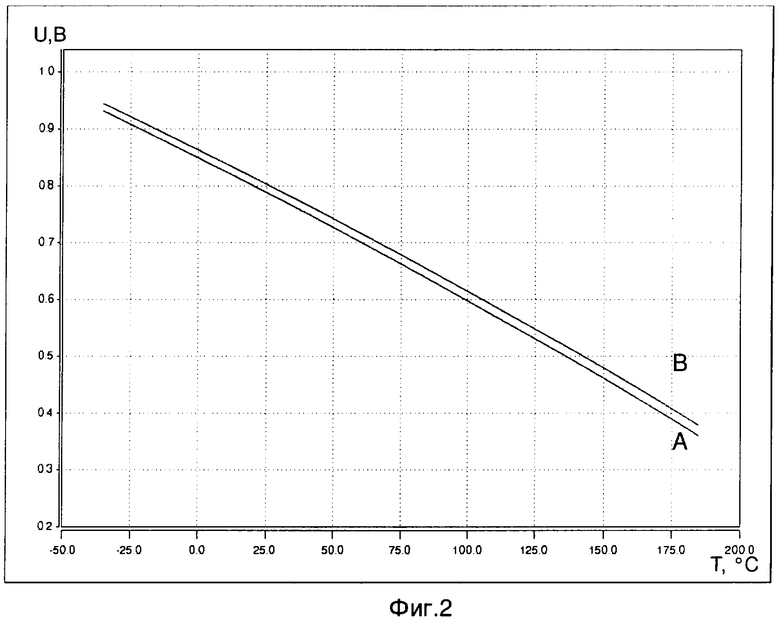

На фиг.2 представлен график зависимости потенциалов в точках А и В от изменения температуры.

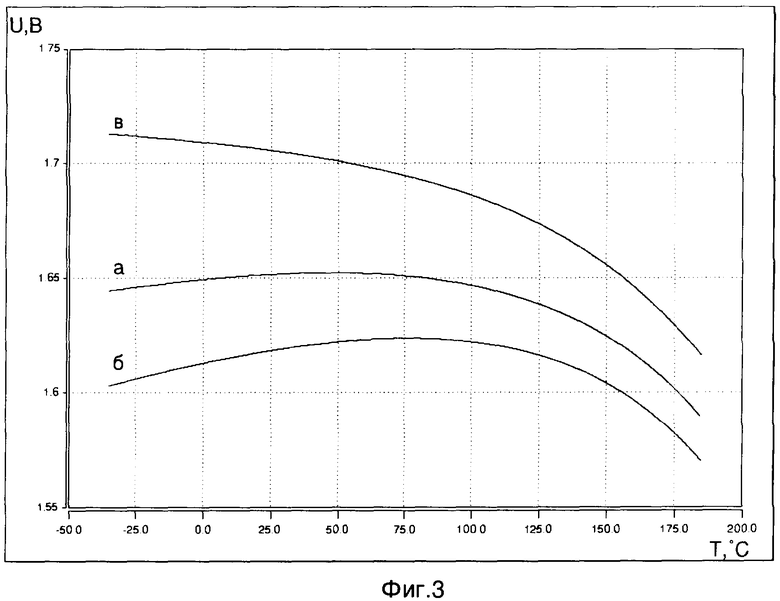

На фиг.3 представлены графики зависимости выходного опорного напряжения с расчетными номиналами резисторов - а; увеличенными на 25% - б; уменьшенными на 25% относительно расчетных - в.

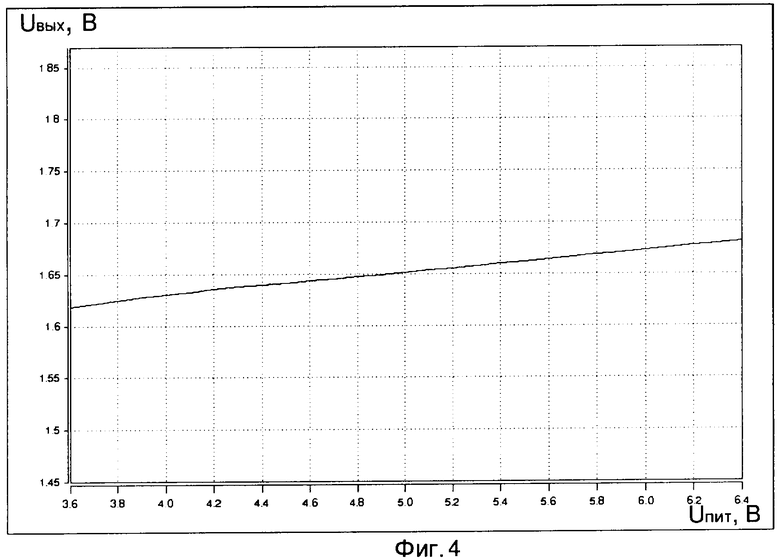

На фиг.4 представлен график зависимости выходного опорного напряжения от изменения напряжения питания.

На чертежах приняты следующие обозначения.

1 - первый операционный усилитель;

2 - первый резистор;

3 - второй резистор;

4 - второй операционный усилитель;

5 - третий резистор;

6 - четвертый резистор;

7 - первый диод;

8 - пятый резистор;

9 - второй диод;

10 - третий операционный усилитель;

11 - шестой резистор;

12 - четвертый операционный усилитель;

13 - седьмой резистор;

14 - восьмой резистор;

15 - пятый операционный усилитель;

16 - девятый резистор;

17 - десятый резистор;

18 - одиннадцатый резистор;

19 - двенадцатый резистор;

20 - тринадцатый резистор;

21 - четырнадцатый резистор;

А - узел А - точка соединения третьего резистора 5, четвертого резистора 6, неинвертирующего входа второго операционного усилителя 4 и неинвертирующего входа четвертого операционного усилителя 12.

В - узел В - точка соединения пятого резистора 8, шестого резистора 11 и неинвертирующего входа третьего операционного усилителя 10;

С - узел С - точка соединения выхода первого операционного усилителя 1, первого резистора 2 и четырнадцатого резистора 21;

D - узел D - точка соединения выхода пятого операционного усилителя 15 со вторым контактом девятого резистора 16 и с первым контактом тринадцатого резистора 20;

а - кривая зависимости выходного опорного напряжения от температуры с расчетными номиналами резисторов (см. фиг.3);

б - кривая зависимости выходного опорного напряжения от температуры с номиналами сопротивлений резисторов, увеличенными на 25% относительно расчетных (см. фиг.3);

в - кривая зависимости выходного опорного напряжения от температуры с номиналами сопротивлений резисторов, уменьшенными на 25% относительно расчетных (см. фиг.3).

Источник опорного напряжения содержит первый операционный усилитель 1; петлю обратной связи первого операционного усилителя 1, состоящую из первого резистора 2 и второго резистора 3; второй операционный усилитель 4 с петлей обратной связи, включающей седьмой резистор 13 и восьмой резистор 14; первую цепь, состоящую из третьего резистора 5, четвертого резистора 6 и первого диода 7; вторую цепь, состоящую из пятого резистора 8, шестого резистора 11 и второго диода 9, третий операционный усилитель 10, четвертый операционный усилитель 12, пятый операционный усилитель 15; петлю обратной связи пятого операционного усилителя 15, состоящую из девятого резистора 16 и десятого резистора 17; третью цепь, состоящую из одиннадцатого резистора 18 и двенадцатого резистора 19; четвертую цепь формирования выходного опорного напряжения, состоящую из тринадцатого резистора 20 и четырнадцатого резистора 21.

Выход первого операционного усилителя 1 подключен к первому контакту первого резистора 2 и к первому контакту четырнадцатого резистора 21, образуя узел С. Инвертирующий вход первого операционного усилителя 1 подключен ко второму контакту первого резистора 2 и к первому контакту второго резистора 3, второй контакт которого соединен с общим проводом. Выход второго операционного усилителя 4 соединен с первым контактом пятого резистора 8, с первым контактом третьего резистора 5 и с первым контактом седьмого резистора 13. Инвертирующий вход второго операционного усилителя 4 соединен со вторым контактом седьмого резистора 13 и с первым контактом восьмого резистора 14, второй контакт которого соединен с общим проводом. Неинвертирующий вход второго операционного усилителя 4 и неинвертирующий вход четвертого операционного усилителя 12 подключены к точке соединения А (узел А) второго контакта третьего резистора 5 и первого контакта четвертого резистора 6, второй контакт которого соединен с анодом первого диода 7. Инвертирующий вход четвертого операционного усилителя 12 соединен с выходом четвертого операционного усилителя 12 и с первым контактом десятого резистора 17.

Неинвертирующий вход третьего операционного усилителя 10 подключен к точке соединения В (узел В) второго контакта пятого резистора 8 и первого контакта шестого резистора 11, второй контакт которого соединен с анодом второго диода 9, а инвертирующий вход третьего операционного усилителя 10 соединен с выходом третьего операционного усилителя 10, с первым контактом одиннадцатого резистора 18 и с неинвертирующим входом первого операционного усилителя 1.

Катод первого диода 7 и катод второго диода 9 соединены с общим проводом.

Неинвертирующий вход пятого операционного усилителя 15 соединен со вторым контактом одиннадцатого резистора 18 и с первым контактом двенадцатого резистора 19, второй контакт которого соединен с общим проводом, а инвертирующий вход пятого операционного усилителя 15 подключен ко второму контакту десятого резистора 17 и к первому контакту девятого резистора 16, выход пятого операционного усилителя 15 подключен ко второму контакту девятого резистора 16 и к первому контакту тринадцатого резистора 20, образуя узел D. Второй контакт тринадцатого резистора 20 соединен со вторым контактом четырнадцатого резистора 21, образуя узел выходного опорного напряжения.

Источник опорного напряжения работает следующим образом.

В источнике опорного напряжения применены однотипные резисторы с одинаковым температурным коэффициентом сопротивления.

На втором операционном усилителе 4, седьмом резисторе 13 и восьмом резисторе 14 собран неинвертирующий усилитель, входным сигналом для которого служит потенциал узла А в цепи, образованной третьим резистором 5 и четвертым резистором 6, а также первым диодом 7.

Такая схема является самозапускающейся при подаче напряжения питания при условии, что сопротивление третьего резистора 5 существенно больше, чем сопротивление четвертого резистора 6. На выходе второго операционного усилителя 4 формируется напряжение, равное потенциалу в точке А, умноженному на сумму отношения сопротивления седьмого резистора 13 к сопротивлению восьмого резистора 14 и единицы, т.е.

Uвых.оу4=UA·(RR13/RR14+1), где

Uвых.оу4 - напряжение на выходе второго операционного усилителя 4;

UA - напряжение в точке А - точке соединения третьего резистора 5 и четвертого резистора 6;

RR13 - сопротивление седьмого резистора 13;

RR14 - сопротивление восьмого резистора 14.

Это напряжение не зависит от напряжения питания схемы. Однако оно зависит от температуры и с ростом последней уменьшается, так как уменьшается падение напряжения на диоде.

Чтобы получить стабильное напряжение на выходе источника опорного напряжения, использована вторая цепь, содержащая пятый резистор 8 и шестой резистор 11, имеющие номиналы сопротивлений, равные соответственно сопротивлению третьего резистора 5 и четвертого резистора 6, а второй диод 9 имеет меньшую площадь р-n-перехода, чем первый диод 7. При этом потенциал в точке В выше, чем потенциал в точке А, и разность между ними с ростом температуры растет (см. фиг.2). На фиг.2 верхняя кривая отображает изменение потенциала точки В от температуры, а нижняя кривая - изменение потенциала точки А от температуры.

Дальнейшая задача состоит в том, чтобы усилить эту разность потенциалов до нужной величины и сложить со спадающей от роста температуры характеристикой напряжения на диоде. Чтобы входные токи последующих каскадов не вносили погрешностей в разность потенциалов между узлами А и В, в данном случае используются повторители этих потенциалов, выполненные на четвертом операционном усилителе 12 и третьем операционном усилителе 10. Первый операционный усилитель 1 с петлей обратной связи на первом резисторе 2 и втором резисторе 3 представляет собой неинвертирующий усилитель, входным сигналом для которого является потенциал точки В, уменьшающейся с ростом температуры. Соотношением сопротивлений второго резистора 2 и третьего резистора 3 задается наклон вольт-температурной характеристики узла С.

Пятый операционный усилитель 15 с петлей обратной связи на девятом резисторе 16 и десятом резисторе 17 и с третьей цепью на одиннадцатом резисторе 18 и двенадцатом резисторе 19 представляет собой дифференциальный усилитель, входными сигналами для которого являются потенциалы в точках А и В, так как потенциал на выходе четвертого операционного усилителя 12 равен потенциалу узла А, а потенциал на выходе третьего операционного усилителя 10 равен потенциалу узла В.

Соотношением номиналов сопротивлений девятого резистора 16 и десятого резистора 17, а также двенадцатого резистора 19 и одиннадцатого резистора 18 задается наклон вольт-температурной характеристики узла D, при этом должно выполняться условие:

RR16/RR17=RR19/RR18, где

RR16 - сопротивление девятого резистора 16,

RR17 - сопротивление десятого резистора 17,

RR18 - сопротивление одиннадцатого резистора 18,

RR19 - сопротивление двенадцатого резистора 19.

Таким образом, с ростом температуры в точке (узле) С напряжение снижается, а в точке (узле) D напряжение повышается. Можно подобрать наклоны этих характеристик так, чтобы при суммировании они выдавали величину напряжения, не зависящую от температуры.

Четвертая цепь, состоящая из тринадцатого резистора 20 и четырнадцатого резистора 21, номиналы сопротивлений которых равны, выполняет роль сумматора токов, порождаемых потенциалами узлов С и D, и в точке соединения этих резисторов формируется выходное температурно-независимое напряжение (см. фиг.3).

Как видно из описания, величина опорного напряжения зависит от соотношения номиналов сопротивлений резисторов в схеме и отношения площадей p-n-переходов диодов, что в случае интегрального исполнения гарантируется технологическим процессом изготовления кристаллов. Так как в схеме нет ни одного транзистора, не охваченного обратной связью (все транзисторы внутри операционных усилителей), то сколько-нибудь существенного влияния на величину выходного напряжения технологический разброс транзисторов не оказывает. Изменение напряжения питания слабо влияет на величину выходного напряжения. Это иллюстрирует график, приведенный на фиг.4.

| название | год | авторы | номер документа |

|---|---|---|---|

| ШИРОКОДИАПАЗОННЫЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2007 |

|

RU2330377C1 |

| МАЛОШУМЯЩИЙ КВАРЦЕВЫЙ ГЕНЕРАТОР С АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКОЙ УСИЛЕНИЯ | 2012 |

|

RU2498498C1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| СХЕМА ВОЗБУЖДЕНИЯ ЧАСТОТНОГО ДАТЧИКА | 2019 |

|

RU2724795C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2010 |

|

RU2426170C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ОПОРНОГО НАПРЯЖЕНИЯ | 2010 |

|

RU2426169C1 |

| АКТИВНЫЙ RC-ФАЗОВЫЙ КОНТУР | 1991 |

|

RU2019027C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАВЛЕНИЯ | 1992 |

|

RU2024831C1 |

| Устройство для контроля электрических параметров трансформаторов | 1982 |

|

SU1122984A1 |

| Множительно-делительное устройство | 1982 |

|

SU1030810A1 |

Изобретение относится к электронике, а именно к источникам стабильного и температурно-независимого напряжения постоянного тока, и может быть использовано в качестве источника опорного напряжения при построении аналоговых интегральных схем (ИС), например, операционных усилителей, усилителей мощности, ИС драйверов двигателей, аналого-цифровых преобразователей (АЦП), цифроаналоговых преобразователей (ЦАП) и т.п. Технический результат - уменьшение влияния технологических разбросов элементов на величину выходного напряжения и улучшение термостабильности в диапазоне рабочих температур. Устройство содержит операционные усилители (1, 4, 10, 12, 15), резисторы (2, 3, 5, 6, 8, 11, 13, 14, 16-21), диоды (7, 9). Величина опорного напряжения зависит от соотношения номиналов сопротивлений резисторов и отношения площадей p-n переходов диодов. 4 ил.

Источник опорного напряжения, содержащий первый операционный усилитель, выход которого соединен с первым контактом первого резистора, а инвертирующий вход первого операционного усилителя соединен со вторым контактом первого резистора и с первым контактом второго резистора, второй контакт которого соединен с общим проводом, второй операционный усилитель, первую цепь, состоящую из третьего резистора, четвертого резистора и первого диода, вторую цепь, состоящую из пятого резистора и второго диода, выход второго операционного усилителя соединен с первым контактом пятого резистора и с первым контактом третьего резистора, второй контакт которого соединен с первым контактом четвертого резистора, второй контакт четвертого резистора соединен с анодом первого диода, катод первого диода и катод второго диода соединены с общим проводом, отличающийся тем, что дополнительно введены третий операционный усилитель, шестой резистор во второй цепи, четвертый операционный усилитель, петля обратной связи для второго операционного усилителя с седьмым резистором и с восьмым резистором, пятый операционный усилитель, девятый резистор, десятый резистор, одиннадцатый резистор, двенадцатый резистор, тринадцатый резистор, четырнадцатый резистор, выход второго операционного усилителя соединен с первым контактом седьмого резистора, а инвертирующий вход второго операционного усилителя соединен со вторым контактом седьмого резистора и с первым контактом восьмого резистора, второй контакт которого соединен с общим проводом, неинвертирующий вход второго операционного усилителя соединен с неинвертирующим входом четвертого операционного усилителя и подключен к точке соединения третьего резистора и четвертого резистора, а инвертирующий вход четвертого операционного усилителя соединен со своим выходом и с первым контактом десятого резистора, неинвертирующий вход третьего операционного усилителя подключен ко второму контакту пятого резистора и к первому контакту шестого резистора, второй контакт которого соединен с анодом второго диода, а инвертирующий вход третьего операционного усилителя соединен со своим выходом, с первым контактом одиннадцатого резистора и с неинвертирующим входом первого операционного усилителя, выход которого соединен с первым контактом четырнадцатого резистора, при этом неинвертирующий вход пятого операционного усилителя соединен со вторым контактом одиннадцатого резистора и с первым контактом двенадцатого резистора, второй контакт которого соединен с общим проводом, а инвертирующий вход пятого операционного усилителя соединен со вторым контактом десятого резистора и с первым контактом девятого резистора, причем выход пятого операционного усилителя соединен со вторым контактом девятого резистора и с первым контактом тринадцатого резистора, второй контакт которого соединен со вторым контактом четырнадцатого резистора, место соединения тринадцатого резистора и четырнадцатого резистора является выходом источника опорного напряжения.

| US 5955873 А, 21.09.1999 | |||

| Источник опорного напряжения | 1982 |

|

SU1053093A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| US 6407611 B1, 18.06.2002 | |||

| US 6184670 В1, 06.02.2001. | |||

Авторы

Даты

2009-01-20—Публикация

2007-06-18—Подача