ных транзисторов, первый вывод седьмого масштабного резистора подключен к неинвертирующему входу второго опе рационного усилителя, выход которого является выходом устройства, источник напряжений смещения, к выходам которого подключены первый и второй выводы балансировочного потенциометра, общий выхбд источника напряжений смещения подключен к шине нулевого потенциала, третий операцинный усилитель, между инвертирующим входом и выходом которого включен восьмой масштабный резистор, второй вывод седьмого масштабного резистора соединен с выходом третьего операционного усилителя, неинвертирующий вход которого через девятый масштабный резистор подключен к шине нулево го потенциала, коллекторы третьего и четвертого усилительных транзисторов соединены соответственно с инвертирующим и неинвертирующим входами третьего операционного усилителя, десятый масштабный резистор, о т л и ч ающе ее я тем, что, с целью повьш1ения точности в работе путем расширения диапазона величин входных сигналов, снижения дрейфа нулевого уровня и расширения области применения за счет реализации перемножения на алгебраическую сумму сигналов, в него введены четвертый операционный усилитель, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый масштабные резисторы, третий, четвертый, пятый и шестой токоограничительные резисторы, первый и второй ограничительные диоды, причем инвертирующий вход четвертого операционного усилителя соединен с первым вы11 водом десятого масштабного резистора, второй вывод которого соединен с шиной нулевого потенциала, между инвертирующим входом и выходом четвертого операционного усилителя включен одиннадцатый масштабный резистор,- неинвертирующий вход четвертого операционного усилителя через двенадцатью масштабный резистор соединен с первым входом устройства, выход четвертого операционного усилителя подключен к первому выводу тринадцатого масштабного резистора, второй вывод которого соединён с эмиттером третьего и четвертого усилительных транзисторов, с анодом первого ограничительного диода и с первым выводом четырнадцатого масштабного резистора, второй вывод которого подключен к неинвертирующему входу четвертого операционного усилителя, катод первого ограничитель ного диода соединен с шиной нулевого потенциалами с катодом второго ограничительного диода, анод которого соединен с вторым выводом четвертого масштабного резистора, первый вывод третьего токоограничительного резистора соединен с базой третьего усилительного транзистора, второй вьгоод третьего токоограничительного резистора соединен с вторым- подвижным контактом балансировочного потенциометра, первые выводы четвертого, пятого и шестого токоограничительных резисторов подключены к базам соответственно первого, второго и третьего усилительных транзисторов, вторые выводы четвертого, пятого и шестого токоограничительных резисторов соединены и являются входом дополнительного сигнала-Слагаемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1982 |

|

SU1119037A1 |

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

| Функциональный преобразователь напряжение - ток | 1989 |

|

SU1672479A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Устройство для перемножения напряжений | 1983 |

|

SU1095197A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Аналоговый перемножитель сигналов | 1989 |

|

SU1626257A1 |

| Четырехквадрантное множительное устройство | 1980 |

|

SU957225A1 |

| Аналоговый делитель | 1982 |

|

SU1022180A1 |

ПЕРЕМНОЖАЮЩЕЕ УСТРОЙСТВО, содержащее первый операционный усили тель, инвертирующий вход которогосоединен с первым выводом первого масштабного резистора, второй вывод которого является входом первого сигнала-сомножителя, между инвертирующим входом и выходом первого операционного усилителя включен второй масштабный резистор, неинвертирующий вход первого операционного усилителя через третий масштабный резистор соединен с шиной нулевого потенциала, выход первого операционного усилителя подключен к первому выводу четвертого масштабного резистора, второй вьгеод которого соединен с первым выводом пятого масштабного резистора, второй вывод которого под ключен к неинвертирующему входу первого операционного усилителя, первый второй, трет1-1й и четвертьш усилитель ные транзисторы, эмиттеры первого и второго усилительных транзисторов подключены к второму вьгооду четвертого масштабного резистора, коллекторы первого, второго, третьего и четвертого усилительных транзисторов через соответств тощие первый, второй, третий и четвертьп резисторы нагрузки соединены с выходом источника Hanps жения, база первого усилительного транзистора соединена с первыми выводами первого резистора смещения и первого токоограничительного резистора, база второго усилительного транзистора соединена с первыми выводами второго резистора смещения, второго токоограничительного резистора и с базой четвертого усилительного транзистора, эмиттер которого соединен с эмиттером третьего усилительного транзистора, база которого подключена к первому выводу третьего резистора смещения, второй вывод которого соединен с вторыми выводами первого и второго резисторов смещения и с шиной нулевого потенциала, второй вывод первого токоограничительного резистора подключен к подвижному контакту балансировочного потенциометра,второй вывод второго токоограничительного резистора соединен с первым выводом терморезистора, второй вывод которого является входом второго сигнала сомножителя, второй операционный усилитель между инвертирующим входом и выходом которого включен шестой масштабный резистор, к неинвертирующему и инвертирующему входам второго операциояного усилителя подключены соответственно коллекторы первого и второго усилитель

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Известно перемножающее устройство, 5 содержащее дифференциальный усилитель.ный каскад, операционные усилители, масштабные и токоограничительные резисторы I) .

Недостатком этого устройства является невысокая точность в работе в большом диапазоне величин входных сигналов.

Наиболее близким к предложенному является перемножающее устройство, содержащее первый операционный усилитель, инвертирующий вход которого соединен с первым выводом первого масштабного резистора, второй вывод которого является первым входом устройства, между инвертирующим входом и вьгходом первого операционного усилителя включен второй масштабный резистор, неинвертирующий вход первого операционного усилителя через третий масштабный резистор соединен с шиной нулевого потенциала, выход первого операционного усилителя подключен к первому выводу четвертого масштабного резистора, второй вывод которого соединен с первым выводом пятого масштабного резистора, второй вывод которого подключен к неинвертирующему входу первого операционного усилителя, первый и второй, третий и четвертый усилительные транзисторы, эмиттеры первого и второго усилитель ных транзисторов подключены к второму выводу четвертого масштабного резистора, коллекторы первого, второго, третьего и четвертого усилительных транзисторов через .соответствующие первый и второй, третий и четвертый резисторы нагрузки соединены с первым выходом источника напряже- ния, второй выход которого через восьмой Масштабный резистор соединен с инвертирующим входом первого операционного усилителя, база первого усилительного транзистора соединена с первыми выводами первого резистора смещения и первого токоограничительного резистора, база второго усилительного транзистора соединена с первыми выводами второго резистора смещения и второго токоограничительного резистора и с базой четвертого усилительного транзистора, эмиттер которого соединен с первым выводом токозадающего резистора и с эмиттером третьего усилительного транзистора, база которого подключена к первому выв.оду третьего резистора смещения, второй вьшод которого соединен с вторым выводом первого и второго резисторов смещения и с шино нулевого потенциала, второй вьгаод первого токоограничительного резистора подключен к подвижному контакту балансировочного потенциометра, второй вывод второго токоограничительного резистора соединен с первым выводом терморезистора, второй вьгоод которого является вторым входом устройства, второй операционный усилитель между инвертирующим входом и выходгм которого включен шестой масштабньп резистор, к неинвертирующему и инвертирующему входам подключены соответственно коллекторы первого и второго усилительных транзисторов, первьй вывод седьмого масштабного резистора подключен к неинвертирующему входу второго операционного усилителя, выход которого является выходом устройства, источник напряжений смещения, к выходам которого подключены первьш и второй выводы балансировочного потенциометра и второй вывод токозадающего резистора общий выход источника напряжений смещения подключен к шине нулевого потенциала, третий операционный усилитель, между инвертирующим входом и выходом которого включен девятый масштабный резистор, второй вывод седьмого масштабного резистора соединен с выходом -третьего операционного усилителя, неинвертирующий вход которого через десятый масштабный резистор подключен к шине нулевого потенциала, коллекторы третьего и четвертого усилительных транзисторов соединены соответственно с инвертирующим и неинвертирукнцим входами третьего операционного усилителя, первый и второй выводы блока коррекции соединены с выводами первого масштабного резистора 2 . Недостатками известного устройства являются узкий диапазон изменения величин входных сигналов из-за неполного использования первого операционного усилителя, значительный дрейф нулевого уровня и узкая область применения, Цель изобретения - повьшение точности в работе путем расширения диапазона величин входных сигналов, снижения дрейфа нулевого уровня и расширения области применения за счет реализации перемножения на алгебраическую сумму сигналов. Указанная цель достигается тем, что в известное перемножакяцее устройство, содержащее первый операционный усилитель, инвертирующий вход которого соединен с первым вьтодом первого масштабного резистора, второй вывод которого является входом первого сигнала-сомножителя, между инвертирующим входом и выходом первого операционного усилителя включен второй масштабный резистор, неинвер-. тирующий вход первого операционного усилителя через третий масштабный резистор соединен с шиной нулевого потенциала, выход первого операционного усилителя подключен к первому выводу четвертого масштабного резистора, второй вывод которого соединен с первым выводом пятого масштабного резистора, второй вывод которого подключен к неинвертирующему входу первого операционного усилителя, первый, второй, третий и четвертый усилительные транзисторы, эмиттеры первого и второго.усилительных транзисторов подключены к второму выводу четвертого масштабного резистора, коллекторы первого и второго, третьего и четвертого усилительных транзисторов через соответств5тощие первый и второй, третий и четвертый резисторы нагрузки соединены с выходом источника напряжения, база первого усилительного транзистора .соединена с первыми выводами первого резистора смещения и первого токоограничительного резистора, база второго усилительного транзистора соединена с первыми выводами второго резистора смещения и второго токоограничительного резистора и с базой четвертого усилительного транзистора эмиттер которого соединен ci эмиттером третьего усилительного транзистора, база которого подключена к пер вому выводу третьего резистора смеще ния, второй вьшод которого соединен вторыми выводами первого и второго резисторов смещения и с шиной нулево го потенциала, второй вывод первого ток.оограничительного резистора подключен к подвижному контакту баланси ровочного потенциометра, второй вывод второго токоограничительного резистора соединен с первым выводом терморезистора, второй вывод которого является входом второго сигнала сомножителя, второй операционный уси литель между инвертирующим входом и выходом которого включен тестой масш табный резистор, к неинвертирующему и инвертирующему входам второго операционного усилителя подключены соот ветственно коллекторы первого и второго усилительных транзисторов,первый вьшод седьмого масштабного резистора подключен к неинвертирующему входу второго операционного усилителя, выход которого является выходом устройства, источник напряжений сме-/ щения, к выходам которого подключены первый и второй выводы балансировочного потенциометра, общий выход источника напряжений смещения подключен к шине нулевого потенциала, третий операционный усилитель, между инвертирующим входом и выходом которого включен восьмой .масштабный резистор, второй вывод седьмого масштабного резистора соединен с выходом, третьего операционного усилителя, неинвертирующий вход которого через девятьй масштабный резистор подключен к шигш нулевого потенциала, коллекторы третьего и четвертого усилительных транзисторов соединены соответственно с инвертирующим и неинвертирзпощим входами третьего операционного усилителя, десятый масштабный резистор, введены четвертый операционный усилитель, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый масштабные резисторы, третий, четвертый, пятый и шестой . токоограничительные резисторы, первый и второй ограничительные диоды, . причем инвертирующий вход четвертого операционного усилителя соединен с первым выводом десятого . масштабного резистора, второй вывод которого соединен с шиной нулевого потенциала, между инвертирующим входом и выходом четвертого операционного усилителя -включен одиннадцатый масштабный резистор, неинвертирующий вход, четвертого операционного усилителя через двенадцатый масштабнь:й резистор соединен с первым входом устройства, выход четвертого операционного усилителя подключен к первому выводу тринадцатого масштабного резистора, второй вывод которого соединен с эмиттерами третьего и четвертого усилительных транзисторов, с анодом первого ограничительного диода и с первым выводом четырнадцатого масштабного резистора, второй вывод которого подключен к неинвертирующему входу четвертого операционного усилителя, катод первого ограничительного диода соединен с шиной нулевого потенциала и с катодом второго ограничительного диода, анод которого соединен с вторым выводом четвертого масштабного резистора.

первый вывод третьего токоограничительного резистора соединен с базой третьего усилительного транзистора, второй вывод третьего токоограничительного резистора соединен с вторым подвижным контактом балансировочного потенциометра, перв.ые выводы четвертого, пятого и шестого токоограничительных резисторов подключены к базам первого, второго и третьего усилительных транзисторов, вторые выводы четвертого, пятого и шестого токоограничительных резисторов соединены и являются входом дополнительного сигнала-слагаемого устройства.

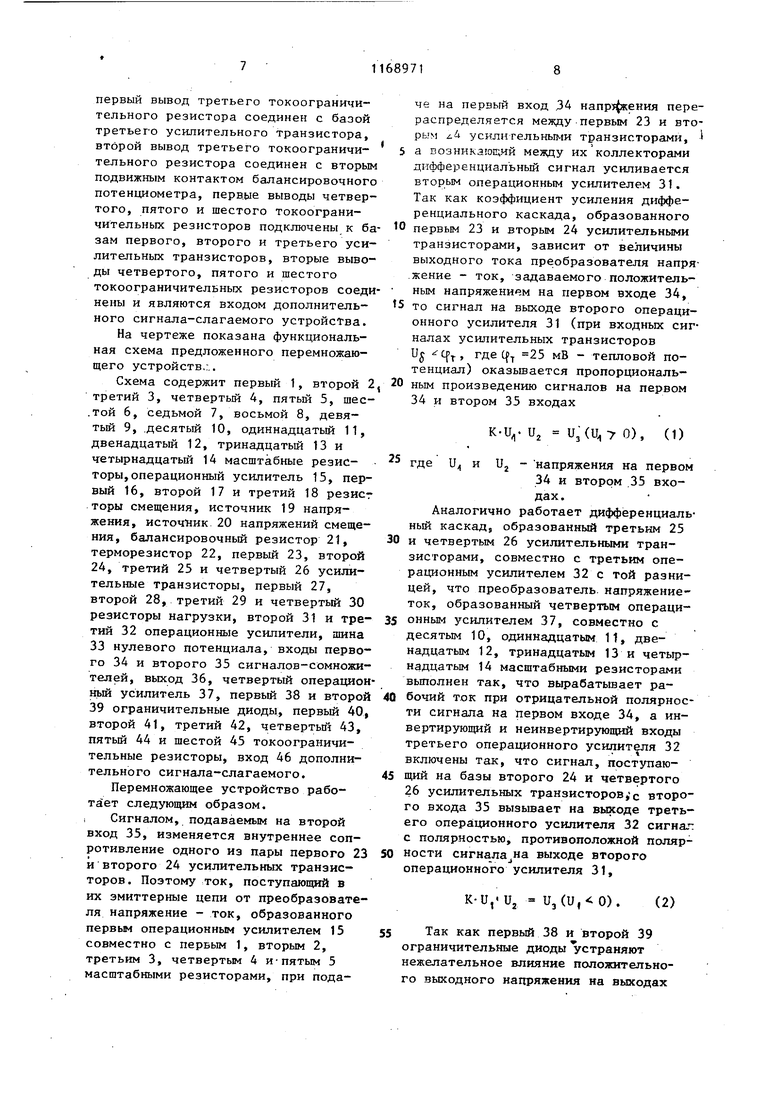

На чертеже показана функциональная схема предложенного перемножающего устройств,:..

Схема содержит первый 1, второй 2 третий 3, четвертьш 4, пятый 5, шес.той 6, седьмой 7, восьмой 8, девятый 9, .десятый 10, одиннадцатый 11, двенадцатый 12, тринадцатый 13 и четырнадцать 14 масштабные резисторы, операционный усилитель 15, первый 16, второй 17 и третий 18 резисг торы смещения, источник 19 напряжения, источник.20 напряжений смещения, балансировочный резистор 21, терморезистор 22, первый 23, второй 24, третий 25 и четвертый 26 усилительные транзисторы, первый 27, второй 28, третий 29 и четвертый 30 резисторы нагрузки, второй 31 и третий 32 операционные усилители, шина 33 нулевого потенциала, входы первого 34 и второго 35 сигналов-сомножителей, выход 36, четвертый операцнонньй усилитель 37, первый 38 и второй 39 ограничительные диоды, первый 40, второй 41, третий 42, четвертьш 43, пятый 44 и шестой 45 токоограничительные резисторы, вход 46 дополнительного сигнала-слагаемого.

Перемножающее устройство работает следующим образом, i Сигналом, подаваемым на второй вход 35, изменяется внутреннее сопротивление одного из пары первого 23 и второго 24 усилительных транзисторов. Поэтому ток, поступающий в их змиттерные цепи от преобразователя напряжение - ток, образованного первым операционным усилителем 15 совместно с первым 1, вторым 2, третьим 3, четвертым 4 и-пятым 5 масштабными резисторами, при подаче на первый вход 34 перераспределяется между первым 23 и вторым й усилительными транзисторами, а возникагощий меящу их коллекторами дифференциальный сигнал усиливается вторым операционным усилителем 31. Так как коэффициент усиления дифференциального каскада, образованного

первым 23 и вторым 24 усилительными транзисторами, зависит от величины выходного тока преобразователя напряжение - ток, задаваемого положительным напряжением на первом входе 34,

то сигнал на выходе второго операционного усилителя 31 (при входных сигналах усилительных транзисторов Uj С{, где ( 25 мВ - тепловой потенциал) оказьшается пропорциональ-

ным произведению сигналов на первом 34 и втором 35 входах

к-и. и, из(Ц7 0), (1)

где и и Uj - напряжения на первом

34 и втором 35 входах.

Аналогично работает дифференциальный каскад, образованный третьим 25

и четвертым 26 усилительными транзисторами, совместно с третьим операционным усилителем 32 с той разницей, что преобразователь, напряжениеток, образованный четвертым операционным усилителем 37, совместно с десятым 10, одиннадцатым 11, двенадцатым 12, тринадцатым 13 и четырнадцатым 14 масштабными резисторами вьтолнен так, что вырабатывает рабочий ток при отрицательной полярности сигнала на первом входе 34, а инвертирующий и неинвертирующий входы третьего операционного усилителя 32 включены так, что сигнал, поступающий на базы второго 24 и четвертого 26 усилительных транзисторов с второго входа 35 вызывает на выходе третьего операционного усилителя 32 сигна-п с полярностью, противоположной полярности сигнала на выходе второго операционного усилителя 31,

K-UjUj из(и,0). (2)

Так как первый 38 и второй 39 ограничительные диоды Устраняют нежелательное влияние положительного выходного напряжения на выходах

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Алексеенко А.Г | |||

| и др | |||

| Применение прецизионных аналоговых ИС | |||

| М Радио и связь, 1981, с | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3532136/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1983-11-05—Подача