того масштабного резистора, первый вывод которого соединен с вторым выводом одиннадцатого масштабного резистора, второй вывод восьмого масштабного резистора подключен к шине нулевого потенциала, затвор первого полевого транзистора через четырнадцатый масштабный резистор соединен с первым выводом шестого масштабного резистора, второй вывод которого подключен к затвору второго полевого 10 Уранзистора, второй вывод второго масштабного резистора соединен с неинвертирующим входом второго one- рационного усилителя, второй вывод первого масштабного резистора является первым входом устройства, затворы первого и второг о полевых транзисторов являются соответственно вторым и третьим входами устройства, выходом которого является выходтретьего операционного усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Множительное устройство | 1977 |

|

SU667971A1 |

| Аналоговое множительное устройство | 1986 |

|

SU1319047A1 |

| Аналоговое множительное устройство | 1985 |

|

SU1280401A1 |

| Управляемое резистивное устройство | 1988 |

|

SU1553987A1 |

| Аналоговое делительное устройство | 1982 |

|

SU1072061A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2007 |

|

RU2344464C1 |

МНОЖИТЕЛЬНО-ЛЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый, второй, третий и четвертый операционные усилители, к неинвертирующему входу первого операцио.нного усилители подключен первый вывод первого масштабного резистора, второй вывод которого соединен с первым выводом второго масштабного резистора, к выходу первого операционного усилителя подключен первый вывод третьего масштабного резистора, неинвертирующий вход второго операционного усилителя через .четвертый масштабный резистор соединен с шиной нулевого потенциала, между инвертирующим входом и выходом второго операционного усилителя подключен пятый масштабный резистор, к инверт тирующему входу третьего операционного усилителя подключен первый вывод шестого масштабного резистора, к выходу третьего операционного усилителя - первый вывод седьмого масштабного резистора, к инвертирующему входу четвертого операционного усилителя - первый вывод восьмого масштабного резистора, к выходу четвертого операционного усилителя первый вывод девятого масштабного резистора, неинвертирующий вход четвертого операционного-усилителя соединён с первым выводом десятого масштабного резистора, второй вывод которого соединен с первыми выводами одиннадцатого и двенадцатого масштабных резисторов, тринадцатый и . четырнадцатый масштабные резисторы, отли чаю щееся тем, что, с целью повышения быстродействия, в него введены первый, второй и третий элементы с управляемой проводимостью, выполненные на полевых транзисторах, истоки полевых транзисторов соединены с шиной нулевого потенциала, стоки первого и второго полевых транзисторов подключены к второму выводу третьего масштабного резистора и к инвертирующему входу первого операционного усилителя; выход которого через тринадцатый . масштабный резистор соединен с инвертирующим входом второго операцион-lQQ ного усилителя, выход которого подключен к затвору третьего полевого транзистора, сток которого соединен с первым выводом двенадцатого масштабного резистора, второй вывод которого подключен к инвертирующему входу третьего операционного усилителя, неинвертирующий вход которого соединен с шиной нулевого потенциала, второй вывод седьмого масштабного резистора подключен к неинвертирующему входу четвертого операционного усилителя, инвертирующий вход которого соединен с вторым выводом девя

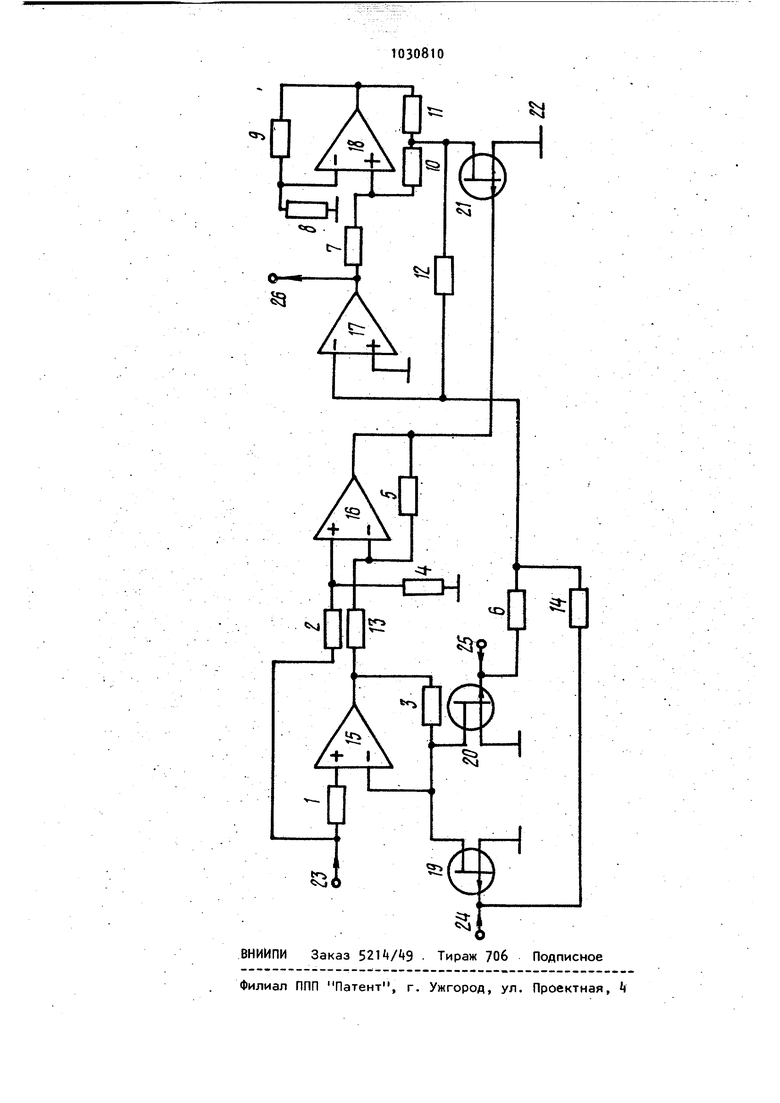

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Известно множительно-делительное устройство, содержащее ключи, блок сравнения, элементы памяти и задерж ки Cl. Недостатком этого устройства является низкое .быстродействие. Наиболее близким к изобретению является множительно-делительное устройство, содержащее операционные усилители и масштабные резисторы, к неинвертирующему входу первог операционного усилителя подключены последовательно соединенные первый и второй масштабные резисторы, а к выходу подключен третий масштабный резистор, неинвертирующкй вход второго операционного усилителя через четвертый масштабный резистор соединен с шиной нулевого потенциала, а между инвертирующим входом и его выходом подключен пятый масштабный резистор, третий и четвертый операЦионные усилители 2 J. Однако известное устройство характеризуется малым быстродействием Целью изобретения является повышение быстродействия. Для достижения цели в множительно-делительное устройство, содержащее первый, второй, третий и четвер тый операционные усилители, к неинвертирующему входу первого операционного усилителя подключен первый вывод первого масштабного резистора второй вывод которого соединен с пе вым выводом второго масштабного резистора, к выходу первого операционного усилителя подключен первый вывод третьего масштабного резистора, неинвертирующий вход второго операционного усилителя через четвертый масштабный резистор соединен с шиной нулевого потенциала, между инвертирующим входом и выходом второго опе{)ационного усилителя подключен пятый масштабный резистор, к инвертирующему входу третьего операционного усилителя подключен первьй вывод шестого масштабного резистора, к выходу третьего операционного усилителя подключен первый вывод седьмого .масштабного резистора, к инвертирующему входу четвертого операционного усилителя подключен первый вывод восьмого масштабного резистора, к выходу четвертого операционного усилителя подключен первый вывод девято.го маси1табного резистора, неинвертирующий вход четвертого операционного усилителя соединен с первым выводом десятого масштабного резистора, второй вывод которого соединен с первыми выводами одиннадцатого и двенадцатого масштабных резисторов, тринадцатый и четырнадцатый масштабные резисторы, введены первый, второй и третий элементы с управляемой проводимостью, выполненные на полевых транзисторах, истоки полевых транзисторов соединены с шиной нулевого потенциала, стоки . первого и второго полевых транзисторов, подключены к второму выводу третьего масштабного резистора и к инвертирующему входу первого операционного усилителя, выход которого через тринадцатый масштабный резистор соединен с инвертирующим входом второго операционного усилителя, выход которого подключен к затвору третьего полевого транзистора, сток которого соединен с первым выводом двенадцатого масштабного резистора, второй вывод которого подключен к инвертирующему входу.третьего операционного усилителя, неинвертирующий вход которого соединен с шиной нулевого потенциала, второй вывод седьмого масштабного резистора подключен к неинвертирующему входу чет вертого операционного усилителя, ин вертирующий вход которого соединен с вторым выводом девятого масштабного резистора, первый вывод которого соединен с вторым выводом один надцатого масштабного резистора, второй вывод восьмого масштабного резистора подключен к шине нyлeвofo потенциала, затвор первого полевого транзистора через четырнадцатый масштабный резистор соединен с первым выводом шестого масштабного резистора, второй вывод которого подключен к затвору второго полевого транзистора, второй вывод второго масштабного резистора соединен с неинвертирующим входом второго операционного усилителя, второй вывод первого масштабного резистора является первым входом устройства, затворы первого и второго полевых тран зисторов являются соответственно вт рым и третьим входами устройства, выходом которого является выход тре тьего операционного усилителя. На . чертеже изображена функционал ная схема множительно-делительного устройства.% Устройство содержит первый , второй , третий, четвертый, пятый, шестой, седьмой, восьмой, девятый,десятый , одиннадцатый, двенадцатый. тринадцатый и четырнадцатый масштаб ные резисторы 1-1, первый, второй, третий и четвертый операционные уси лители 15-18, первый, второй и трет полевые транзисторы 19-21, шину нул вого потенциала 22, первый, второй, и третий входы 23-25 и выход 2б уст ройства, Множительно-делительное устройство работает следующим образом. Первый .операционный усилитель 15 включен по схеме неинвертирующего усилителя и на его выходе напряжение определяется коэффициентом передачи, пропорциональным отношению величины сопротивления третьего масштабного резистора 3 и величины сопротивления параллельно соединенных каналов первого и второго полевых транзисторов 19 и 20. На выходе второго операционного усилителя 16 напряжение пропорционально разности сигналов на его входах. На выходе третьего операционного усилителя 17 напряжение пропорционально сумме сигналов с второго 2 и третьего 25 входов и сигнала обратной связи с третьего полевого транзистора 21. Четвертый операционный усилитель 18 включен по схеме усилителя с выходом по току с заземленной нагрузкой, которой является сопротивление канала третьего полевого транзистора 21. Ток через третий полевой транзистор 21 равен где U. - выходное напряжение третьего операционного усилителя;Rg Rg, R. сопротивления восьмого 8, девятого 9 и одиннадцатого 11 масштабных резисторов соответственно; сопротивление канала третьего полевого транзистора 21. Входной ток третьего операционного усилителя 17, вызванный действием сигналов на втором 2k и третьем 25 входах, равен Т -J:.JJj + -) (2; 1Ъ7 17 R 14 где и , и - напряжения на втором 2й и третьем 25 входах; сопротивления шестого 6 и четырнадцатого Ш масштабных резисторов соответственно. Входной ток цепи обратной связи третьего операционного усилителя 17 равен ,. где R сопротивление двенадцатого 12 масштабного резистора. В установившемся режиме токи ат сигналов на втором и третьем 25 входах и ток обратной связи равны и при равенстве сопротивлений шестого 6 и четырнадцатого 1 масштаб ных резисторов можно записать 14 ,12. Как известно, у полевых транзисторов сопротивление канала прямо пропорционально управляющему напряжению на затворе. Поэтому можно записать с учетом формулы k R где и., - выходное напряжение второго ояерационного усидите ля 16. Выходное напряжение второго операционного усилителя 16 равно П -J . f/. ) 1 13 R , V / мг -19/10 Kj-xf ..лМЛ где 0. - напряжение на первом входе 23; нигд 20 на на ше 25 ром же ств .тел 30 выс Rr ti Сопротивления третьего 3 пятого 5 и тринадцатого 13 масштабных резисторов соответственно; сопротивление параллельно 29/20 соединенных каналов первого 19 и второго 20 полевых транзисторов;. 10/10- 0,.,и О, Подставив в выражение { 5; значе(6) и (7) получим Uv,-,,() ,vUaUb Из равенства {.8 получим U,. К - коэффициент пропорциональности. Из выражения ( 8 , следует, что выходе 2б устройства формируется ряжение, пропорциональное отноию произведения напряжений на вто24 и третьем 25 входах к напряию на первом 23 входе. По сравнению с известным устройом предлагаемое множительио-делиьное устройство обладает более оким быстродействием.

Авторы

Даты

1983-07-23—Публикация

1982-04-26—Подача