Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях, компараторах и т.п.).

Известны схемы дифференциальных усилителей (ДУ) на основе двух параллельно-включенных дифференциальных каскадов с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов и выходных каскадов, выполненных по схеме с общим эмиттером [1-15]. ДУ с такой архитектурой стали основой построения многих современных операционных усилителей [1-15], в т.ч. операционных усилителей с опцией rail-to-rail (имеющих максимальную амплитуду выходного напряжения, близкую к напряжению питания). Однако такие дифференциальные усилители имеют ряд недостатков - это достаточно высокое напряжение смещения нуля Uсм (порядка сотен микровольт - единиц милливольт) и высокий температурный дрейф Uсм, связанный со структурными особенностями схемы.

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4417216, содержащий входной параллельно-балансный каскад 1, общая эмиттерная цепь 2 которого связана с первой шиной 3 источника питания через токостабилизирующий двухполюсник 4, первый токовый выход 5 входного параллельно-балансного каскада 1 связан с входом 6 токового зеркала 7, согласованного со второй шиной 8 источника питания, второй токовый выход 9 входного параллельно-балансного каскада 1 связан со входом 10 выходного каскада 11 и выходом 12 токового зеркала 7, причем выходной каскад 11 содержит входной 15 и выходной 16 транзисторы, база входного транзистора 15 соединена со входом 10 выходного каскада 11, эмиттер связан со второй шиной 8 источника питания через двухполюсник 17 и соединен с базой выходного транзистора 16, эмиттер которого подключен ко второй шине 8 источника питания, а коллектор соединен с выходом 18 выходного каскада 11 и связан со второй шиной 8 источника питания через источник тока 19.

Существенный недостаток известного дифференциального усилителя состоит в том, что он имеет относительно высокое напряжение смещения нуля Uсм и повышенную температурную нестабильность Uсм.

Основная цель предлагаемого изобретения состоит в уменьшении систематической составляющей напряжения смещения нуля Uсм и повышении его температурной стабильности.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1, общая эмиттерная цепь 2 которого связана с первой шиной 3 источника питания через токостабилизирующий двухполюсник 4, первый токовый выход 5 входного параллельно-балансного каскада 1 связан с входом 6 токового зеркала 7, согласованного со второй шиной 8 источника питания, второй токовый выход 9 входного параллельно-балансного каскада 1 связан со входом 10 выходного каскада 11 и выходом 12 токового зеркала 7, причем выходной каскад 11 содержит входной 15 и выходной 16 транзисторы, база входного транзистора 15 соединена со входом 10 выходного каскада 11, эмиттер связан со второй шиной 8 источника питания через двухполюсник 17 и соединен с базой выходного транзистора 16, эмиттер которого подключен ко второй шине 8 источника питания, а коллектор соединен с выходом 18 выходного каскада 11 и связан со второй шиной 8 источника питания через источник тока 19, предусмотрены новые элементы и связи - в схему введены первая 13 и вторая 14 цепи смещения потенциалов, первый токовый выход 5 параллельно-балансного каскада 1 связан с входом 6 токового зеркала 7 через первую 13 цепь смещения потенциалов, а второй токовый выход 9 параллельно-балансного каскада 1 связан с выходом 12 токового зеркала 7 через вторую 14 цепь смещения потенциалов, причем в схему также введен дополнительный транзистор 20, база которого соединена с первым токовым выходом 5 параллельно-балансного каскада 1, эмиттер связан с базой выходного транзистора 16 выходного каскада 11, а коллектор дополнительного транзистора 20 соединен с первой шиной 3 источника питания.

Схема заявляемого устройства показана на фиг.2. При этом в соответствии с формулой изобретения выходной каскад 11 содержит входной 15 и выходной 16 транзисторы, база входного транзистора 15 соединена со входом 10 выходного каскада 11, эмиттер соединен со второй шиной 8 источника питания через двухполюсник 17 и связан с базой выходного транзистора 16, эмиттер которого подключен ко второй шине 8 источника питания, а коллектор соединен с выходом 18 выходного каскада 11 и связан со второй шиной 8 источника питания через источник тока 19.

Кроме этого в схему введен дополнительный транзистор 20, база которого соединена с первым токовым выходом 5 параллельно-балансного каскада 1, эмиттер связан с базой 21 выходного транзистора 16 выходного каскада 11, а коллектор дополнительного транзистора 20 согласован с первой шиной 3 источника питания. За счет введения дополнительного транзистора 20 повышается стабильность работы выходного каскада 11 и дифференциального усилителя в целом.

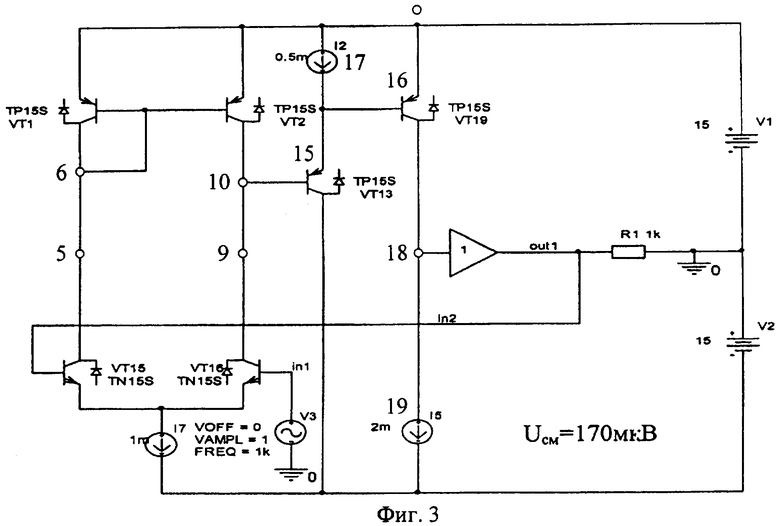

На фиг.3 в среде PSpice показана схема ДУ-прототипа фиг.1, которая исследовалась авторами при определении зависимости напряжения смещения нуля Uсм (170 мкВ при 27°С) от температуры.

На фиг.4 показана схема заявляемого дифференциального усилителя (фиг.2), которая также исследовалась авторами в среде PSpice при определении зависимости напряжения смещения нуля Uсм (2,6 мкВ при 27°С) от температуры. Исследования проводились на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На графике фиг.5 показаны зависимости напряжения смещения нуля Uсм от температуры, полученные при исследовании авторами схем прототипа и заявляемого дифференциального усилителя.

Дифференциальный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, общая эмиттерная цепь 2 которого связана с первой шиной 3 источника питания через токостабилизирующий двухполюсник 4, первый токовый выход 5 входного параллельно-балансного каскада 1 связан с входом 6 токового зеркала 7, согласованного со второй шиной 8 источника питания, второй токовый выход 9 входного параллельно-балансного каскада 1 связан со входом 10 выходного каскада 11 и выходом 12 токового зеркала 7, причем выходной каскад 11 содержит входной 15 и выходной 16 транзисторы, база входного транзистора 15 соединена со входом 10 выходного каскада 11, эмиттер связан со второй шиной 8 источника питания через двухполюсник 17 и соединен с базой выходного транзистора 16, эмиттер которого подключен ко второй шине 8 источника питания, а коллектор соединен с выходом 18 выходного каскада 11 и связан со второй шиной 8 источника питания через источник тока 19. В схему введены первая 13 и вторая 14 цепи смещения потенциалов, причем первый токовый выход 5 параллельно-балансного каскада 1 связан с входом 6 токового зеркала 7 через первую 13 цепь смещения потенциалов, а второй токовый выход 9 параллельно-балансного каскада 1 связан с выходом 12 токового зеркала 7 через вторую 14 цепь смещения потенциалов. В схему также введен дополнительный транзистор 20, база которого соединена с первым токовым выходом 5 параллельно-балансного каскада 1, эмиттер связан с базой выходного транзистора 16 выходного каскада 11, а коллектор дополнительного транзистора 20 соединен с первой шиной 3 источника питания.

Рассмотрим работу ДУ фиг.2.

Одной из доминирующих причин, влияющих на статические параметры современных транзисторных дифференциальных усилителей, является эффект Эрли, связанный с влиянием величины напряжения коллектор-эмиттер (Uкэ) или коллектор-база (Uкб) на входные характеристики транзисторов. Данный фактор недооценивается в современной технической литературе, что приводит к существенным ошибкам при проектировании микросхем.

В предлагаемом техническом решении за счет введения элементов 13 и 14 формируются условия, при которых эффект Эрли создает в эмиттерных переходах транзисторов дифференциального каскада 1 и транзисторах токового зеркала 7 противоположные по знаку, но компенсирующие друг друга смещения входных характеристик. Это позволяет за счет симметрирования напряжений

минимизировать влияние внутренней обратной связи в транзисторах схемы на основные статические параметры ДУ: Uсм, коэффициент ослабления входных синфазных сигналов, температурный дрейф Uсм и т.д. В зависимости от числа р-n переходов во входной цепи выходного каскада 11 число р-n переходов в элементах смещения 13 и 14 может меняться. Так, при использовании в схеме ДУ выходного каскада 11 по патенту США №4417216 элементы 13 и 14 должны содержать не по одному, а по два р-n перехода. Таким образом, входной каскад схемы фиг.2 несмотря на асимметрию архитектуры обладает высокой симметрией статического режима.

Дополнительным фактором, улучшающим систематическую составляющую Uсм, является введение транзистора 20, ток базы которого Iб компенсирует входной ток буферного усилителя 11.

Предлагаемая система мер создает условия для уменьшения Uсм и его температурного дрейфа.

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва) (фиг.4, фиг.5) - заявляемый ДУ имеет более, чем на порядок меньшее напряжение смещения нуля (2,6 мкВ), обусловленное структурными особенностями схемы (без учета разброса параметров элементов), и значительно лучшую температурную стабильность Uсм.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4417216 (прототип).

2. Патент Японии 2004040157.

3. Патентная заявка США №2004/0061544.

4. Патентная заявка США №2003/0155959.

5. Патентная заявка США №2003/0141919.

6. Патент США №6292033.

7. Патент США №5936468.

8. Патент США №4866397.

9. Патент США №4331929.

10. Патент DE №10321442.

11. Патент США №6262628.

12. Патент США №6172551.

13. Патент США №5461342.

14. Патент США №5373741.

15. Патент США №6917257.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2412528C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412539C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401508C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402156C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ И ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2010 |

|

RU2426221C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ), компараторах и т.п.). Дифференциальный усилитель с низковольтным питанием, содержащий входной параллельно-балансный каскад (1), общая эмиттерная цепь (2) которого связана с первой шиной (3) источника питания через токостабилизирующий двухполюсник (4), первый токовый выход (5) входного параллельно-балансного каскада (1) связан с входом (6) токового зеркала (7), согласованного со второй шиной (8) источника питания, второй токовый выход (9) входного параллельно-балансного каскада (1), связанный со входом (10) выходного каскада (11) и выходом (12) токового зеркала (7). В схему введены первая (13) и вторая (14) цепи смещения потенциалов, причем первый токовый выход (5) параллельно-балансного каскада (1) связан с входом (6) токового зеркала (7) через первую (13) цепь смещения потенциалов, а второй токовый выход (9) параллельно-балансного каскада (1) связан с выходом (12) токового зеркала (7) через вторую (14) цепь смещения потенциалов. Технический результат - повышение температурной стабильности. 5 ил.

Дифференциальный усилитель с низковольтным питанием, содержащий входной параллельно-балансный каскад (1), общая эмиттерная цепь (2) которого связана с первой шиной (3) источника питания через токостабилизирующий двухполюсник (4), первый токовый выход (5) входного параллельно-балансного каскада (1) связан с входом (6) токового зеркала (7), согласованного со второй шиной (8) источника питания, второй токовый выход (9) входного параллельно-балансного каскада (1) связан со входом (10) выходного каскада (11) и выходом (12) токового зеркала (7), причем выходной каскад (11) содержит входной (15) и выходной (16) транзисторы, база входного транзистора (15) соединена с входом (10) выходного каскада (11), эмиттер связан с второй шиной (8) источника питания через двухполюсник (17) и соединен с базой выходного транзистора (16), эмиттер которого подключен ко второй шине (8) источника питания, а коллектор - соединен с выходом (18) выходного каскада (11) и связан с второй шиной (8) источника питания через источник тока (19), отличающийся тем, что в схему введены первая (13) и вторая (14) цепи смещения потенциалов, первый токовый выход (5) параллельно-балансного каскада (1) связан с входом (6) токового зеркала (7) через первую (13) цепь смещения потенциалов, а второй токовый выход (9) параллельно-балансного каскада (1) связан с выходом (12) токового зеркала (7) через вторую (14) цепь смещения потенциалов, причем в схему также введен дополнительный транзистор (20), база которого соединена с первым токовым выходом (5) параллельно-балансного каскада (1), эмиттер связан с базой выходного транзистора (16) выходного каскада (11), а коллектор дополнительного транзистора (20) соединен с первой шиной (3) источника питания.

| JP 91095763 A, 22.04.1997 | |||

| Операционный усилитель | 1983 |

|

SU1193773A1 |

Авторы

Даты

2009-02-10—Публикация

2008-02-01—Подача