Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных решающих усилителях с малыми значениями э.д.с. смещения нуля).

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ на базе «перегнутых» каскодов [1-18], получившие широкое применение в микроэлектронных изделиях. Предлагаемое изобретение относится к данному типу ОУ.

Наиболее близким по технической сущности к заявляемому ОУ является классическая схема ОУ, фиг.1, представленная в патенте фирмы Analog Devices №6483382, fig.1, fig.2, которая также присутствует в других патентах [1-18].

Существенный недостаток известного ОУ, фиг.1, состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля Uсм.

Основная задача предлагаемого изобретения состоит в уменьшении напряжения смещения нуля Uсм.

Поставленная цель достигается тем, что в дифференциальном операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, первый коллекторный выход 2 соединен с эмиттером первого 4 выходного транзистора, эмиттеры первого 4 и второго 5 выходных транзисторов через первый 6 и второй 7 токостабилизирующие двухполюсники связаны с шиной источника питания 8, цепь смещения потенциалов 9, связанную с объединенными базами первого 4 и второго 5 выходных транзисторов, токовое зеркало 10, вход которого подключен к коллектору первого 4 выходного транзистора, а выход соединен с коллектором второго 5 выходного транзистора и базой транзистора 11 выходного буферного усилителя 12, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 16, база которого соединена с цепью смещения потенциалов 9, коллектор подключен к эмиттеру второго 5 выходного транзистора, а эмиттер соединен со вторым 3 токовым выходом входного дифференциального каскада 1.

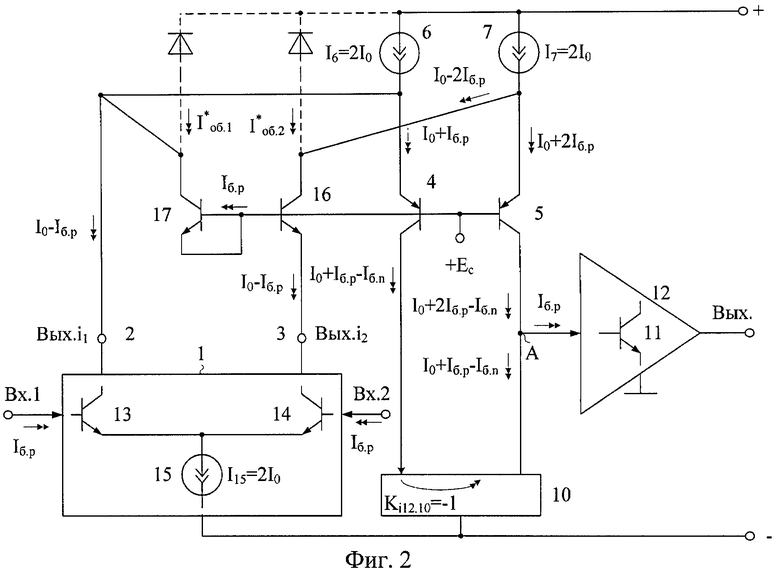

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

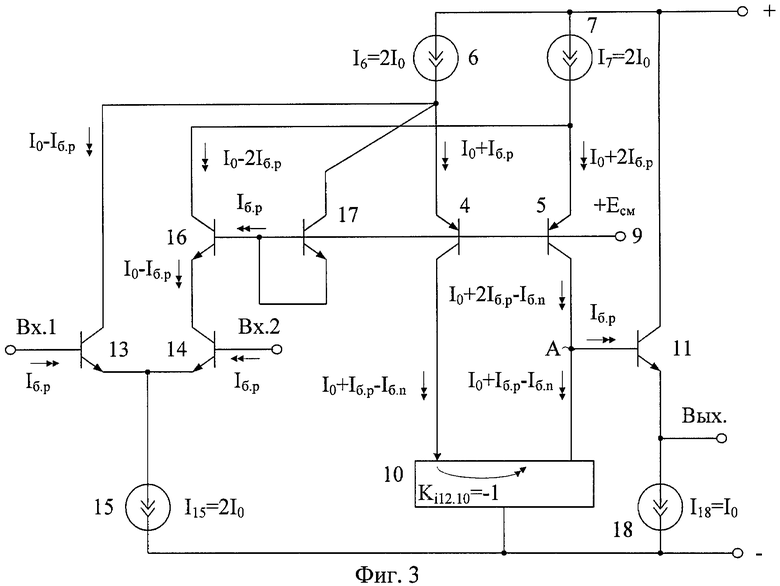

На фиг.3 показана схема фиг.2 в соответствии с п.1 формулы изобретения и конкретным выполнением выходного эмиттерного повторителя 12.

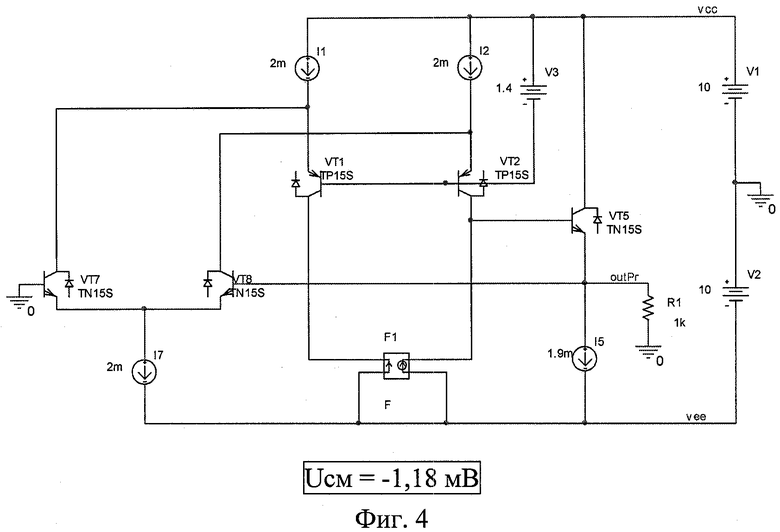

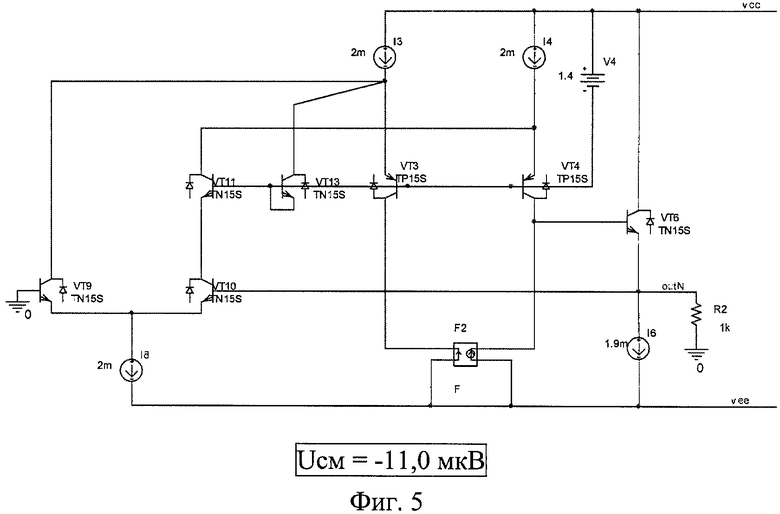

На фиг.4 и 5 показаны схемы дифференциального усилителя-прототипа (фиг.4) и заявляемого ОУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

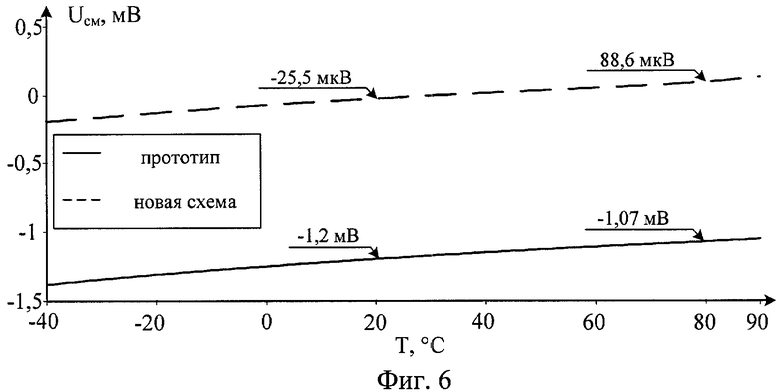

На фиг.6 показаны результаты компьютерного моделирования схем фиг.4 и фиг.5 - зависимость напряжения смещения нуля Uсм от температуры.

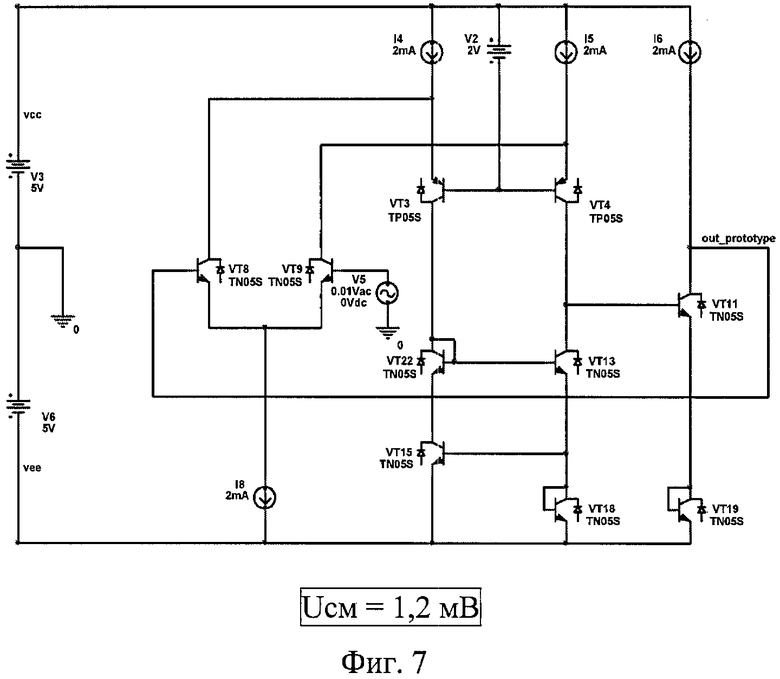

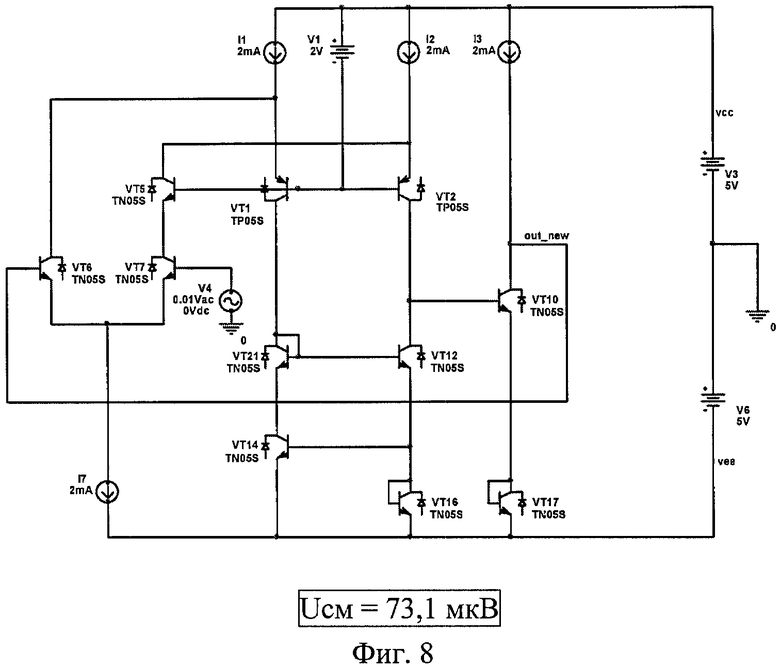

На фиг.7 и 8 представлены варианты практической реализации в среде PSpice известного (фиг.7) и заявляемого (фиг.8) ОУ, фиг.2, с конкретным выполнением токового зеркала 10 (по схеме Вильсона) и выходного буферного усилителя 12 в виде каскада с общим эмиттером.

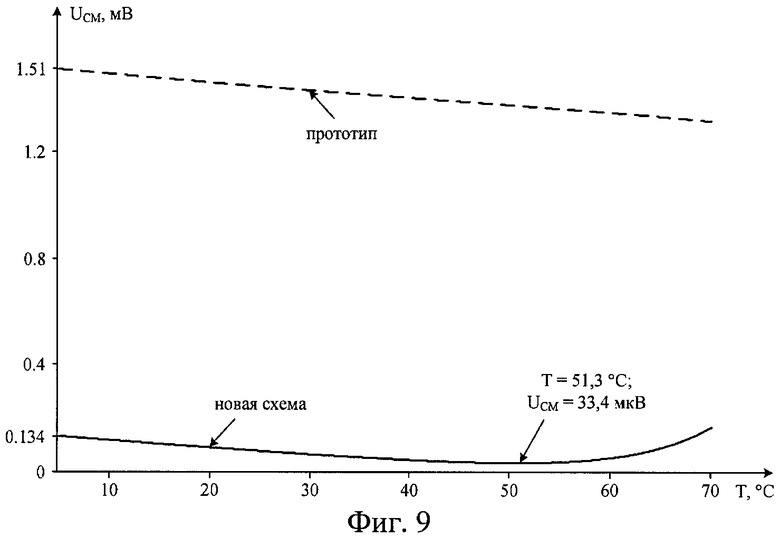

Графики фиг.9 характеризуют температурную зависимость напряжения смещения нуля схем фиг.7 и 8.

Дифференциальный операционный усилитель, фиг.2, содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, первый коллекторный выход 2 соединен с эмиттером первого 4 выходного транзистора, эмиттеры первого 4 и второго 5 выходных транзисторов через первый 6 и второй 7 токостабилизирующие двухполюсники связаны с шиной источника питания 8, цепь смещения потенциалов 9, связанную с объединенными базами первого 4 и второго 5 выходных транзисторов, токовое зеркало 10, вход которого подключен к коллектору первого 4 выходного транзистора, а выход соединен с коллектором второго 5 выходного транзистора и базой транзистора 11 выходного буферного усилителя 12. Дифференциальный каскад 1 выполнен на транзисторах 13, 14 и двухполюснике 15. В схему введен дополнительный транзистор 16, база которого соединена с цепью смещения потенциалов 9, коллектор подключен к эмиттеру второго 5 выходного транзистора, а эмиттер соединен со вторым 3 токовым выходом входного дифференциального каскада 1. В схеме фиг.4 выходной буферный усилитель выполнен на транзисторе 11 и двухполюснике 18.

На фиг.2 и 3, в соответствии с п.2 формулы изобретения, в схему введен транзистор терморадиационной компенсации 17, коллектор которого подключен к эмиттеру первого 4 выходного транзистора.

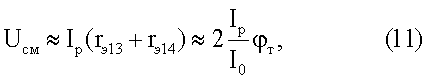

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.3.

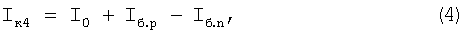

Если ток двухполюсника 15 равен 2I0, то токи коллекторов транзисторов 13 и 14, 16, 4 и 5:

где Iб.i=Iэ.i/βi - ток базы i-го n-p-n (Iб.р) или p-n-p (Iб.n) транзистора при эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления но току базы i-го транзистора.

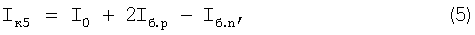

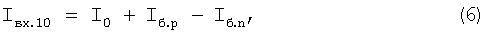

Поэтому входной (Iвх.10) и выходной (Iвых.10) токи токового зеркала 10

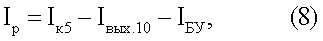

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где IБУ=Iб.р - ток базы n-p-n транзистора 11 буферного усилителя 12. Подставляя (1)÷(7) в (8) находим, что разностный ток, определяющий Uсм ДУ:

Как следствие, при Iр=0 не требуется смещения нуля ДУ, фиг.2, на величину Uсм, подача которого на его входы Bx.(+)1, Bx.(-)2 компенсирует разностный ток Iр в узле «А».

Таким образом, в заявляемом устройстве уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного дифференциального напряжения uвх ДУ в выходной ток узла «А»:

где rэ13=rэ14 - сопротивления эмиттерных переходов входных транзисторов 13 и 14 дифференциального каскада 1.

Поэтому для схем фиг.1-3

где φт,=26 мВ - температурный потенциал.

В ДУ-прототипе Ip-Iб.р≠0, поэтому здесь систематическая составляющая Uсм получается более чем на порядок больше (Uсм=-1,18 мВ), чем в заявляемой схеме (Uсм=-11,0 мкВ) (фиг.4-9).

Компьютерное моделирование схем фиг.4 подтверждает данные теоретические выводы (фиг.6, 9).

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5091701, fig.1.

2. Патент США №6448853, fig.6.

3. Патент США №6529076.

4. Патент США №5327100, fig.2.

5. Патентная заявка США 2002/0196079 fig.1.

6. Патент США №5734296, fig.3.

7. Патентная заявка США 2003/0090321 fig.8.

8. Патент США №6710654.

9. Патент США №6483382, fig.2.

10. Патентная заявка США 2006/0202762.

11. Патент США №5140280, fig.1.

12. Патент США №4600893, fig.7.

13. Патент США №6788143.

14. Патент США №6734720, fig.1.

15. Патентная заявка США 2008/0186091, fig.4.

16. Патентная заявка США 2007/0069815.

17. Патент США №6304143, fig.3.

18. Патент Англии GB 2035003.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411635C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416155C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416151C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412532C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412537C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412539C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412540C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях (ОУ) с малыми значениями э.д.с. смещения нуля). Технический результат: уменьшение напряжения смещения нуля. Дифференциальный операционный усилитель содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) коллекторными выходами, первый коллекторный выход (2) соединен с эмиттером первого (4) выходного транзистора (Т), эмиттеры первого (4) и второго (5) выходных Т через первый (6) и второй (7) токостабилизирующие двухполюсники связаны с шиной источника питания (8), цепь смещения потенциалов (9), связанную с объединенными базами Т (4) и Т (5), токовое зеркало (10), вход которого подключен к коллектору Т (4), а выход соединен с коллектором Т (5) и базой Т (11) выходного буферного усилителя (12). В схему введен дополнительный Т (16), база которого соединена с цепью смещения потенциалов (9), коллектор подключен к эмиттеру Т (5), а эмиттер соединен со вторым (3) токовым выходом входного ДК (1). 1 з.п. ф-лы, 9 ил.

1. Дифференциальный операционный усилитель с малым напряжением смещения нуля, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) коллекторными выходами, первый коллекторный выход (2) соединен с эмиттером первого (4) выходного транзистора, эмиттеры первого (4) и второго (5) выходных транзисторов через первый (6) и второй (7) токостабилизирующие двухполюсники связаны с шиной источника питания (8), цепь смещения потенциалов (9), связанную с объединенными базами первого (4) и второго (5) выходных транзисторов, токовое зеркало (10), вход которого подключен к коллектору первого (4) выходного транзистора, а выход соединен с коллектором второго (5) выходного транзистора и базой транзистора (11) выходного буферного усилителя (12), отличающийся тем, что в схему введен дополнительный транзистор (16), база которого соединена с цепью смещения потенциалов (9), коллектор подключен к эмиттеру второго (5) выходного транзистора, а эмиттер соединен со вторым (3) токовым выходом входного дифференциального каскада (1).

2. Устройство по п.1, отличающееся тем, что в схему введен транзистор терморадиационной компенсации (17), коллектор которого подключен к эмиттеру первого (4) выходного транзистора.

| US 6483382 B1, 19.11.2002 | |||

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| US 4533844 А, 06.08.1985 | |||

| US 6011431 А, 04.01.2000. | |||

Авторы

Даты

2010-10-20—Публикация

2009-07-29—Подача