Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях (ОУ) с малыми значениями э.д.с. смещения нуля).

В современной радиоэлектронной аппаратуре находят применение операционные усилители с существенными различными параметрами. Особое место занимают ОУ на базе каскодных параллельно-балансных каскадов [1-12], получившие широкое применение в микроэлектронных изделиях. Предлагаемое изобретение относится к данному типу ОУ.

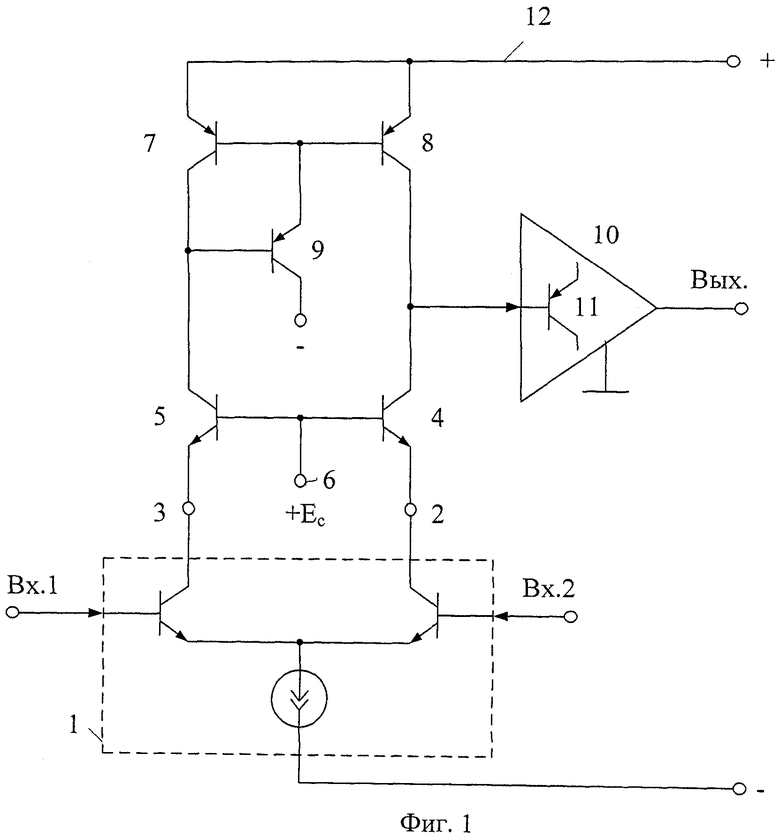

Наиболее близким по технической сущности к заявляемому ОУ является классическая схема ОУ (фиг.1), представленная в монографии Полонникова Д.Е «Операционные усилители: Принципы построения, теория, схемотехника», стр.94, рис.3.9, которая также присутствует во многих патентах [1-12].

Существенный недостаток известного ОУ (фиг.1) состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм).

Основная задача предлагаемого изобретения состоит в уменьшении Uсм.

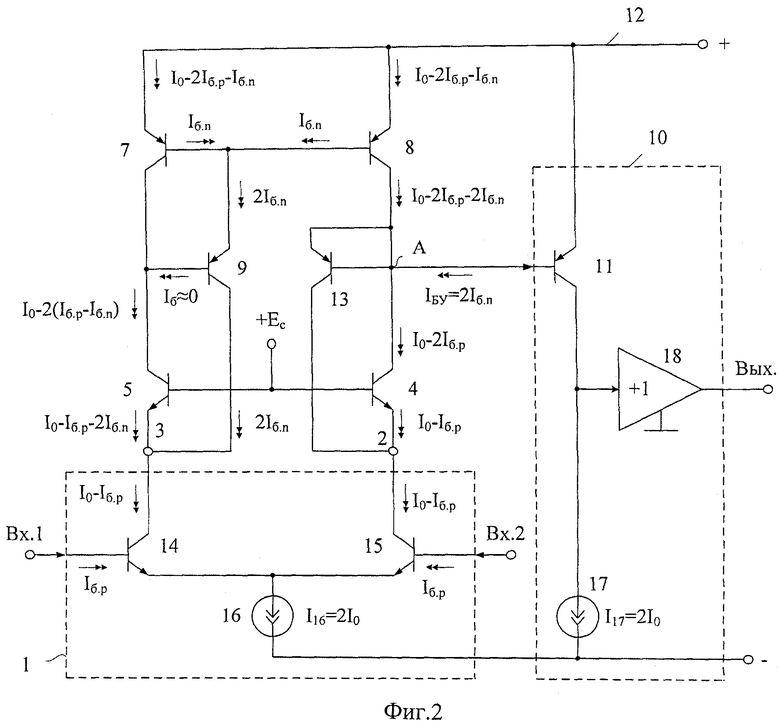

Поставленная задача достигается тем, что в дифференциальном операционном усилителе (фиг.1), содержащем входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с эмиттерами первого 4 и второго 5 выходных транзисторов, базы которых объединены и подключены к цепи смещения потенциалов 6, третий 7 и четвертый 8 выходные транзисторы, базы которых объединены и подключены к эмиттеру вспомогательного транзистора 9, выходной буферный усилитель 10 на основе входного транзистора 11, тип проводимости которого совпадает с типом проводимости вспомогательного транзистора 9, причем вход буферного усилителя 10 соединен с объединенными коллекторами первого 4 и четвертого 8 выходных транзисторов, база вспомогательного транзистора 9 подключена к объединенным коллекторам второго 5 и третьего 7 выходных транзисторов, а эмиттеры третьего 7 и четвертого 8 выходных транзисторов связаны с шиной источника питания 12, предусмотрены новые элементы и связи - коллектор вспомогательного транзистора 9 соединен с эмиттером второго 5 выходного транзистора.

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

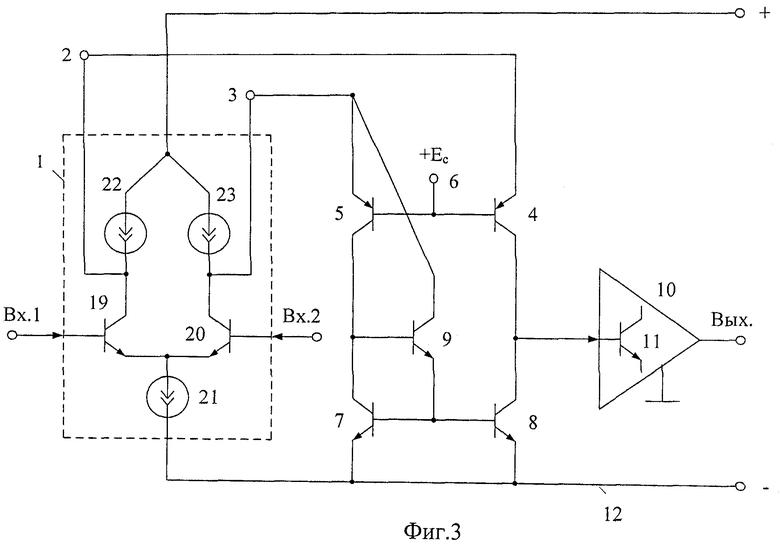

На фиг.3 показана схема фиг.2 с другим вариантом построения входного параллельно-балансного каскада 1, соответствующая п.1 формулы изобретения.

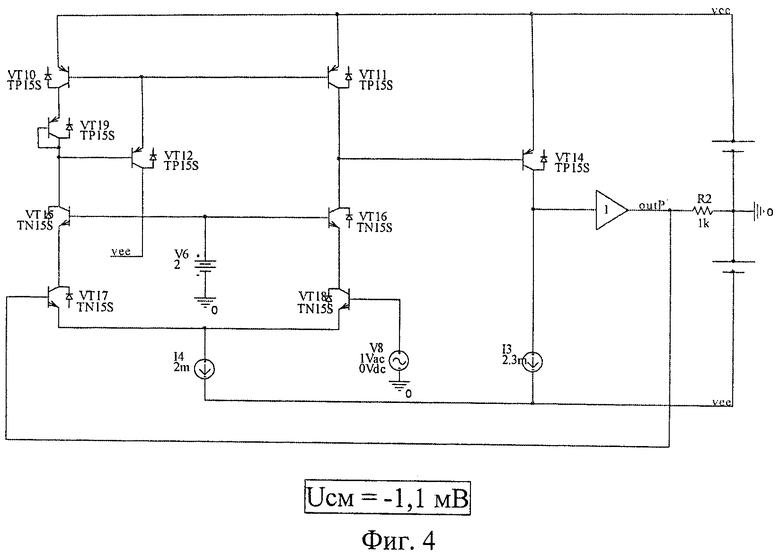

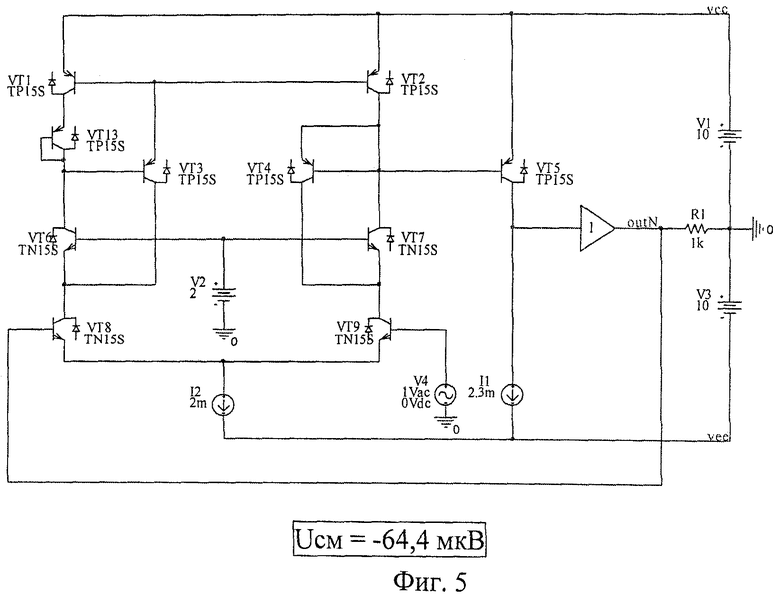

На фиг.4 - фиг.5 приведены схемы дифференциального усилителя-прототипа (фиг.4) и заявляемого ОУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

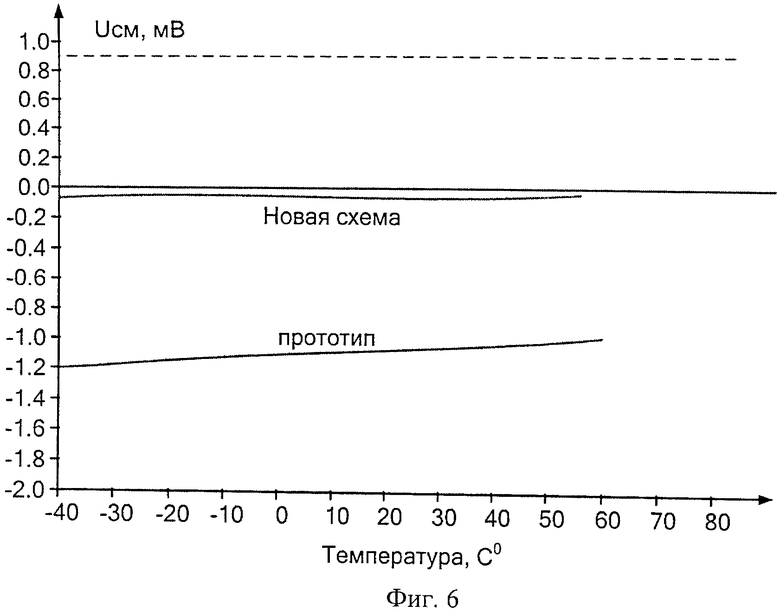

На фиг.6 показаны результаты компьютерного моделирования схем фиг.4 и фиг.5 - зависимость напряжения смещения нуля Uсм от температуры.

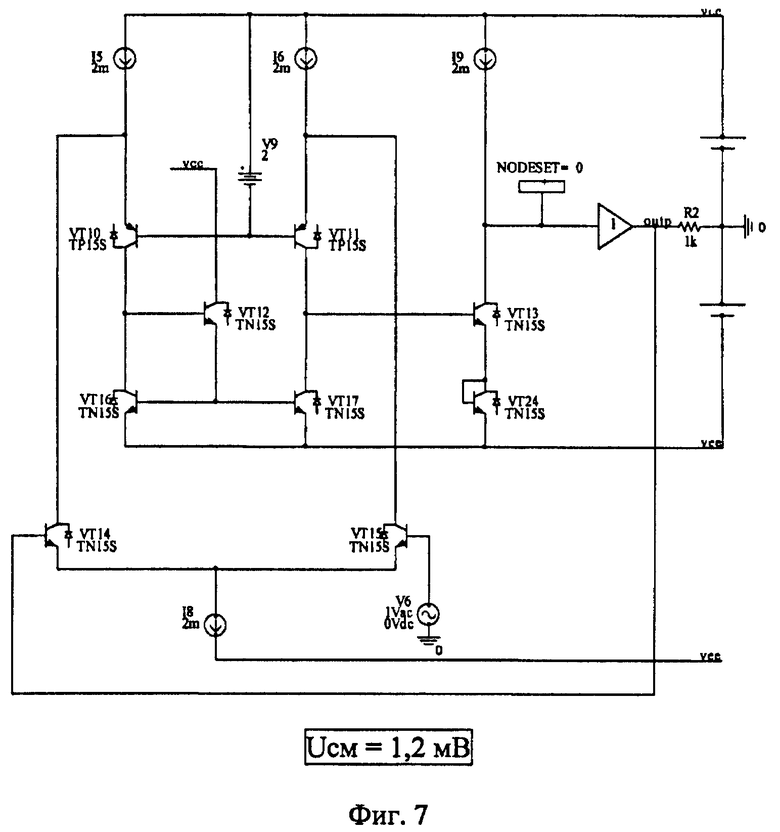

На фиг.7 приведена схема фиг.1 в среде компьютерного моделирования PSpice для случая, когда его выходная подсхема реализована на основе «перегнутого» каскода (фиг.3).

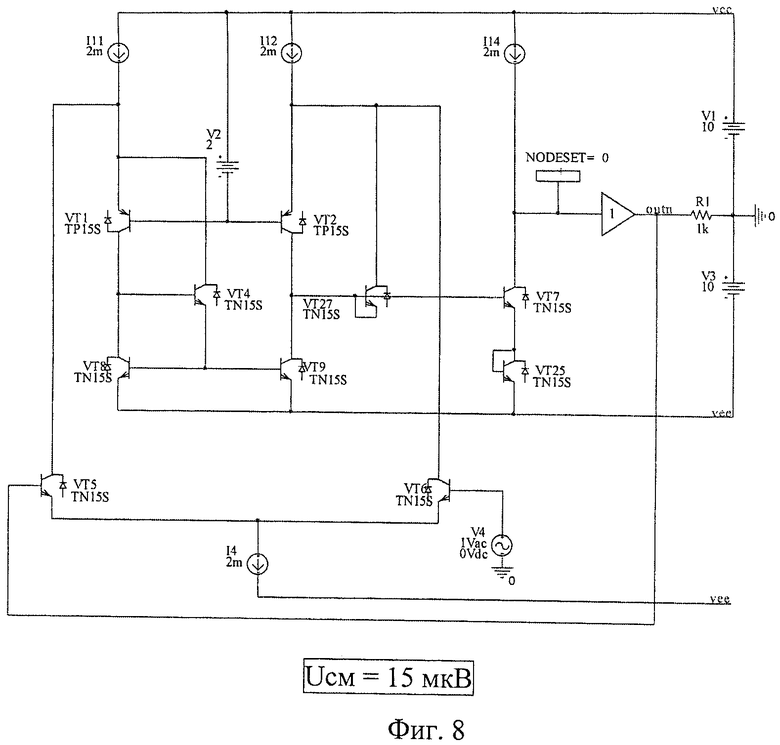

На фиг.8 показана схема фиг.3 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

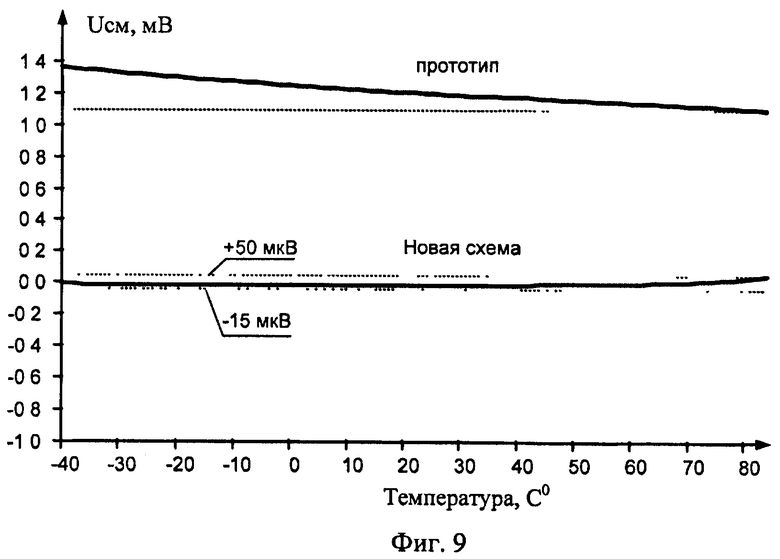

На фиг.9 показаны результаты компьютерного моделирования схем фиг.7 и фиг.8 - зависимость напряжения смещения нуля Uсм от температуры.

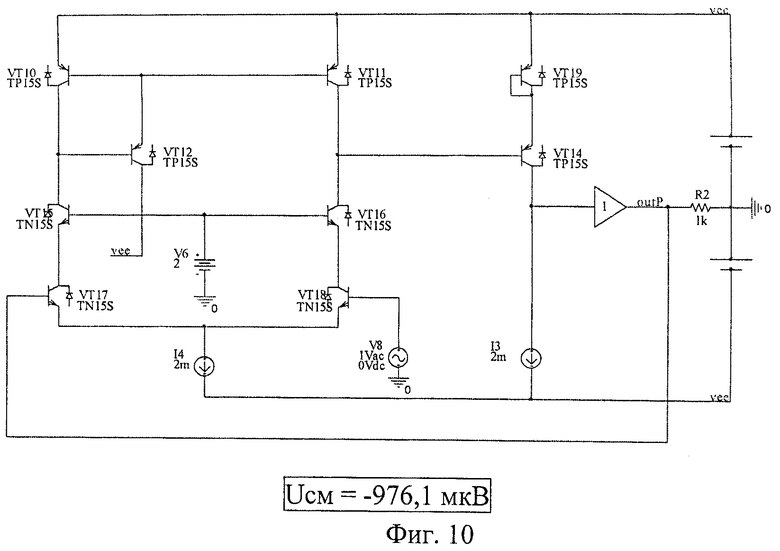

На фиг.10 приведена схема прототипа фиг.1 в среде компьютерного моделирования PSpice.

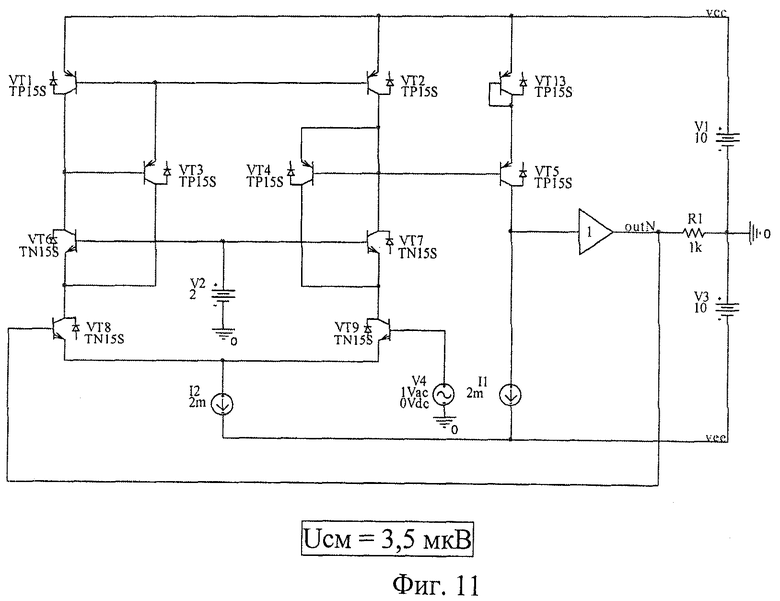

На фиг.11 показана схема заявляемого устройства фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

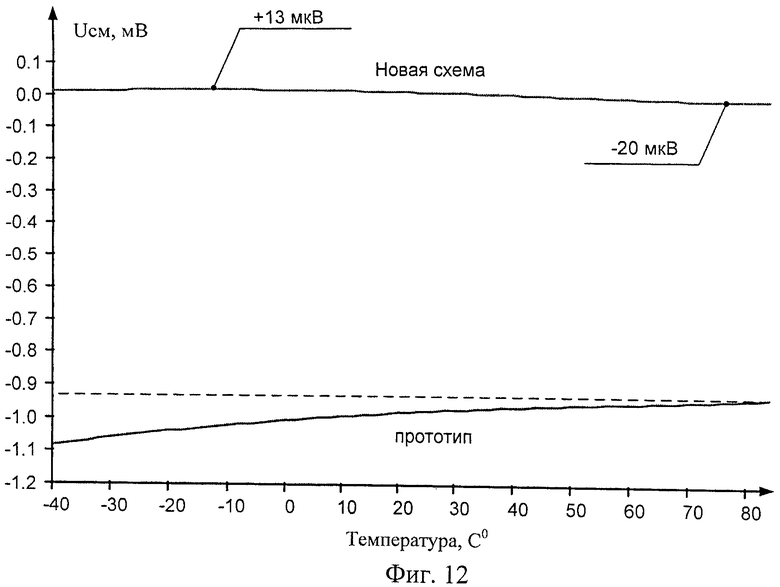

На фиг.12 показаны результаты компьютерного моделирования схем фиг.10 и фиг.11 - зависимость напряжения смещения нуля Uсм от температуры.

Фиг.7 - фиг.12 предоставляют дополнительные сведения о преимуществах заявляемого устройства в частных вариантах его исполнения и носят вспомогательный характер.

Каскодный дифференциальный операционный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, первый 2 и второй 3 токовые выходы которого связаны с эмиттерами первого 4 и второго 5 выходных транзисторов, базы которых объединены и подключены к цепи смещения потенциалов 6, третий 7 и четвертый 8 выходные транзисторы, базы которых объединены и подключены к эмиттеру вспомогательного транзистора 9, выходной буферный усилитель 10 на основе входного транзистора 11, тип проводимости которого совпадает с типом проводимости вспомогательного транзистора 9, причем вход буферного усилителя 10 соединен с объединенными коллекторами первого 4 и четвертого 8 выходных транзисторов, база вспомогательного транзистора 9 подключена к объединенным коллекторам второго 5 и третьего 7 выходных транзисторов, а эмиттеры третьего 7 и четвертого 8 выходных транзисторов связаны с шиной источника питания 12. Коллектор вспомогательного транзистора 9 соединен с эмиттером второго 5 выходного транзистора.

На фиг.2, в соответствии с п.2 формулы изобретения, в схему введен транзистор 13 терморадиационной компенсации, коллектор которого связан с эмиттером первого 4 выходного транзистора.

В схеме фиг.2 входной каскад 1 реализован на основе транзисторов 14, 15 и токостабилизирующего двухполюсника 16, а буферный усилитель 10 содержит двухполюсник 17 и повторитель 18.

В схеме фиг.3 входной параллельно-балансный каскад 1 реализован по классической схеме на базе транзисторов 19, 20 и двухполюсников 21, 22 и 23.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2.

Если ток двухполюсника 16 равен 2I0, то токи коллекторов транзисторов 14, 15 и токи эмиттеров и коллекторов транзисторов 5 и 6:

где Iб.i,=Iэi/βi - ток базы р-n-р (Iбn) или n-p-n (Iбp) транзистора при эмиттерном токе Iэi≈I0;

βi - коэффициент усиления по току базы i-го транзистора.

Поэтому коллекторный ток транзистора 8

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где IБУ=2Iбp - ток базы n-р-n транзистора 11 буферного усилителя 10. Подставляя (1)-(7) в (8) находим, что разностный ток, определяющий Uсм ДУ, равен нулю: Iр=0.

Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного дифференциального напряжения uвx ДУ в выходной ток узла «А»:

где rэ14=rэ15 - сопротивления эмиттерных переходов входных транзисторов 14 и 15 дифференциального каскада 1.

Поэтому для схем фиг.1 - фиг.2

где φт=26 мВ - температурный потенциал.

В ДУ-прототипе Iр≠0, поэтому здесь систематическая составляющая Uсм получается на один-два порядка больше, чем в заявляемой схеме.

Компьютерное моделирование (фиг.6, фиг.9, фиг.12) сравниваемых схем подтверждает данные теоретические выводы.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Литература

1. Патент США №6.114.234.

2. Патент США №5.091.701, fig.1.

3. Патент США №5.140.280.

4. Патент США №5.786.729.

5. Патент США №6.448.853.

6. Патент США №4.390.850.

7. Патент США №5.327.100 fig.2.

8. Патент США №6.4383.382 fig.2, fig.1.

9. Патент США №5.374.897.

10. Патент США №6.529.076.

11. Патент США №5.627.495 fig.2.

12. Патент Франции №2.227.574 fig.1, fig.3c, fig.4a.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2402151C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402871C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411636C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402870C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390916C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2368066C1 |

Изобретение относится к радиотехнике и связи для усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат: уменьшение напряжения смещения нуля. Каскодный дифференциальный операционный усилитель содержит входной параллельно-балансный каскад (1), первый (2) и второй (3) токовые выходы которого связаны с эмиттерами первого (4) и второго (5) выходных транзисторов (Т), базы которых объединены и подключены к цепи смещения потенциалов (6), третий (7) и четвертый (8) выходные Т, базы которых объединены и подключены к эмиттеру вспомогательного Т (9), выходной буферный усилитель (БУ) (10) на основе входного Т (11), тип проводимости которого совпадает с типом проводимости вспомогательного Т (9), причем вход БУ (10) соединен с объединенными коллекторами первого Т (4) и четвертого Т (8), база вспомогательного Т (9) подключена к объединенным коллекторам второго Т (5) и третьего Т (7), а эмиттеры третьего Т (7) и четвертого Т (8) связаны с шиной источника питания (12). Коллектор вспомогательного Т (9) соединен с эмиттером второго Т (5). 1 з.п. ф-лы, 12 ил.

1. Каскодный дифференциальный операционный усилитель с малым напряжением смещения нуля, содержащий входной параллельно-балансный каскад (1), первый (2) и второй (3) токовые выходы которого связаны с эмиттерами первого (4) и второго (5) выходных транзисторов, базы которых объединены и подключены к цепи смещения потенциалов (6), третий (7) и четвертый (8) выходные транзисторы, базы которых объединены и подключены к эмиттеру вспомогательного транзистора (9), выходной буферный усилитель (10) на основе входного транзистора (11), тип проводимости которого совпадает с типом проводимости вспомогательного транзистора (9), причем вход буферного усилителя (10) соединен с объединенными коллекторами первого (4) и четвертого (8) выходных транзисторов, база вспомогательного транзистора (9) подключена к объединенным коллекторам второго (5) и третьего (7) выходных транзисторов, а эмиттеры третьего (7) и четвертого (8) выходных транзисторов связаны с шиной источника питания (12), отличающийся тем, что коллектор вспомогательного транзистора (9) соединен с эмиттером второго (5) выходного транзистора.

2. Устройство по п.1, отличающееся тем, что в схему введен транзистор (13) терморадиационной компенсации, коллектор которого связан с эмиттером первого (4) выходного транзистора.

| US 3614645 А, 19.10.1971 | |||

| Компенсационный стабилизатор постоянного напряжения | 1981 |

|

SU922698A1 |

| Операционный усилитель | 1980 |

|

SU970638A1 |

| Операционный усилитель | 1986 |

|

SU1446689A1 |

Авторы

Даты

2011-02-20—Публикация

2009-08-11—Подача