Самосинхронный D-триггер относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен D-триггер [1], содержащий шесть элементов И-НЕ.

Недостаток известного устройства - отсутствие средств индикации окончания переходных процессов.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является D-триггер [2], содержащий два однотактных триггера с парафазным кодированием информационных входов и выходов.

Недостаток прототипа - работа только с данными, представленными в парафазном коде, что не позволяет использовать его в качестве элемента интерфейса между синхронными и самосинхронными схемами

Задача, решаемая в изобретении, заключается в обеспечении самосинхронной реализации D-триггера с однофазным входом данных и парафазным выходом без спейсера, хранящим свое состояние до следующей операции записи в него нового состояния.

Это достигается тем, что в D-триггере, содержащем два однотактных триггера, информационный вход, управляющий вход, вход обнуления, прямой и инверсный информационные выходы и индикаторный выход, введены инверторы на входах: информационном и управляющем, а также изменено устройство индикации окончания переходных процессов в триггере, реализованное на трех элементах И-ИЛИ-НЕ, элементе ИЛИ-НЕ и инверторе, первый однотактный триггер реализован на двух элементах И-ИЛИ-НЕ, а второй однотактный триггер реализован на двух элементах ИЛИ-И-НЕ, информационный вход подключен ко входу первого инвертора, третьему входу первой группы входов И второго элемента И-ИЛИ-НЕ, первому входу элемента ИЛИ-НЕ и второму входу третьей группы входов И четвертого элемента И-ИЛИ-НЕ, управляющий вход подключен ко входу второго инвертора и второму входу элемента ИЛИ-НЕ, вход обнуления подключен ко второму входу второй группы входов И второго элемента И-ИЛИ-НЕ, выход первого инвертора подключен к первому входу первой группы входов И первого элемента И-ИЛИ-НЕ и первому входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход второго инвертора подключен ко вторым входам первых групп И первого и второго элементов И-ИЛИ-НЕ, вторым входам первых групп ИЛИ первого и второго элементов ИЛИ-И-НЕ, входу третьей группы входов И третьего элемента И-ИЛИ-НЕ, третьему входу третьей группы входов И четвертого элемента И-ИЛИ-НЕ и второму входу четвертой группы входов И четвертого элемента И-ИЛИ-НЕ, выход элемента ИЛИ-НЕ подключен к первому входу первой группы входов И и третьему входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ, первому входу второй группы входов И второго элемента И-ИЛИ-НЕ, первому входу первой группы входов И третьего элемента И-ИЛИ-НЕ и первому входу третьей группы входов И четвертого элемента И-ИЛИ-НЕ, выход второго элемента И-ИЛИ-НЕ подключен к входу второй группы входов И первого элемента И-ИЛИ-НЕ, первому входу первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ, второму входу второй группы входов И третьего элемента И-ИЛИ-НЕ и второму входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход первого элемента ИЛИ-И-НЕ подключен к инверсному информационному выходу триггера, входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ и второму входу первой группы входов И третьего элемента И-ИЛИ-НЕ, выход второго элемента ИЛИ-И-НЕ подключен к прямому информационному выходу триггера, входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и первому входу второй группы входов И третьего элемента И-ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ подключен к первым входам первой и второй групп входов И пятого элемента И-ИЛИ-НЕ, выход четвертого элемента И-ИЛИ-НЕ подключен ко вторым входам первой и третьей групп входов И пятого элемента И-ИЛИ-НЕ, третьему входу первой группы входов И первого элемента И-ИЛИ-НЕ и первому входу первой группы входов И второго элемента И-ИЛИ-НЕ, выход пятого элемента И-ИЛИ-НЕ подключен к входу третьего инвертора, второму входу первой группы входов И и первому входу четвертой группы входов И четвертого элемента И-ИЛИ-НЕ, выход третьего инвертора подключен к индикаторному выходу и второму и первому входам второй и третьей групп входов И пятого элемента И-ИЛИ-НЕ соответственно.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Использование элементов И-ИЛИ-НЕ, ИЛИ-И-НЕ, ИЛИ-НЕ и инверторов для реализации D-триггера известно. Однако использование их в данном случае позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

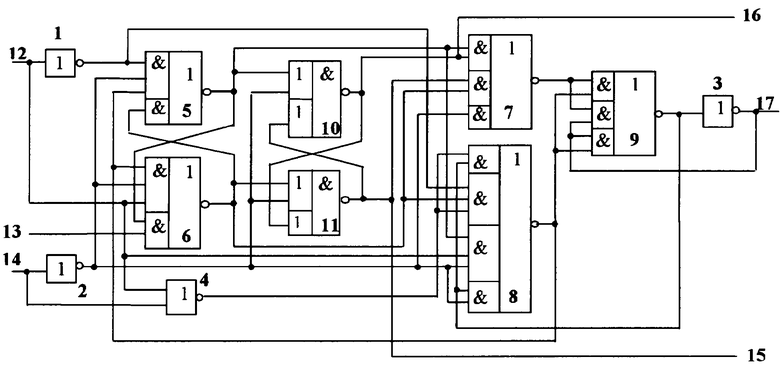

На чертеже изображена схема самосинхронного D-триггера.

Схема D-триггера содержит три инвертора 1-3, элемент ИЛИ-НЕ 4, пять элементов И-ИЛИ-НЕ 5-9, два элемента ИЛИ-И-НЕ 10-11, информационный вход 12, вход обнуления 13, управляющий вход 14, прямой информационный выход 15, инверсный информационный выход 16 и индикаторный выход 17, информационный вход 12 подключен ко входу инвертора 1, третьему входу первой группы входов И элемента 6, первому входу элемента 4 и второму входу третьей группы входов И элемента 8, вход обнуления 13 подключен ко второму входу второй группы входов элемента 6, управляющий вход 14 подключен ко входу инвертора 2 и второму входу элемента 4, выход инвертора 1 подключен к первому входу первой группы входов И элемента 5 и первому входу второй группы входов И элемента 8, выход инвертора 2 подключен ко вторым входам первых групп И элементов 5 и 6, вторым входам первых групп ИЛИ элементов 10 и 11, входу третьей группы входов И элемента 7, третьему входу третьей группы входов И элемента 8 и второму входу четвертой группы входов И элемента 8, выход элемента 4 подключен к первому входу первой группы входов И и третьему входу второй группы входов И элемента 8, выход элемента 5 подключен к первому входу первой группы входов ИЛИ элемента 10, первому входу второй группы входов И элемента 6, первому входу первой группы входов И элемента 7 и первому входу третьей группы входов И элемента 8, выход элемента 6 подключен ко входу второй группы входов И элемента 5, первому входу первой группы входов ИЛИ элемента 11, второму входу второй группы входов И элемента 7 и второму входу второй группы входов И элемента 8, выход элемента 10 подключен к инверсному информационному выходу триггера 16, входу второй группы входов ИЛИ элемента 11 и второму входу первой группы входов И элемента 7, выход элемента 11 подключен к прямому информационному выходу триггера 15, входу второй группы входов ИЛИ элемента 10 и первому входу второй группы входов И элемента 7, выход элемента 7 подключен к первым входам первой и второй групп входов И элемента 9, выход элемента 8 подключен ко вторым входам первой и третьей групп входов И элемента 9, третьему входу первой группы входов И элемента 5 и первому входу первой группы входов И элемента 6, выход элемента 9 подключен ко входу инвертора 3, второму входу первой группы входов И и первому входу четвертой группы входов И элемента 8, выход инвертора 3 подключен к индикаторному выходу 17 и второму и первому входам второй и третьей групп входов И элемента 9 соответственно.

Схема работает следующим образом. Установка начального состояния происходит при подаче низкого уровня на вход 13 и высокого уровня сигнала на вход управления 14. При этом выход 16 устанавливается в «1» (высокий уровень), а выход 15 - в «0» (низкий уровень). Запись нового состояния с информационного входа 12 в первый однотактный триггер, образованный элементами 5 и 6, обеспечивается подачей на вход 14 низкого уровня. При этом на выходе инвертора 2 формируется высокий логический уровень, разрешающий запись в первый однотактный триггер и запирающий по входам второй однотактный триггер, образованный элементами 10 и 11. Перезапись информации из первого однотактного триггера во второй осуществляется при подаче на управляющий вход 14 высокого уровня сигнала. В этом случае первый однотактный триггер запирается по входам и хранит состояние своих выходов, которое и переписывается во второй однотактный триггер. Элементы 3, 4, 7-9 выполняют функцию индикатора окончания переходных процессов в D-триггере и регулятора фаз переключения D-триггера, при этом элемент 7 анализирует на соответствие состояния первого и второго однотактных триггеров, а элемент 8 индицирует соответствие состояния выходов первого однотактного триггера значению информационного входа 12 и выхода инвертора 1.

В предлагаемой схеме используется синхронная установка нуля: переход выходов триггера в устанавливаемое состояние специально не индицируется. Как правило, сброс в D-триггерах используется только для приведения триггера в исходное состояние сразу после включения питания. При этом время сброса выбирается большим, достаточным для приведения в исходное состояние всех элементов системы, частью которой является D-триггер. Реализация самосинхронного сброса в таких условиях была бы излишней и аппаратно избыточной.

Особенности данной схемы по сравнению с прототипом следующие.

Информационный вход триггера является однофазным, что позволяет использовать D-триггер в качестве элемента интерфейса между синхронной и самосинхронной схемами. Информационные выходы триггера имеют парафазное (взаимоинверсное) кодирование без спейсера. Благодаря этому информационные выходы сохраняют свое значение между моментами обновления, что облегчает их использование последующими устройствами. Уточненный индикаторный выход фиксирует момент окончания переходных процессов во всех элементах триггера, как тех, которые были в составе прототипа, так и вновь введенных, что обеспечивает индикацию всех элементов в составе самосинхронной схемы.

Таким образом, предлагаемое устройство обеспечивает самосинхронность D-триггера и улучшение его потребительских характеристик за счет однофазности информационного входа и парафазности информационного выхода без спейсера. Цель изобретения достигнута.

Кроме того, предлагаемый D-триггер позволяет вдвое сократить число информационных связей между многоразрядным источником входной информации и регистром на базе данного самосинхронного D-триггера.

Понятия «однофазный» и «парафазный» определяются следующим образом. «Однофазным» считается сигнал, если он одиночный и требует использования инвертора для получения противоположного (инверсного) значения. «Парафазным» считается сигнал, представленный парой переменных (сигналов). В статическом состоянии, после окончания динамических процессов переключения элементов в схеме, две составляющие парафазного сигнала имеют взаимоинверсные состояния. В результате в статическом состоянии парафазный сигнал {X, ХВ} может принимать одно из двух рабочих состояний: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход из одного статического состояния в противоположное осуществляется через одно и то же динамическое состояние, {1,1} или {0,0}, определяемое типом элементов, формирующих парафазный сигнал. Типичным представителем устройства с парафазным выходом является обычный синхронный триггер с перекрестными обратными связями, например RS-триггер.

Источники информации

[1] Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд., испр. - Челябинск, Металлургия, Челябинское отд., 1989 - рис.1.54а.

[2] Апериодические автоматы. Под ред. В.И.Варшавского. М.: Наука, 1976. - 424 с. - рис.2.16а.

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОСИНХРОННЫЙ ОДНОКРАТНЫЙ D-ТРИГГЕР С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362266C1 |

| САМОСИНХРОННЫЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С НИЗКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362267C1 |

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| САМОСИНХРОННЫЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2365031C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390092C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2391772C2 |

| D-ТРИГГЕР С САМОСИНХРОННОЙ ПРЕДУСТАНОВКОЙ | 2006 |

|

RU2319297C1 |

| САМОСИНХРОННЫЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С НИЗКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2366080C2 |

| САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ (ВАРИАНТЫ) | 2009 |

|

RU2427955C2 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

Изобретение относится к импульсной и вычислительной технике и может быть использовано при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации. Техническим результатом изобретения является обеспечение самосинхронности D-триггера с однофазным кодированием информационного входа и парафазным кодированием информационного выхода. Этот результат достигается тем, что в схему, содержащую два однотактных триггера, введены инверторы на входах: информационном и управляющем, а также добавлено устройство индикации окончания переходных процессов в триггере, реализованное на трех элементах И-ИЛИ-НЕ, элементе ИЛИ-НЕ и инверторе. 1 ил.

Самосинхронный D-триггер, содержащий два однотактных триггера, информационный вход, управляющий вход, вход обнуления, прямой и инверсный информационные выходы, индикаторный выход, отличающийся тем, что в схему введены инверторы на входах: информационном и управляющем, первый однотактный триггер реализован на двух элементах И-ИЛИ-НЕ - первом и втором, а второй однотактный триггер реализован на двух элементах ИЛИ-И-НЕ - первом и втором, а также добавлено устройство индикации окончания переходных процессов в триггере, реализованное на трех элементах И-ИЛИ-НЕ - третьем, четвертом и пятом, элементе ИЛИ-НЕ и инверторе, информационный вход подключен ко входу первого инвертора, третьему входу первой группы входов И второго элемента И-ИЛИ-НЕ, первому входу элемента ИЛИ-НЕ и второму входу третьей группы входов И четвертого элемента И-ИЛИ-НЕ, управляющий вход подключен ко входу второго инвертора и второму входу элемента ИЛИ-НЕ, вход обнуления подключен ко второму входу второй группы И входов второго элемента И-ИЛИ-НЕ, выход первого инвертора подключен к первому входу первой группы входов И первого элемента И-ИЛИ-НЕ и первому входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход второго инвертора подключен ко вторым входам первых групп И первого и второго элементов И-ИЛИ-НЕ, вторым входам первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ, входу третьей группы входов И третьего элемента И-ИЛИ-НЕ, третьему входу третьей группы входов И четвертого элемента И-ИЛИ-НЕ и второму входу четвертой группы входов И четвертого элемента И-ИЛИ-НЕ, выход элемента ИЛИ-НЕ подключен к первому входу первой группы входов И и третьему входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ, первому входу второй группы входов И второго элемента И-ИЛИ-НЕ, первому входу первой группы входов И третьего элемента И-ИЛИ-НЕ и первому входу третьей группы входов И четвертого элемента И-ИЛИ-НЕ, выход второго элемента И-ИЛИ-НЕ подключен к входу второй группы входов И первого элемента И-ИЛИ-НЕ, первому входу первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ, второму входу второй группы входов И третьего элемента И-ИЛИ-НЕ и второму входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход первого элемента ИЛИ-И-НЕ подключен к инверсному информационному выходу триггера, входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ и второму входу первой группы входов И третьего элемента И-ИЛИ-НЕ, выход второго элемента ИЛИ-И-НЕ подключен к прямому информационному выходу триггера, входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и первому входу второй группы входов И третьего элемента И-ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ подключен к первым входам первой и второй групп входов И пятого элемента И-ИЛИ-НЕ, выход четвертого элемента И-ИЛИ-НЕ подключен ко вторым входам первой и третьей групп входов И пятого элемента И-ИЛИ-НЕ, третьему входу первой группы входов И первого элемента И-ИЛИ-НЕ и первому входу первой группы входов И второго элемента И-ИЛИ-НЕ, выход пятого элемента И-ИЛИ-НЕ подключен ко входу третьего инвертора, второму входу первой группы входов И и первому входу четвертой группы входов И четвертого элемента И-ИЛИ-НЕ, выход третьего инвертора подключен к индикаторному выходу и второму и первому входам второй и третьей групп входов И пятого элемента И-ИЛИ-НЕ соответственно.

| Апериодические автоматы | |||

| Под ред | |||

| Варшавского В.И | |||

| - М.: Наука, 1976, с.424 | |||

| Триггер с индикацией моментов окончания переходных процессов | 1987 |

|

SU1420647A1 |

| US 6239640 B1, 29.05.2001 | |||

| US 2002047736 A1, 25.04.2002. | |||

Авторы

Даты

2009-07-10—Публикация

2007-10-12—Подача