Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером относится к импульсной и вычислительной технике и может использоваться при построении сбоеустойчивых самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен самосинхронный однотактный RS-триггер с единичным спейсером [1, фиг. 3], содержащий элемент И-НЕ и два элемента ИЛИ-И-НЕ.

Недостаток известного устройства - низкая сбоеустойчивость, допускающая переключение триггера в противоположное состояние при воздействии ионизирующего излучения, тяжелых заряженных частиц, протонов и нейтронов.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является RS-триггер DICE-типа [2, рис. 3(a)], содержащий восемь КМОП транзисторов n-типа и восемь КМОП транзисторов р-типа.

Недостаток прототипа - невозможность его использовании в самосинхронном режиме работы из-за отсутствия индикации окончания переключений элементов схемы RS-триггера.

Задача, решаемая в изобретении, заключается в обеспечении самосинхронной работы триггера посредством реализации индицируемости всех его элементов.

Это достигается тем, что в однотактный RS-триггер, содержащий восемь КМОП транзисторов n-типа, восемь КМОП транзисторов р-типа, два парафазных информационных входа с единичным спейсером и два бифазных информационных выхода, причем истоки и подложки всех транзисторов р-типа подключены к шине питания, стоки первого и второго транзисторов р-типа соединены со стоком первого транзистора n-типа, затворами шестых транзисторов р- и n-типа и прямым компонентом первого бифазного выхода, стоки третьего и четвертого транзисторов р-типа соединены со стоком второго транзистора n-типа, затворами седьмого транзистора р-типа и пятого транзистора n-типа и прямым компонентом второго бифазного выхода, стоки пятого и шестого транзисторов р-типа соединены со стоком пятого транзистора n-типа, затворами третьего транзистора р-типа и первого транзистора n-типа и инверсным компонентом первого бифазного выхода, стоки седьмого и восьмого транзисторов р-типа соединены со стоком шестого транзистора n-типа, затворами вторых транзисторов р- и n-типа и инверсным компонентом второго бифазного выхода, исток первого транзистора n-типа подключен к стоку третьего транзистора n-типа, исток второго транзистора n-типа n-подключен к стоку четвертого транзистора n-типа, исток пятого транзистора n-типа подключен к стоку седьмого транзистора n-типа, исток шестого транзистора n-типа подключен к стоку восьмого транзистора n-типа, истоки третьего, четвертого, седьмого и восьмого транзисторов n-типа и подложки всех транзисторов n-типа соединены с шиной "земли", затворы первого транзистора р-типа и четвертого транзистора n-типа подключены к прямому компоненту первого парафазного информационного входа с единичным спейсером, затворы четвертого транзистора р-типа и третьего транзистора n-типа подключены к прямому компоненту второго парафазного информационного входа с единичным спейсером, затворы пятого транзистора р-типа и восьмого транзистора n-типа подключены к инверсному компоненту первого парафазного информационного входа с единичным спейсером, затворы восьмого транзистора р-типа и седьмого транзистора n-типа подключены к инверсному компоненту второго парафазного информационного входа с единичным спейсером, введены два элемента ИЛИ-И-НЕ, гистерезисный триггер (Г-триггер) и индикаторный выход RS-триггера, причем два входа первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключены к прямому компоненту второго парафазного информационного входа с единичным спейсером и инверсному компоненту второго бифазного выхода RS-триггера, два входа второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключены к прямому компоненту второго бифазного выхода RS-триггера и инверсному компоненту второго парафазного информационного входа с единичным спейсером, два входа первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключены к прямому компоненту первого парафазного информационного входа с единичным спейсером и инверсному компоненту первого бифазного выхода RS-триггера, два входа второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключены к прямому компоненту первого бифазного выхода RS-триггера и инверсному компоненту первого парафазного информационного входа с единичным спейсером, выходы первого и второго элементов ИЛИ-И-НЕ соединены с входами Г-триггера, выход которого подключен к индикаторному выходу RS-триггера.

Предлагаемое устройство обладает существенными признаками, отличающими его от прототипа и обеспечивающими достижение заявленного технического результата. Действительно, использование элемента ИЛИ-И-НЕ для формирования индикаторного выхода известно и в других самосинхронных триггерах. Но только применение двух элементов ИЛИ-И-НЕ, подключенных к информационным входам и выходам самосинхронного однотактного RS-триггера и входам Г-триггера указанным способом, позволило достичь эффекта, выраженного целью изобретения.

Указанные существенные признаки являются отличительными, поскольку указанные введенные конструктивные связи в аналогичных технических решениях не известны.

Понятие "парафазный", используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими - парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если в качестве спейсерного используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то - парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, переключение в которое в самосинхронной схемотехнике должно фиксироваться индикатором окончания переходного процесса, в данном случае - окончания переключения в спейсерное состояние.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0}, - называемое транзитным состоянием.

Понятие "бифазный", используемое в тексте данной заявки, определяется следующим образом. Бифазным считается сигнал, являющийся выходом {Q, QB} бистабильной ячейки (БЯ) - RS-триггера на двух логических элементах с перекрестными связями. В статической фазе его компоненты имеют взаимоинверсные значения: {Q=0, QB=1} или {Q=l, QB=0}. Переход бифазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние осуществляется через промежуточное динамическое (транзитное) состояние. Транзитное состояние: {нулевое - Q=QB=0} или {единичное - Q=QB=1}, -определяется типом логических элементов в БЯ.

В материалах данной заявки речь идет об использовании в качестве информационного входа парафазного сигнала с единичным спейсером, в дальнейшем - просто парафазного сигнала, и бифазного сигнала с единичным транзитным состоянием.

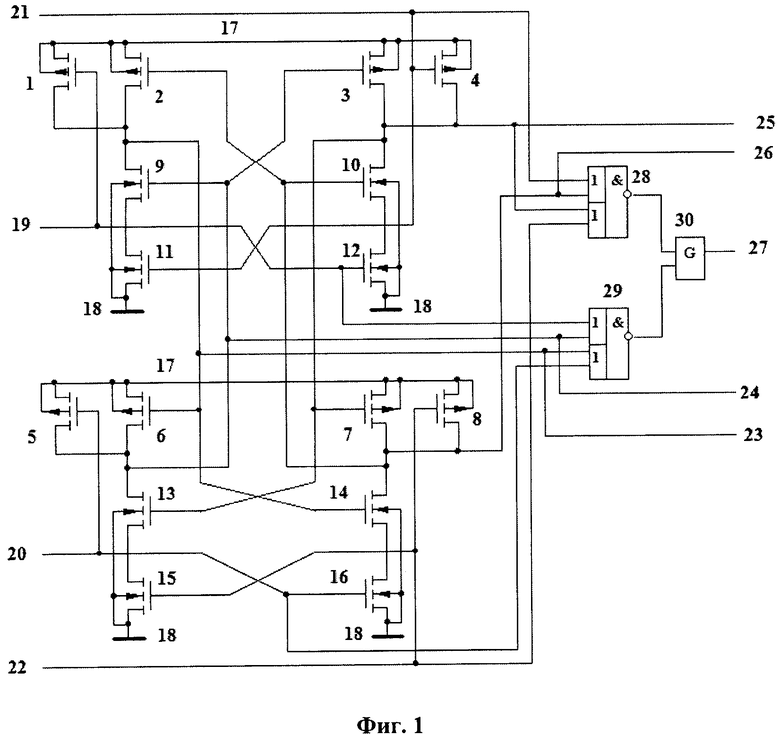

На Фиг. 1 представлена схема сбоеустойчивого самосинхронного однотактного RS-триггера с единичным спейсером. Схема содержит восемь МОП транзисторов р-типа 1-8, восемь МОП транзисторов n-типа 9-16, шину питания 17, шину "земли" 18, прямой 19 и инверсный 20 компоненты первого информационного парафазного входа с единичным спейсером, прямой 21 и инверсный 22 компоненты второго информационного парафазного входа с единичным спейсером, прямой 23 и инверсный 24 компоненты первого бифазного выхода, прямой 25 и инверсный 26 компоненты второго бифазного выхода, индикаторный выход 27, элементы ИЛИ-И-НЕ 28-29 и Г-триггер 30, истоки и подложки всех транзисторов р-типа 1-8 подключены к шине питания 17, стоки первого 1 и второго 2 транзисторов р-типа соединены со стоком первого транзистора п-типа 9, затворами шестых транзисторов р-типа 6 и n-типа 14 и прямым компонентом 23 первого бифазного выхода, стоки третьего 3 и четвертого 4 транзисторов р-типа соединены со стоком второго транзистора n-типа 10, затворами седьмого транзистора р-типа 7 и пятого транзистора n-типа 13 и прямым компонентом второго бифазного выхода, стоки пятого 5 и шестого 6 транзисторов р-типа соединены со стоком пятого 13 транзистора n-типа, затворами третьего 3 транзистора р-типа и первого 9 транзистора n-типа и инверсным компонентом 24 первого бифазного выхода, стоки седьмого 7 и восьмого 8 транзисторов р-типа соединены со стоком шестого 14 транзистора n-типа, затворами вторых транзисторов р-типа 2 и n-типа 10 и инверсным компонентом 26 второго бифазного выхода, исток первого транзистора n-типа 9 подключен к стоку третьего транзистора n-типа 11, исток второго транзистора n-типа 10 подключен к стоку четвертого транзистора n-типа 12, исток пятого транзистора n-типа 13 подключен к стоку седьмого транзистора n-типа 15, исток шестого транзистора n-типа 14 подключен к стоку восьмого транзистора n-типа 16, истоки третьего 11, четвертого 12, седьмого 15 и восьмого 16 транзисторов n-типа и подложки всех транзисторов n-типа соединены с шиной "земли", затворы первого транзистора р-типа 1 и четвертого транзистора n-типа 12 подключены к прямому компоненту 19 первого парафазного информационного входа с единичным спейсером, затворы четвертого транзистора р-типа 4 и третьего транзистора n-типа 11 подключены к прямому компоненту 21 второго парафазного информационного входа с единичным спейсером, затворы пятого транзистора р-типа 5 и восьмого транзистора n-типа 16 подключены к инверсному компоненту 20 первого парафазного информационного входа с единичным спейсером, затворы восьмого транзистора р-типа 8 и седьмого транзистора n-типа 15 подключены к инверсному компоненту 22 второго парафазного информационного входа с единичным спейсером, введены индикаторный выход RS-триггера 27, два элемента ИЛИ-И-НЕ 28-29 и Г-триггер 30, причем два входа первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 28 подключены к прямому компоненту 21 второго парафазного информационного входа с единичным спейсером и инверсному компоненту 26 второго бифазного выхода RS-триггера, два входа второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 28 подключены к прямому компоненту 25 второго бифазного выхода RS-триггера и инверсному компоненту 22 второго парафазного информационного входа с единичным спейсером, два входа первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ 29 подключены к прямому компоненту 19 первого парафазного информационного входа с единичным спейсером и инверсному компоненту 24 первого бифазного выхода RS-триггера, два входа второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 29 подключены к прямому компоненту 23 первого бифазного выхода RS-триггера и инверсному компоненту 20 первого парафазного информационного входа с единичным спейсером, выходы первого 28 и второго 29 элементов ИЛИ-И-НЕ соединены с входами Г-триггера 30, выход которого подключен к индикаторному выходу 17 RS-триггера.

Схема работает следующим образом. Первый и второй парафазные входы логически идентичны. Первый и второй бифазные выходы также логически идентичны. Использование идентичных пар входов и выходов обеспечивает сбоеустойчивость передаваемой и хранимой в триггере информации. Оба бифазных выхода триггера переключатся в новое идентичное состояние только тогда, когда оба парафазных входа перейдут в одинаковую рабочую фазу. Входы имеют единичный спейсер. Это значит, что спейсерное значение "1" любого компонента любого входа не способно изменить состояние бифазных выходов триггера.

Обозначим прямой 19 и инверсный 20 компоненты первого парафазного входа как S1 и R1, компоненты 21 и 22 второго парафазного входа - как S2 и R2; прямой 23 и 24 инверсный компоненты первого бифазного выхода как Q1 и QB1, компоненты 25 и 26 второго бифазного выхода как Q2 и QB2; индикаторный выход 27 как I. Пусть в исходном состоянии триггер находится в спейсере: R1=R2=S1=S2=1, - и хранит состояние: Q1=Q2=1, QB1=QB2=0. Открыты транзисторы 2, 3, 11-16; закрыты транзисторы 1, 4-10. На выходах элементов 28 и 29 низкий логический уровень. Индикаторный выход подтверждает окончание переключения триггера в спейсер: I=0. Пусть на вход триггера поступает сигнал R1=0, а остальные входы остаются неизменными. Низкий уровень на затворах транзисторов 5 и 16 приведет к отпиранию транзистора 5 и запиранию транзистора 16. Открытый транзистор 5 будет "тянуть" выход QB1 к питанию (уровню логической единицы), но открытые транзисторы 13 и 15 будут этому препятствовать. Размеры транзисторов р-типа и n-типа в данной схеме подбираются таким образом, чтобы открытый транзистор р-типа не смог "перетянуть" последовательно соединенные открытые транзисторы n-типа. Тогда уровень выхода QB1 будет по-прежнему соответствовать логическому нулю и состояние RS-триггера не изменится. Только после переключения входа R2 в значение, идентичное входу Rl (R2=0), вызывающего отпирание транзистора р-типа 8 и запирание транзистора n-типа 15, транзистор 5 сможет поднять потенциал выхода QB1 до уровня логической единицы. Одновременно выход QB2 переключается в состояние логической единицы из-за открытого транзистора 8 и закрытого транзистора 16. Это вызовет последующие переключения в схеме: запирание транзисторов 2 и 3, отпирание транзисторов 9 и 10, затем переключение выходов Q1 и Q2 в состояние логического нуля (Q1=Q2=0). В результате триггер перейдет в новое состояние Q1=Q2=0, QB1=QB2=1. В соответствии с новыми значениями входов и выходов триггера выходы элементов 28 и 29 переключатся в значение логической единицы и инициируют переключение Г-триггера также в состояние логической единицы (I=1), которое подтвердит успешное окончание переключения самосинхронного однотактного триггера в новое рабочее состояние.

Сбоеустойчивость триггера подтверждается его реакцией на воздействие одиночной причины, вызывающей логический сбой - переключение одного компонента одного бифазного выхода триггера в противоположное состояние. Пусть, например, триггер находится в том же исходном состоянии: R1=R2=S1=S2=1, Q1=Q2=1, QB1=QB2=:0, I=0, - и тяжелая заряженная частица, пролетев через область стока транзистора n-типа 13, вызвала ионизационный ток, зарядивший паразитную емкость выхода QB1 до уровня логической единицы. Это приведет к запиранию транзистора 3 и отпиранию транзистора 10. Поскольку транзистор 9 закрыт, состояние выхода Q1 при этом не изменится, так как оно поддерживается открытым транзистором 2, а состояние выхода Q2 останется прежним (Q2=l) из-за хранения заряда паразитной емкостью этого выхода при закрытом транзисторе 10. Ионизационный ток заканчивается достаточно быстро, поскольку транзисторы 13 и 15 остаются открытыми и вызывают рассасывание избыточных носителей в теле полупроводника. Выход QB1 возвращается в исходное состояние (QB1=0) и триггер продолжает успешно хранить свое состояние. Кратковременное переключение выхода QB1 в состояние логической единицы не вызывает переключения элементов 28, 29 и 30, и индикаторный выход 27 триггера сохраняет свое значение, оповещая приемники о том, что триггер все еще находится в спейсере и его состояние нельзя использовать.

Особенности данной схемы по сравнению с прототипом следующие.

Элементы ИЛИ-И-НЕ и Г-триггер, объединяя парафазные входы и бифазные выходы и формируя индикаторный выход однотактного RS-триггера, обеспечивают управление фазами работы триггера, индицирование соответствия состояния парафазных входов состоянию бифазных выходов в рабочей фазе и индицирование переключения входов в спейсер. Тем самым обеспечивается самосинхронность переключения однотактного RS-триггера из рабочей фазы в спейсер и обратно.

Таким образом, предлагаемое устройство реализует самосинхронную работу однотактного RS-триггера посредством обеспечения индицируемости всех его выводов и элементов. Цель изобретения достигнута.

Источники

[1] Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.Г., Петрухин B.C. Однотактный самосинхронный RS-триггер с предустановкой. Патент №2390092. Опубл. в Б.И., 2010,№14. - 18 с.

[2] Катунин Ю.В., Стенин В.Я., Степанов П.В. Моделирование характеристик триггерных элементов КМОП двухфазной логики с учетом разделения заряда при воздействии отдельных ядерных частиц // Микроэлектроника, 2014, Т.43, №2. - С. 104-117.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2808236C1 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с единичным спейсером | 2024 |

|

RU2834690C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390092C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером | 2023 |

|

RU2808782C1 |

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с нулевым спейсером | 2024 |

|

RU2835382C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693318C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2391772C2 |

Изобретение предназначено для построения сбоеустойчивых самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации. Технический результат заключается в обеспечении самосинхронной работы триггера посредством реализации индицируемости всех его элементов. В схему триггера, содержащую восемь КМОП транзисторов n-типа, восемь КМОП транзисторов р-типа, два парафазных информационных входа с единичным спейсером и два бифазных информационных выхода, введены два элемента ИЛИ-И-НЕ, гистерезисный триггер и индикаторный выход, парафазные входы и бифазные выходы RS-триггера подключены к входам элементов ИЛИ-И-НЕ, выходы которых соединены с входами гистерезисного триггера, чей выход подключен к индикаторному выходу RS-триггера. 1 ил.

Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером, содержащий восемь КМОП транзисторов n-типа, восемь КМОП транзисторов р-типа, два парафазных информационных входа с единичным спейсером и два бифазных информационных выхода, причем истоки и подложки всех транзисторов р-типа подключены к шине питания, стоки первого и второго транзисторов р-типа соединены со стоком первого транзистора n-типа, затворами шестых транзисторов р- и n-типа и прямым компонентом первого бифазного выхода, стоки третьего и четвертого транзисторов р-типа соединены со стоком второго транзистора n-типа, затворами седьмого транзистора р-типа и пятого транзистора n-типа и прямым компонентом второго бифазного выхода, стоки пятого и шестого транзисторов р-типа соединены со стоком пятого транзистора n-типа, затворами третьего транзистора р-типа и первого транзистора n-типа и инверсным компонентом первого бифазного выхода, стоки седьмого и восьмого транзисторов р-типа соединены со стоком шестого транзистора n-типа, затворами вторых транзисторов р- и n-типа и инверсным компонентом второго бифазного выхода, исток первого транзистора n-типа подключен к стоку третьего транзистора n-типа, исток второго транзистора n-типа подключен к стоку четвертого транзистора n-типа, исток пятого транзистора n-типа подключен к стоку седьмого транзистора n-типа, исток шестого транзистора n-типа подключен к стоку восьмого транзистора n-типа, истоки третьего, четвертого, седьмого и восьмого транзисторов n-типа и подложки всех транзисторов n-типа соединены с шиной "земли", затворы первого транзистора р-типа и четвертого транзистора n-типа подключены к прямому компоненту первого парафазного информационного входа с единичным спейсером, затворы четвертого транзистора р-типа и третьего транзистора n-типа подключены к прямому компоненту второго парафазного информационного входа с единичным спейсером, затворы пятого транзистора р-типа и восьмого транзистора n-типа подключены к инверсному компоненту первого парафазного информационного входа с единичным спейсером, затворы восьмого транзистора р-типа и седьмого транзистора n-типа подключены к инверсному компоненту второго парафазного информационного входа с единичным спейсером, отличающийся тем, что в схему введены два элемента ИЛИ-И-НЕ, гистерезисный триггер и индикаторный выход, причем два входа первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключены к прямому компоненту второго парафазного информационного входа с единичным спейсером и инверсному компоненту второго бифазного выхода RS-триггера, два входа второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ подключены к прямому компоненту второго бифазного выхода RS-триггера и инверсному компоненту второго парафазного информационного входа с единичным спейсером, два входа первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключены к прямому компоненту первого парафазного информационного входа с единичным спейсером и инверсному компоненту первого бифазного выхода RS-триггера, два входа второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключены к прямому компоненту первого бифазного выхода RS-триггера и инверсному компоненту первого парафазного информационного входа с единичным спейсером, выходы первого и второго элементов ИЛИ-И-НЕ соединены с входами гистерезисного триггера, выход которого подключен к индикаторному выходу RS-триггера.

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390092C1 |

| САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ (ВАРИАНТЫ) | 2009 |

|

RU2427955C2 |

| САМОСИНХРОННЫЙ ТРИГГЕР ДЛЯ СВЯЗИ С УДАЛЕННЫМ ПРИЕМНИКОМ | 2008 |

|

RU2382487C1 |

| КОМБИНИРОВАННЫЙ Г-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2010 |

|

RU2434318C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2391772C2 |

| Триггерный синхронный R-S триггер на полевых транзисторах | 2018 |

|

RU2702051C1 |

| Устройство для контроля магнитных сердечников | 1980 |

|

SU905892A1 |

| US 8232825 B2, 31.07.2012 | |||

| US 7697319 B2, 13.04.2010. | |||

Авторы

Даты

2020-07-06—Публикация

2019-12-20—Подача