Самосинхронный триггер с однофазным информационным входом относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации как в качестве ячейки хранения информации, так и в качестве интерфейса между синхронной и самосинхронной частями одной схемы.

Известен триггер [1], содержащий четыре элемента И-НЕ и инвертор.

Недостаток известного устройства - отсутствие средств индикации окончания переходных процессов.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный триггер [2], содержащий блок хранения в составе бистабильной ячейки на элементах И-ИЛИ-НЕ с парафазным кодированием информационных входов и выходов и индикаторного элемента И-ИЛИ-НЕ.

Недостаток прототипа - работа только с данными, представленными в парафазном коде, что удваивает число информационных связей между многоразрядным источником входной информации и регистром на базе данного триггера и не позволяет использовать его в качестве элемента интерфейса между синхронными и самосинхронными схемами.

Задача, решаемая в изобретении, заключается в обеспечении самосинхронной реализации триггера с однофазным информационным входом, гарантирующей работоспособность триггера при любых задержках составляющих его элементов.

Это достигается тем, что в самосинхронный триггер, содержащий блок хранения, однофазный информационный вход, вход управления, информационный выход и индикаторный выход, причем блок хранения имеет прямую и инверсную составляющие парафазного информационного входа, вход управления, информационный выход и индикаторный выход, информационный выход блока хранения подключен к информационному выходу триггера, прямая составляющая парафазного информационного входа блока хранения соединена с однофазным информационным входом триггера, индикаторный выход блока хранения подключен к индикаторному выходу триггера, введен блок конвертирования информационного сигнала и сигнала управления (далее просто блок конвертирования), имеющий информационный вход, вход управления, информационный выход и выход сигнала управления, информационный вход блока конвертирования подключен к однофазному информационному входу триггера, вход управления блока конвертирования соединен с входом управления триггера, информационный выход блока конвертирования подключен к инверсной составляющей парафазного информационного входа блока хранения, выход сигнала управления блока конвертирования соединен с входом управления блока хранения.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Использование устройства преобразования однофазных сигналов в парафазные известно. Однако в данном случае оно включает и преобразование входа управления триггера, что позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

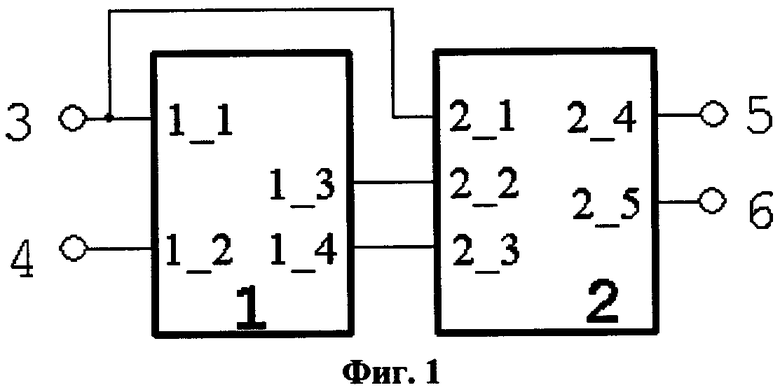

На фиг.1 изображена схема самосинхронного триггера с однофазным информационным входом. Схема содержит блок конвертирования 1, блок хранения 2, однофазный информационный вход 3, вход управления 4, информационный выход 5, индикаторный выход 6, однофазный информационный вход триггера 3 подключен к информационному входу 1_1 блока конвертирования 1 и прямой составляющей парафазного информационного входа 2_1 блока хранения 2, вход управления триггера 4 соединен с входом управления 1_2 блока конвертирования 1, информационный выход 1_3 блока конвертирования 1 подключен к инверсной составляющей парафазного информационного входа 2_2 блока хранения 2, выход сигнала управления 1_4 блока конвертирования 1 соединен с входом управления 2_3 блока хранения 2, информационный выход 2_4 блока хранения 2 подключен к информационному выходу 5 триггера, индикаторный выход блока хранения 2_5 соединен с индикаторным выходом триггера 6.

Схема работает следующим образом. Однофазный информационный сигнал поступает на вход 3 триггера, а управляющий сигнал - на вход 4 (только после факта окончания переходного процесса на входе 3). Блок конвертирования дополняет однофазный информационный вход триггера его инверсной составляющей и корректирует сигнал управления таким образом, чтобы обеспечить самосинхронность переключений триггера. Преобразованные сигналы вместе с однофазным информационным входом триггера подаются на входы блока хранения. Управляющий сигнал служит для разрешения или запрета записи информационных входов блока хранения в его внутреннее состояние. Например, при высоком уровне управляющего сигнала блок хранения воспринимает и запоминает состояние информационных входов, а при низком уровне - хранит свое состояние. Блок хранения имеет в своем составе индикаторный элемент, который отслеживает окончание переходных процессов во всех элементах, составляющих триггер. Выход индикаторного элемента может находиться в одном из двух состояний, одно из которых, например, высокое, соответствует окончанию записи нового состояния в блок хранения (рабочая фаза триггера - фаза записи в триггер), а второе (низкое) - окончанию подготовки триггера к приему новых данных (спейсерная фаза - фаза хранения информации). Блок конвертирования обеспечивает надлежащее преобразование однофазного информационного сигнала и корректирует вход управления триггера с учетом значения однофазного информационного входа так, чтобы гарантировать безошибочное запоминание в блоке хранения требуемого состояния и успешное индицирование обеих фаз работы триггера.

Особенности данной схемы по сравнению с прототипом следующие.

Информационный вход триггера является однофазным, что позволяет использовать триггер в качестве элемента интерфейса между синхронной и самосинхронной схемами и сокращает вдвое число информационных связей между источником и приемником информации при использовании его в составе самосинхронных схем. Это упрощает проблему трассируемости схемы на кристалле или на плате при реализации общей системы. Кроме того, непарный (однофазный) информационный выход обеспечивает каскадирование данных триггеров при построении конвейерных структур в самосинхронных схемах с минимальным числом информационных связей между ними.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу триггера с однофазным информационным входом. Цель изобретения достигнута.

Конкретная техническая реализация предлагаемого устройства и его составных блоков зависит от типа входа управления: высоким или низким его рабочим уровнем разрешается запись в блок хранения нового состояния, и от функционального назначения триггера. Тип управляющего сигнала влияет на базис реализации блока конвертирования и блока хранения: И-ИЛИ-НЕ или ИЛИ-И-НЕ. Функциональное назначение определяет способ реализации блока хранения: на одной или на двух бистабильных ячейках. В первом случае блок хранения используется для построения однотактного самосинхронного триггера. Во втором случае блок хранения используется для построения двухтактного самосинхронного триггера.

Блок конвертирования является общим для всех триггеров с однофазным информационным входом и реализуется идентично для всех триггеров с одинаковым типом входа управления.

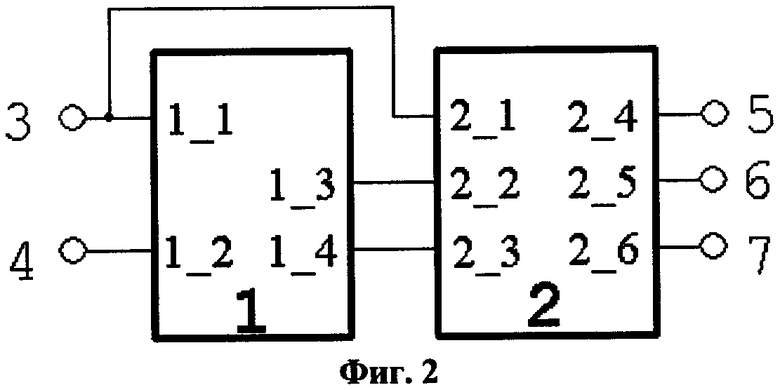

Наличие одного информационного выхода не всегда удобно при построении самосинхронных схем, так как традиционно в них используется парафазное кодирование информационных сигналов. На фиг.2 представлена схема самосинхронного триггера, отличающаяся от схемы на фиг.1 наличием инверсной составляющей информационного выхода триггера 7, подключенной к инверсному выходу 2_6 блока хранения 2. Таким образом, сигнал, формируемый на информационных выходах триггера, становится парафазным.

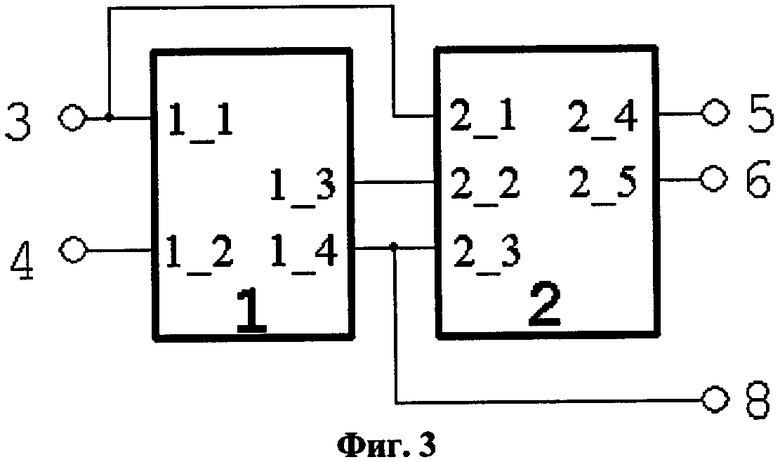

На фиг.3 изображена схема самосинхронного триггера с однофазным информационным входом, отличающаяся от схемы на фиг.1 наличием выхода обратной связи 8, подключенного к выходу сигнала управления 1_4 блока конвертирования 1. Выход обратной связи служит для ускорения срабатывания устройства - источника однофазного информационного входа триггера: разрешение на его переход в противоположную фазу работы выдается сразу, как только переключится в соответствующую фазу выход управления 1_4 блока конвертирования, без ожидания окончания переключения остальных элементов в составе схемы триггера.

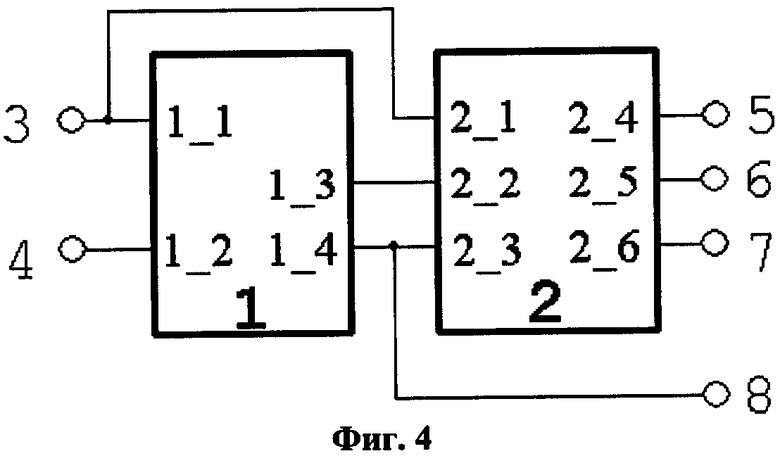

На фиг.4 представлена схема самосинхронного триггера с однофазным информационным входом, отличающаяся от схемы на фиг.2 наличием выхода обратной связи 8, подключенного к выходу сигнала управления 1_4 блока конвертирования 1. Наличие парафазного информационного выхода (5 и 7) и одновременно выхода обратной связи 8 в самосинхронном триггере повышает степень универсальности его использования и быстродействие его взаимодействия с внешней средой.

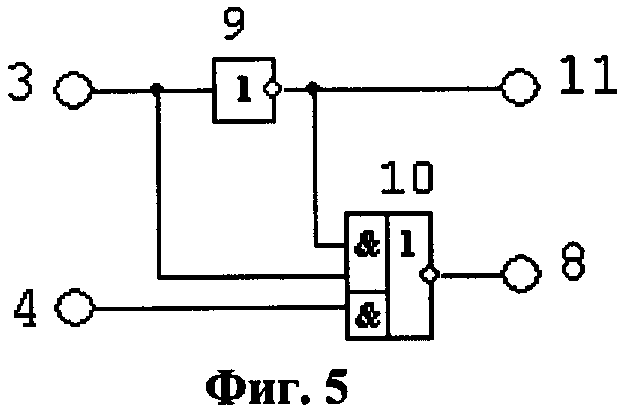

На фиг.5 представлена реализация блока конвертирования для случая, когда запись нового состояния в триггер разрешается низким уровнем на входе управления триггера.

Схема содержит инвертор 9, элемент И-ИЛИ-НЕ 10, однофазный информационный вход 3, вход управления 4, информационный выход 11 и выход управления 8, вход инвертора 9 подключен к однофазному информационному входу 3 и второму входу первой группы входов И элемента И-ИЛИ-НЕ 10, а выход инвертора 9 соединен с информационным выходом 11 и с первым входом первой группы входов И элемента И-ИЛИ-НЕ 10, вход управления 4 соединен с входом второй группы входов И элемента И-ИЛИ-НЕ 10, выход которого подключен к выходу управления 8.

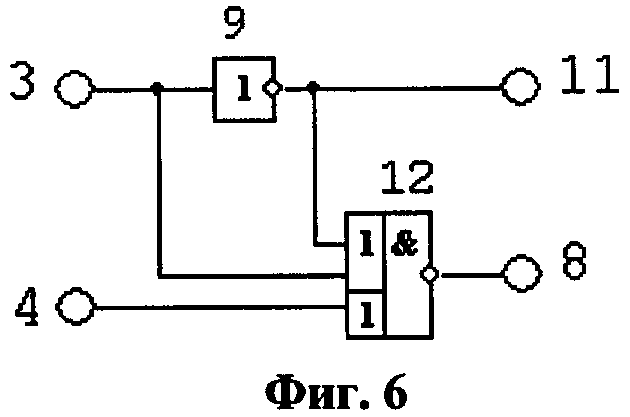

На фиг.6 представлена реализация блока конвертирования для случая, когда запись нового состояния в триггер разрешается высоким уровнем на входе управления триггера.

Схема содержит инвертор 9, элемент ИЛИ-И-НЕ 12, однофазный информационный вход 3, вход управления 4, информационный выход 11 и выход управления 8, вход инвертора 9 подключен к однофазному информационному входу 3 и второму входу первой группы входов ИЛИ элемента ИЛИ-И-НЕ 12, а выход инвертора 9 соединен с информационным выходом 11 и с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ 12, вход управления 4 соединен с входом второй группы входов ИЛИ элемента ИЛИ-И-НЕ 12, выход которого подключен к выходу управления 8.

Элементы 10 на фиг.5 и 12 на фиг.6, на первый взгляд, избыточны, так как на входы первой группы их входов поступают взаимоинверсные информационные сигналы. Однако именно это позволяет получить самосинхронное поведение триггера, когда переход в следующую фазу работы разрешается только после окончания переключения всех элементов схемы в текущую фазу. В соответствии с определением схема считается самосинхронной, если она правильно работает при любых конечных задержках входящих в нее элементов. Если бы элементы 10 на фиг.5 и 12 на фиг.6 не имели такой первой группы входов, то при некоторых комбинациях входных сигналов и произвольных задержках элементов схемы инвертор 9 мог бы не успеть переключиться в противоположное состояние за время формирования нового состояния на информационных выходах триггера и при последующем переходе в новую рабочую фазу привел бы к неправильному переключению триггера. Предложенное же решение обеспечивает строгое соблюдение принципа самосинхронности: индикатор блока хранения переключается в рабочую фазу только после того, как инвертор 9 переключится в состояние, противоположное значению однофазного информационного входа 3.

Блок конвертирования инвертирует фазу управляющего сигнала при его преобразовании. Поэтому блок хранения должен быть реализован схемой, имеющей вход управления, тип которого противоположен типу входа управления триггера и блока конвертирования.

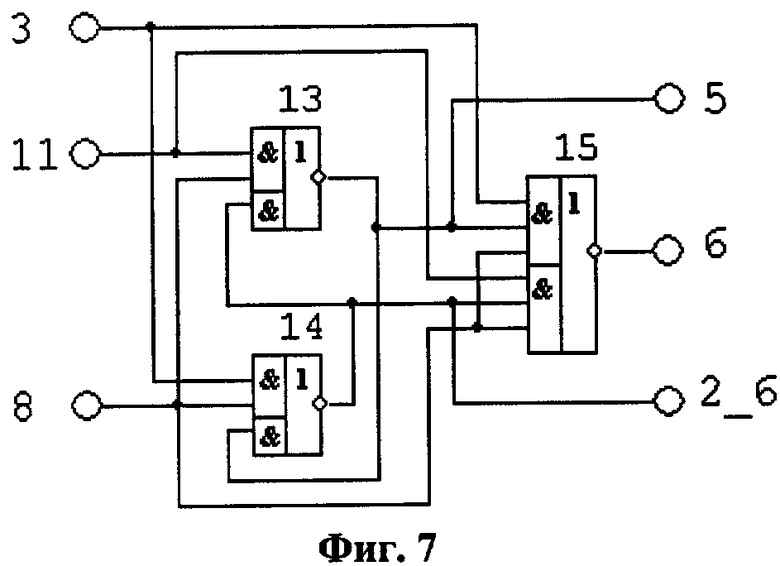

На фиг.7 приведена схема блока хранения однотактного самосинхронного триггера для случая, когда запись нового состояния происходит при высоком уровне его входа управления [2]. Схема содержит три элемента И-ИЛИ-НЕ 13-15, парафазный информационный вход 3, 11, вход управления 8, информационный 5 и инверсный информационный 2_6 выходы, индикаторный выход 6, прямая составляющая парафазного информационного входа 3 подключена к первым входам первых групп входов И второго 14 и третьего 15 элементов И-ИЛИ-НЕ, инверсная составляющая парафазного информационного входа 11 подключена к первым входам первой группы входов И первого элемента И-ИЛИ-НЕ 13 и второй группы входов И третьего элемента И-ИЛИ-НЕ 15, вход управления 8 соединен со вторыми входами первых групп входов И первого 13 и второго 14 элементов И-ИЛИ-НЕ и третьими входами первой и второй групп входов И третьего элемента И-ИЛИ-НЕ 15, выход первого элемента И-ИЛИ-НЕ 13 подключен к входу второй группы входов И второго элемента И-ИЛИ-НЕ 14, второму входу первой группы входов И третьего элемента И-ИЛИ-НЕ 15 и информационному выходу 5, выход второго элемента И-ИЛИ-НЕ 14 подключен к входу второй группы входов И первого элемента И-ИЛИ-НЕ 13, второму входу второй группы входов И третьего элемента И-ИЛИ-НЕ 15 и инверсному информационному выходу 2_6, выход третьего элемента И-ИЛИ-НЕ 15 подключен к индикаторному выходу 6.

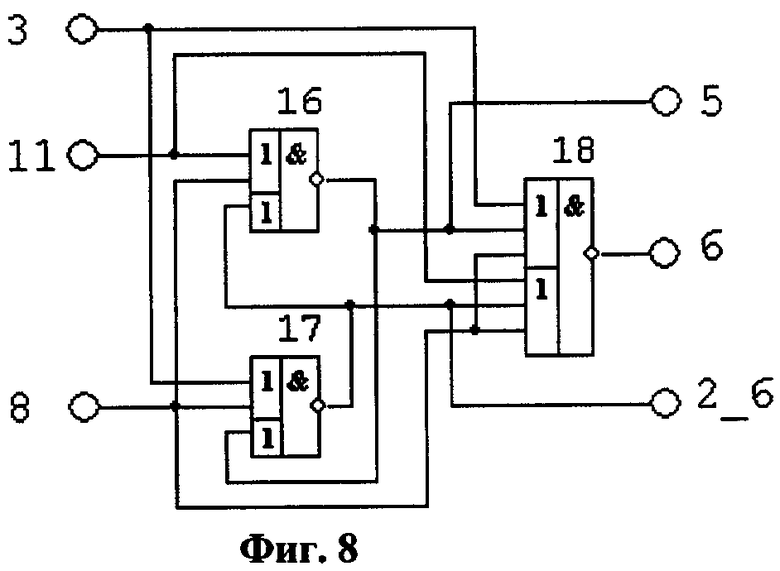

На фиг.8 изображена схема блока хранения однотактного триггера с низким рабочим уровнем входа управления [3] (элементы прототипа после применения правил булевой алгебры преобразуются к типу ИЛИ-И-НЕ). Схема содержит три элемента ИЛИ-И-НЕ 16-18, парафазный информационный вход 3, 11, вход управления 8, информационный 5 и инверсный информационный 2_6 выходы, индикаторный выход 6, прямая составляющая 3 парафазного информационного входа подключена к первым входам первых групп входов ИЛИ второго 17 и третьего 18 элементов ИЛИ-И-НЕ, инверсная составляющая 11 парафазного информационного входа подключена к первьм входам первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 16 и второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ 18, вход управления 8 соединен со вторыми входами первых групп входов ИЛИ первого 16 и второго 17 элементов ИЛИ-И-НЕ и третьими входами первой и второй групп входов ИЛИ третьего элемента ИЛИ-И-НЕ 18, выход первого элемента ИЛИ-И-НЕ 16 подключен к входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 17, второму входу первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ 18 и информационному выходу 5, выход второго элемента ИЛИ-И-НЕ 17 подключен к входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 16, второму входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ 18 и инверсному информационному выходу 2_6, выход третьего элемента ИЛИ-И-НЕ 18 подключен к индикаторному выходу 6.

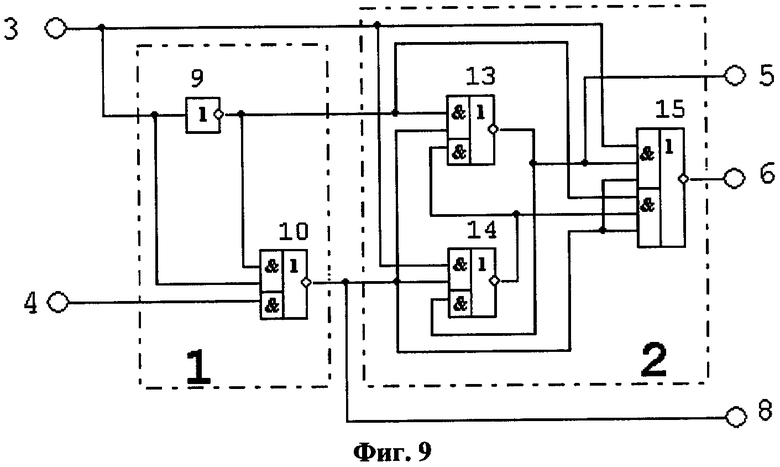

Таким образом, в простейшем случае однотактный самосинхронный триггер с однофазным информационным входом реализуется схемой, представленной на фиг.9. Схема содержит блок конвертирования 1, реализованный на инверторе 9 и элементе И-ИЛИ-НЕ 10, блок хранения 2, включающий бистабильную ячейку на элементах И-ИЛИ-НЕ 13 и 14 и индикаторный элемент И-ИЛИ-НЕ 15, однофазный информационный вход 3, вход управления 4, информационный 5 и инверсный информационный 2_6 выходы, индикаторный выход 6 и выход обратной связи 8.

Описанный выше триггер не имеет входов установки нуля и единицы, что в ряде практических случаев является существенным недостатком. Однако предлагаемые варианты блока хранения и триггера легко преобразуются в схему с предустановкой.

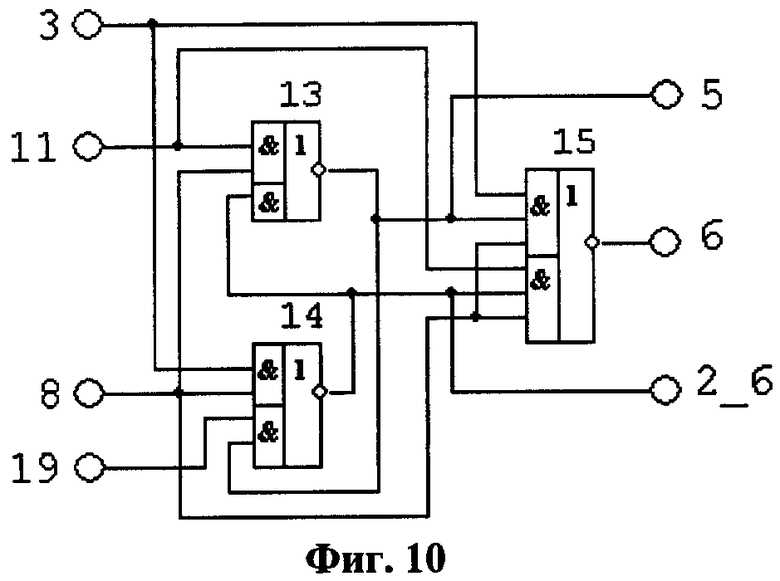

На фиг.10 изображена схема блока хранения однотактного триггера с высоким рабочим уровнем входа управления 8, имеющая дополнительный вход установки нуля 19. Она отличается от схемы на фиг.7 тем, что во вторую группу входов И второго элемента И-ИЛИ-НЕ 14 введен второй вход, подключенный к входу установки нуля 19.

Схема работает следующим образом. Запись нового состояния с парафазного информационного входа 3, 11 обеспечивается подачей на вход управления 8 высокого уровня с выхода управления блока конвертирования. Если на входе 3 при этом высокий уровень, элемент И-ИЛИ-НЕ 14 переключится в состояние низкого уровня (логического "0"), а элемент И-ИЛИ-НЕ 13 - в состояние логической "1". При этом индикаторный выход 6 переходит в состояние "0". При низком уровне сигнала на входе управления 8 бистабильная ячейка на элементах 13 и 14 запирается по входам, сохраняя состояние своих выходов. При этом индикаторный выход 6 перейдет в состояние "1". Элемент И-ИЛИ-НЕ 15 выполняет функцию индикатора окончания переходных процессов во всех элементах триггера. Значение "0" на выходе элемента 15 свидетельствует об окончании переключения триггера в рабочую фазу, а значение "1" - об окончании переключения триггера в спейсер - фазу хранения своего состояния, обеспечивая тем самым самосинхронность его функционирования.

Установка нуля осуществляется подачей на вход управления 8 и на вход установки нуля 19 низкого уровня. В результате выход элемента И-ИЛИ-НЕ 14, формирующий инверсный информационный выход блока хранения 2_6, переключается в состояние логической "1", а элемент И-ИЛИ-НЕ 13, формирующий информационный выход триггера 5, вслед за этим переходит в состояние логического ”0", завершая установку.

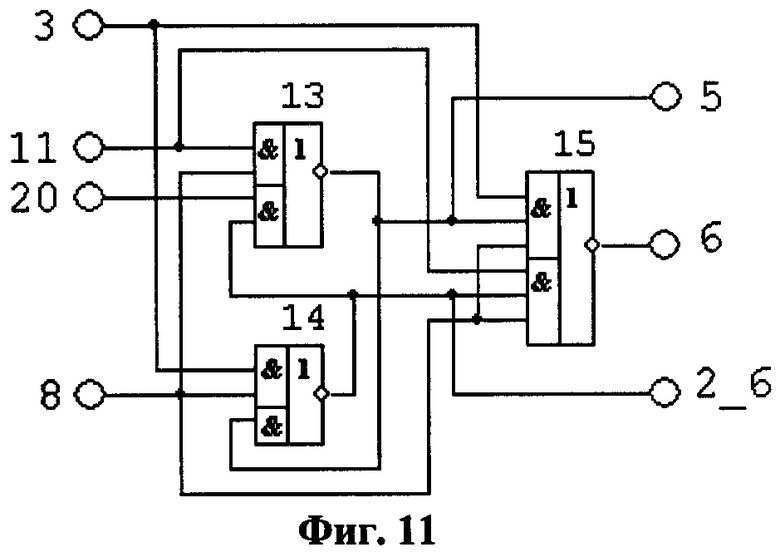

На фиг.11 изображена схема блока хранения однотактного триггера с высоким рабочим уровнем входа управления 8 и с входом установки единицы 20. Схема отличается от схемы на фиг.7 тем, что во вторую группу входов И элемента И-ИЛИ-НЕ 13 добавлен второй вход, подключенный к входу установки единицы 20. Установка единицы осуществляется подачей на вход управления 8 и на вход установки 20 низкого уровня. В результате выход элемента И-ИЛИ-НЕ 13, формирующий информационный выход триггера 5, переключается в состояние логической "1", а выход элемента И-ИЛИ-НЕ 14 вслед за этим переходит в состояние логического "0".

На фиг.12 изображена схема блока хранения однотактного триггера с высоким рабочим уровнем входа управления 8 и с входами установки нуля 19 и единицы 20. Схема отличается от схемы на фиг.10 тем, что во вторую группу входов И элемента И-ИЛИ-НЕ 13 добавлен второй вход, подключенный к входу установки единицы 20. Установка нуля или единицы осуществляется способом, описанным выше. Одновременная подача на входы установки нуля 19 и единицы 20 низкого уровня запрещена.

Аналогичным образом строятся схемы блока хранения в случае, когда запись нового состояния в него разрешается при низком уровне на входе управления.

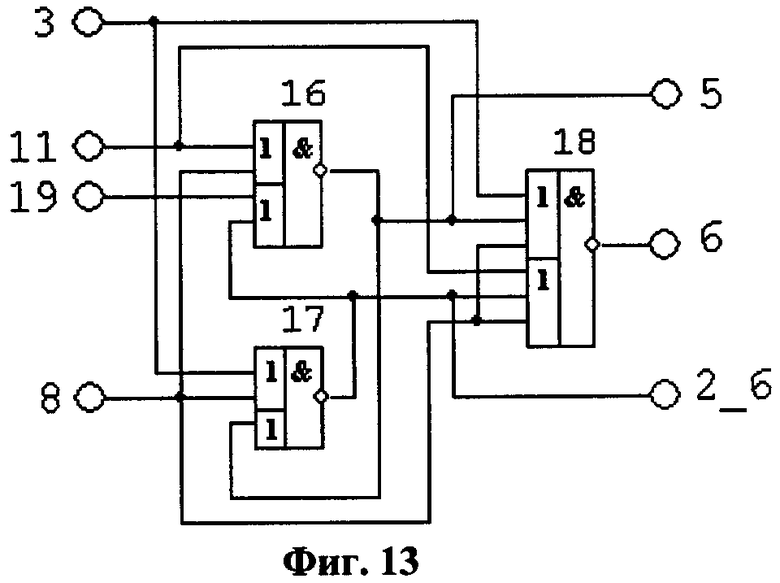

На фиг.13 изображена схема блока хранения однотактного триггера с низким рабочим уровнем входа управления 8, имеющая дополнительный вход установки нуля 19. Она отличается от схемы на фиг.8 тем, что во вторую группу входов ИЛИ первого элемента ИЛИ-И-НЕ 16 введен второй вход, подключенный к входу установки нуля 19.

Схема работает следующим образом. Запись нового состояния с парафазного информационного входа 3, 11 обеспечивается подачей на вход управления 8 низкого уровня. Если на входе 3 при этом низкий уровень, элемент ИЛИ-И-НЕ 17 переключится в состояние логической "1", а элемент ИЛИ-И-НЕ 16 - в состояние логического "0". При этом индикаторный выход 6 переходит в состояние "1". При высоком уровне сигнала на входе управления 8 бистабильная ячейка на элементах 16 и 17 запирается по входам, сохраняя состояние своих выходов, а индикаторный выход 6 перейдет в состояние "0".

Установка нуля осуществляется подачей на вход управления 8 и на вход установки нуля 19 высокого уровня. В результате выход элемента ИЛИ-И-НЕ 16, формирующий информационный выход триггера 5, переключается в состояние логического "0", а элемент ИЛИ-И-НЕ 17, формирующий инверсный информационный выход блока хранения 2_6, вслед за этим переходит в состояние логической "1", завершая установку.

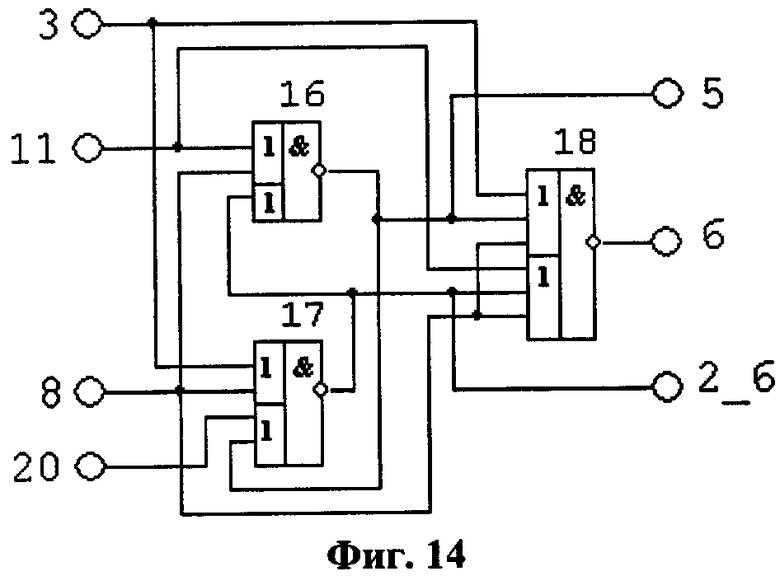

На фиг.14 изображена схема блока хранения однотактного триггера с низким рабочим уровнем входа управления 8 и с входом установки единицы 20. Схема отличается от схемы на фиг.8 тем, что во вторую группу входов ИЛИ элемента ИЛИ-И-НЕ 17 добавлен второй вход, подключенный к входу установки единицы 20. Установка единицы осуществляется подачей на вход управления 8 и на вход установки 20 высокого уровня. В результате выход элемента ИЛИ-И-НЕ 17, формирующий инверсный информационный выход блока хранения 2_6, переключается в состояние логического "0", а выход элемента ИЛИ-И-НЕ 16, формирующий информационный выход триггера 5, вслед за этим переходит в состояние логической "1".

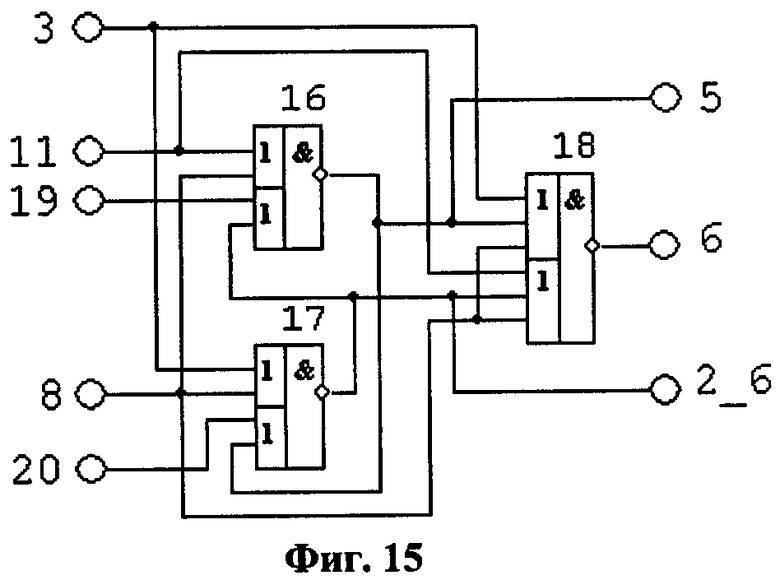

На фиг.15 изображена схема блока хранения однотактного триггера с низким рабочим уровнем входа управления 8 и с входами установки нуля 19 и единицы 20. Схема отличается от схемы на фиг.13 тем, что во вторую группу входов ИЛИ элемента ИЛИ-И-НЕ 17 добавлен второй вход, подключенный к входу установки единицы 20. Установка нуля или единицы осуществляется способом, описанным выше. Одновременная подача на входы установки нуля 19 и единицы 20 высокого уровня запрещена.

Установка нуля и/или единицы в описанных выше вариантах реализации блока хранения может быть как синхронной, так и самосинхронной. В случае синхронной установки, традиционно использующейся для начальной установки схемы после включения питания, предполагается, что схема установится в требуемое состояние спустя определенное время. При этом длительность сигнала установки выбирается с запасом, достаточным для успешного завершения установки в схеме. В случае самосинхронной установки вводится дополнительная схема индикации момента завершения установки, описанная ниже. Она контролирует соответствующий выход, переключающийся в процессе установки последним. В обоих случаях индикаторный элемент остается в спейсерном состоянии, поскольку вход управления находится в спейсере.

Приведенные выше реализации блока хранения являются однотактными и не могут использоваться для построения на их основе, например, регистров сдвига. Для того чтобы предлагаемый триггер мог использоваться в качестве разряда регистра сдвига, блок хранения должен быть реализован на двух последовательных бистабильных ячейках с противофазным управлением. При этом выходы обеих бистабильных ячеек должны быть проиндицированы. Блок конвертирования не изменяется и соответствует схемам на фиг.5 или 6 в зависимости от рабочего состояния входа управления.

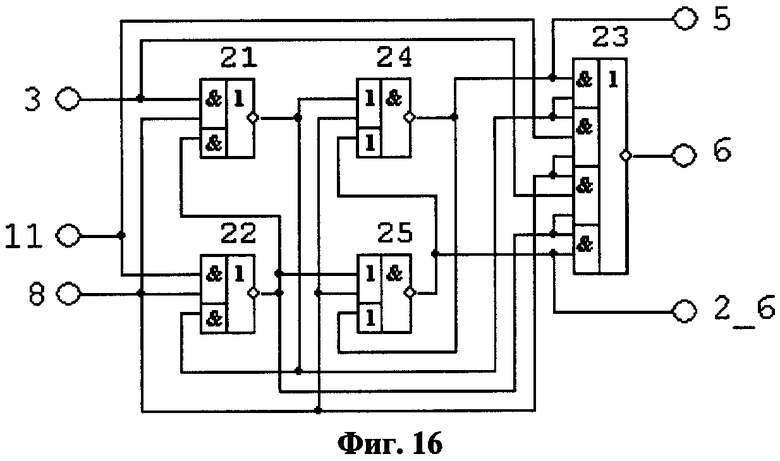

На фиг.16 приведена схема блока хранения двухтактного самосинхронного триггера для случая, когда запись нового состояния происходит при высоком уровне его входа управления. Она получается путем применения правил булевой алгебры к схеме двухтактного самосинхронното триггера [4].

Схема содержит три элемента И-ИЛИ-НЕ 21-23, два элемента ИЛИ-И-НЕ 24-25, прямую 3 и инверсную 11 составляющие парафазного информационного входа, вход управления 8, информационный выход 5, инверсный информационный выход 2_6 и индикаторный выход 6, прямая составляющая парафазного информационного входа 3 подключена к первому входу первой группы входов И элемента И-ИЛИ-НЕ 21 и второму входу третьей группы входов И элемента И-ИЛИ-НЕ 23, инверсная составляющая парафазного информационного входа 11 подключена к первому входу первой группы входов И элемента И-ИЛИ-НЕ 22 и второму входу второй группы входов И элемента И-ИЛИ-НЕ 23, вход управления 8 соединен со вторыми входами первых групп входов И элементов И-ИЛИ-НЕ 21 и 22 и первых групп входов ИЛИ элементов ИЛИ-И-НЕ 24 и 25, с третьим входом второй группы входов И и первым входом третьей группы входов И элемента И-ИЛИ-НЕ 23, выход элемента И-ИЛИ-НЕ 21 подключен ко второму входу первой группы входов И и первому входу второй группы входов И элемента И-ИЛИ-НЕ 23, входу второй группы входов И элемента И-ИЛИ-НЕ 22 и первому входу первой группы входов ИЛИ элемента ИЛИ-И-НЕ 24, выход которого соединен с входом второй группы входов ИЛИ элемента ИЛИ-И-НЕ 25, первым входом первой группы входов И элемента И-ИЛИ-НЕ 23 и информационным выходом блока хранения 5, выход элемента И-ИЛИ-НЕ 22 соединен с третьим входом третьей группы входов И и первым входом четвертой группы входов И элемента И-ИЛИ-НЕ 23, входом второй группы входов И элемента И-ИЛИ-НЕ 21 и первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ 25, выход которого соединен с входом второй группы входов ИЛИ элемента ИЛИ-И-НЕ 24, вторым входом четвертой группы входов И элемента И-ИЛИ-НЕ 23 и инверсным информационным выходом блока хранения 2_6, выход элемента И-ИЛИ-НЕ 23 подключен к индикаторному выходу 6.

Схема работает следующим образом. Запись нового состояния с парафазного информационного входа 3, 11 в бистабильную ячейку, образованную элементами 21 и 22, обеспечивается подачей на вход управления 8 высокого уровня. При этом входы бистабильной ячейки на элементах 21 и 22 открываются для записи. Если на прямой составляющей парафазного информационного входа 3 высокий уровень, элемент И-ИЛИ-НЕ 21 переключится в состояние "0", а элемент И-ИЛИ-НЕ 22 - в состояние "1". При этом индикаторный выход 6 переходит в состояние "0", а бистабильная ячейка на элементах ИЛИ-И-НЕ 24 и 25 хранит свое состояние. При низком уровне сигнала на входе управления 8 бистабильная ячейка на элементах 21 и 22 запирается по входам, сохраняя состояние своих выходов. При этом отпирается по входам вторая бистабильная ячейка на элементах ИЛИ-И-НЕ 24 и 25 и состояние выходов первой бистабильной ячейки перезаписывается во вторую бистабильную ячейку. Состояние выходов блока хранения 5 и 2_6 обновляется, а индикаторный выход 6 переходит в состояние "1". Элемент И-ИЛИ-НЕ 23 выполняет функцию индикатора окончания переходных процессов во всех элементах и на всех входах двухтактного триггера. Значение "0" на выходе элемента 23 свидетельствует об окончании переключения триггера в рабочую фазу - фиксации значения парафазного информационного входа 3, 11 на выходах первой бистабильной ячейки на элементах 21 и 22, а значение "1" - об окончании переключения триггера в спейсер - фазу хранения состояния первой бистабильной ячейки и обновления состояния выходов второй бистабильной ячейки на элементах 24 и 25, обеспечивая тем самым самосинхронность его функционирования.

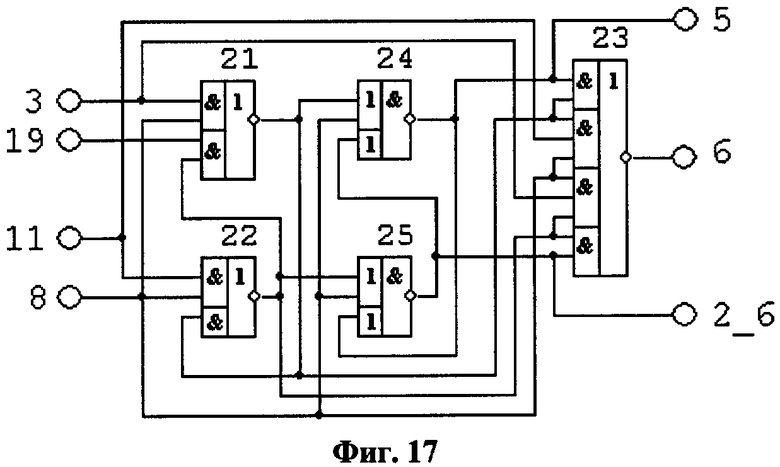

На фиг.17 изображена схема блока хранения двухтактного триггера с входом установки нуля 19 и высоким рабочим уровнем входа управления 8. Схема отличается от схемы на фиг.16 тем, что во вторую группу входов И элемента И-ИЛИ-НЕ 21 введен второй вход, подключенный к входу установки нуля 19. Установка нуля осуществляется подачей на вход управления 8 и на вход установки нуля 19 низкого уровня. В результате выход элемента И-ИЛИ-НЕ 21 переключается в состояние логической "1", элемент И-ИЛИ-НЕ 22 - в "0", элемент ИЛИ-И-НЕ 25, формирующий инверсный информационный выход блока хранения 2_6, - в "1", а элемент ИЛИ-И-НЕ 24, формирующий информационный выход блока хранения 5, - в "0", завершая установку.

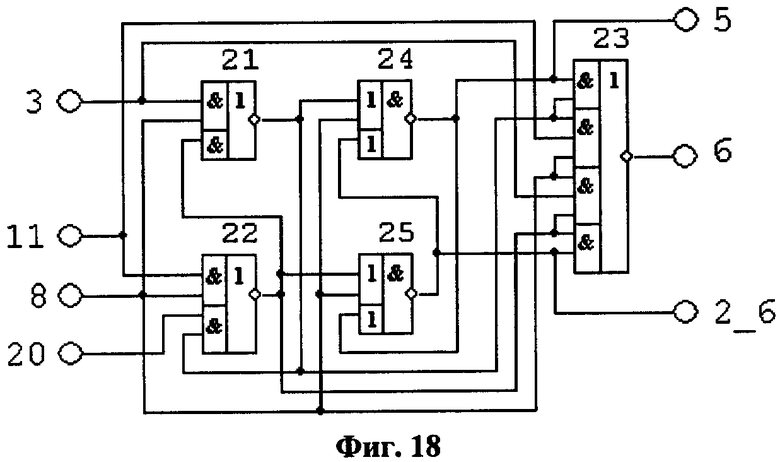

На фиг.18 изображена схема блока хранения двухтактного триггера с входом установки единицы 20 и высоким рабочим уровнем входа управления 8. Схема отличается от схемы на фиг.16 тем, что во вторую группу входов И элемента И-ИЛИ-НЕ 22 введен второй вход, подключенный к входу установки единицы 20. Установка единицы осуществляется подачей на вход управления 8 и на вход установки единицы 20 низкого уровня ("0"). В результате выход элемента И-ИЛИ-НЕ 22 переключается в состояние логической "1", выход элемента И-ИЛИ-НЕ 21 - в "0", элемент ИЛИ-И-НЕ 24, формирующий информационный выход блока хранения 5, - в "1", а элемент ИЛИ-И-НЕ 25, формирующий инверсный информационный выход блока хранения 2_6, - в "0", завершая установку.

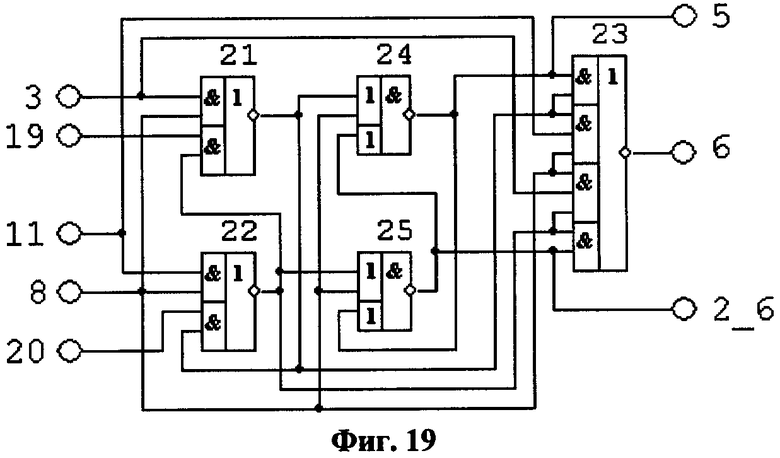

На фиг.19 изображена схема блока хранения двухтактного триггера с входами установки нуля 19 и единицы 20 и высоким рабочим уровнем входа управления 8. Схема отличается от схемы на фиг.17 тем, что во вторую группу входов И элемента И-ИЛИ-НЕ 22 введен второй вход, подключенный к входу установки единицы 20. Установка нуля или единицы осуществляется способом, описанным выше. Одновременная подача на входы установки нуля 19 и единицы 20 низкого уровня запрещена.

Описанные варианты реализации блока хранения двухтактного триггера с установкой нуля и/или единицы и с высоким рабочим уровнем входа управления характеризуются тем, что установка не является самосинхронной. В процессе установки переключение выходов первой и второй бистабильных ячеек приводит к кратковременному неконтролируемому переключению индикаторного выхода 6. В большинстве практических случаев это оказывается несущественным, поскольку установка триггеров осуществляется одноразово - при подаче питания на устройство, в составе которого используется триггер. Однако такое решение недопустимо для динамической установки нуля или единицы на выходах триггера в строго самосинхронных устройствах. Одним из условий принадлежности устройства к классу строго самосинхронных является отсутствие неконтролируемых переключений элементов, "дребезга" на входах элементов.

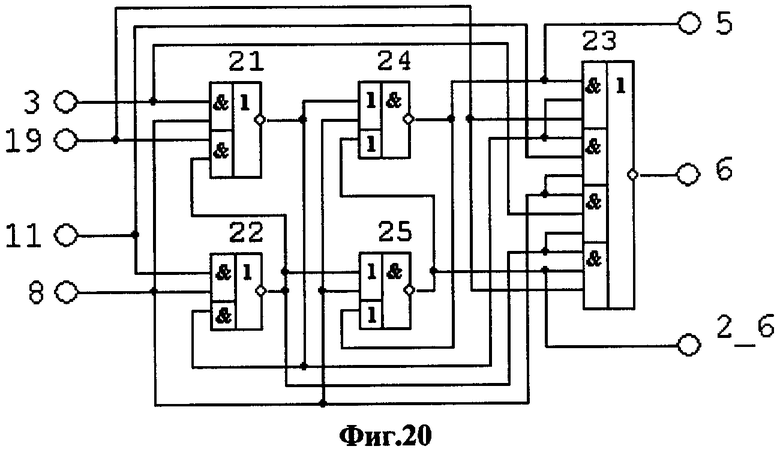

На фиг.20 изображена схема блока хранения двухтактного триггера с высоким рабочим уровнем входа управления 8 и входом установки нуля 19, удовлетворяющая требованиям, предъявляемым к строго самосинхронным схемам. Данный вариант блока хранения отличается от схемы на фиг.17 тем, что в первую и четвертую группы входов И элемента И-ИЛИ-НЕ 23 введены третьи входы, подключенные к входу установки нуля 19. Установка нуля осуществляется способом, описанным выше. Но при этом выход индикаторного элемента И-ИЛИ-НЕ 23 не изменяется, поскольку все его группы входов блокированы низкими уровнями на входах управления 8 и установки нуля 19. Индикация окончания установки блока хранения осуществляется дополнительной логикой, контролирующей переключение в состояние "0" информационного выхода блока хранения 5.

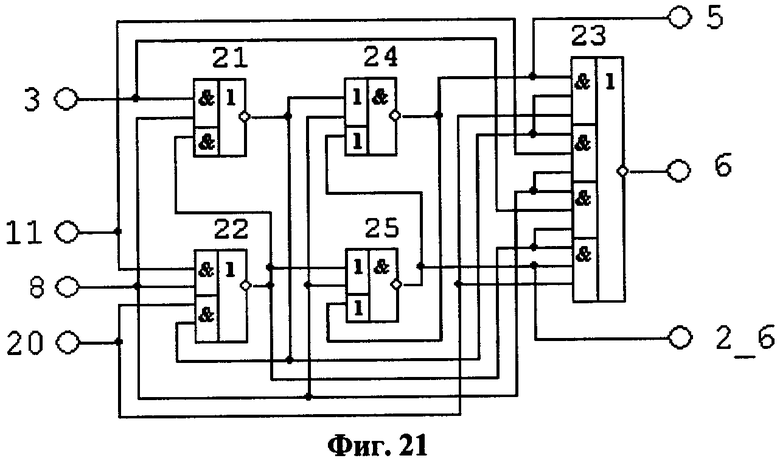

На фиг.21 изображена схема блока хранения двухтактного триггера с высоким рабочим уровнем входа управления 8 и входом установки единицы 20, удовлетворяющая требованиям, предъявляемым к строго самосинхронным схемам. Данный вариант блока хранения отличается от схемы на фиг.18 тем, что в первую и четвертую группы входов И элемента И-ИЛИ-НЕ 23 введены третьи входы, подключенные к входу установки единицы 20. Установка единицы осуществляется способом, описанным выше. Но при этом выход индикаторного элемента И-ИЛИ-НЕ 23 не изменяется, поскольку все его группы входов блокированы низким уровнем на входах управления 8 и установки единицы 20. Индикация окончания установки блока хранения осуществляется дополнительной логикой, контролирующей переключение в "0" инверсного информационного выхода блока хранения 2_6.

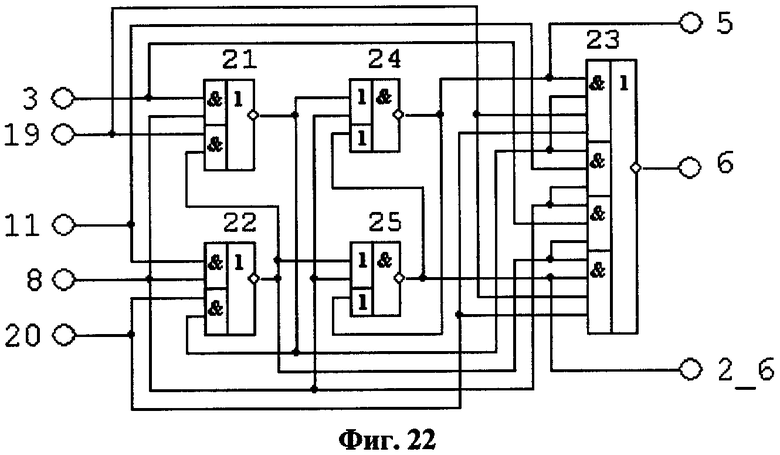

На фиг.22 изображена схема блока хранения двухтактного триггера с высоким рабочим уровнем входа управления 8 и входами установки нуля 19 и единицы 20, удовлетворяющая требованиям, предъявляемым к строго самосинхронным схемам. Данный вариант блока хранения отличается от схемы на фиг.20 тем, что в первую и четвертую группы входов И элемента И-ИЛИ-НЕ 23 введены четвертые входы, подключенные к входу установки единицы 20. Установка нуля и единицы осуществляется способом, описанным выше. Но при этом выход индикаторного элемента И-ИЛИ-НЕ 23 не изменяется, поскольку все его группы входов блокированы низким уровнем на входе установки нуля 19 (или единицы 20) и входе управления 8. Индикация окончания установки блока хранения осуществляется дополнительной логикой, контролирующей переключение в состояние "0" информационного выхода триггера 5 (при установке нуля) или переключение в состояние "0" инверсного информационного выхода блока хранения 2_6 (при установке единицы).

Одновременная подача на входы установки нуля 19 и единицы 20 низкого уровня запрещена.

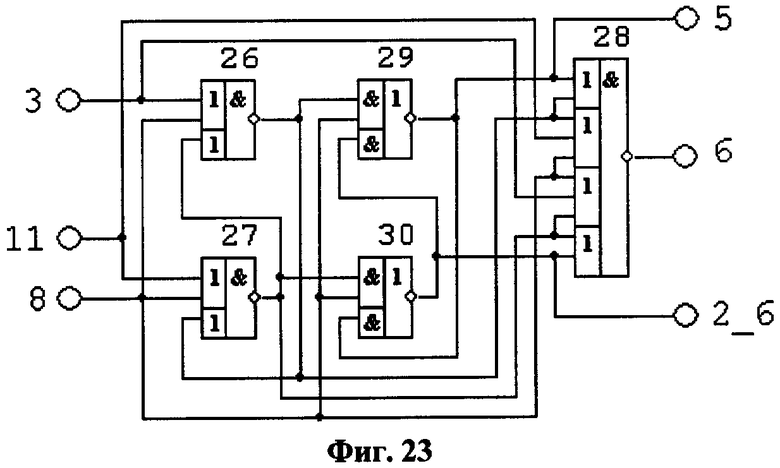

На фиг.23 изображена схема блока хранения двухтактного триггера для случая, когда запись нового состояния в блок хранения происходит при низком уровне входа управления 8. Она получается путем применения правил булевой алгебры к схеме двухтактного самосинхронного триггера [5].

Схема содержит три элемента ИЛИ-И-НЕ 26-28, два элемента И-ИЛИ-НЕ 29-30, прямую 3 и инверсную 11 составляющие парафазного информационного входа, вход управления 8, информационный выход 5, инверсный информационный выход 2_6 и индикаторный выход 6, прямая составляющая парафазного информационного входа 3 подключена к первому входу первой группы входов ИЛИ элемента ИЛИ-И-НЕ 26 и второму входу третьей группы входов ИЛИ элемента ИЛИ-И-НЕ 28, инверсная составляющая парафазного информационного входа 11 подключена к первому входу первой группы входов ИЛИ элемента ИЛИ-И-НЕ 27 и второму входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ 28, вход управления 8 соединен со вторыми входами первых групп входов ИЛИ элементов ИЛИ-И-НЕ 26 и 27 и первых групп входов И элементов И-ИЛИ-НЕ 29 и 30, с третьим входом второй группы входов ИЛИ и первым входом третьей группы входов ИЛИ элемента ИЛИ-И-НЕ 28, выход элемента ИЛИ-И-НЕ 26 подключен ко второму входу первой группы входов ИЛИ и первому входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ 28, входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ 27 и первому входу первой группы входов И элемента И-ИЛИ-НЕ 29, выход которого соединен с входом второй группы входов И элемента И-ИЛИ-НЕ 30, первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ 28 и информационным выходом блока хранения 5, выход элемента ИЛИ-И-НЕ 27 соединен с третьим входом третьей группы входов ИЛИ и первым входом четвертой группы входов ИЛИ элемента ИЛИ-И-НЕ 28, входом второй группы входов ИЛИ элемента ИЛИ-И-НЕ 26 и первым входом первой группы входов И элемента И-ИЛИ-НЕ 30, выход которого соединен с входом второй группы входов И элемента И-ИЛИ-НЕ 29, вторым входом четвертой группы входов ИЛИ элемента ИЛИ-И-НЕ 28 и инверсным информационным выходом блока хранения 2_6, выход элемента ИЛИ-И-НЕ 28 подключен к индикаторному выходу 6.

Схема работает следующим образом. Запись нового состояния с парафазного информационного входа 3, 11 в бистабильную ячейку, образованную элементами 26 и 27, обеспечивается подачей на вход управления 8 низкого уровня. При этом входы бистабильной ячейки на элементах 26 и 27 открываются для записи. Если на прямой составляющей парафазного информационного входа 3 низкий уровень, элемент ИЛИ-И-НЕ 26 переключится в состояние "1", а элемент ИЛИ-И-НЕ 27 - в состояние "0". При этом индикаторный выход 6 переходит в состояние "1", а бистабильная ячейка на элементах И-ИЛИ-НЕ 29 и 30 хранит свое состояние. При высоком уровне сигнала на входе управления 8 бистабильная ячейка на элементах 26 и 27 запирается по входам, сохраняя состояние своих выходов. При этом отпирается по входам вторая бистабильная ячейка на элементах И-ИЛИ-НЕ 29 и 30 и состояние выходов первой бистабильной ячейки перезаписывается во вторую бистабильную ячейку. Состояние выходов блока хранения 5 и 2_6 обновляется, а индикаторный выход 6 переходит в состояние "0". Элемент ИЛИ-И-НЕ 28 выполняет функцию индикатора окончания переходных процессов во всех элементах и на всех входах блока хранения двухтактного триггера. Значение "1" на выходе элемента 28 свидетельствует об окончании переключения блока хранения в рабочую фазу - фиксации значения парафазного информационного входа 3, 11 на выходах первой бистабильной ячейки на элементах 26 и 27, а значение "0" - об окончании переключения блока хранения в спейсер - фазу хранения состояния первой бистабильной ячейки и обновления состояния выходов второй бистабильной ячейки на элементах 29 и 30, обеспечивая тем самым самосинхронность его функционирования.

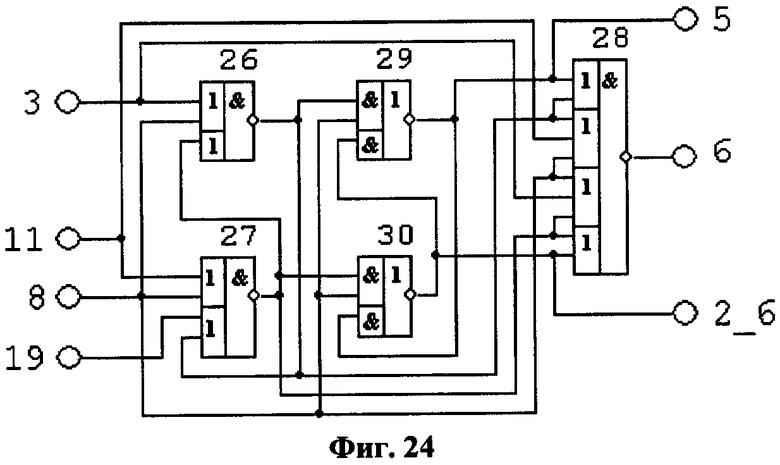

На фиг.24 изображена схема блока хранения двухтактного триггера с входом установки нуля 19 и низким рабочим уровнем входа управления 8. Схема отличается от схемы на фиг.23 тем, что во вторую группу входов ИЛИ элемента ИЛИ-И-НЕ 27 введен второй вход, подключенный к входу установки нуля 19. Установка нуля осуществляется подачей на вход управления 8 и на вход установки нуля 19 высокого уровня. В результате выход элемента ИЛИ-И-НЕ 27 переключается в состояние логического "0", элемент ИЛИ-И-НЕ 26 - в "1", элемент И-ИЛИ-НЕ 29, формирующий информационный выход блока хранения 5, - в "0", а элемент И-ИЛИ-НЕ 30, формирующий инверсный информационный выход блока хранения 2_6, - в "1", завершая установку.

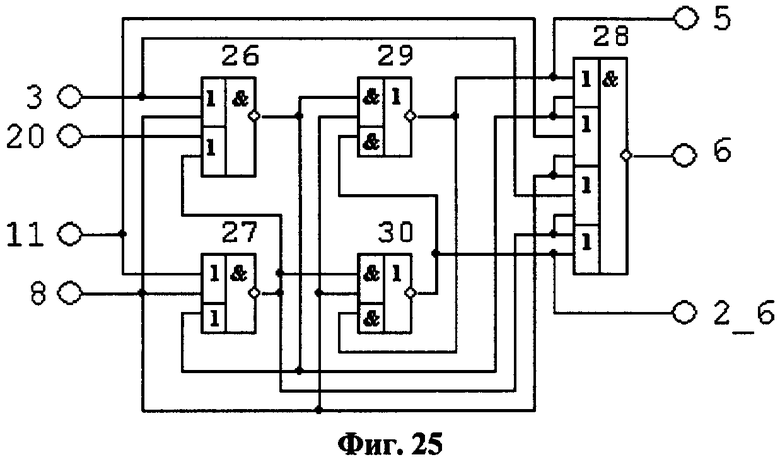

На фиг.25 изображена схема блока хранения двухтактного триггера с входом установки единицы 20 и низким рабочим уровнем входа управления 8. Схема отличается от схемы на фиг.23 тем, что во вторую группу входов ИЛИ элемента ИЛИ-И-НЕ 26 введен второй вход, подключенный к входу установки единицы 20. Установка единицы осуществляется подачей на вход управления 8 и на вход установки единицы 20 высокого уровня. В результате выход элемента ИЛИ-И-НЕ 26 переключается в состояние логического "0", выход элемента ИЛИ-И-НЕ 27 - в "1", элемент И-ИЛИ-НЕ 30, формирующий инверсный информационный выход блока хранения 2_6, - в "0", а элемент И-ИЛИ-НЕ 29, формирующий информационный выход блока хранения 5, - в "1", завершая установку.

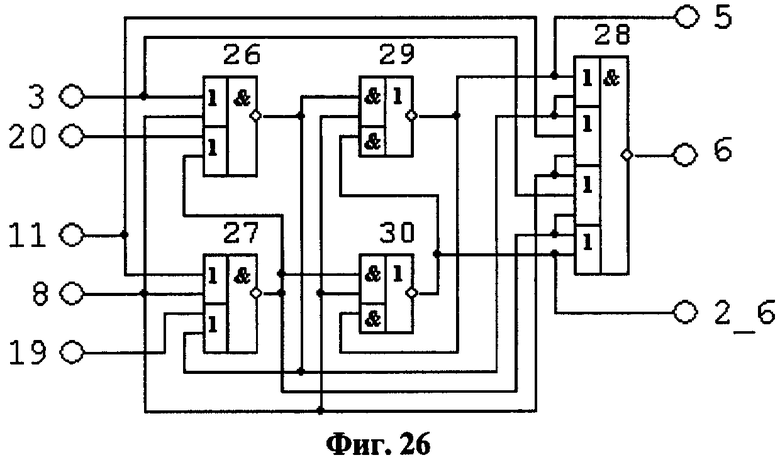

На фиг.26 изображена схема блока хранения двухтактного триггера с входами установки нуля 19 и единицы 20 и низким рабочим уровнем входа управления 8. Схема отличается от схемы на фиг.24 тем, что во вторую группу входов ИЛИ элемента ИЛИ-И-НЕ 26 введен второй вход, подключенный к входу установки единицы 20. Установка нуля или единицы осуществляется способом, описанным выше. Одновременная подача на входы установки нуля 19 и единицы 20 высокого уровня запрещена.

Описанные варианты реализации блока хранения двухтактного триггера с установкой нуля и/или единицы и с низким рабочим уровнем входа управления характеризуются тем, что установка не является самосинхронной. В процессе установки переключение выходов первой и второй бистабильных ячеек приводит к кратковременному неконтролируемому переключению индикаторного выхода 6. Такое решение недопустимо для динамической установки нуля или единицы на выходах триггера в строго самосинхронных устройствах.

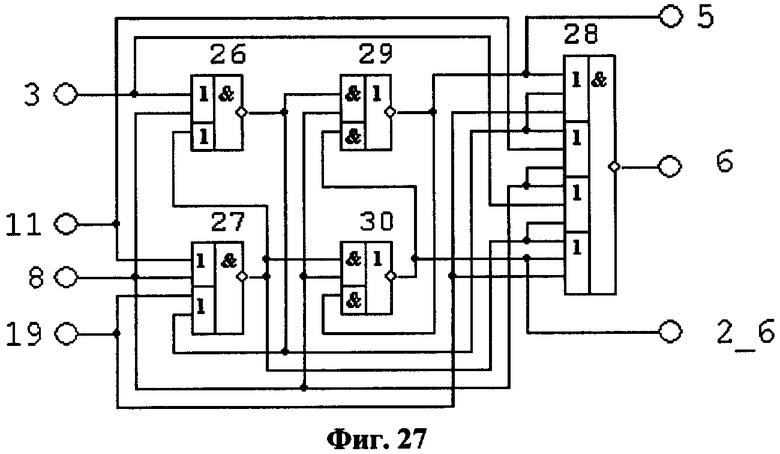

На фиг.27 изображена схема блока хранения двухтактного триггера с низким рабочим уровнем входа управления 8 и входом установки нуля 19, удовлетворяющая требованиям, предъявляемым к строго самосинхронным схемам. Данный вариант блока хранения отличается от схемы на фиг.24 тем, что в первую и четвертую группы входов ИЛИ элемента ИЛИ-И-НЕ 28 введены третьи входы, подключенные к входу установки нуля 19. Установка нуля осуществляется способом, описанным выше. Но при этом выход индикаторного элемента ИЛИ-И-НЕ 28 не изменяется, поскольку все его группы входов блокированы высокими уровнями на входах управления 8 и установки нуля 19. Индикация окончания установки блока хранения осуществляется дополнительной логикой, контролирующей переключение в состояние "1" инверсного информационного выхода блока хранения 2_6.

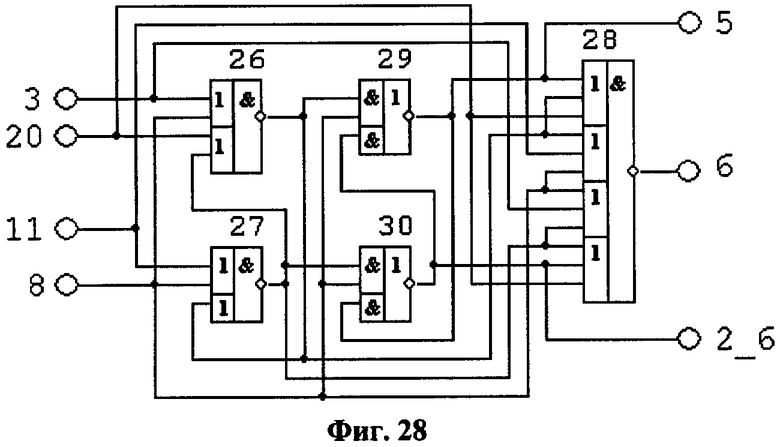

На фиг.28 изображена схема блока хранения двухтактного триггера с низким рабочим уровнем входа управления 8 и входом установки единицы 20, удовлетворяющая требованиям, предъявляемым к строго самосинхронным схемам. Данный вариант блока хранения отличается от схемы на фиг.25 тем, что в первую и четвертую группы входов ИЛИ элемента ИЛИ-И-НЕ 28 введены третьи входы, подключенные к входу установки единицы 20. Установка единицы осуществляется способом, описанным выше. Но при этом выход индикаторного элемента ИЛИ-И-НЕ 28 не изменяется, поскольку все его группы входов блокированы высоким уровнем на входах управления 8 и установки единицы 20. Индикация окончания установки блока хранения осуществляется дополнительной логикой, контролирующей переключение в "1" информационного выхода триггера 5.

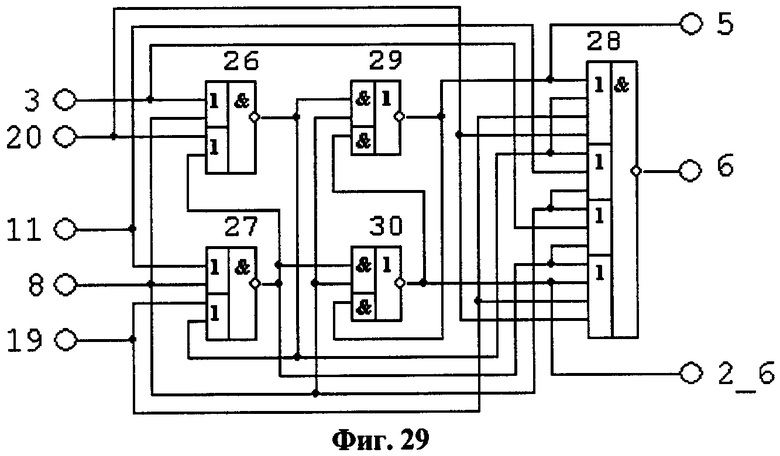

На фиг.29 изображена схема блока хранения двухтактного триггера с низким рабочим уровнем входа управления 8 и входами установки нуля 19 и единицы 20, удовлетворяющая требованиям, предъявляемым к строго самосинхронным схемам. Данный вариант блока хранения отличается от схемы на фиг.27 тем, что в первую и четвертую группы входов ИЛИ элемента ИЛИ-И-НЕ 28 введены четвертые входы, подключенные к входу установки единицы 20. Установка нуля и единицы осуществляется способом, описанным выше. Но при этом выход индикаторного элемента ИЛИ-И-НЕ 28 не изменяется, поскольку все его группы входов блокированы высоким уровнем на входе установки нуля 19 (или единицы 20) и входе управления 8. Индикация окончания установки блока хранения осуществляется дополнительной логикой, контролирующей переключение в состояние "1" информационного выхода триггера 5 (при установке единицы) или переключение в состояние "1" инверсного информационного выхода блока хранения 2_6 (при установке нуля). Одновременная подача на входы установки нуля 19 и единицы 20 высокого уровня запрещена.

Самосинхронная предустановка нуля и единицы требует индикации окончания переключения всех элементов в процессе предустановки. Выше уже отмечалось, что для этого необходимо и достаточно контролировать состояние выхода элемента в триггере, который переключается последним. Такой элемент в предложенных реализациях однотактных и двухтактных триггеров всегда один.

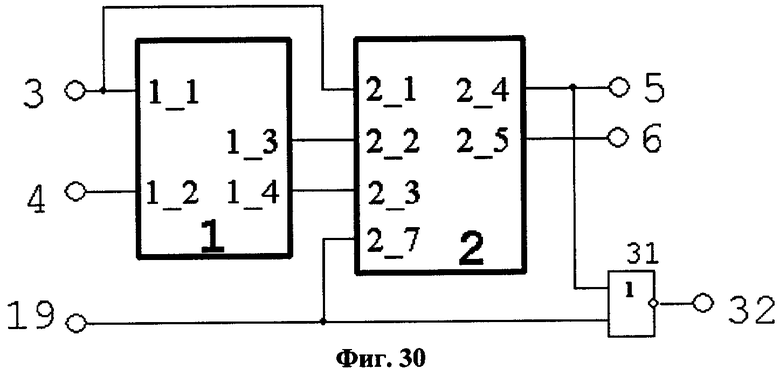

На фиг.30 показана схема самосинхронного триггера с однофазным информационным входом, сигналом управления с низким рабочим уровнем и входом установки нуля. Она отличается от схемы на фиг.2 тем, что содержит вход установки нуля 19, элемент ИЛИ-НЕ 31 и второй индикаторный выход 32, а блок хранения 2 имеет вход установки нуля 2_7, причем вход установки нуля триггера 19 подключен к входу установки нуля 2_7 блока хранения 2 и ко второму входу элемента ИЛИ-НЕ 31, первый вход которого соединен с информационным выходом триггера 5, а выход - со вторым индикаторным выходом 32 триггера.

Схема работает следующим образом. Пусть изначально триггер хранит на своем информационном выходе состояние "1". При установке нуля на управляющий вход 4 подается высокий уровень, а на вход установки нуля 19 - низкий. При этом элемент, формирующий информационный выход блока хранения и триггера, реализованного в соответствии со схемой на фиг.10 или фиг.20, переключается последним в состояние "0". Только после этого элемент ИЛИ-НЕ 31 переключится в состояние "1", фиксируя окончание установки триггера.

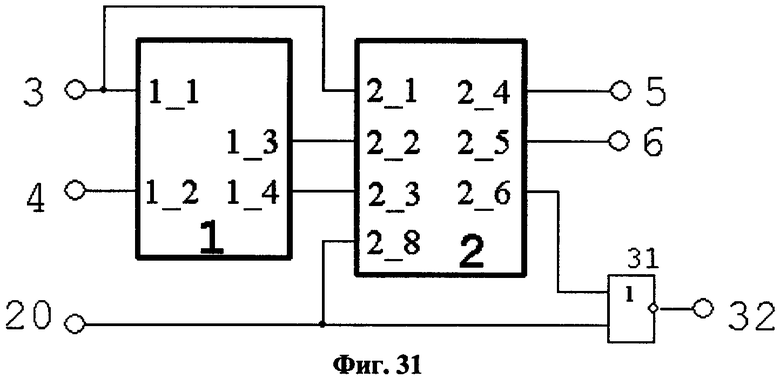

На фиг.31 показана схема самосинхронного триггера с однофазным информационным входом, сигналом управления с низким рабочим уровнем и входом установки единицы. Она отличается от схемы на фиг.2 тем, что содержит вход установки единицы 20, элемент ИЛИ-НЕ 31 и второй индикаторный выход 32, а блок хранения 2 имеет вход установки единицы 2_8, причем вход установки единицы триггера 20 подключен к входу установки единицы 2_8 блока хранения 2 и ко второму входу элемента ИЛИ-НЕ 31, первый вход которого соединен с инверсным информационным выходом блока хранения 2_6, а выход - со вторым индикаторным выходом 32 триггера.

Схема работает следующим образом. Пусть изначально триггер хранит на своем информационном выходе состояние "0". При установке единицы на управляющий вход 4 подается высокий уровень, а на вход установки единицы 20 - низкий. При этом элемент, формирующий инверсный информационный выход блока хранения и триггера, реализованного в соответствии со схемой на фиг.11 или фиг.21, переключается последним в состояние "0". Только после этого элемент ИЛИ-НЕ 31 переключится в состояние "1", фиксируя окончание установки триггера.

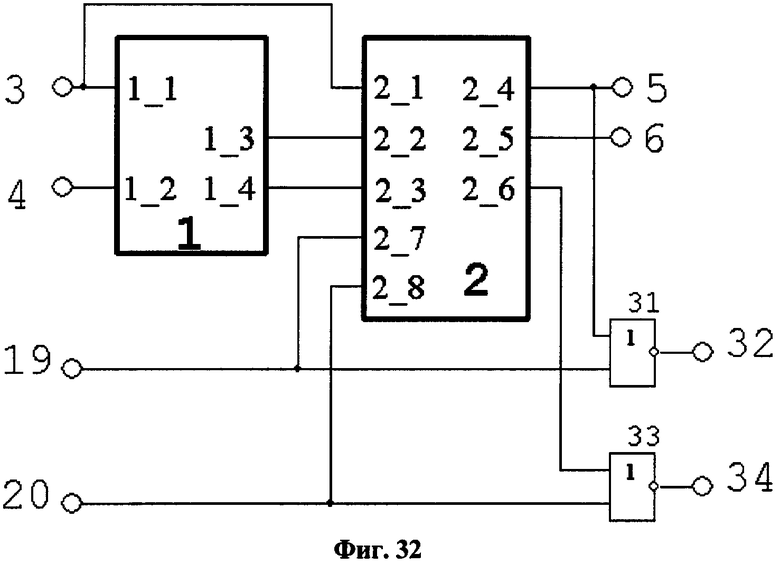

На фиг.32 показана схема самосинхронного триггера с однофазным информационным входом, сигналом управления с низким рабочим уровнем и входами установки нуля и единицы. Она отличается от схемы на фиг.30 тем, что содержит вход установки единицы 20, элемент ИЛИ-НЕ 33 и третий индикаторный выход 34, а блок хранения 2 имеет вход установки единицы 2_8, причем вход установки единицы триггера 20 подключен к входу установки единицы 2_8 блока хранения 2 и ко второму входу элемента ИЛИ-НЕ 33, первый вход которого соединен с инверсным информационным выходом блока хранения 2_6, а выход - с третьим индикаторным выходом 34 триггера. Наличие двух индикаторных элементов ИЛИ-НЕ 31 и 33 позволяет независимо индицировать установку нуля и единицы. Установка нуля и единицы реализуется описанным выше способом.

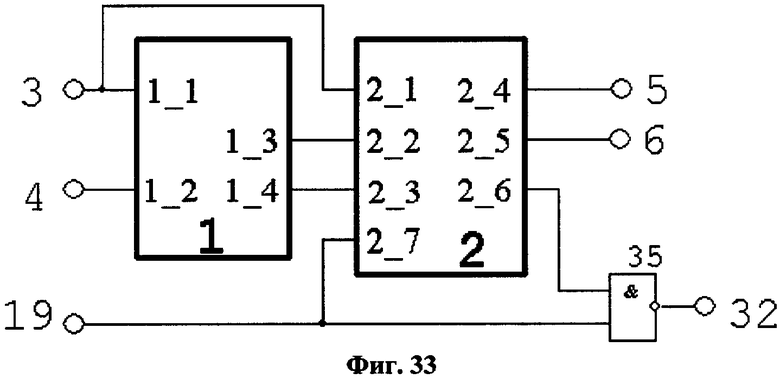

На фиг.33 показана схема самосинхронного триггера с однофазным информационным входом, сигналом управления с высоким рабочим уровнем и входом установки нуля. Она отличается от схемы на фиг.2 тем, что содержит вход установки нуля 19, элемент И-НЕ 35 и второй индикаторный выход 32, а блок хранения 2 имеет вход установки нуля 2_7, причем вход установки нуля триггера 19 подключен к входу установки нуля 2_7 блока хранения 2 и ко второму входу элемента И-НЕ 35, первый вход которого соединен с инверсным информационным выходом блока хранения 2_6, а выход - со вторым индикаторным выходом 32 триггера.

Схема работает следующим образом. Пусть изначально триггер хранит на своем информационном выходе состояние "1". При установке нуля на управляющий вход 4 подается низкий уровень, а на вход установки нуля 19 - высокий. При этом элемент, формирующий инверсный информационный выход блока хранения и триггера, реализованного в соответствии со схемой на фиг.13 или фиг.27, переключается последним в состояние "1". Только после этого элемент И-НЕ 35 переключится в состояние "0", фиксируя окончание установки триггера.

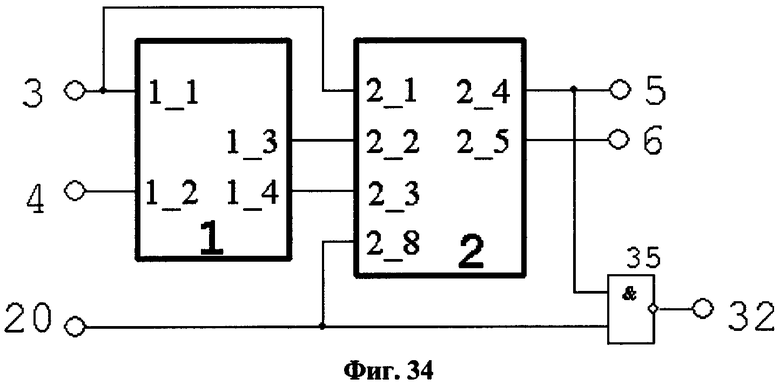

На фиг.34 показана схема самосинхронного триггера с однофазным информационным входом, сигналом управления с высоким рабочим уровнем и входом установки единицы. Она отличается от схемы на фиг.2 тем, что содержит вход установки единицы 20, элемент И-НЕ 35 и второй индикаторный выход 32, а блок хранения 2 имеет вход установки единицы 2_8, причем вход установки единицы триггера 20 подключен к входу установки единицы 2_8 блока хранения 2 и ко второму входу элемента И-НЕ 35, первый вход которого соединен с информационным выходом триггера 5, а выход - со вторым индикаторным выходом 32 триггера.

Схема работает следующим образом. Пусть изначально триггер хранит на своем информационном выходе состояние "0". При установке единицы на управляющий вход 4 подается низкий уровень, а на вход установки единицы 20 - высокий. При этом элемент, формирующий информационный выход блока хранения и триггера, реализованного в соответствии со схемой на фиг.14 или фиг.28, переключается последним в состояние "1". Только после этого элемент И-НЕ 35 переключится в состояние "0", фиксируя окончание установки триггера.

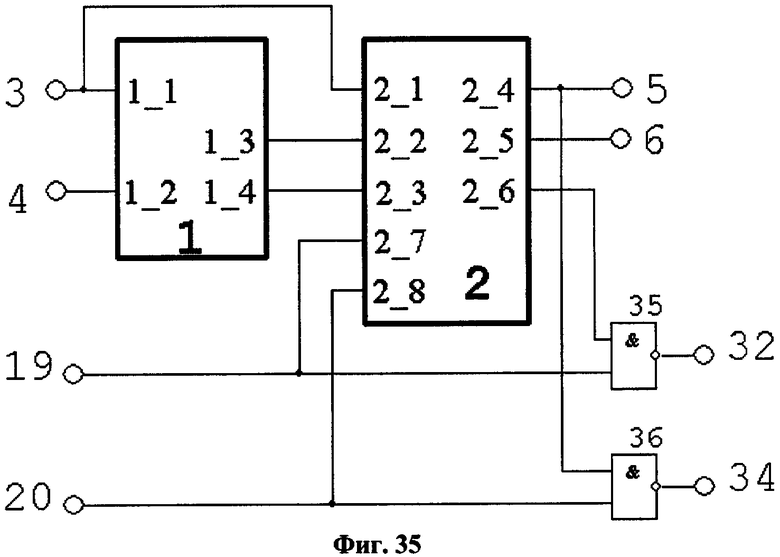

На фиг.35 показана схема самосинхронного триггера с однофазным информационным входом, сигналом управления с высоким рабочим уровнем и входами установки нуля и единицы. Она отличается от схемы на фиг.33 тем, что содержит вход установки единицы 20, элемент И-НЕ 36 и третий индикаторный выход 34, а блок хранения 2 имеет вход установки единицы 2_8, причем вход установки единицы триггера 20 подключен к входу установки единицы 2_8 блока хранения 2 и ко второму входу элемента И-НЕ 36, первый вход которого соединен с информационным выходом триггера 5, а выход - с третьим индикаторным выходом 34 триггера. Установка нуля и единицы реализуется описанным выше способом.

При построении многоразрядного устройства на основе предлагаемого триггера с самосинхронной предустановкой выходы индикаторных элементов ИЛИ-НЕ 31, 33 собираются элементом И-НЕ - для каждого типа установки (нуля или единицы) своим, - формируя общий индикаторный сигнал окончания установки в устройстве. Выходы же индикаторных элементов И-НЕ 35, 36 собираются элементом ИЛИ-НЕ - также своим для каждого типа установки (нуля или единицы).

Общая индикаторная подсхема установки нуля и/или единицы может быть преобразована к любому виду и любому базису реализации с помощью правил булевой алгебры.

Источники информации:

[1] Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд., испр. - Челябинск: Металлургия, Челябинское отд., 1989. - рис.1.50а.

[2] Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. // Под ред. В.И.Варшавского. - М.: Наука, 1976. - рис.2.7, б. (однотактный триггер с парафазным информационным входом и разрешением записи высоким уровнем входа управления).

[3] Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. // Под ред. В.И.Варшавского. - М.: Наука, 1976. - рис.2.7, а (однотактный триггер с парафазным информационным входом и разрешением записи низким уровнем входа управления).

[4] Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. // Под ред. В.И.Варшавского. - М.: Наука, 1976. - рис.рис.2.16, а (двухтактный триггер с парафазным информационным входом и разрешением записи высоким уровнем входа управления).

[5] Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. // Под ред. В.И.Варшавского. - М.: Наука, 1976. - рис.2.16, б (двухтактный триггер с парафазным информационным входом и разрешением записи низким уровнем входа управления).

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОСИНХРОННЫЙ ОДНОКРАТНЫЙ D-ТРИГГЕР С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362266C1 |

| САМОСИНХРОННЫЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С НИЗКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362267C1 |

| САМОСИНХРОННЫЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С НИЗКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2366080C2 |

| САМОСИНХРОННЫЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2365031C1 |

| ДВУХТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2390093C1 |

| ДВУХТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390923C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2391772C2 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390092C1 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с нулевым спейсером | 2024 |

|

RU2835382C1 |

| D-ТРИГГЕР С САМОСИНХРОННОЙ ПРЕДУСТАНОВКОЙ | 2006 |

|

RU2319297C1 |

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств. Достигаемый технический результат - обеспечение самосинхронной реализации триггера с однофазным информационным входом, гарантирующей работоспособность триггера при любых задержках составляющих его элементов. Самосинхронный триггер с однофазным информационным входом содержит блок хранения и блок конвертирования, выполненные на элементах И-ИЛИ-НЕ или ИЛИ-И-НЕ. 28 з.п. ф-лы, 35 ил.

1. Самосинхронный триггер с однофазным информационным входом, содержащий блок хранения, однофазный информационный вход, вход управления, информационный выход и индикаторный выход, причем блок хранения имеет прямую и инверсную составляющие парафазного информационного входа, вход управления, информационный выход и индикаторный выход, информационный выход блока хранения подключен к информационному выходу триггера, прямая составляющая парафазного информационного входа блока хранения соединена с однофазным информационным входом триггера, индикаторный выход блока хранения подключен к индикаторному выходу триггера, отличающийся тем, что в него введен блок конвертирования информационного сигнала и сигнала управления, имеющий информационный вход, вход управления, информационный выход и выход сигнала управления, информационный вход блока конвертирования подключен к однофазному информационному входу триггера, вход управления блока конвертирования соединен с входом управления триггера, информационный выход блока конвертирования подключен к инверсной составляющей парафазного информационного входа блока хранения, выход сигнала управления блока конвертирования соединен с входом управления блока хранения.

2. Самосинхронный триггер с однофазным информационным входом по п.1, отличающийся тем, что в схему введены инверсные информационные выходы блока хранения и триггера, соединенные друг с другом.

3. Самосинхронный триггер с однофазным информационным входом по п.1 или 2, отличающийся тем, что в схему введен выход обратной связи, подключенный к выходу сигнала управления блока конвертирования.

4. Самосинхронный триггер с однофазным информационным входом по п.1, отличающийся тем, что блок конвертирования содержит инвертор и элемент И-ИЛИ-НЕ, вход инвертора подключен к информационному входу блока конвертирования и второму входу первой группы входов И элемента И-ИЛИ-НЕ, а выход инвертора соединен с информационным выходом блока конвертирования и с первым входом первой группы входов И элемента И-ИЛИ-НЕ, вход управления блока конвертирования соединен с входом второй группы входов И элемента И-ИЛИ-НЕ, выход которого подключен к выходу управления блока конвертирования.

5. Самосинхронный триггер с однофазным информационным входом по п.1, отличающийся тем, что блок конвертирования содержит инвертор и элемент ИЛИ-И-НЕ, вход инвертора подключен к информационному входу блока конвертирования и второму входу первой группы входов ИЛИ элемента ИЛИ-И-НЕ, а выход инвертора соединен с информационным выходом блока конвертирования и с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ, вход управления блока конвертирования соединен с входом второй группы входов ИЛИ элемента ИЛИ-И-НЕ, выход которого подключен к выходу управления блока конвертирования.

6. Самосинхронный триггер с однофазным информационным входом по п.4, отличающийся тем, что в схему введены вход установки нуля и инверсный информационный выход блока хранения, блок хранения содержит три элемента И-ИЛИ-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первым входам первых групп входов И второго и третьего элементов И-ИЛИ-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первьм входам первой группы входов И первого элемента И-ИЛИ-НЕ и второй группы входов И третьего элемента И-ИЛИ-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов И первого и второго элементов И-ИЛИ-НЕ и третьими входами первой и второй групп входов И третьего элемента И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к входу второй группы входов И второго элемента И-ИЛИ-НЕ, второму входу первой группы входов И третьего элемента И-ИЛИ-НЕ и информационному выходу блока хранения, выход второго элемента И-ИЛИ-НЕ подключен к входу второй группы входов И первого элемента И-ИЛИ-НЕ и второму входу второй группы входов И третьего элемента И-ИЛИ-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов И второго элемента И-ИЛИ-НЕ блока хранения введен второй вход, подключенный к входу установки нуля, а инверсный информационный выход блока хранения подключен к выходу второго элемента И-ИЛИ-НЕ.

7. Самосинхронный триггер с однофазным информационным входом по п.4, отличающийся тем, что в схему введены вход установки единицы и инверсный информационный выход блока хранения, блок хранения содержит три элемента И-ИЛИ-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первым входам первых групп входов И второго и третьего элемента И-ИЛИ-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первым входам первой группы входов И первого элемента И-ИЛИ-НЕ и второй группы входов И третьего элемента И-ИЛИ-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов И первого и второго элементов И-ИЛИ-НЕ и третьими входами первой и второй групп входов И третьего элемента И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к входу второй группы входов И второго элемента И-ИЛИ-НЕ, второму входу первой группы входов И третьего элемента И-ИЛИ-НЕ и информационному выходу блока хранения, выход второго элемента И-ИЛИ-НЕ подключен к входу второй группы входов И первого элемента И-ИЛИ-НЕ и второму входу второй группы входов И третьего элемента И-ИЛИ-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов И первого элемента И-ИЛИ-НЕ блока хранения введен второй вход, подключенный к входу установки единицы, а инверсный информационный выход блока хранения подключен к выходу второго элемента И-ИЛИ-НЕ.

8. Самосинхронный триггер с однофазным информационным входом по п.6, отличающийся тем, что в него введен вход установки единицы и во вторую группу входов И первого элемента И-ИЛИ-НЕ блока хранения введен второй вход, подключенный к входу установки единицы.

9. Самосинхронный триггер с однофазным информационным входом по п.5, отличающийся тем, что в схему введены вход установки нуля и инверсный информационный выход блока хранения, блок хранения содержит три элемента ИЛИ-И-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первым входам первых групп входов ИЛИ второго и третьего элементов ИЛИ-И-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первым входам первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ и второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ и третьими входами первой и второй групп входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ подключен к входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ, второму входу первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и информационному выходу блока хранения, выход второго элемента ИЛИ-И-НЕ подключен к входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и второму входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов ИЛИ первого элемента ИЛИ-И-НЕ блока хранения введен второй вход, подключенный к входу установки нуля, а инверсный информационный выход блока хранения подключен к выходу второго элемента ИЛИ-И-НЕ.

10. Самосинхронный триггер с однофазным информационным входом по п.5, отличающийся тем, что в схему введены вход установки единицы и инверсный информационный выход блока хранения, блок хранения содержит три элемента ИЛИ-И-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первым входам первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ и первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первым входам первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ и второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ и третьими входами первой и второй групп входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ подключен к входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ, второму входу первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и информационному выходу блока хранения, выход второго элемента ИЛИ-И-НЕ подключен к входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и второму входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов ИЛИ второго элемента ИЛИ-И-НЕ блока хранения введен второй вход, подключенный к входу установки единицы, а инверсный информационный выход блока хранения подключен к выходу второго элемента ИЛИ-И-НЕ.

11. Самосинхронный триггер с однофазным информационным входом по п.9, отличающийся тем, что в него введен вход установки единицы, и во вторую группу входов ИЛИ второго элемента ИЛИ-И-НЕ блока хранения введен второй вход, подключенный к входу установки единицы.

12. Самосинхронный триггер с однофазным информационным входом по п.4, отличающийся тем, что в него введены вход установки нуля и инверсный информационный выход блока хранения, блок хранения содержит три элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов И первого элемента И-ИЛИ-НЕ и второму входу третьей группы входов И третьего элемента И-ИЛИ-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов И второго элемента И-ИЛИ-НЕ и второму входу второй группы входов И третьего элемента И-ИЛИ-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов И первого и второго элементов И-ИЛИ-НЕ и первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ, с третьим входом второй группы входов И и первым входом третьей группы входов И третьего элемента И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен ко второму входу первой группы входов И и первому входу второй группы входов И третьего элемента И-ИЛИ-НЕ, входу второй группы входов И второго элемента И-ИЛИ-НЕ и первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ, выход которого соединен с входом второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ, первым входом первой группы входов И третьего элемента И-ИЛИ-НЕ и информационным выходом блока хранения, выход второго элемента И-ИЛИ-НЕ соединен с третьим входом третьей группы входов И и первым входом четвертой группы входов И третьего элемента И-ИЛИ-НЕ, входом второй группы входов И первого элемента И-ИЛИ-НЕ и первым входом первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ, выход которого соединен с входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и вторым входом четвертой группы входов И третьего элемента И-ИЛИ-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов И первого элемента И-ИЛИ-НЕ блока хранения введен второй вход, подключенный к входу установки нуля, а инверсный информационный выход блока хранения подключен к выходу второго элемента ИЛИ-И-НЕ.

13. Самосинхронный триггер с однофазным информационным входом по п.4, отличающийся тем, что в него введены вход установки единицы и инверсный информационный выход блока хранения, блок хранения содержит три элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов И первого элемента И-ИЛИ-НЕ и второму входу третьей группы входов И третьего элемента И-ИЛИ-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов И второго элемента И-ИЛИ-НЕ и второму входу второй группы входов И третьего элемента И-ИЛИ-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов И первого и второго элементов И-ИЛИ-НЕ и первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ, с третьим входом второй группы входов И и первым входом третьей группы входов И третьего элемента И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен ко второму входу первой группы входов И и первому входу второй группы входов И третьего элемента И-ИЛИ-НЕ, входу второй группы входов И второго элемента И-ИЛИ-НЕ и первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ, выход которого соединен с входом второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ, первым входом первой группы входов И третьего элемента И-ИЛИ-НЕ и информационным выходом блока хранения, выход второго элемента И-ИЛИ-НЕ соединен с третьим входом третьей группы входов И и первым входом четвертой группы входов И третьего элемента И-ИЛИ-НЕ, входом второй группы входов И первого элемента И-ИЛИ-НЕ и первым входом первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ, выход которого соединен с входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и вторым входом четвертой группы входов И третьего элемента И-ИЛИ-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов И второго элемента И-ИЛИ-НЕ блока хранения введен второй вход, подключенный к входу установки единицы, а инверсный информационный выход блока хранения подключен к выходу второго элемента ИЛИ-И-НЕ.

14. Самосинхронный триггер с однофазным информационным входом по п.12, отличающийся тем, что в него введен вход установки единицы, и во вторую группу входов И второго элемента И-ИЛИ-НЕ блока хранения введен второй вход, подключенный к входу установки единицы.

15. Самосинхронный триггер с однофазным информационным входом по п.12, отличающийся тем, что в первую и четвертую группы входов И третьего элемента И-ИЛИ-НЕ блока хранения введены третьи входы, подключенные к входу установки нуля.

16. Самосинхронный триггер с однофазным информационным входом по п.13, отличающийся тем, что в первую и четвертую группы входов И третьего элемента И-ИЛИ-НЕ блока хранения введены третьи входы, подключенные к входу установки единицы.

17. Самосинхронный триггер с однофазным информационным входом по п.14, отличающийся тем, что в первую и четвертую группы входов И третьего элемента И-ИЛИ-НЕ блока хранения введены третьи и четвертые входы, подключенные к входам установки нуля и установки единицы соответственно.

18. Самосинхронный триггер с однофазным информационным входом по п.5, отличающийся тем, что в него введены вход установки нуля и инверсный информационный выход блока хранения, блок хранения содержит три элемента ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ и второму входу третьей группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ и второму входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ и первых групп входов И первого и второго элементов И-ИЛИ-НЕ, с третьим входом второй группы входов ИЛИ и первым входом третьей группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ подключен ко второму входу первой группы входов ИЛИ и первому входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ и первому входу первой группы входов И первого элемента И-ИЛИ-НЕ, выход которого соединен с входом второй группы входов И второго элемента И-ИЛИ-НЕ, первым входом первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и информационным выходом блока хранения, выход второго элемента ИЛИ-И-НЕ соединен с третьим входом третьей группы входов ИЛИ и первым входом четвертой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и первым входом первой группы входов И второго элемента И-ИЛИ-НЕ, выход которого соединен с входом второй группы входов И первого элемента И-ИЛИ-НЕ и вторым входом четвертой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов ИЛИ второго элемента ИЛИ-И-НЕ блока хранения введен второй вход, подключенный к входу установки нуля, а инверсный информационный выход блока хранения подключен к выходу второго элемента И-ИЛИ-НЕ.

19. Самосинхронный триггер с однофазным информационным входом по п.5, отличающийся тем, что в него введены вход установки единицы и инверсный информационный выход блока хранения, блок хранения содержит три элемента ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, прямая составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ и второму входу третьей группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, инверсная составляющая парафазного информационного входа блока хранения подключена к первому входу первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ и второму входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, вход управления блока хранения соединен со вторыми входами первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ и первых групп входов И первого и второго элементов И-ИЛИ-НЕ, с третьим входом второй группы входов ИЛИ и первым входом третьей группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ подключен ко второму входу первой группы входов ИЛИ и первому входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ и первому входу первой группы входов И первого элемента И-ИЛИ-НЕ, выход которого соединен с входом второй группы входов И второго элемента И-ИЛИ-НЕ, первым входом первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и информационным выходом блока хранения, выход второго элемента ИЛИ-И-НЕ соединен с третьим входом третьей группы входов ИЛИ и первым входом четвертой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ и первым входом первой группы входов И второго элемента И-ИЛИ-НЕ, выход которого соединен с входом второй группы входов И первого элемента И-ИЛИ-НЕ и вторым входом четвертой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход которого подключен к индикаторному выходу блока хранения, во вторую группу входов ИЛИ первого элемента ИЛИ-И-НЕ блока хранения введен второй вход, подключенный к входу установки единицы, а инверсный информационный выход блока хранения подключен к выходу второго элемента И-ИЛИ-НЕ.

20. Самосинхронный триггер с однофазным информационным входом по п.18, отличающийся тем, что в него введен вход установки единицы и во вторую группу входов ИЛИ первого элемента ИЛИ-И-НЕ блока хранения введен второй вход, подключенный к входу установки единицы.

21. Самосинхронный триггер с однофазным информационным входом по п.18, отличающийся тем, что в первую и четвертую группы входов ИЛИ третьего элемента ИЛИ-И-НЕ блока хранения введены третьи входы, подключенные к входу установки нуля.

22. Самосинхронный триггер с однофазным информационным входом по п.19, отличающийся тем, что в первую и четвертую группы входов ИЛИ третьего элемента ИЛИ-И-НЕ блока хранения введены третьи входы, подключенные к входу установки единицы.

23. Самосинхронный триггер с однофазным информационным входом по п.20, отличающийся тем, что в первую и четвертую группы входов ИЛИ третьего элемента ИЛИ-И-НЕ блока хранения введены третьи и четвертые входы, подключенные к входам установки нуля и установки единицы соответственно.

24. Самосинхронный триггер с однофазным информационным входом по п.6 или 15, отличающийся тем, что в него введены второй индикаторный выход и элемент ИЛИ-НЕ, причем первый и второй входы элемента ИЛИ-НЕ подключены к информационному выходу блока хранения и к входу установки нуля соответственно, а его выход соединен со вторым индикаторным выходом.

25. Самосинхронный триггер с однофазным информационным входом по п.7 или 16, отличающийся тем, что в него введены второй индикаторный выход и элемент ИЛИ-НЕ, причем первый и второй входы элемента ИЛИ-НЕ подключены к инверсному информационному выходу блока хранения и к входу установки единицы соответственно, а его выход соединен со вторым индикаторным выходом.

26. Самосинхронный триггер с однофазным информационным входом по п.8 или 17, отличающийся тем, что в него введены второй и третий индикаторные выходы и два элемента ИЛИ-НЕ, причем первый и второй входы первого элемента ИЛИ-НЕ подключены к информационному выходу блока хранения и к входу установки нуля соответственно, а его выход соединен со вторым индикаторным выходом, первый и второй входы второго элемента ИЛИ-НЕ подключены к инверсному информационному выходу блока хранения и к входу установки единицы соответственно, а его выход соединен с третьим индикаторным выходом.

27. Самосинхронный триггер с однофазным информационным входом по п.9 или 21, отличающийся тем, что в него введены второй индикаторный выход и элемент И-НЕ, причем первый и второй входы элемента И-НЕ подключены к инверсному информационному выходу блока хранения и к входу установки нуля соответственно, а его выход соединен со вторым индикаторным выходом.

28. Самосинхронный триггер с однофазным информационным входом по п.10 или 22, отличающийся тем, что в него введены второй индикаторный выход и элемент И-НЕ, причем первый и второй входы элемента И-НЕ подключены к информационному выходу блока хранения и к входу установки единицы соответственно, а его выход соединен со вторым индикаторным выходом.

29. Самосинхронный триггер с однофазным информационным входом по п.11 или 23, отличающийся тем, что в него введены второй и третий индикаторные выходы и два элемента И-НЕ, причем первый и второй входы первого элемента И-НЕ подключены к инверсному информационному выходу блока хранения и к входу установки нуля соответственно, а его выход соединен со вторым индикаторным выходом, первый и второй входы второго элемента И-НЕ подключены к информационному выходу блока хранения и к входу установки единицы соответственно, а его выход соединен с третьим индикаторным выходом,

| РАЗРЯД САМОСИНХРОННОГО РЕГИСТРА СДВИГА | 2006 |

|

RU2319232C1 |

| JP 11163686 A, 18.06.1999 | |||

| EP 1865601 A1, 12.12.2007 | |||

| Резервированный RS-триггер | 1989 |

|

SU1629962A1 |

Авторы

Даты

2010-11-27—Публикация

2008-04-15—Подача