Настоящая заявка на патент притязает на приоритет предварительной заявки № 60/681199, озаглавленной "Усовершенствованный перемежитель канала для широковещания по технологии Platinum Broadcast" и поданной 13 мая 2005, и предварительной заявки № 60/680855, озаглавленной "Усовершенствованный перемежитель канала для широковещания по технологии Platinum Broadcast" и поданной 12 мая 2005, которые включены в данный документ посредством ссылки.

Область техники, к которой относится изобретение

Настоящее изобретение относится к беспроводной связи и, в частности, к перемежению канала для систем связи, предоставляющих службы широковещания/многоадресной рассылки.

Уровень техники

В области беспроводной связи существует множество приложений, включающих в себя, например, беспроводные телефоны, пейджинговую связь, беспроводные абонентские линии, персональные цифровые секретари (PDA), интернет-телефонию и системы спутниковой связи. Особо важным приложением являются системы сотовой связи для мобильных абонентов. В данном документе термин "сотовая" система охватывает как частоты сотовой службы, так и частоты персональной службы связи (Personal Communications Service, PCS). Для подобных сотовых телефонных систем были разработаны различные эфирные интерфейсы, включающие в себя, например, Множественный Доступ с Частотным Разделением (Frequency Division Multiple Access, FDMA), Мультиплексирование с Ортогональным Разделением Частоты (Orthogonal Frequency Division Multiplexing, OFDM), Множественный Доступ с Временным Разделением (Time Division Multiple Access, TDMA) и Множественный Доступ с Кодовым Разделением (Code Division Multiple Access, CDMA). В связи с ними было основано множество различных внутригосударственных и международных стандартов, включая, например, Advanced Mobile Phone Service (AMPS), Global System for Mobile (GSM) и Interim Standard 95 (IS-95). В частности, стандарт IS-95 и его производные - IS-95A, IS-95W, ANSI J-STD-008 (на которые в собирательном смысле в данном документе часто ссылаются как на IS-95) и предлагаемые системы с высокой скоростью передачи данных и т.п. публикуются Ассоциацией Индустрии Связи (Telecommunication Industry Association, TIA), Международным Союзом Электросвязи (International Telecommunications Union (ITU)) и другими известными органами стандартизации.

В сотовых телефонных системах, сконфигурированных в соответствии со стандартом IS-95, для предоставления высокоэффективной и устойчивой сотовой телефонной службы применяется способ CDMA обработки сигнала. Примеры сотовых телефонных систем, сконфигурированных, по существу, в соответствии со стандартом IS-95, описаны в патентах США №№ 5103459 и 4901307. Примером системы, в которой используется метод CDMA, является cdma2000. Стандарт для cdma2000 определен в Стандарте IS-2000, который во многом совместим с системами IS-95. Еще одним стандартом CDMA является стандарт WCDMA согласно следующим документа Проекта Партнерства 3-го Поколения (3rd Generation Partnership Project, 3GPP): 3G TS 25.211, 3G TS 25.212, 3G TS 25.213 и 3G TS 25.214. Еще одним стандартом CDMA является Стандарт IS-856, на который обычно ссылаются как на систему с Высокой Скоростью Передачи Данных (High Data Rate, HDR).

Передача цифровых данных по своей природе подвержена помехам, которые могут вводить ошибки в передаваемые данные. Для улучшения характеристики канала передачи некоторые схемы кодирования включают в себя перемежители, которые смешивают порядок битов в пакете во время кодирования. Таким образом, когда во время передачи помехи разрушают несколько смежных битов, эффект помех распределяется на весь исходный пакет, и этот эффект можно более легко преодолеть путем процесса декодирования. В последнее время были предложены службы широковещания/многоадресной рассылки для эффективной передачи больших объемов данных от одного источника группе пользователей в системах беспроводной связи. Содержимое, подходящее для таких служб типа точка-многоточка, включает в себя новости, биржевые сводки, спортивные события, фильмы, аудио- и видеоклипы и другие мультимедиа данные. Ввиду того, что потребность в передаче мультимедиа данных растет, существует задача в усовершенствовании таких служб, а также необходимость в усовершенствованном перемежении канала, которое поддерживает службы широковещания/многоадресной рассылки.

Сущность изобретения

В настоящем документе представлены новые и усовершенствованные способы и устройства для перемежения совокупности систематических битов и совокупности битов четности, чтобы генерировать выходную последовательность, которая может быть передана в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи.

В одном аспекте устройство содержит средство для демультиплексирования совокупности систематических битов и битов четности в совокупность последовательностей, причем совокупность систематических битов и битов четности последовательно распределяется среди последовательностей;

средство для переупорядочивания последовательностей на основании индексного множества;

средство для группирования последовательностей в совокупность сегментов и для перемежения каждого из этих сегментов, формируя совокупность матриц, содержащих совокупность элементов;

средство для модуляции элементов матрицы; и

средство для отбрасывания модулированных элементов каждой матрицы, причем выходная последовательность содержит отброшенные модулированные элементы из каждой матрицы, входящей в совокупность матриц. В этом аспекте демультиплексирование происходит путем сохранения систематических битов и битов четности в совокупность прямоугольных массивов из R строк и C столбцов, формируя первый входной блок U, второй входной блок W0 и третий входной блок W1, причем первый входной блок U содержит систематические биты, второй входной блок W0 формируется путем сочленения первого множества битов четности, и третий входной блок W1 формируется путем сочленения второго множества битов четности. Систематические биты и биты четности записываются в массивы входных блоков

U, W0 и W1 по строкам, и биты размещаются, начиная с верхней строки, слева направо. В этом аспекте индексное множество может быть отсортировано в возрастающем порядке. Переупорядочивание может быть выполнено путем определения индексного множества как содержащего совокупность множеств; сортировки совокупности элементов каждого из множеств; и переупорядочивания совокупности последовательностей в соответствии с группами скоростей. Перемежение может быть выполнено путем группирования переупорядоченных последовательностей в сегменты, и выполнения перемежения матрицы на каждом из этих сегментов. Схемой модуляции для средства модуляции может быть 16-QAM (16-позиционная квадратурная амплитудная модуляция). Средство отбрасывания может, сверх того, содержать средство для повторения модулированных элементов. В еще одном аспекте параметры для индексного множества могут храниться в справочной таблице.

В еще одном аспекте раскрыт способ для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может быть передана в многослотовых пакетах из базовой станции и удаленную станцию в системе беспроводной связи. Способ содержит этапы, на которых демультиплексируют совокупность систематических битов и битов четности в совокупность последовательностей, причем совокупность систематических битов и битов четности последовательно распределяют среди последовательностей;

переупорядочивают последовательности на основании индексного множества;

группируют последовательности в совокупность сегментов и перемежают каждый из этих сегментов, формируя совокупность матриц, содержащих совокупность элементов;

модулируют элементы матриц; и

отбрасывают модулированные элементы каждой матрицы, причем выходная последовательность содержит отброшенные модулированные элементы из каждой матрицы, входящей в совокупность матриц. В этом аспекте отбрасывание может быть выполнено в соответствии с желаемой скоростью кодового символа. Очевидно, что очередность этапов модуляции и отбрасывания может быть обращена без какого-либо эффекта на выходную последовательность настоящего изобретения.

В еще одном другом аспекте представлено устройство для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может быть передана в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи. Это устройство содержит средство для демультиплексирования совокупности систематических битов и битов четности в совокупность последовательностей, причем совокупность систематических битов и битов четности последовательно распределяется среди последовательностей;

средство для переупорядочивания последовательностей;

средство для формирования совокупности матриц из переупорядоченных последовательностей, причем это средство формирования основано на индексном множестве;

средство для перестановки матриц, формируя сочлененную матрицу, содержащую совокупность сегментов, совокупность столбцов и совокупность элементов;

средство для перемежения столбцов;

средство для модуляции элементов в сегментах; и

средство для отбрасывания модулированных элементов в сегментах сочлененной матрицы, причем выходная последовательность содержит отброшенные модулированные элементы из сегментов сочлененной матрицы.

С вышеизложенным аспектом демультиплексирование происходит путем сохранения систематических битов и битов четности в совокупность прямоугольных массивов из R строк и C столбцов, формируя первый входной блок U, второй входной блок W0 и третий входной блок W1, причем первый входной блок U содержит систематические биты, второй входной блок W0 формируется путем сочленения первого множества битов четности, и третий входной блок W1 формируется путем сочленения второго множества битов четности. Систематические биты и биты четности записываются в массивы входных блоков U, W0 и W1 по строкам, и биты размещаются начиная с верхней строки, слева направо. Индексное множество может быть отсортировано в возрастающем порядке. Переупорядочивание может происходить путем циклического сдвига вниз каждого элемента в каждом столбце каждого блока; изменения порядка столбцов внутри каждого блока. Более конкретно, внутри первого входного блока U символы в i-ом столбце могут циклически сдвигаться на величину (i mod R); и внутри входных блоков W0 и W1 символы в i-ом столбце могут циклически сдвигаться на величину (floor(i/D)mod R), где D представляет собой предопределенный параметр, основанный на группе скоростей, а R обозначает количество строк прямоугольных массивов, формирующих входные блоки. Формирование может происходить путем определения индексного множества как содержащего совокупность множеств, содержащих параметры, которые могут быть специфицированы в справочной таблице. Перестановка может происходить путем расстановки столбцов матриц предопределенным образом и разделения сочлененной матрицы на совокупность сегментов, содержащих предопределенное количество столбцов. Перемежение может происходить путем сдвига i-ого столбца на место π(i)-ого столбца в каждом k-ом сегменте, где π(i)=79imodL k, 0≤i<L k, и считывания символов в каждом из сегментов, причем сначала дается приращение индексу строки, а затем индексу столбца. Схемой модуляции для средства модуляции может быть 16-QAM (16-позиционная квадратурная амплитудная модуляция). В добавление, средство отбрасывания может, сверх того, содержать средство для повторения модулированных элементов. Кроме того, очевидно, что параметры для индексного множества могут храниться в справочной таблице.

Здесь также предложен еще один способ для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может передаваться в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи, причем способ содержит этапы, на которых

демультиплексируют совокупность систематических битов и битов четности в совокупность последовательностей, причем совокупность систематических битов и битов четности последовательно распределяют среди совокупности последовательностей;

переупорядочивают последовательности;

формируют совокупность матриц из переупорядоченных последовательностей, причем это формирование выполняют на основании индексного множества;

перестанавливают матрицы, формируя сочлененную матрицу, содержащую совокупность сегментов, совокупность столбцов и совокупность элементов;

перемежают столбцы;

модулируют элементы в совокупности сегментов; и

отбрасывают модулированные элементы в сегментах сочлененной матрицы, причем выходная последовательность содержит отброшенные модулированные элементы из сегментов сочлененной матрицы. В этом аспекте отбрасывание может быть выполнено в соответствии с желаемой скоростью кодового символа. Очевидно, что очередность этапов модуляции и отбрасывания может быть обращена без какого-либо эффекта на выходную последовательность настоящего изобретения.

Эти и другие отличительные признаки изобретения будут очевидны из описания различных вариантов осуществления со ссылкой на прилагаемые чертежи.

Краткое описание чертежей

Сопутствующие чертежи, которые включены в состав данного документа и которые представляют часть этой спецификации, иллюстрируют варианты осуществления настоящего изобретения и вместе с описанием служат для разъяснения отличительных признаков и принципов настоящего изобретения. На чертежах:

Фиг.1 - структурная схема примера системы передачи голоса и данных;

Фиг.2 - структурная схема турбо-кодера;

Фиг.3 - структурная схема устройства, которое использует турбо-кодер для генерации каналов прямого трафика;

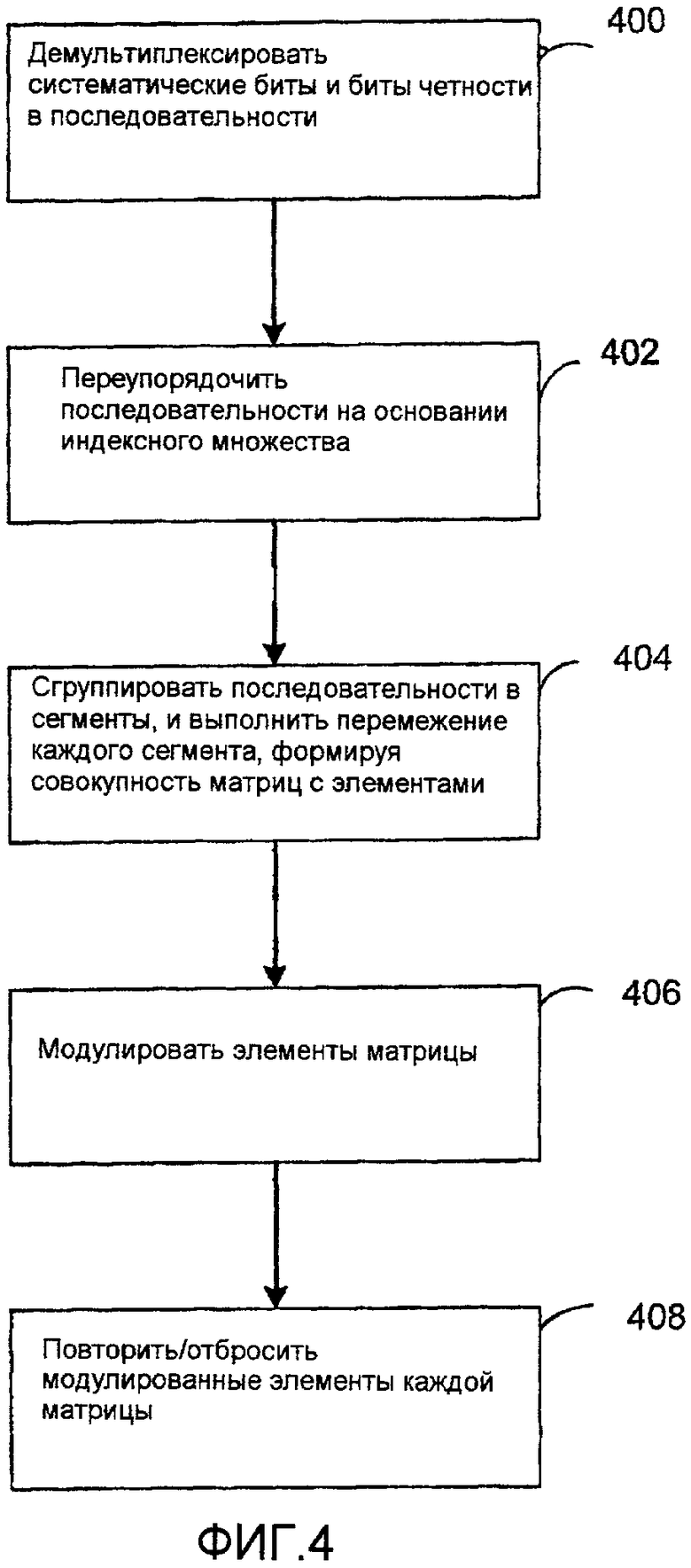

Фиг.4 - схема последовательности операций варианта осуществления, который переупорядочивает выход турбо-кодера;

Фиг.5 - схема последовательности операций еще одного варианта осуществления, который переупорядочивает выход турбо-кодера; и

Фиг.6 - схема созвездия сигналов для схемы модуляции 16-QAM.

Подробное описание

На Фиг.1 показана сеть 10 беспроводной связи, которая включает в себя множество мобильных станций (которые также называют абонентскими блоками или оборудованием пользователя) 12a-12d, множество базовых станций (которые также называют приемопередатчиками базовой станции (Base Station Transceiver, BTS) или Узлами В (Node B) 14a-14c, контроллер 16 базовой станции (Base Station Controller, BSC) (который также называют контроллером радиосети или функцией управления пакетной передачей), центр коммутации мобильной связи (Mobile Switching Center (MSC)) или переключатель 18, узел 20 службы пакетной передачи данных (Packet Data Serving Node, PDSN) (или функция межсетевого взаимодействия (Internetworking Function, IWF), телефонную коммутируемую сеть 22 общего пользования (Public Switched Telephone Network, PSTN) (как правило, телефонная компания) и IP (Internet Protocol) сеть 24 (как правило, Интернет). Для простоты показаны только четыре мобильные станции 12a-12d, три базовые станции 14a-14c, один BSC 16, один MSC 18 и одна PDSN 20. Специалистам в данной области техники будет очевидно, что может использоваться любое количество мобильных станций 12, базовых станций 14, BSC 16, MSC 18 и PDSN 20.

В одном аспекте сеть 10 беспроводной связи представляет собой сеть служб пакетной передачи данных. Мобильные станции 12a-12d могут быть любого типа из множества типов устройств беспроводной связи, таких как портативный телефон, сотовый телефон, который соединен с лэптопом, на котором выполняются приложения веб-браузера, основанные на IP, сотовый телефон со связанным набором Hands-Free для автомобилей, персональный цифровой ассистент (PDA), на котором выполняются приложения веб-браузера, основанные на IP, модуль беспроводной связи, входящий в состав портативного компьютера, или стационарный модуль связи, который можно встретить в беспроводных абонентских линиях или системе считывания показаний. В самом общем варианте осуществления мобильные станции могут быть любого типа блока связи.

Мобильные станции 12a-12d могут быть сконфигурированы, чтобы выполнять один или более протоколов беспроводной пакетной передачи данных, таких как, например, описанные в стандарте EIA/TIA/IS-707. В особом аспекте мобильные станции 12a-12d генерируют IP-пакеты, предназначенные для IP-сети 24, и инкапсулируют эти IP-пакеты в кадры, используя протокол точка-точка (Point-to-Point Protocol, PPP).

С вышеупомянутым аспектом IP-сеть 24 соединена с PDSN 20, PDSN 20 соединен с MSC 18, MSC 18 соединен с BSC 16 и PSTN 22, а BSC 16 соединен с базовыми станциями 14a-14c через проводные линии, сконфигурированные для передачи голоса и/или пакетов данных согласно какому-либо из нескольких протоколов, которые включают в себя, но не ограничиваются перечисленным, протоколы E1, T1, ATM, IP, Frame Relay, HDSL, ADSL или xDSL, например. В альтернативном аспекте BSC 16 напрямую соединен с PDSN 20, и MSC 18 не соединен с PDSN 20. В еще одном аспекте мобильные станции 12a-12d осуществляют связь с базовыми станциями 14a-14c через радиочастотный интерфейс, как определено в документе Проекта 2 Партнерства Третьего Поколения (3rd Generation Partnership Project 2 "3GPP2") "Стандарт физического уровня для систем cdma2000 с расширенным спектром" No. C.S0002-A, TIA PN-4694, опубликованном как TIA/EIA/IS-2000-2-A.

Во время типичной работы сети 10 беспроводной связи базовые станции 14a-14c принимают и демодулируют множество сигналов обратной линии связи от различных мобильных станций 12a-12d, участвующих в телефонных вызовах, просмотре веб-страниц или в иной передаче данных. Каждый сигнал обратной линии связи, принятый заданной базовой станцией 14a-14c, обрабатывается в этой базовой станции 14а-14с. Каждая базовая станция 14a-14c может осуществлять связь со множеством мобильных станций 12a-12d путем модуляции и передачи множества сигналов прямой линии связи в мобильные терминалы 12a-12d. Например, как показано на Фиг.1, базовая станция 14a одновременно осуществляет связь с первой и второй мобильными станциями 12a, 12b, а базовая станция 14c одновременно осуществляет связь с третьей и четвертой мобильными станциями 12c, 12d. Получающиеся в результате пакеты перенаправляются в BSC 16, который предоставляет распределение ресурсов вызова и функциональные возможности управления мобильностью, включающие в себя оркестровку плавных эстафетных переключений вызова конкретной мобильной станции 12a-12d с одной базовой станции 14a-14c на другую базовую станцию 14a-14c. Например, мобильная станция 12c осуществляет связь одновременно с двумя базовыми станциями 14b, 14c. В конечном счете, когда мобильная станция 12c переместится достаточно далеко от одной из базовых станций 14c, вызов по эстафете будет переключен на другую базовую станцию 14b.

Если передача представляет собой обычный телефонный вызов, то BSC 16 будет переводить полученные данные по маршруту в MSC 18, который предоставляет дополнительные службы маршрутизации для интерфейса с PSTN 22. Если передача представляет собой пакетную передачу данных, такую как сеанс передачи данных, предназначенных для IP-сети 24, то MSC 18 передает пакеты данных по маршруту в PDSN 20, который передаст пакеты в IP-сеть 24. Альтернативно, BSC 16 будет направлять пакеты по маршруту напрямую в PDSN 20, который передает пакеты в IP-сеть 24.

В некоторых примерах систем CDMA пакеты, несущие трафик данных, разделяются на субпакеты, которые занимают "слоты" канала передачи. Исключительно в целях облегчения иллюстрации в данном документе использован ряд систем с Высокой Скоростью Передачи Данных (High Data Rate, HDR), и, более конкретно, HDR-система, предоставляющая службы широковещания/многоадресной рассылки. Тем не менее, следует понимать, что реализация настоящего изобретения не ограничена HDR-системами. То есть варианты осуществления настоящего изобретения могут быть реализованы в других системах CDMA, таких как, например, cdma2000, без какого-либо эффекта на объем описанных здесь вариантов осуществления.

В HDR-системе размеры слота установлены равными 1,66 мс, однако следует понимать, что размеры слотов могут варьировать в описанных здесь вариантах осуществления, без эффекта на их объем. Например, длительность слота в системах cdma2000 составляет 1,25 мс. В добавление, трафик данных может передаваться в кадрах сообщения, которые в системе IS-95 могут иметь длительность 5 мс, 10 мс, 20 мс, 40 мс или 80 мс. Термины "слоты" и "кадры" представляют собой термины, используемые относительно различных каналов передачи данных в одной системе CDMA или между различными системами CDMA. Система CDMA содержит множество каналов в прямой линии связи и обратной линии связи, причем некоторые каналы по структуре отличаются от других. Следовательно, терминология для описания некоторых каналов будет отличаться в соответствии со структурой. Исключительно для целей иллюстрации термин "слоты" используется здесь для описания уплотнения сигналов, распространяющихся по воздуху.

Избыточные представления полезной нагрузки данных упаковываются в кадры, или субпакеты, которые далее можно программно комбинировать в приемнике. Избыточность относится к, по существу, схожей информации, несомой каждым субпакетом. Избыточные представления могут генерироваться либо путем повторения, либо путем дополнительного кодирования. Процесс программного комбинирования предоставляет возможность восстановления искаженных битов. Посредством программного комбинирования, где один искаженный субпакет комбинируется с другим искаженным субпакетом, передача повторных и избыточных субпакетов может предоставить возможность системе передавать данные на минимальной скорости передачи. Передача повторных и избыточных субпакетов в особенности желательна при наличии замирания. Релеевское замирание, которое представляет собой форму многоканальных помех, происходит, когда множество копий одного и того же сигнала достигают приемника с различными фазами, что потенциально вызывает деструктивные помехи. Значительные многоканальные помехи с очень малым распределением задержки могут привести к возникновению равномерного замирания по всей полосе пропускания сигнала. Если удаленная станция перемещается в быстро изменяющемся окружении, то пиковые замирания могут возникнуть в моменты, когда планируется повторная передача субпакетов. Когда возникает подобное обстоятельство, базовой станции требуется дополнительная мощность передачи, чтобы передать субпакет.

Например, если блок планировщика в базовой станции принял пакет данных для передачи в удаленную станцию, то полезная нагрузка данных избыточным образом упаковывается во множество субпакетов, которые последовательно передаются в удаленную станцию. При передаче субпакетов блок планировщика может принять решение передавать субпакеты либо периодически, либо способом, зависящим от канала.

Прямая линия связи от базовой станции до удаленной станции, работающей в зоне базовой станции, может содержать множество каналов. Некоторые из каналов прямой линии связи могут включать в себя, но не ограничиваются перечисленным, пилот-канал, канал синхронизации, канал пейджинга, канал быстрого пейджинга, канал широковещания, канал управления мощностью, канал назначения, канал управления, выделенный канал управления, канал управления доступом к среде передачи (канал MAC), основной канал, дополнительный канал, дополнительный кодовый канал и канал передачи пакетных данных. Обратная линия связи от удаленной станции до базовой станции также содержит множество каналов. Каждый канал несет в точку назначения различные типы информации. Как правило, голосовой трафик передается по основным каналам, а трафик данных передается по дополнительным каналам или по каналам передачи пакетных данных. Дополнительные каналы обычно представляют собой выделенные канала, тогда как каналы передачи пакетных данных обычно несут сигналы, которые предназначены для различных сторон, по способу временного мультиплексирования. Альтернативно, каналы передачи пакетных данных также описываются как разделенные дополнительные каналы. Для целей описания вариантов осуществления в данном документе на дополнительные каналы и на каналы передачи пакетных данных в целом ссылаются как на каналы трафика данных.

Дополнительные каналы и каналы передачи пакетных данных могут улучшить среднюю скорость передачи системы путем предоставления возможности передачи в целевую станцию неожиданных сообщений данных. Поскольку полезная нагрузка данных может быть избыточным образом упакована на этих каналах, многослотовая передача, запланированная на прямой линии связи, может быть завершена раньше, если удаленная станция сможет определить, что полезную нагрузку данных можно восстановить из субпакетов, которые уже были приняты. Как описано выше, полезная нагрузка данных, которая несется в каждом слоте, подвергается различным этапам кодирования, причем кодированные биты переупорядочиваются в приемлемом для канала формате. Следовательно, для того чтобы выполнить восстановление данных, декодер удаленной станции должен оперировать на всем содержимом каждого слота многослотовой передачи.

Описанные здесь варианты осуществления предоставляют возможность поддержания минимальной скорости передачи.

Определение скоростей передачи данных на прямой линии связи

В HDR-системе, предоставляющей службы широковещания/многоадресной рассылки, скорости, на которых супбпакеты должны передаваться из базовой станции в удаленную станцию, определяются посредством алгоритма управления скорости, выполняемого удаленной станцией, и алгоритма планирования, выполняемого в базовой станции. На этот способ для изменения скорости передачи данных ссылаются как на процедуру Автоматического Запроса на Повтор (Automatic Repeat Request, ARQ). Следует отметить, что пропускная способность системы определяется скоростью, на которой фактически принимается полезная нагрузка данных, и она отличается от битовой скорости передаваемых субпакетов.

Алгоритм управления скорости выполняется удаленной станцией, чтобы определить, какая базовая станция из активного набора может обеспечить наилучшую пропускную способность, и чтобы определить максимальную скорость передачи данных, на которой удаленная станция сможет принимать пакеты с достаточной степенью надежности. Активным набором является набор базовых станций, который в текущее время осуществляет связь с данной удаленной станцией. В типичной системе CDMA или системе, отличной от CDMA, базовая станция через точно определенные, периодические интервалы передает известный сигнал, на который обычно ссылаются как на "пилот-сигнал". Как правило, удаленная станция выполняет мониторинг пилот-сигнала каждой базовой станции из активного набора и определяет отношение Сигнала к Шуму и Помехам (Signal-to-Noise and Interference Ratio, SINR) каждого пилот-сигнала. На основании информации прошлого SINR удаленная станция прогнозирует будущее значение SINR для каждой базовой станции, причем будущее значение SINR будет связано с длительностью следующего пакета. Удаленная станция, тогда, выбирает ту базовую станцию, которая вероятно будет иметь наилучшее SINR в течение определенного периода в ближайшем будущем, и приблизительно вычисляет наилучшую скорость передачи данных, на которой удаленная станция сможет принять следующий пакет данных от этой базовой станции. Удаленная станция, тогда, передает сообщение Управления Скоростью Передачи Данных (Data Rate Control, DRC), которое несет в базовую станцию информацию об этой скорости передачи данных. Следует понимать, что информация о наилучшей скорости передачи данных, несомая сообщением DRC, является скоростью передачи данных, на которой должен передаваться следующий пакет данных согласно запросу удаленной станции. В HDR-системе сообщения DRC передаются по каналу MAC обратной линии связи.

Алгоритм планирования реализовывается в базовой станции, чтобы определить, какая удаленная станция будет получателем следующего пакета. Алгоритм планирования учитывает необходимость максимизировать пропускную способность базовой станции, необходимость удерживать равнодоступность всех удаленных станций, действующей в зоне базовой станции, и необходимость обеспечивать скорости передачи данных, запрашиваемые различными удаленными станциями. Как описано ниже, процедура быстрого ARQ определяет действительную скорость передачи данных, на которой принимается каждый пакет данных, в отличие от скорости передачи данных, изначально определенной алгоритмом управления скорости.

Блок планирования в базовой станции выполняет мониторинг поступления сообщений DRC от всех удаленных станций, которые действуют в ее зоне, и использует информацию DRC в алгоритме планирования, чтобы определить, какая удаленная станция будет получателем следующего пакета данных в соответствии с оптимальным уровнем пропускной способности прямой линии связи. Следует отметить, что оптимальная пропускная способность прямой линии связи также учитывает поддержание приемлемых характеристик линии связи для всех удаленных станций, работающих в зоне базовой станции. Блок планирования вновь собирает пакет данных в субпакеты с подходящей битовой скоростью и генерирует график передачи для субпакетов по назначенным слотам.

В HDR-системе, предоставляющей службы широковещания/многоадресной рассылки, скорости передачи данных прямой линии связи варьируют в пределах от 409,6 кбит/сек до 2,4 Мбит/сек. Длительность каждой передачи пакета в количестве слотов, а также другие параметры модуляции приведены в таблице 1.

Форматы OFDM и группы скоростей

Полезная нагрузка 3072

Полезная нагрузка 2048

Полезная нагрузка 5120

Полезная нагрузка 4096

Полезная нагрузка 3072

В HDR-системе кодовые символы, которые передаются в субпактах на меньших скоростях, являются расширениями или повторениями кодовых символов, которые передаются на определенных, более высоких скоростях. Во многих случаях кодовые символы, передаваемые в заданном субпакете, являются сдвинутыми повторениями кодовых символов, переданных в более ранних слотах пакета.

Более низкие скорости передачи данных требуют меньшего SINR для заданной низкой вероятности ошибки пакета. Следовательно, если удаленная станция определяет, что состояние канала неблагоприятно, то удаленная станция передает сообщение DRC с запросом пакета с низкой скоростью передачи данных, который содержит множество субпакетов. Тогда базовая станция передаст многослотовые пакеты в соответствии с параметрами, хранимыми в блоке планирования.

Когда субпакеты передаются, удаленная станция может определить, что пакет данных может быть декодирован только из части субпакетов, которые планируется передавать. Используя процедуру быстрого ARQ, удаленная станция подает команду базовой станции остановить передачу остающихся субпакетов, посредством чего увеличивается эффективная скорость передачи данных системы.

Следует отметить, что процедура ARQ потенциально может значительно увеличить пропускную способность прямой линии системы беспроводной связи. Как описано выше, когда удаленная станция передает сообщение DRC в базовую станцию, требуемая скорость передачи данных определяется, используя алгоритм управления скоростью, который использует прошлые величины SINR, чтобы прогнозировать величину SINR в ближайшем будущем. Однако вследствие условий замирания, которые возникают из-за факторов окружающей среды и мобильности удаленной станции, прогноз SINR для ближайшего будущего не будет достоверным. В добавление, SINR сигнала трафика прямой линии может сильно отличаться от SINR пилот-сигнала вследствие помех от соседних базовых станций. Возможно, некоторые из соседних базовых станций были в режиме простоя в течение периода пробирования для вычислений прогноза SINR. В результате удаленная станция не всегда может прогнозироваться SINR с высокой точностью. Следовательно, алгоритм управления скоростью предоставляет нижний предел оценки для действительного SINR в течение длительности следующего пакета с высокой вероятностью и определяет максимальную скорость передачи данных, которую можно будет поддерживать, если фактическое SINR будет равно этому нижнему пределу оценки. Иначе говоря, алгоритм управления скоростью предоставляет консервативную меру скорости передачи данных, на которой может быть передан следующий пакет. Процедура ARQ уточняет эту оценку на основании качества данных, принятых в течение первых этапов передачи пакета. Следовательно, для удаленной станции важно информировать базовую станцию сразу же после того, как удаленная станция получает достаточно информации для декодирования пакета данных, так чтобы могло возникнуть раннее завершение передачи, что улучшает скорость передачи пакета данных.

Передачи субпакетов в удаленную станцию, как правило, выполняются по чередующему образцу, так что между субпакетами возникают пробелы. В одном аспекте субпакеты периодически передаются на каждом 4-м слоте. Задержка между субпакетами предоставляет возможность целевой удаленной станции декодировать субпакет до приема следующего субпакета. Если удаленная станция будет в состоянии декодировать субпакет до поступления следующего субпакета и верифицировать биты Контроля с Циклической Избыточностью (Cyclic Redundancy Check, CRC) декодированного результата до поступления следующего субпакета, то удаленная станция может передать в базовую станцию сигнал подтверждения приема, на который ссылаются как на сигнал FAST_ACK. Если базовая станция сможет демодулировать и интерпретировать сигнал FAST_ACK с достаточным запасом по времени до следующей спланированной передачи субпакета, то базовой станции не потребуется выполнять остающиеся спланированные передачи субпакетов. Тогда базовая станция может передать новый пакет данных в ту же удаленную станцию или в другую удаленную станцию в течение периода слота, который был предназначен для отмененных субпакетов. Следует отметить, что описанный здесь сигнал FAST_ACK является отдельным и отличается от сообщений ACK, которыми обмениваются протоколы высших уровней, такие как Протокол Радио Линии (Radio Link Protocol, RLP) и Протокол Управления Передачей (Transmission Control Protocol, TCP).

Поскольку процедура ARQ позволяет выполнять быструю адаптацию скорости к состояниям канала, процедура ARQ предоставляет возможность осуществления системы, в которой начальная передача данных выполняется на высокой скорости передачи данных, и при необходимости эта скорость уменьшается. В противоположность, система без ARQ будет вынуждена работать на низкой скорости передачи данных, чтобы обеспечить достаточный запас потенциала линии связи для того, чтобы учесть вариации канала в течение передач пакетов.

Передача перемеженных символов, которые максимизируют производительность декодера

В одном аспекте, чтобы уменьшить операции декодера, субпакеты могут передаваться таким образом, чтобы декодер мог быстро определять полезную нагрузки частичных передач слотов, между тем все так же обеспечивая защиту от пакетных ошибок.

Перемежитель канала может быть сконфигурирован в соответствии с этим аспектом, чтобы переставлять биты кодированного символа и предоставлять нарастающую избыточность. В этом аспекте перестановка битов разработана так, что систематические биты передаются в течение частичной передачи многослотового пакета. Декодер, вероятно, сможет определить полезную нагрузку данных из поступления только части субпакетов. Если полезная нагрузка не может быть декодирована, то удаленная станция передает отрицательное подтверждение приема (Negative Acknowledgement, NAK) по каналу ARQ. Базовая станция принимает NAK и передает следующий субпакет, содержащий дополнительные биты четности. Если удаленная станция не может декодировать субпакеты с помощью уже принятых систематических битов и недавно принятых битов четности, то передается еще одно NAK. Базовая станция принимает второе NAK и передает еще один субпакет, который включает в себя дополнительные биты четности. По мере поступления дополнительных NAK в течение процедуры ARQ, последующие субпакеты, передаваемые базовой станцией, содержат больше битов четности.

Иначе говоря, перемежитель канала переставляет систематические биты и биты четности так, что систематические биты загружаются в переднюю часть пакета, а биты четности загружаются в заднюю часть пакет. Исходя из соображений передачи, пакет разделяется на части, и каждая часть передается последовательно согласно требованиям удаленной станции. Следовательно, если для декодирования полезной нагрузки данных необходима дополнительная информация, то вместо повторной передачи полного вывода кодера передаются только дополнительные биты четности.

Может показаться, что этот процесс загрузки систематических битов в начало спланированной передачи пакета противоречит цели перемежения канала, однако описанные здесь варианты осуществления могут быть реализованы, чтобы обеспечивать устойчивость к пакетным ошибкам, между тем предоставляя возможность декодеру оперировать только на частичной передаче пакета. Во многих реализациях энергоэффективных систем беспроводной связи с использованием турбо-кодов выход турбо-кодера скремблируется либо до, либо после перемежения канала, так что данные рандомизируются до выполнения модуляции. Случайное скремблирование выхода турбо-кодера ограничивает отношение пикового значения к среднему значению огибающей модулированной волны.

На Фиг.2 показана структурная схема турбо-кодера, который сконфигурирован, чтобы работать с описанными здесь перемежителями канала согласно настоящему изобретению. Турбо-кодер 200 содержит первый составной кодер 210, турбо-перемежитель 220, второй составной кодер 230 и элемент 240 генерации символов. Первый составной кодер 210 и второй составной кодер 230 соединены в параллель с турбо-перемежителем 220, который расположен перед вторым составным кодером 230. Выход первого составного кодера 210 и выход второго составного кодера 230 вводятся в элемент 240 генерации символов, в котором эти выходы прореживаются и повторяются, чтобы сформировать желаемое количество выходных символов турбо-кодера.

В одном варианте осуществления первый и второй составные кодеры 210, 230 представляют собой рекурсивные, сверточные кодеры, каждый из которых сконфигурирован в соответствии со следующей передаточной функцией:

G(D)=[1, n0(D)/d(D), n1(D)/d(D)],

где d(D)=1+D2+D3, n0(D)=1+D+D3 и n1(D)=1+D+D2+D3. Используя первый и второй составные кодеры 210, 230, турбо-кодер 200 генерирует множество выходных символов кодированных данных и множество выходных символов кодированного хвоста, причем множество выходных символов кодированных данных впоследствии прореживаются посредством элемента 240 генерации символов, и множество выходных символов кодированного хвоста впоследствии прореживаются и повторяются посредством элемента 240 генерации символов, как описано в патентной заявке США № 09/863196, озаглавленной "Усовершенствованное перемежение канала для оптимальной пропускной способности", права на которую переданы настоящему заявителю.

Фиг.3 представляет собой структурную схему устройства, которое использует турбо-кодер для генерации каналов прямого трафика. Пакеты данных вводятся в турбо-кодер 300. Турбо-кодер 300 может быть сконфигурирован таким же образом, как описано для Фиг.2, но в рамках объема вариантов осуществления могут быть реализованы альтернативные конфигурации. В одном варианте осуществления скремблер 310 используется, чтобы рандомизировать выход турбо-кодера 300. Скремблер 310 может быть реализован посредством Сдвигового Регистра с Линейной Обратной Связью (Linear Feedback Shift Register, LFSR), который сконфигурирован в соответствии со следующей последовательностью генератора: h(D)=D17+D14+1. По каждому выходному кодовому символу турбо-кодера 300 и выходному биту скремблера 310 выполняется логическая операция XOR. Скремблер 310 может быть инициализирован посредством такой информации, как индексная величина MAC и/или скорость передачи данных, и он синхронизируется по каждому выходному символу кодера. Выход скремблера 310 перемежается посредством перемежителя 320 канала. Перемежение выполняется в соответствии с вариантами осуществления настоящего изобретения, как описано ниже.

Для реализации описанных ниже вариантов осуществления могут быть использованы различные осуществления перемежителя 320 канала. Например, элемент перемежения канала может быть произведен с использованием, по меньшей мере, одного элемента памяти и процессора. Альтернативно, может использоваться справочная таблица адресов ЧТЕНИЯ или адресов ЗАПИСИ, чтобы переставлять элементы массива входных символов, чтобы сгенерировать массив перемеженных символов. В еще одном альтернативном варианте может использоваться конечный автомат, чтобы генерировать последовательность адресов, определяющих перестановку входных символов. Специалистам в данной области техники известны также другие реализации, которые здесь не описаны. Выбор той или иной реализации не влияет на объем приведенных ниже вариантов осуществления.

Естественно, перемежитель 320 канала настоящего изобретения способен работать в HDR-системах, предоставляющих широковещание по технологии Platinum Broadcast согласно спецификации 1xEV-DO. В случае Platinum Broadcast, перемежитель канала должен удовлетворять следующим требованиям:

1. почти равномерное прореживание битов четности (используемое, чтобы поддерживать скорости кода, отличные от 1/3 и 1/5);

2. равномерное распределение систематических битов по всем символам модуляции OFDM в течение первого слота передачи;

3. совместимость скоростей передачи данных в одной группе скоростей. Иначе говоря, передачи на высокой скорости представляют собой усеченные версии передач на низкой скорости из той же группы скоростей. Это является требованием для любой системы, основанной на Гибридном ARQ (H-ARQ). Даже несмотря на то, что в технологии Platinum Broadcast не применяется H-ARQ, это все равно является очень полезной функциональной особенностью для Platinum Broadcast, поскольку H-ARQ предоставляет возможность широковещательной передачи с переменной скоростью, а также упрощает реализацию модема; и

4. дружественное по отношению к модуляции повторение последовательности: Очередность этапов модуляции и повторения последовательности могут быть измены без воздействия на окончательную форму сигнала передачи. Это свойство упрощает процедуру демодуляции, когда вовлекается повторение последовательности.

Следует отметить, что существующие в настоящее время перемежители канала и способы перемежения удовлетворят только некоторым из вышеизложенных требований. Например, несмотря на то, что перемежитель канала с оптимизацией данных (Data Optimized, DO) спроектирован, чтобы удовлетворять вышеизложенному требованию (1) для скоростей кода по стандарту 1xEV-DO, он только частично удовлетворяет требованию (1) для скоростей кода по стандарту Platinum Broadcast. В еще одном примере, компания Nokia предложила модифицированный перемежитель канала для Platinum Broadcast, который удовлетворяет вышеупомянутым требованиям (1) и (2), но не удовлетворяет требованиям (3) и (4). См. "Конструкция усовершенствованного перемежителя канала для службы DO BCMCS", Жоу и другие, Nokia.

Для иллюстрации первого аспекта перемежения согласно настоящему изобретению выход турбо-кодера может быть скремблирован и демультиплексирован в пять последовательностей, обозначенных как S, P0, P0', P1 и P1'. В частности, последовательность S относится к систематическим битам турбо-кодера. Последовательности P0 и P0' относятся к первым последовательностям четности (скорость 1/3) из двух составных кодеров турбо-кодера, а последовательности P1 и P1' относятся ко вторым последовательностям четности (скорость 1/5) из двух составных кодеров турбо-кодера. Для групп 3 и 4 скоростей P1 и P1' обозначают пустые последовательности. В таблице 1 показаны группы 1-5 скоростей по стандарту Platinum Broadcast. Каждая из пяти последовательностей S, P0, P0', P1 и P1' имеет длину в N символов. Для групп 1 и 4 скоростей N=3072; для группы 2 скоростей N=2048; для группы 3 скоростей N=5120; и для группы 5 скоростей N=4096. Пусть M обозначает количество кодовых символов, которое может быть передано в одном слоте, например M=3840 для групп 1, 2 и 3 скоростей, а для групп 4 и 5 скоростей M=5120.

Реорганизация последовательности

С вышеизложенным аспектом блок или последовательность U устанавливается равной S, блок или последовательность W0 формируется путем сочленения P0 и P0', а блок или последовательность W1 формируется путем сочленения P1 и P1'. Для групп 3 и 5 скоростей P1 и P1' и, следовательно, блок W1 могут содержать пустые последовательности. Более конкретно, при работе турбо-кодера настоящего изобретения на скорости 1/3 демультиплексирование может быть завершено с использованием трех последовательностей, обозначенных как S, P0 и P0'. В этом случае переупорядочивание или реорганизация порядка P0 и P0', с точки зрения характеристики ошибок, имеет результатом эквивалентный перемежитель, поскольку требование о том, чтобы первая и последняя последовательности оставались в первой позиции и последней позиции, не было нарушено. Иначе говоря, перемежитель канала будет сконфигурирован, чтобы переставлять кодовые символы в трех отдельных блоках или последовательностях перемежителя, причем первый блок или последовательность U содержит последовательность из символов S, второй блок или последовательность W0 содержит последовательность из символов P0 и P0', и третий блок или последовательность W1 содержит последовательность из символов P1 и P1'. Как упомянуто выше, в варианте осуществления, где турбо-кодер работает на скорости 1/3, перемежитель канала будет сконфигурирован, чтобы переставлять кодовые символы в двух отдельных блоках или последовательностях, причем первый блок или последовательность U содержит последовательность из символов S, а второй блок или последовательность W0 содержит последовательность из символов P0 и P0'.

В варианте осуществления, где до выполнения перемежения канала на выходных символах турбо-кодера используется скремблирующий элемент, вышеупомянутый вариант осуществления все же может быть осуществлен на блоке или последовательности из скремблированных символов S, на блоке или последовательности из скремблированных символов P0 и P0', на блоке или последовательности из скремблированных символов P1 и P1'.

Переупорядочивание символов

Фиг.4 иллюстрирует схему последовательности операций для серии этапов перестановки в соответствии с вышеупомянутым аспектом настоящего изобретения. На этапе 400 последовательности S, P0, P0', P1 и P1' записываются в прямоугольные массивы из R строк и C столбцов, чтобы сформировать первый входной блок или последовательность U, второй блок или последовательность W0 формируется путем сочленения P0 и P0', а третий входной блок или последовательность W1 формируется путем сочленения P1 и P1'. Символы записываются в блоки или последовательности по строкам, причем символы размещаются начиная с верхней строки, слева направо. На этапе 402 последовательности кодовых символов переупорядочиваются следующим образом:

Во-первых, определяют

Как указано выше, M определяется как количество кодовых символов, которое может быть передано в одном слоте, а N определяется как длина каждой из пяти последовательностей S, P0, P0', P1 и P1'. Очевидно, что также могут использоваться другие реализации перемежителя, например может быть использована справочная таблица, основанная на эмпирических данных или иных данных, чтобы определять значения для M1, M2 и M3, чтобы генерировать индексные множества и последовательности кодовых символов. То есть M1, M2 и M3 могут быть произвольными значениями, определяемыми посредством справочной таблицы.

Следующее, индексные множества S1-S5 определяют следующим образом:

S 1={round(i*(2N/M 1)|0≤i<M 1},

S 2={round(i*(2N/M 2)|0≤i<M 1)-S 1,

S 3={i|0≤i<2N}-S 1-S 2,

S 4={round(i*(2N/M 3)|0≤i<M 3},

S 5={i|0≤i<2N)-S 4.

Элементы каждого из индексных множеств S 1-S 5, тогда, сортируются в возрастающем порядке.

Следующее, последовательности кодовых символов переупорядочиваются следующим образом.

Для групп 1, 2 и 4 скоростей последовательности кодовых символов переупорядочиваются как: U, W0(S1), W0(S2), W0(S3), W1(S4), W1(S5).

Для групп 3 и 5 скоростей последовательности кодовых символов переупорядочиваются как: U, W0(S1), W0(S2), W0(S3).

Перемежение матрицы

На этапе 404 переупорядоченные последовательности кодовых символов с этапа переупорядочивания символов группируются в несколько сегментов длиной M каждый, и тогда каждый сегмент подвергается перемежению матрицы в соответствии с нижеописанным способом.

Для групп 1 и 3 скоростей переупорядоченные последовательности кодовых символов с этапа переупорядочивания символов группируются в три сегмента длиной M каждый, и тогда сегмент подвергается перемежению матрицы с R=4 строками, C=64 столбцами и L=15 уровнями.

Для группы 2 скоростей переупорядоченные последовательности кодовых символов с этапа переупорядочивания символов группируются в два сегмента длиной M каждый, и далее следует третий сегмент длиной 5N-2M=2560. Каждый из первых двух сегментов подвергается перемежению матрицы с R=4 строками, C=64 столбцами и L=15 уровнями. Третий сегмент подвергается перемежению матрицы с R=4 строками, C=128 столбцами и L=5 уровнями. Для группы 2 скоростей выходной последовательностью перемежителя для турбо-кодера будут перемеженные символы U, за которыми следуют перемеженные символы W0(S1)/W0(S2)/W0(S3).

Для группы 4 скоростей переупорядоченные последовательности кодовых символов с этапа переупорядочивания символов группируются в три сегмента длиной M каждый, и тогда каждый сегмент подвергается перемежению матрицы с R=4 строками, C=256 столбцами и L=5 уровнями. Для группы 4 скоростей выходной последовательностью перемежителя для турбо-кодера будут перемеженные символы U, за которыми следуют перемеженные символы W0(S1)/W0(S2)/W0(S3) и далее перемеженные символы W1(S4)/W1(S5).

Для группы 5 скоростей переупорядоченные последовательности кодовых символов с этапа переупорядочивания символов группируются в два сегмента длиной M каждый, за которыми следует третий сегмент длиной 3N-2M=2048. Каждый из первых двух сегментов подвергается перемежению матрицы с R=4 строками, C=256 столбцами и L=5 уровнями. Третий сегмент подвергается перемежению матрицы с R=4 строками, C=512 столбцами и L=1 уровнем. Для группы 5 скоростей выходной последовательностью перемежителя для турбо-кодера будут перемеженные символы U, за которыми следуют перемеженные символы W0(S1)/W0(S2)/W0(S3) и далее перемеженные символы W1(S4)/W1(S5).

Модуляция

На этапе 406 используется 16-позиционная Квадратурная Амплитудная Модуляция (16-QAM), чтобы модулировать переупорядоченные и перемеженные символы с этапа перемежения матрицы. Фиг.6 иллюстрирует созвездие сигналов для схемы модуляции 16-QAM. Четыре последовательных выходных символа перемежителя канала: x(4i), x(4i+l), x(4i+2) и x(4i+3), i=0,..., M-1, сопоставляются точке (m I(i), m Q(i)) созвездия сигналов. В таблице 2 приведено соответствие перемеженных символов модулированным символам.

Модуляция 16-QAM, где А=1/√10

x(4k+3)

x(4k+2)

x(4k+1)

x(4k)

Повторение/отбрасывание последовательности

Возвращаясь к Фиг.4, на этапе 408, если количество требуемых модулированных символов больше количества, предоставленного в вышеупомянутых вариантах осуществления, то целая последовательность входных модулированных символов может быть повторена как можно больше раз по всей последовательности, после чего следует частичная передача последовательности. Если необходима частичная передача, то может быть использована первая часть последовательности входных модулированных символов. Аналогично, если количество необходимых модулированных символов меньше предоставленного количества, то используется только первая часть последовательности входных модулированных символов, а остальная часть отбрасывается.

В еще одном аспекте настоящего изобретения очередность этапа 406 модуляции и этапа 408 повторения/отбрасывания последовательности может быть обращена, без какого-либо эффекта на окончательный результат выхода перемежителя.

В еще одном аспекте настоящего изобретения выход турбо-кодера может быть скремблирован и демультиплексирован в пять субпоследовательностей, обозначенных как S, P0, P0', P1 и P1'. Аналогично первому аспекту последовательность S относится к систематическим битам турбо-кодера. Последовательности P0 и P0' относятся к первым последовательностям четности (скорость 1/3) из двух составных кодеров турбо-кодера, а последовательности P1 и P1' относятся ко вторым последовательностям четности (скорость 1/5) из двух составных кодеров турбо-кодера. Для групп 3 и 4 скоростей, P1 и P1' обозначают пустые последовательности. Каждая из пяти последовательностей S, P0, P0', P1 и P1' имеет длину в N символов. Для групп 1 и 4 скоростей N=3072; для группы 2 скоростей N=2048; для группы 3 скоростей N=5120; и для группы 5 скоростей N=4096. Пусть M обозначает количество кодовых символов, которое может быть передано в одном слоте, например M=3840 для групп 1, 2 и 3 скоростей, а для групп 4 и 5 скоростей M=5120.

Перемежение матрицы

Фиг.5 иллюстрирует схему последовательности операций для серии этапов перестановок в соответствии с этим аспектом настоящего изобретения. Последовательности S, P0, P0', P1 и P1' записываются в прямоугольные массивы из R строк и C столбцов, чтобы сформировать первый входной блок или матрицу U, второй входной блок или матрица W0 формируется путем сочленения P0 и P0', а третий входной блок или матрица W1 формируется путем сочленения P1 и P1'. Символы записываются в блоки или матрицы по строкам, причем символы размещаются начиная с верхней строки, слева направо.

Более конкретно, на этапе 500 последовательность S записывается по строкам в матрицу W с R=4 строками и C=N/R столбцами. Очевидно, что количество строк и столбцов в каждой матрице определяется схемой модуляции, используемой для данного типа пакета. Например, количество строк равно количеству кодовых символов на модулированный символ (4 для 16-QAM), а количество столбцов каждой матрицы определяется длиной последовательностей U, P0, P0' и т.д. Последовательность P0 сочленяется с последовательностью P0' и считывается в матрицу W0 с R=4 строками и 2C=2N/R столбцами. Если последовательности P1 и P1' являются непустыми, то последовательность P1 сочленяется с последовательностью P1' и считывается в матрицу W1 с R=4 строками и 2C=2N/R столбцами. Символы считываются в каждую матрицу, причем сначала дается приращение индексу столбца, а затем индексу строки. Далее, на этапе 502 символы в i-ом столбце матрицы W циклически сдвигаются на величину (i mod R). На этот процесс ссылаются как на операцию циклического сдвига. В матрицах W0 и W1 символы i-ого столбца циклически сдвигаются на величину (floor(i/D)mod R), где параметр D специфицирован в таблице 3. Очевидно, что величины, выбранные для вышеупомянутых параметров, приведены только для целей иллюстрации, и могут быть использованы другие величины.

Параметры перемежителя матрицы для каждой группы скоростей

Переупорядочивание столбцов

На этапе 504 столбцы матрицы W0 разбиваются на множества S 1, S 2 и S 3 следующим образом:

Индексные множества S 1, S 2 и S 3 определяются следующим образом:

S 1={floor(C/M 1)+round(i*(2C/M 1)|0≤i<M 1},

S 2={floor(C/M 2)+round(i*(2C/M 2)|0≤i<M 2}-S 1,

S 3={i|0≤i<2C}-S 1-S 2,

где C специфицировано в таблице 3, а M 1, M 2 и M 3 специфицированы в таблице 4.

Если матрица W1 является непустой, то столбцы матрицы W2 разбиваются на множества S4 и S5 следующим образом:

S 4={floor(C/M 3)+round(i*(2C/M 3)|0≤i<M 3},

S 5={i|0≤i<2C}-S 4.

Параметры разбивки столбцов

В каждом индексном множестве S 1, S 2,..., S 5, элементы сортируются в возрастающем порядке, чтобы составить переупорядоченную группу из элементов.

Сочленение и сегментация матрицы

На этапе 506 матрицы W, W0 и W1 сочленяются, при этом столбцы располагаются следующим образом:

W, W0(S1), W0(S2), W0(S3), W1(S4), W1(S5), W...

В некоторых случая матрица W1 является непустой. Если матрица W1 является непустой, то сочлененная матрица имеет R=4 строк, 4C или 6C столбцов и K уровней.

Далее, определяют

L 2=L 3=M/R

Тогда, сочлененная матрица сегментируется на четыре части на основании индексов L 1, L 2 и L 3 своих столбцов. В частности, первый, второй и третий сегменты содержат L 1, L 2 и L 3 столбцов соответственно, а четвертый сегмент содержит остающиеся столбцы сочлененной матрицы.

Перемежение столбцов

На этапе 508 столбцы первых трех сегментов с этапа сочленения и сегментации матрицы перемежаются следующим образом:

в k-ом сегменте (k=1, 2, 3,...) сочлененной матрицы i-ый столбец перемещают на место π(i)-ого столбца, где

π(i)=79imodL k, 0≤i<L k.

Тогда символы в каждом сегменте считываются, причем сначала задается приращение индексу столбца, а затем индексу строки.

Модуляция

После этапа перемежения столбцов, на этапе 510 используется модуляция 16-QAM, чтобы модулировать перемеженные символы. В частности, четыре последовательные строки символов (R=4) с этапа перемежения столбцов группируются, чтобы сформировать символ, модулированный согласно 16-QAM. Схема модуляции 16-QAM описана выше относительно других аспектов изобретения.

Повторение/отбрасывание последовательности

Аналогично другим аспектам настоящего изобретения, на этапе 512, если количество требуемых модулированных символов больше количества, предоставленного в вышеупомянутых вариантах осуществления, то целая последовательность входных модулированных символов может быть повторена как можно больше раз по всей последовательности, после чего следует частичная передача последовательности. Если необходима частичная передача, то может быть использована первая часть последовательности входных модулированных символов. Если количество необходимых модулированных символов меньше предоставленного количества, то используется только первая часть последовательности входных модулированных символов, а остальная часть отбрасывается.

В еще одном аспекте настоящего изобретения, очередность этапа 510 модуляции и этапа 512 повторения/отбрасывания последовательности может быть обращена, без какого-либо эффекта на окончательный результат выхода перемежителя.

С помощью перемежителя канала настоящего изобретения коды с высокими скоростями, такие как используемые для служб широковещания/многоадресной рассылки, могут генерироваться простым образом путем пренебрежения или отбрасывания последних нескольких выводов перемежителя. Эта процедура предоставляет результаты, которые почти равны оптимальным или близким к оптимальным турбо-кодам, работающим на таких скоростях как 4/5, 2/3, 1/2, 1/3, 1/4 и 1/5, с подходящими шаблонами прореживания, и на других скоростях, предусмотренных для работы в системах, предоставляющих широковещание по технологии Platinum Broadcast согласно спецификации 1xEV-DO.

Специалистам в данной области техники будет понятно, что информация и сигналы могут быть представлены посредством любой технологии и способа из широкого спектра. Например, данные, инструкции, команды, информация, сигналы, биты, символы и элементарные сигналы, которые возможно упоминались в вышеизложенном описании, могут быть представлены посредством напряжений, токов, электромагнитных волн, магнитных полей или частиц, оптических полей или частиц, или их любой комбинации.

Специалистам в данной области техники также будет понятно, что различные иллюстративные логические блоки, модули, схемы и этапы алгоритмов, описанные в привязке к раскрытым здесь вариантам осуществления, могут быть реализованы как электронное аппаратное обеспечение, компьютерное программное обеспечение или их комбинации. Для ясной иллюстрации этой взаимозаменяемости аппаратного обеспечения и программного обеспечения различные иллюстративные компоненты, блоки, модули, схемы и этапы выше были описаны в терминах их функциональности. То, как реализована такая функция - как аппаратное обеспечение или программное обеспечение - зависит от конкретного приложения и конструктивных ограничений, налагаемых на систему в целом. Специалисты могут реализовать описанные функции различными способами для каждого конкретного применения, но подобные решения реализации не должны быть интерпретированы как выходящие за рамки объема настоящего изобретения.

Различные иллюстративные логические блоки, модули и схемы, описанные в привязке к раскрытым здесь вариантам осуществления, могут быть реализованы или выполнены посредством процессора общего назначения, цифрового процессора сигналов, специализированной микросхемы, программируемой вентильной матрицы или другого программируемого логического устройства, дискретного вентиля или транзисторной логической схемы, дискретных аппаратных компонентов или их любой комбинации, сконструированной для выполнения описанных здесь функций. Процессор общего назначения может быть микропроцессором, но альтернативно процессор может быть любым обычным процессором, котроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован как комбинация вычислительных устройств, например комбинация цифрового процессора сигналов и микропроцессора, множество микропроцессоров, один или более микропроцессоров в сочетании с цифровым процессором сигналов в качестве ядра, или любая другая такая конфигурация.

Этапы способа или алгоритма, описанного в привязке к раскрытым здесь вариантам осуществления, могут быть осуществлены непосредственно аппаратно, посредством программного модуля, исполняемого процессором, или посредством комбинации этих двух вариантов. Программный модуль может храниться в памяти ОЗУ, флэш-памяти, памяти ПЗУ, памяти СППЗУ, памяти ЭСППЗУ, регистрах, жестких дисках, съемных дисках, дисках CD-ROM, или любой другой известной форме носителей данных. Пример носителя данных соединен с процессором так, чтобы процессор мог считывать информацию с носителя данных и записывать информацию на него. Альтернативно, носитель данных может быть интегрирован с процессором. Процессор и носитель данных могут быть в специализированной микросхеме. Специализированная микросхема может быть в терминале пользователя. Альтернативно, процессор и носитель данных могут быть расположены в терминале пользователя как раздельные компоненты.

Предшествующее описание раскрытых вариантов осуществления предоставлено, чтобы предоставить возможность специалистам в данной области техники реализовать или использовать настоящее изобретение. Специалистам в данной области техники совершенно очевидны различные модификации к этим вариантам осуществления, и описанные здесь ключевые принципы могут применяться к другим вариантам осуществления в рамках сущности или объема настоящего изобретения. Следовательно, настоящее изобретение не ограничивается показанными здесь вариантами осуществления, а ему следует сопоставить самый широкий объем в соответствии с описанными здесь принципами и новыми отличительными признаками.

Изобретение относится к беспроводной связи и, в частности, к перемежению канала для систем связи, представляющих службы широковещания/многоадресной рассылки. Заявлены устройство и способ для перемежения систематических битов и битов четности для генерации выходной последовательности, которую передают в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи. Устройство содержит элемент памяти и элемент управления, соединенный с элементом памяти, причем элемент управления сконфигурирован, чтобы демультиплексировать систематические биты и биты четности в последовательности, при этом систематические биты и биты четности последовательно распределяются среди последовательностей. Элемент управления также сконфигурирован, чтобы переупорядочивать последовательности на основании индексного множества, чтобы группировать последовательности в сегменты и чтобы перемежать каждый из сегментов, формируя матрицы с элементами. Элемент управления также сконфигурирован, чтобы модулировать элементы матриц и чтобы отбрасывать модулированные элементы каждой матрицы, так чтобы производить выходную последовательность, которая содержит отброшенные модулированные элементы из каждой матрицы. Технический результат - обеспечение эффективной передачи больших объемов данных от одного источника группе пользователей в системах беспроводной связи. 5 н. и 50 з.п. ф-лы, 4 табл., 6 ил.

1. Устройство для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может быть передана в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи, содержащее:

средство для демультиплексирования совокупности систематических битов и совокупности битов четности в совокупность последовательностей, причем совокупность систематических битов и совокупность битов четности последовательно распределяются среди совокупности последовательностей;

средство для переупорядочивания совокупности последовательностей на основании индексного множества;

средство для группирования совокупности последовательностей в совокупность сегментов и для перемежения каждого из этих сегментов, формируя совокупность матриц, содержащих совокупность элементов;

средство для модуляции совокупности элементов, входящих в совокупность матриц; и

средство для отбрасывания модулированных элементов каждой матрицы, входящей в совокупность матриц, причем выходная последовательность содержит отброшенные модулированные элементы из каждой матрицы, входящей в совокупность матриц.

2. Устройство по п.1, в котором демультиплексирование происходит путем сохранения систематических битов и битов четности в совокупность прямоугольных массивов из R строк и С столбцов, формируя первый входной блок U, второй входной блок W0 и третий входной блок W1, причем первый входной блок U содержит систематические биты, второй входной блок W0 формируется путем сочленения первого множества битов четности, и третий входной блок W1 формируется путем сочленения второго множества битов четности.

3. Устройство по п.2, в котором систематические биты и биты четности записываются в совокупность массивов входных блоков U, W0 и W1 по строкам, причем биты размещаются начиная с верхней строки, слева направо.

4. Устройство по п.1, в котором индексное множество сортируется в возрастающем порядке.

5. Устройство по п.1, в котором переупорядочивание происходит путем:

определения

M1=M-N, если M>N,

2M-N в других случаях;

M2=min(2N, M1+M);

M3=M1+M-2N, если M2+M>2N,

M2+M-2N в других случаях,

где М обозначает количество битов, которое может быть передано в одном слоте, а N обозначает длину совокупности последовательностей;

определения индексного множества, как содержащего совокупность множеств S1, S2, S3, S4 и S5,

где S1={round(i*(2N/M1)|0≤i<M1},

S2={round(i*(2N/M2)|0≤i<M1}-S1,

S3={i|0≤i<2N}-S1-S2,

S4={round(i*(2N/M3)|0≤i<M3},

S5={i|0≤i<2N)-S4;

сортировки совокупности элементов каждого из множеств S1, S2, S3, S4 и S5 в порядке возрастания, и

переупорядочивания совокупности последовательностей следующим образом:

U, W0(S1), W0(S2), W0(S3), W1(S4), W1(S5) для групп 1, 2 и 4 скоростей, и

U, W0(S1), W0(S2), W0(S3) для групп 3 и 5 скоростей.

6. Устройство по п.5, в котором параметры для M1, M2 и М3 хранятся в справочной таблице.

7. Устройство по п.1, в котором группирование и перемежение происходит путем:

группирования переупорядоченной совокупности последовательностей в сегменты длиной М каждый и

выполнения перемежения матрицы на каждом из этих сегментов.

8. Устройство по п.1, в котором схемой модуляции для средства модуляции является 16-QAM.

9. Устройство по п.1, в котором средство отбрасывания также содержит средство для повторения модулированных элементов.

10. Устройство по п.1, в котором параметры для индексного множества хранятся в справочной таблице.

11. Способ для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может быть передана в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи, содержащий этапы, на которых:

демультиплексируют совокупность систематических битов и совокупность битов четности в совокупность последовательностей, причем совокупность систематических битов и совокупность битов четности последовательно распределяют среди совокупности последовательностей;

переупорядочивают совокупность последовательностей на основании индексного множества;

группируют совокупность последовательностей в совокупность сегментов и перемежают каждый из этих сегментов, формируя совокупность матриц, содержащих совокупность элементов;

модулируют совокупность элементов, входящих в совокупность матриц;

и

отбрасывают модулированные элементы каждой матрицы, входящей в совокупность матриц, причем выходная последовательность содержит отброшенные модулированные элементы из каждой матрицы, входящей в совокупность матриц.

12. Способ по п.11, в котором демультиплексирование происходит путем сохранения систематических битов и битов четности в совокупность прямоугольных массивов из R строк и С столбцов, формируя первый входной блок U, второй входной блок W0 и третий входной блок W1, причем первый входной блок U содержит систематические биты, второй входной блок W0 формируется путем сочленения первого множества битов четности, и третий входной блок W1 формируется путем сочленения второго множества битов четности.

13. Способ по п.12, в котором систематические биты и биты четности записываются в совокупность массивов входных блоков U, W0 и W1 по строкам, причем биты размещаются начиная с верхней строки, слева направо.

14. Способ по п.11, в котором индексное множество сортируется в возрастающем порядке.

15. Способ по п.11, в котором переупорядочивание происходит путем:

определения

M1=M-N, если M>N,

2M-N в других случаях;

M2=min(2N, M1+M);

M3=M1+M-2N, если M2+M>2N,

M2+M-2N в других случаях,

где М обозначает количество битов, которое может быть передано в одном слоте, а N обозначает длину совокупности последовательностей;

определения индексного множества, как содержащего совокупность множеств S1, S2, S3, S4 и S5,

где S1={round(i*(2N/M1)|0≤i<M1},

S2={round(i*(2N/M2)|0≤i<M1}-S1,

S3={i|0≤i<2N}-S1-S2,

S4={round(i*(2N/M3)|0≤i<M3},

S5={i|0≤i<2N)-S4;

сортировки совокупности элементов каждого из множеств S1, S2, S3, S4 и S5 в порядке возрастания; и

переупорядочивания совокупности последовательностей следующим образом:

U, W0(S1), W0(S2), W0(S3), W1(S4), W1(S5) для групп 1, 2 и 4 скоростей, и

U, W0(S1), W0(S2), W0(S3) для групп 3 и 5 скоростей.

16. Способ по п.15, в котором параметры для M1, M2 и М3 хранятся в справочной таблице.

17. Способ по п.11, в котором группирование и перемежение происходит путем:

группирования переупорядоченной совокупности последовательностей в сегменты длиной М каждый и

выполнения перемежения матрицы на каждом из этих сегментов.

18. Способ по п.11, в котором схемой модуляции для этапа модуляции является 16-QAM.

19. Способ по п.11, в котором этап отбрасывания также содержит этап повторения модулированных элементов.

20. Способ по п.11, в котором параметры для индексного множества хранятся в справочной таблице.

21. Способ по п.11, в котором отбрасывание выполняется в соответствии с желаемой скоростью кодового символа.

22. Способ для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может быть передана в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи, содержащий этапы, на которых:

демультиплексируют совокупность систематических битов и совокупность битов четности в совокупность последовательностей, причем совокупность систематических битов и совокупность битов четности последовательно распределяют среди совокупности последовательностей;

переупорядочивают совокупность последовательностей на основании индексного множества;

группируют совокупность последовательностей в совокупность сегментов и перемежают каждый из этих сегментов, формируя совокупность матриц, содержащих совокупность элементов;

отбрасывают элементы каждой матрицы, входящей в совокупность матриц, причем выходная последовательность содержит отброшенные элементы из каждой матрицы, входящей в совокупность матриц; и модулируют элементы совокупности матриц.

23. Способ по п.22, в котором индексное множество сортируется в возрастающем порядке.

24. Устройство для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может быть передана в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи, содержащее:

средство для демультиплексирования совокупности систематических битов и совокупности битов четности в совокупность последовательностей, причем совокупность систематических битов и совокупность битов четности последовательно распределяются среди совокупности последовательностей;

средство для переупорядочивания совокупности последовательностей;

средство для формирования совокупности матриц из переупорядоченных последовательностей, причем это средство формирования основано на индексном множестве;

средство для перестановки совокупности матриц, формируя сочлененную матрицу, содержащую совокупность сегментов, совокупность столбцов и совокупность элементов;

средство для перемежения совокупности столбцов;

средство для модуляции совокупности элементов, входящих в совокупность сегментов; и

средство для отбрасывания модулированных элементов в совокупности сегментов сочлененной матрицы, причем выходная последовательность содержит отброшенные модулированные элементы из совокупности сегментов сочлененной матрицы.

25. Устройство по п.24, в котором демультиплексирование происходит путем сохранения систематических битов и битов четности в совокупность прямоугольных массивов из R строк и С столбцов, формируя первый входной блок U, второй входной блок W0 и третий входной блок W1, причем первый входной блок U содержит систематические биты, второй входной блок W0 формируется путем сочленения первого множества битов четности, и третий входной блок W1 формируется путем сочленения второго множества битов четности.

26. Устройство по п.24, в котором систематические биты и биты четности записываются в совокупность массивов входных блоков U, W0 и W1 по строкам, причем биты размещаются начиная с верхней строки, слева направо.

27. Устройство по п.24, в котором индексное множество сортируется в возрастающем порядке.

28. Устройство по п.25, в котором переупорядочивание происходит путем:

циклического сдвига вниз каждого элемента в каждом столбце каждого блока и

изменения порядка расположения столбцов в каждом блоке.

29. Устройство по п.28, в котором в первом входном блоке U элементы в i-ом столбце циклически сдвигаются на величину (i mod R), где R обозначает количество строк прямоугольных массивов, формирующих входные блоки.

30. Устройство по п.28, в котором во входных блоках W0 и W1 элементы i-го столбца циклически сдвигаются на величину (floor(i/D)mod R), где D является предопределенным параметром, основанным на группе скоростей, а R обозначает количество строк прямоугольных массивов, формирующих входные блоки.

31. Устройство по п.24, в котором формирование происходит путем:

определения индексного множества, как содержащего совокупность множеств S1, S2, S3, S4 и S5,

где S1={floor(C/M1)+round(i*(2C/M1)|0≤i<M1},

S2={floor(C/M2)+round(i*(2C/M2)|0≤i<M2}-S1,

S3={i|0≤i<2C}-S1-S2,

S4={floor(C/M3)+round(i*(2C/M3)|0≤i<M3},

S5={i|0≤i<2C}-S4,

где параметры M1, M2 и М3 специфицированы в справочной таблице, а С обозначает количество столбцов прямоугольных массивов, формирующих входные блоки.

32. Устройство по п.24, в котором перестановка происходит путем:

расположения столбцов совокупности матриц следующим образом:

W, W0(S1), W0(S2), W0(S3), W1(S4), W1(S5), и

разбивки сочлененной матрицы на совокупность сегментов, включающих в себя столбцы L1, L2, L3 и L4, где L1, L2, L3 и L4 определяются следующим образом:

L1=2M/R, если группа скоростей = 3,

M/R в других случаях,

L2=L3=M/R;

L4=остающиеся столбцы,

где М обозначает количество кодовых символов, которое может быть передано в одном слоте, a R обозначает количество строк прямоугольных массивов, формирующих входные блоки.

33. Устройство по п.32, в котором параметры для M1, M2 и М3 хранятся в справочной таблице.

34. Устройство по п.32, в котором сочлененная матрица имеет 4 строки, 4С или 6С столбцов и К уровней, где С обозначает количество столбцов прямоугольных массивов, формирующих входные блоки, а К определяет уровень перемежения для сочлененной матрицы.

35. Устройство по п.32, в котором перемежение происходит путем:

сдвига i-го столбца на место π(i)-го столбца в каждом k-м сегменте (k=1, 2, 3), где

π(i)=79imodLk, 0≤i<Lk; и

считывания элементов в каждом сегменте, причем сначала дается приращение индексу столбца, а затем индексу строки.

36. Устройство по п.24, в котором схемой модуляции для средства модуляции является 16-QAM.

37. Устройство по п.24, в котором средство отбрасывания, сверх того, содержит средство для повторения модулированных элементов.

38. Устройство по п.24, в котором параметры для индексного множества хранятся в справочной таблице.

39. Способ для перемежения совокупности систематических битов и совокупности битов четности и для генерации выходной последовательности, которая может быть передана в многослотовых пакетах из базовой станции в удаленную станцию в системе беспроводной связи, содержащий этапы, на которых:

демультиплексируют совокупность систематических битов и совокупность битов четности в совокупность последовательностей, причем совокупность систематических битов и совокупность битов четности последовательно распределяют среди совокупности последовательностей;

переупорядочивают совокупность последовательностей;

формируют совокупность матриц из переупорядоченной совокупности последовательностей, причем это формирование основано на индексном множестве;

переставляют совокупность матриц, формируя сочлененную матрицу, содержащую совокупность сегментов, совокупность столбцов и совокупность элементов;

перемежают совокупность столбцов;

модулируют совокупность элементов, входящих в совокупность сегментов; и

отбрасывают модулированные элементы в совокупности сегментов сочлененной матрицы, причем выходная последовательность содержит отброшенные модулированные элементы из совокупности сегментов сочлененной матрицы.