Область техники

[0001] Варианты осуществления настоящей заявки относятся к области связи и, в частности, к способу обработки информации и аппаратуре связи.

Уровень техники

[0002] Код проверки четности с низкой плотностью (LDPC) представляет собой тип линейного блочного кода, характеризуемого разреженной матрицей проверки, и имеет гибкую структуру и низкую сложность декодирования. Поскольку частично параллельный алгоритм итеративного декодирования может быть использован при декодировании кодированного слова с кодированием LDPC, код LDPC имеет более высокую эффективность, чем традиционный турбокод. Код LDPC может использоваться в качестве кода с исправлением ошибок в системе связи, чтобы улучшить надежность и использование мощности при канальной передаче. Код LDPC также может широко использоваться в пространственной связи, оптоволоконной связи, системах персональной связи, асимметричной цифровой абонентской линии (ADSL), устройствах магнитной записи и тому подобном. В настоящее время код LDPC считается одной из схем канального кодирования в системах мобильной связи пятого поколения (5G).

[0003] В реальных применениях могут использоваться матрицы LDPC, имеющие разные специальные структуры. Матрица H LDPC, имеющая специальную структуру, может быть получена путем расширения (также называемого подъемом) базовой матрицы LDPC, имеющей структуру квазицикла (QC). Схема кодирования с использованием матриц QC-LDPC подходит для аппаратных средств с высокой степенью параллелизма и обеспечивает более высокую эффективность. Матрица QC-LDPC может быть спроектирована так, чтобы она подходила для канального кодирования.

[0004] Схема кодирования с использованием матриц QC-LDPC подходит для аппаратных средств с высокой степенью параллелизма и обеспечивает более высокую эффективность. Матрица QC-LDPC может быть спроектирована так, чтобы она подходила для канального кодирования.

Сущность изобретения

[0005] Варианты осуществления настоящей заявки предоставляют способ обработки информации, а также аппаратуру и систему связи, чтобы поддерживать кодирование и декодирование информационных битовых последовательностей с множеством длин.

[0006] Согласно первому аспекту предоставлены способ кодирования и кодер. Кодер кодирует входную последовательность с использованием матрицы проверки четности с низкой плотностью (LDPC).

[0007] Согласно второму аспекту предоставлены способ декодирования и декодер. Декодер декодирует входную последовательность с использованием матрицы LDPC.

[0008] В первой реализации первого аспекта или второго аспекта матрица LDPC получается на основе коэффициента Z подъема и базовой матрицы.

[0009] На основании вышеизложенной реализации базовая матрица базового графа включает в себя одно из следующего:

базовая матрица включает в себя строку 0 - строку 6, столбец 0 - столбец 16 одной из матриц, показанных на фиг. с 3b-1 по 3b-8 или

базовая матрица включает в себя строку 0 - строку 6, некоторые из столбца 0 - столбца 16 в одной из матриц, показанных на фиг. с 3b-1 по 3b-8 или

базовая матрица является матрицей, полученной путем выполнения преобразования строки/столбца для строки 0 - строки 6, столбца 0 столбца 16 в одной из матриц, показанных на фиг. с 3b-1 по 3b-8 или

базовая матрица представляет собой матрицу, полученную путем выполнения преобразования строки/столбца в строке 0 – строке 6, некоторых из столбца 0 - столбца 16 в одной из матриц, показанных на фиг. с 3b-1 по 3b-8.

[0010] Чтобы поддерживать разные длины кодовых блоков, для кода LDPC требуются разные коэффициенты Z подъема. На основе вышеупомянутых реализаций используются базовые матрицы, соответствующие различным коэффициентам Z подъема, на основе различных коэффициентов Z подъема. В некоторых реализациях Z=a×2j, где 0≤j<7, и a∈ {2,3,5,7,9,11,13,15}.

[0011] Кроме того, на основе вышеупомянутых реализаций матрица LDPC может быть получена на основе коэффициента Z подъема и матрицы Hs, которая получается путем сдвига вышеупомянутой базовой матрицы. Альтернативно, матрица LDPC может быть получена на основе коэффициента Z подъема и матрицы, которая получается путем выполнения преобразования строки/столбца для матрицы Hs, а Hs получается путем сдвига вышеупомянутой базовой матрицы. Сдвиг вышеуказанной базовой матрицы может увеличивать или уменьшать значение сдвига, большее или равное 0, в одном или нескольких столбцах посредством некоторого сдвига.

[0012] Базовый граф и базовая матрица матрицы LDPC в вышеприведенных реализациях могут удовлетворять требованию к производительности кодовых блоков множества длин блоков.

[0013] Коэффициент Z подъема может быть определен кодером или декодером на основе длины K входной последовательности или может быть определен другим устройством и предоставлен кодеру или декодеру в качестве входного параметра. Необязательно, матрица LDPC может быть получена на основе полученного коэффициента Z подъема и базовой матрицы, соответствующей коэффициенту Z подъема.

[0014] Во второй реализации первого аспекта или второго аспекта матрица LDPC получается на основе коэффициента Z подъема и параметра(ов) матрицы LDPC.

[0015] Параметры матрицы LDPC могут включать в себя индекс строки, индекс столбца некоторого столбца, в котором расположен ненулевой элемент, и значение сдвига ненулевого элемента. Параметры хранятся таким образом, как строки от 0 до 6 в одной из таблицы 2 и с таблицы 3b-1 по таблицу 3b-8. Параметры матрицы LDPC могут дополнительно включать в себя вес строки. Расположение ненулевых элементов в столбцах находится в однозначном соответствии со значениями сдвига ненулевых элементов.

[0016] Для устройства связи на передающей стороне кодирование входной последовательности с использованием матрицы LDPC может включать в себя: кодирование входной последовательности с использованием матрицы LDPC, соответствующей коэффициенту Z подъема; или кодирование входной последовательности с использованием матрицы, полученной путем выполнения преобразования строки/столбца в матрице LDPC, соответствующей коэффициенту Z подъема. Преобразование строки/столбца в этой заявке означает преобразование строки, преобразование столбца или преобразование строки и преобразование столбца.

[0017] Для устройства связи на приемной стороне декодирование входной последовательности с использованием матрицы LDPC может включать в себя: декодирование входной последовательности с использованием матрицы LDPC, соответствующей коэффициенту Z подъема; или декодирование входной последовательности с использованием матрицы, полученной путем выполнения преобразования строки/столбца в матрице LDPC, соответствующей коэффициенту Z подъема. Преобразование строки/столбца в этой заявке означает преобразование строки, преобразование столбца или преобразование строки и преобразование столбца.

[0018] В возможной реализации матрица LDPC может быть сохранена, и матрица LDPC используется для кодирования входной последовательности, или матрица LDPC, которая может использоваться для кодирования, получается путем выполнения преобразования (преобразования строки/столбца) или подъема на основе матрицы LDPC.

[0019] В другой возможной реализации параметр или параметры могут быть сохранены, и матрица LDPC, используемая для кодирования или декодирования, может быть получена на основе параметра, так что входная последовательность может быть кодирована или декодирована на основе матрицы LDPC. Параметр или параметры включают в себя по меньшей мере одно из следующего: базовый граф, базовую матрицу, преобразованную матрицу, полученную посредством выполнения преобразования строки/столбца на базовом графе или базовой матрице, поднимающую матрицу на основе базового графа или базовой матрицы, значение сдвига ненулевого элемента в базовой матрице или любой параметр, используемый для получения матрицы LDPC.

[0020] В еще одной возможной реализации базовая матрица матрицы LDPC может храниться в памяти.

[0021] В еще одной возможной реализации базовый граф матрицы LDPC может храниться в памяти, а значение сдвига ненулевого элемента в базовой матрице матрицы LDPC может храниться в памяти.

[0022] В еще одной возможной реализации параметр матрицы LDPC сохраняется в памяти способами, подобными Таблице 2 или Таблицам 3b-1 - 3b-8, или могут быть сохранены некоторые группы элементов параметра.

[0023] На основании вышеизложенных возможных реализаций, в возможном исполнении по меньшей мере одно из базового графа и базовой матрицы, используемых для кодирования или декодирования LDPC, получается посредством выполнения преобразования строки или преобразования столбца, или преобразования строки и преобразования столбца, по меньшей мере, для одного из базового графа и базовой матрицы упомянутой матрицы LDPC.

[0024] Согласно третьему аспекту предоставляется аппаратура связи. Аппаратура связи может включать в себя программные модули и/или аппаратные компоненты, сконфигурированные для выполнения вышеизложенных способов исполнения.

[0025] В возможном исполнении аппаратура связи, предусмотренная в третьем аспекте, включает в себя процессор и компонент приемопередатчика. Процессор и компонент приемопередатчика могут быть выполнены с возможностью выполнения любой из возможных реализаций способа кодирования или способа декодирования. Устройство связи может быть терминалом, базовой станцией или другим сетевым устройством, а компонент приемопередатчика аппаратуры связи может быть приемопередатчиком. Аппаратура связи может быть микросхемой основной полосы частот или платой основной полосы частот, а компонент приемопередатчика аппаратуры связи может быть схемой ввода/вывода микросхемы основной полосы частот или платы основной полосы частот и сконфигурирована для приема/отправки входного/выходного сигнала. Необязательно, аппаратура связи может дополнительно включать в себя память, сконфигурированную для хранения данных и/или инструкций.

[0026] В одной реализации процессор может включать в себя кодер в соответствии с первым аспектом и блок определения. Блок определения выполнен с возможностью определения коэффициента Z подъема, требуемого для кодирования входной последовательности. Кодер сконфигурирован для кодирования входной последовательности с использованием матрицы LDPC, соответствующей коэффициенту подъема Z подъема.

[0027] В другой реализации процессор может включать в себя декодер согласно второму аспекту и модуль получения. Модуль получения выполнен с возможностью получения программного значения кода LDPC и коэффициента Z подъема. Декодер выполнен с возможностью декодировать программное значение кода LDPC на основе базовой матрицы HB, соответствующей коэффициенту Z подъема, для получения последовательности битов информации.

[0028] Согласно четвертому аспекту предоставлена аппаратура связи. Аппаратура связи включает в себя один или несколько процессоров. В возможном исполнении один или несколько процессоров сконфигурированы для выполнения любой из возможных реализаций кодера согласно первому аспекту. В другом возможном исполнении кодер в соответствии с первым аспектом может быть частью процессора. В дополнение к функциям кодера согласно первому аспекту процессор может дополнительно реализовывать другие функции. В возможном исполнении один или несколько процессоров могут реализовывать функции декодера согласно второму аспекту. В другом возможном исполнении декодер согласно второму аспекту может быть частью процессора.

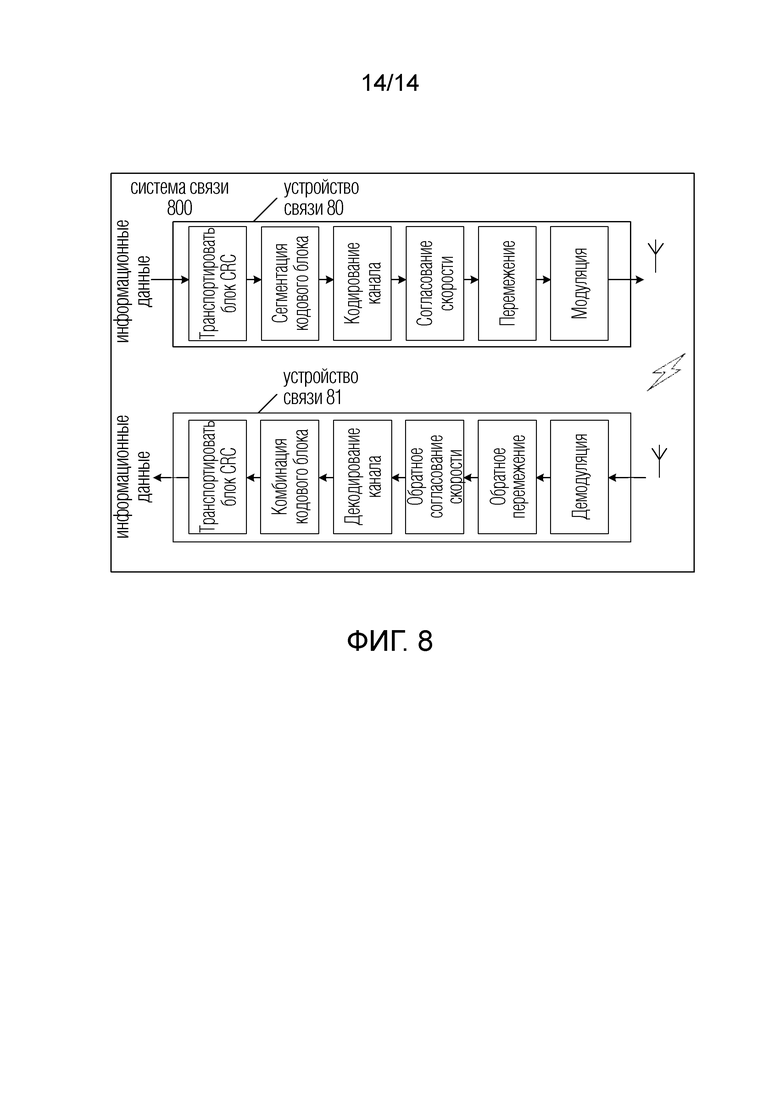

[0029] Необязательно, аппаратура связи может дополнительно включать в себя приемопередатчик и антенну. Необязательно, аппаратура связи может дополнительно включать в себя компонент для циклическим избыточным кодом (CRC) транспортного блока, компонент для сегментации кодового блока и проверки CRC, перемежитель для перемежения, модулятор для обработки модуляции или тому подобное. В возможном исполнении функции этих компонентов могут быть реализованы с использованием одного или нескольких процессоров.

[0030] Необязательно, аппаратура связи может дополнительно включать в себя демодулятор для операции демодуляции, обращенный перемежитель для обратного перемежения, компонент для обеспечения несовпадения скорости или тому подобное. Функции этих устройств могут быть реализованы с использованием одного или нескольких процессоров.

[0031] Согласно пятому аспекту вариант осуществления настоящей заявки предоставляет систему связи. Система включает в себя аппаратуру связи согласно третьему аспекту.

[0032] Согласно шестому аспекту вариант осуществления настоящей заявки предоставляет систему связи. Система включает в себя одну или несколько аппаратур связи в соответствии с четвертым аспектом.

[0033] Согласно еще одному аспекту вариант осуществления настоящей заявки предоставляет компьютерный носитель данных. Компьютерный носитель данных хранит программу, и когда программа запускается, компьютер должен выполнять способы, описанные в предыдущих аспектах.

[0034] Еще один аспект этой заявки предоставляет компьютерный программный продукт, включающий в себя одну или несколько инструкций, которые при выполнении компьютером заставляют компьютер выполнять способы в соответствии с вышеизложенными аспектами.

[0035] Согласно способу обработки информации, аппаратуре, устройству связи и системе связи в вариантах осуществления настоящей заявки, требования гибкой кодовой длины и скорости кодирования системы могут быть удовлетворены с точки зрения производительности кодирования и минимального уровня ошибок.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

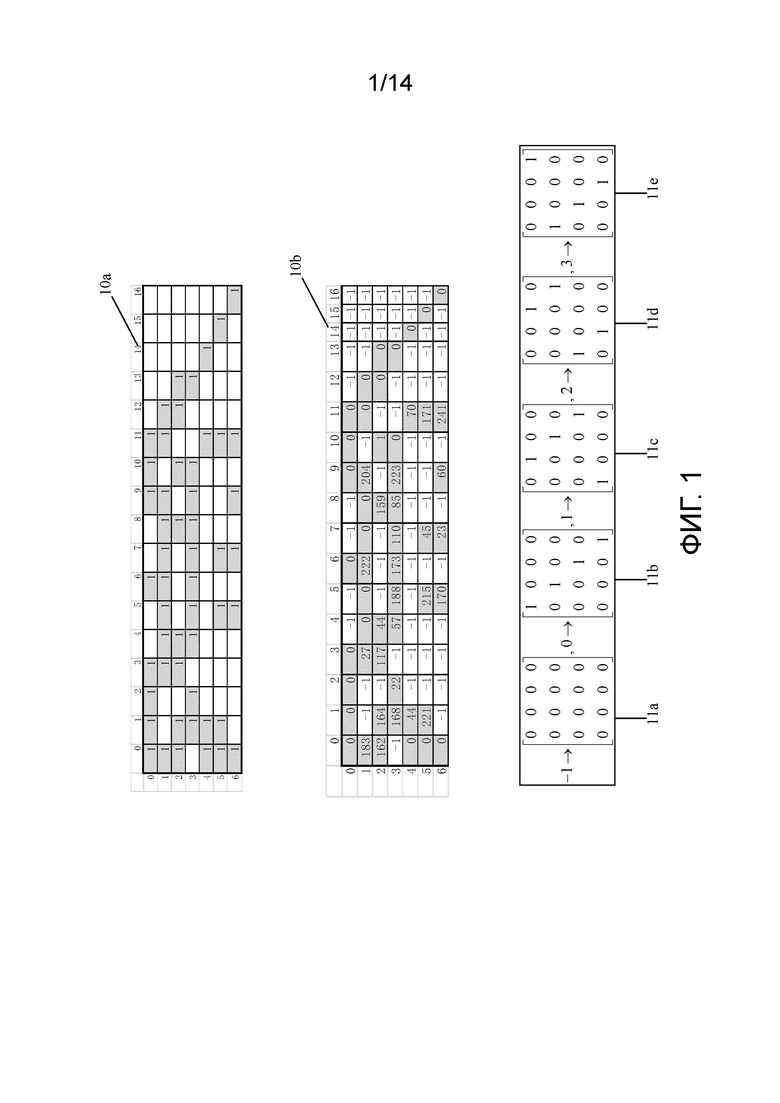

[0036] Фиг. 1 показывает примеры базового графа, базовой матрицы и матриц циклической перестановки, которые используются в коде LDPC;

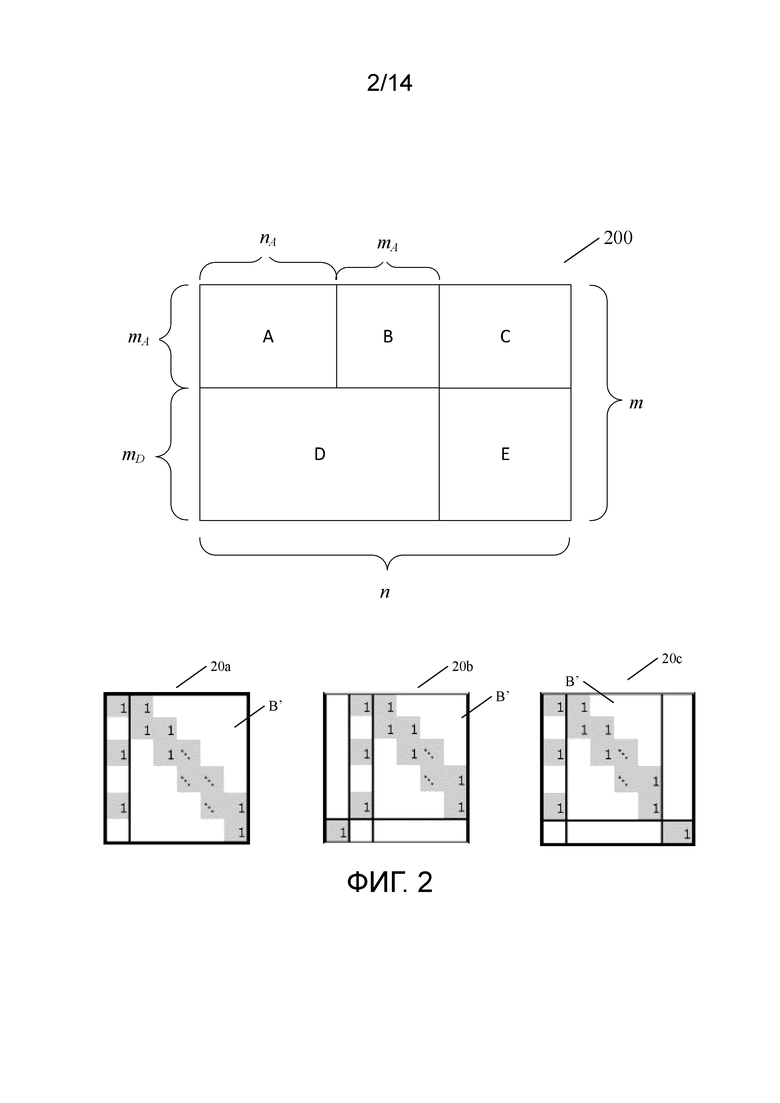

[0037] Фиг. 2 - структурная схема базового графа, который используется в коде LDPC;

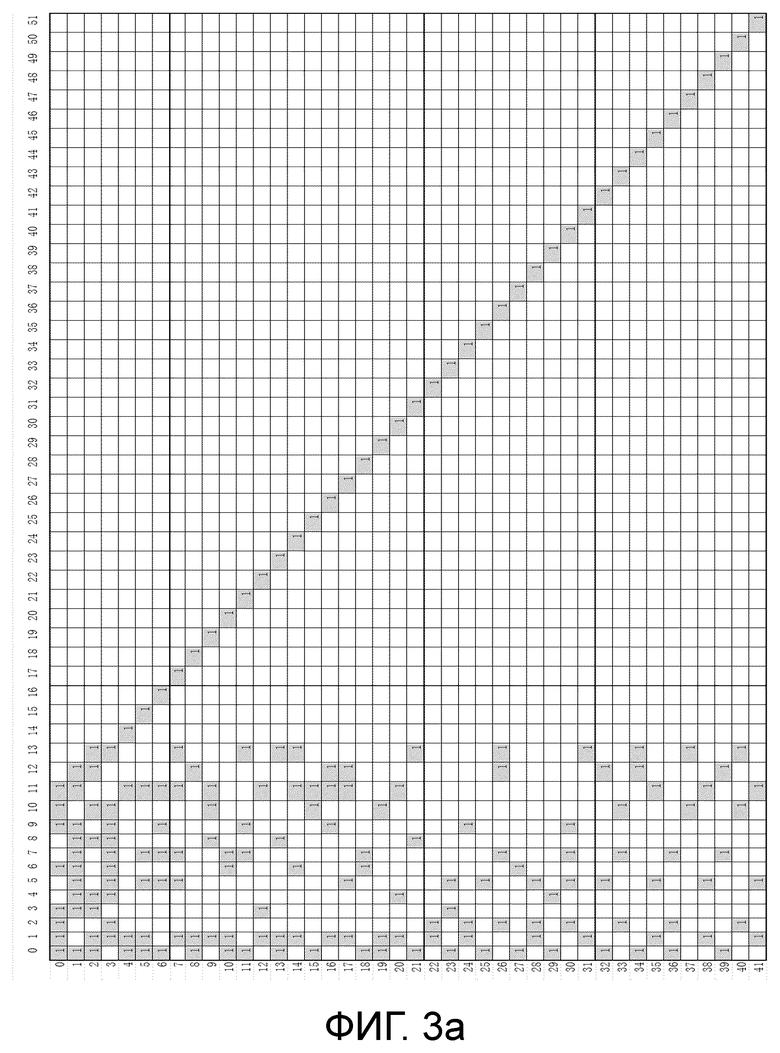

[0038] Фиг. 3a является схематической диаграммой базового графа, который используется в коде LDPC согласно варианту осуществления настоящей заявки;

[0039] Фиг. 3b-1 является схематической диаграммой базовой матрицы в соответствии с вариантом осуществления настоящей заявки;

[0040] Фиг. 3b-2 - схематическая диаграмма другой базовой матрицы в соответствии с вариантом осуществления настоящей заявки;

[0041] Фиг. 3b-3 - схематическая диаграмма другой базовой матрицы в соответствии с вариантом осуществления настоящей заявки;

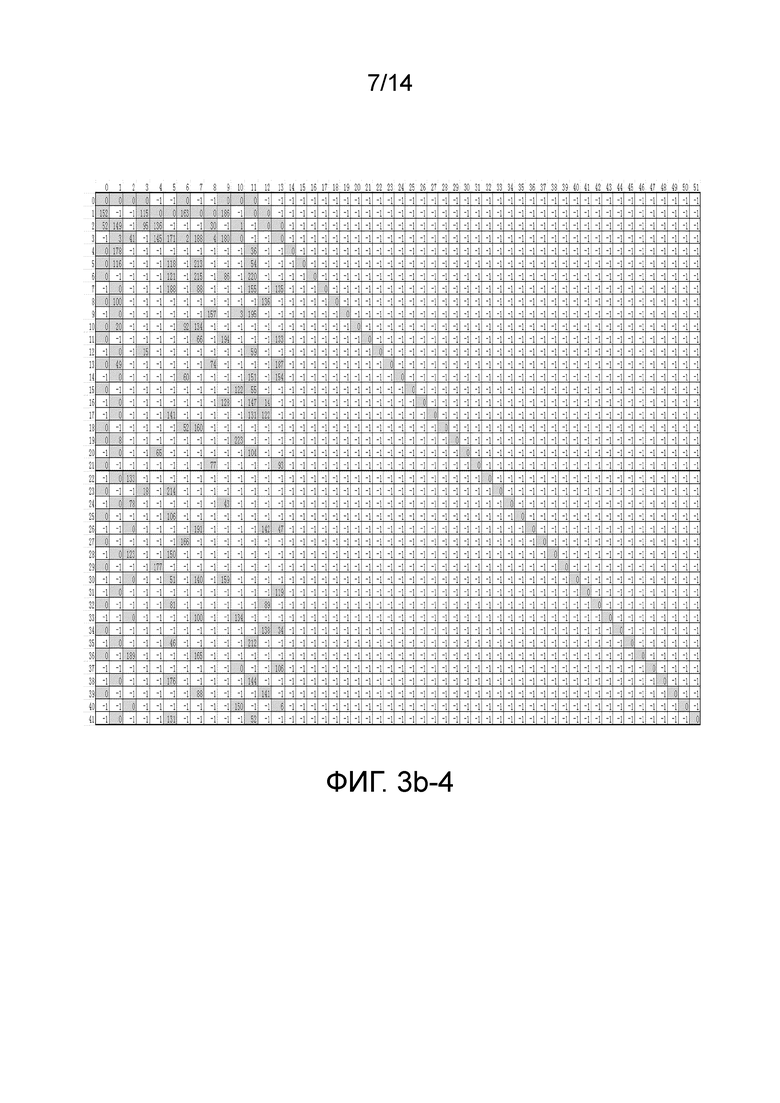

[0042] Фиг. 3b-4 является схематической диаграммой другой базовой матрицы согласно варианту осуществления настоящей заявки;

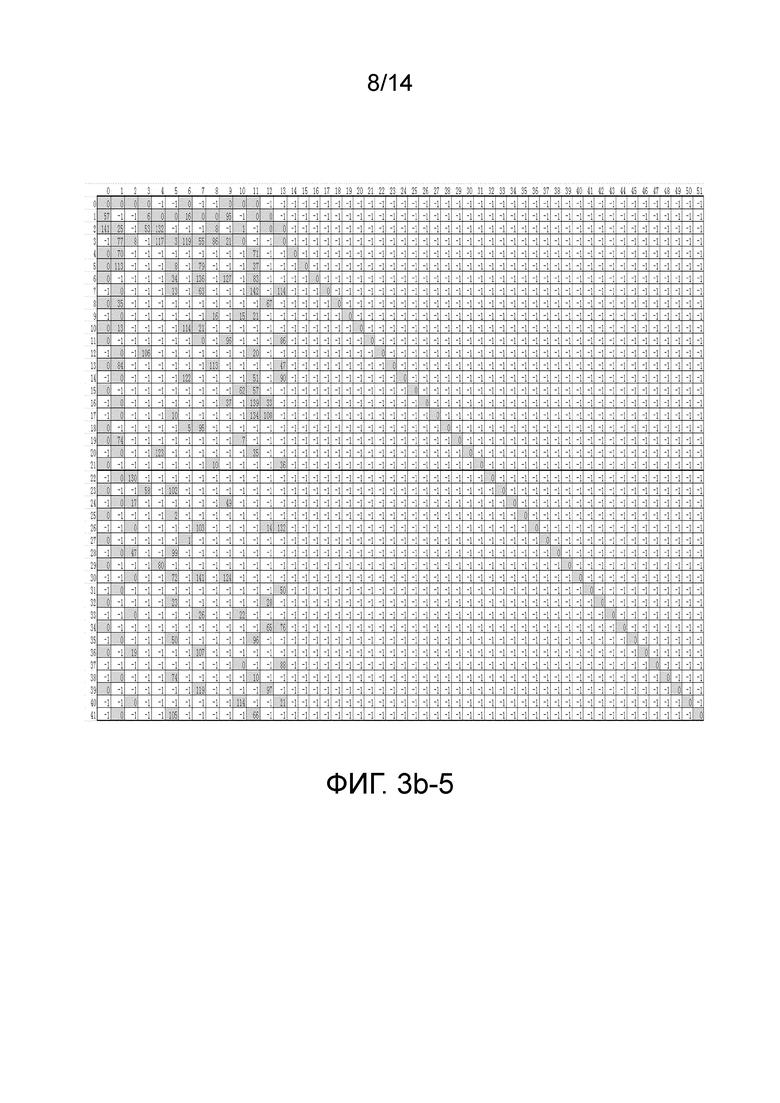

[0043] Фиг. 3b-5 является схематической диаграммой другой базовой матрицы согласно варианту осуществления настоящей заявки;

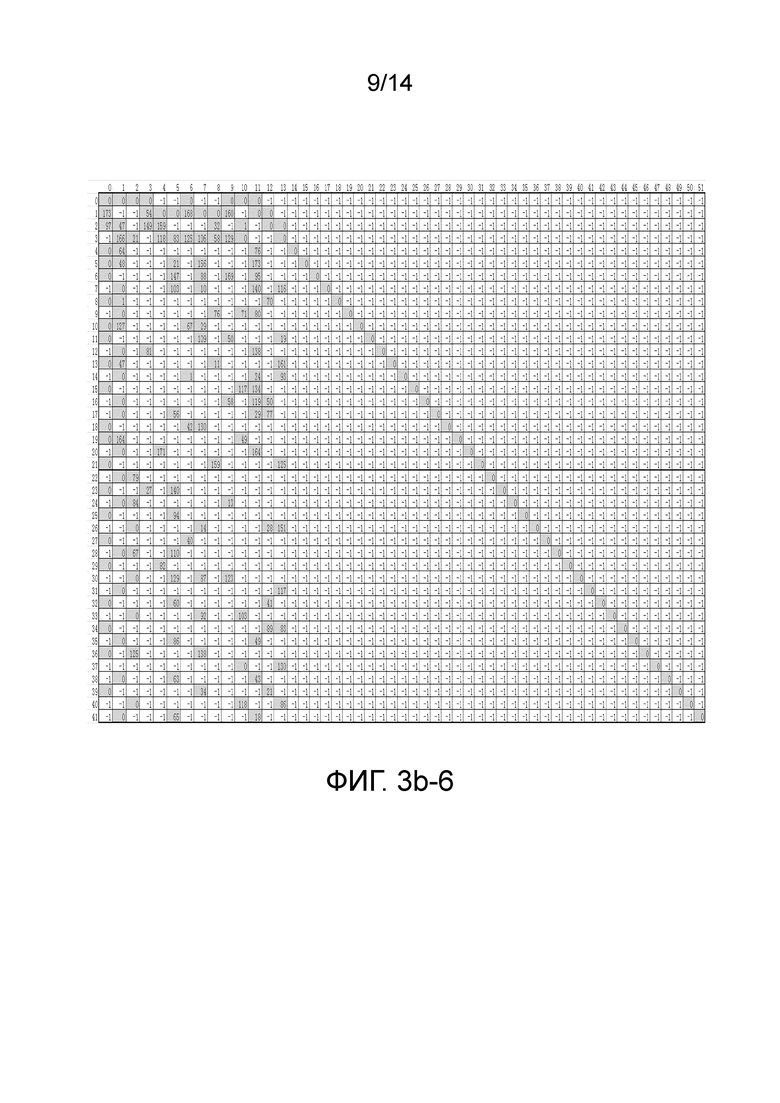

[0044] Фиг. 3b-6 - схематическая диаграмма другой базовой матрицы в соответствии с вариантом осуществления настоящей заявки;

[0045] Фиг. 3b-7 - схематическая диаграмма другой базовой матрицы в соответствии с вариантом осуществления настоящей заявки;

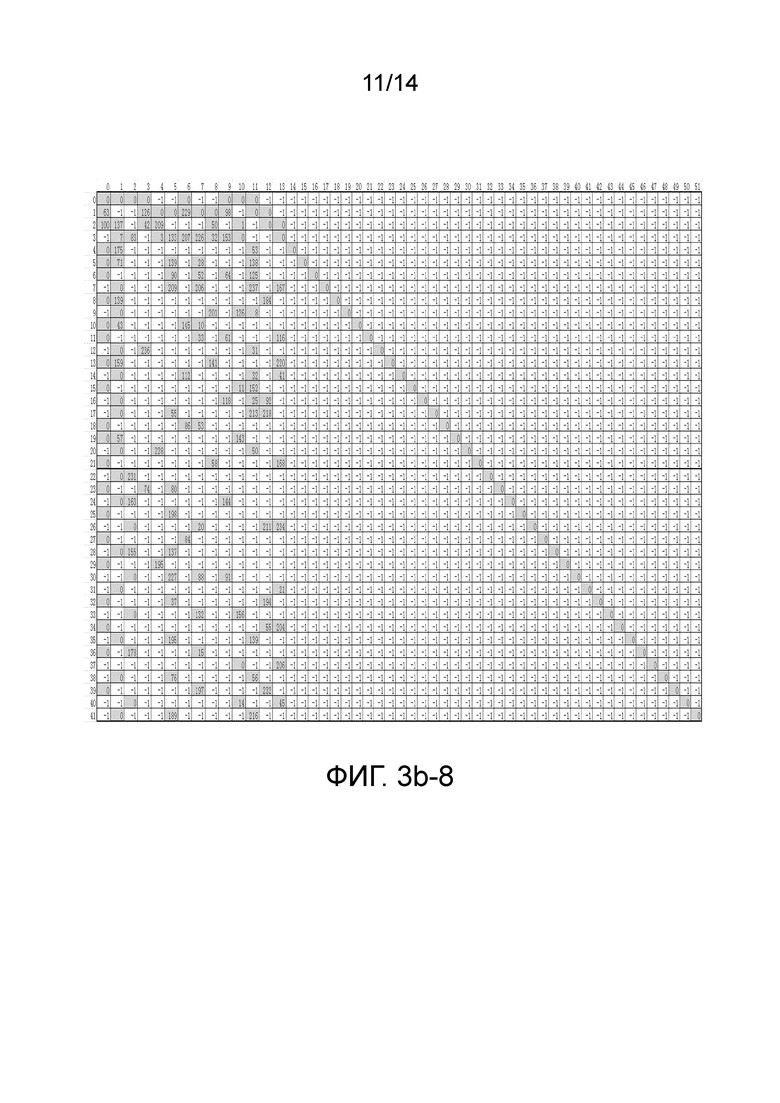

[0046] Фиг. 3b-8 - схематическая диаграмма другой базовой матрицы в соответствии с вариантом осуществления настоящей заявки;

[0047] Фиг. 4 является диаграммой производительности, обеспеченной вариантом осуществления настоящей заявки;

[0048] Фиг. 5 - блок-схема процедуры обработки информации в соответствии с вариантом осуществления настоящей заявки;

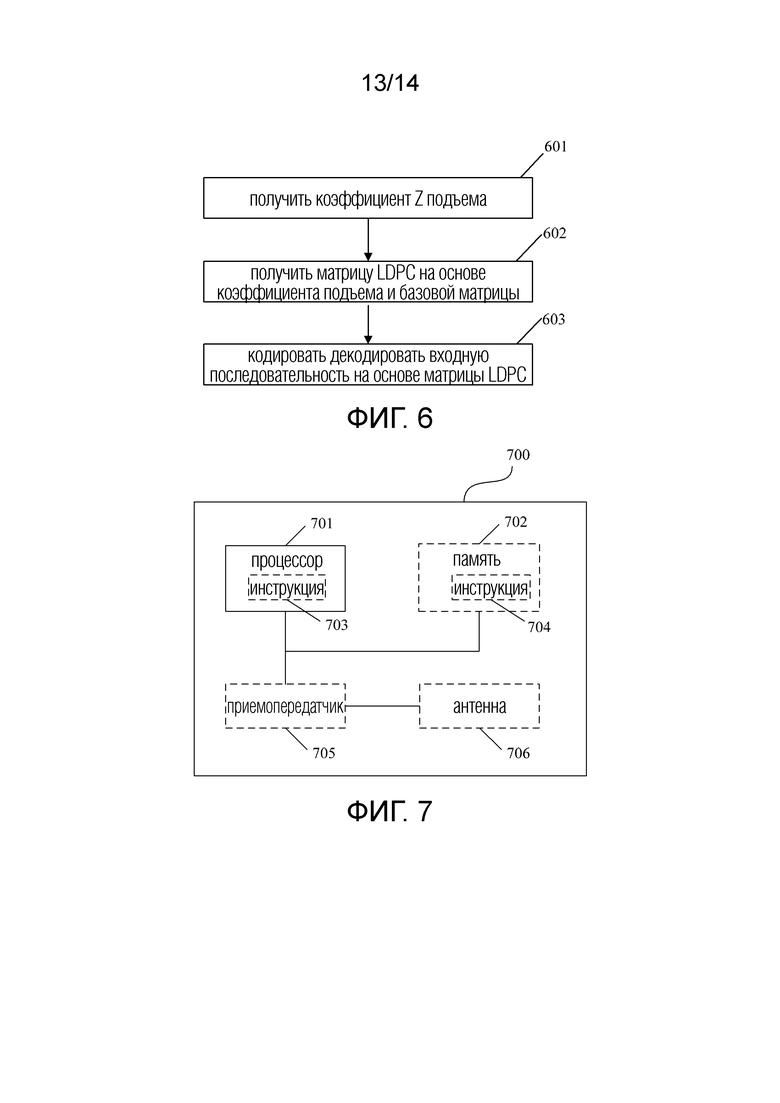

[0049] Фиг. 6 - блок-схема процедуры обработки информации в соответствии с вариантом осуществления настоящей заявки;

[0050] Фиг.7 - упрощенная блок-схема устройства связи в соответствии с вариантом осуществления настоящей заявки; и

[0051] Фиг. 8 - блок-схема системы связи в соответствии с вариантом осуществления настоящей заявки.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0052] Для простоты понимания ниже описаны некоторые термины, используемые в данной заявке.

[0053] В этой заявке термины «сеть» и «система» часто используются взаимозаменяемо, «аппаратура» и «устройство» часто используются взаимозаменяемо, и «информация» и «данные» также часто используются взаимозаменяемо. Значения этих терминов общеприняты. «Аппаратура связи» может относиться к микросхеме (например, микросхеме основной полосы частот, микросхеме цифровой обработки сигналов или микросхеме общего назначения), терминалу, базовой станции или другим сетевым устройствам. Терминал - это устройство, имеющее функции связи. Терминал может быть портативным устройством, автомобильным устройством, носимым устройством или другими видами устройств, которые имеют функции беспроводной связи. Терминал может называться разными названиями в разных сетях, такими как пользовательское оборудование, мобильная станция, абонентское устройство, станция, сотовый телефон, персональный цифровой помощник, беспроводной модем, устройство беспроводной связи, портативное устройство, портативный компьютер, беспроводной телефонный аппарат или беспроводная локальная линейная станция. Для простоты описания эти устройства все вместе упоминаются как терминал в этой заявке. Базовая станция (base station, BS) или называемая устройством базовой станции - это устройство, развернутое в сети радиодоступа для обеспечения функций беспроводной связи. Базовая станция может называться разными названиями в разных системах беспроводного доступа. Например, базовая станция в сети Универсальной системы мобильной связи (UMTS) упоминается как NodeB (узел B). Базовая станция в сети долгосрочного развития (LTE) упоминается как развитый NodeB (eNB или eNodeB). Базовая станция в новой сети радиосвязи (NR) упоминается как точка приема передачи (TRP) или NodeB следующего поколения (gNB). Базовые станции в других сетях могут называться другими названиями. Это не ограничено в настоящей заявке.

[0054] Технические решения в вариантах осуществления настоящей заявки описаны ниже со ссылкой на прилагаемые чертежи.

[0055] Код LDPC может быть определен матрицей H проверки на четность H. В одной реализации матрица H проверки на четность для кода LDPC, также называемая матрицей LDPC, представлена матрицей, называемой базовым графом, и каждый элемент в базовом графе представляет собой матрицу расширения (подъема) Z×Z. Z представляет собой положительное целое число и упоминается как коэффициент Z подъема. Z также может упоминаться как размер подъема или тому подобное. Базовый граф используется для указания местоположения нулевых элементов и ненулевых элементов. Каждый ненулевой элемент в базовом графе соответствует значению сдвига. Матрица H проверки на четность для кода LDPC может быть получена на основе базового графа и значений сдвига. Обычно базовый граф включает в себя m × n матричных элементов (также называемые записями) и представлен матрицей из m строк и n столбцов. Значение каждого элемента матрицы равно 0 или 1. Элемент, значение которого равно 0, называется нулевым элементом, который соответствует матрице из всех нулей Z столбца ×Z строки. Элемент, значение которого равно 1, называется ненулевым элементом, который соответствует матрице циклической перестановки Z столбца×Z строки. Другими словами, каждый элемент базового графа представляет собой либо матрицу из всех нулей, либо матрицу циклической перестановки. В примере 10a базового графа, показанном на фиг. 1, m=7 и n=17, и базовый граф 10a имеет структуру QC. Следует отметить, что во всем этой заявке индексы строк и индексы столбцов базовых графов и базовых матриц нумеруются начиная с 0, и это просто для простоты описания. Например, индекс 0 столбца представляет первый столбец в базовом графе или базовой матрице, индекс 1 столбца представляет второй столбец в базовом графе или базовой матрице, индекс 0 строки представляет первую строку в базовом графе или базовой матрице индекс 1 строки представляет вторую строку в базовом графе или базовой матрице и так далее.

[0056] Понятно, что строки и столбцы могут альтернативно быть пронумерованы, начиная с 1. В этом случае индексы строк и столбцов, показанные в данном описании, увеличиваются на 1 соответственно. Например, если индексы строк и индексов столбцов нумеруются, начиная с 1, столбец 1 представляет первый столбец в базовом графе и матрице, столбец 2 представляет второй столбец в базовом графе и матрице, строка 1 представляет первую строку в базовом графе и матрице, строка 2 представляет вторую строку в базовом графе и матрице и так далее.

[0057] В другой реализации базовая матрица из m строк и n столбцов может быть определена и иногда упоминается как PCM (parity check matrix). Например, любая матрица, представленная на фиг. с 3b-1 по фиг. 3b-8 или матрица, включающая в себя некоторые строки и столбцы в любой матрице на фиг. с 3b-1 по фиг. 3b-8 определена. Элементы в базовой матрице однозначно соответствуют элементам в базовом графе. Нулевой элемент в базовом графе имеет такую же позицию в базовой матрице. В базовой матрице нулевой элемент может быть представлен как -1 или «ноль». Расположение ненулевого элемента в строке i и столбце j, значение которого равно 1 в базовом графе, имеет такую же позицию в базовой матрице, и ненулевой элемент представлен как Vi,j. Значение Vi,j в базовой матрице может быть определено системой или может быть предварительно определено, или Vi,j может быть получено на основе значения Pi,j сдвига ненулевого элемента в базовом графе и коэффициента Z подъема. Pi,j является значением сдвига, соответствующим заранее определенному или конкретному коэффициенту Z подъема. Pi,j может быть получено на основе Z и Vi,j. В реализации Pi,j и Vi,j удовлетворяют следующему соотношению:

Pi,j=mod(Vi,j, Z)

где i и j представляют индекс строки и индекс столбца ненулевого элемента и указывают местоположение элемента в базовой матрице.

[0058] В вариантах осуществления этой заявки иногда базовая матрица также упоминается как матрица сдвига базового графа. Базовая матрица может быть получена в соответствии с базовым графом и значением сдвига. Если элемент в строке i и столбце j базового графа имеет значение 1, а значение сдвига элемента равно Pi,j, где Pi,j - целое число, большее или равное 0, это означает, что элемент может быть заменен на матрицу циклической перестановки Z×Z, соответствующую Pi,j. Матрица циклической перестановки также может называться матрицей сдвига. Матрица циклической перестановки может быть получена путем циклического сдвига единичной матрицы Z×Z вправо или влево Pi,j раз. В реализации,

Pi,j=mod(Vi,j, Z)

где Vi,j - это значение в базовой матрице, которое соответствует ненулевому элементу в базовом графе. Иногда Vi,j также может упоминаться как значение сдвига, значение циклического сдвига или коэффициент сдвига. Vi,j может быть, например, значением сдвига, соответствующим максимальному коэффициенту Zmax. Zmax является максимальным значением в наборе значений Z. Если значение элемента в строке i и столбце j в базовом графе равно 0, элемент может быть заменен на матрицу Z×Z со всеми нулями. Если значение элемента в строке i и столбце j в базовом графе равно 1, элемент может быть заменен матрицей циклической перестановки Z×Z, имеющей значение сдвига Pi,j. Таким образом, получается матрица H проверки четности для кода LDPC. Z является положительным целым числом и может упоминаться как коэффициент подъема, размер подъема или тому подобное. Z может быть определен на основе размера кодового блока и размера информационных данных, которые поддерживаются системой. Можно видеть, что для базового графа из m строк × n столбцов размер матрицы H проверки четности для кода LDPC составляет (m×Z) строк × (n×Z) столбцов. Например, если коэффициент Z подъема равен 4, каждый нулевой элемент заменяется матрицей из всех нулей размером 4×4 (см. 11a на фиг. 1). Если P2,3=2, ненулевой элемент в строке 2 и столбце 3 базовой матрицы заменяется матрицей 11d циклической перестановки 4×4 на фиг. 1. Матрица 11d получается путем циклического сдвига единичной матрицы 11b 4×4 вправо дважды. Если P2,4=0, ненулевой элемент в строке 2 и столбце 4 заменяется единичной матрицей 11b. Следует отметить, что этот пример приведен только для иллюстрации и не предназначен для ограничения.

[0059] Значение Pi,j может зависеть от коэффициента Z подъема. Для элемента 1 в базовом графе Pi,j может отличаться для разных коэффициентов Z подъема. Базовая матрица, соответствующая базовому графу 10a, показана на фиг.10b на фиг. 1. Например, для значения 1 в строке 1 и столбце 3 в базовом графе 10a соответствующее значение Vi,j сдвига в строке 1 и столбце 3 в базовой матрице 10b равно 27. Значение Pi,j может быть получено в соответствии с Pi,j=mod(Vi,j, Z). Таким образом, элемент в строке 1 и столбце 3 может быть заменен матрицей циклической перестановки, которая получается путем циклического сдвига единичной матрицы размера Z×Z вправо или влево Pi,j раз.

[0060] Обычно базовый граф или базовая матрица для кода LDPC могут дополнительно включать в себя p столбцов встроенного выколотого столбца, где p может быть целым числом от 0 до 2. Эти столбцы могут использоваться при кодировании, но закодированные системные биты, соответствующие встроенным выколотым столбцам, не отправляются. В этом случае скорость кодирования базовой матрицы для кода LDPC удовлетворяет условию R=(n-m)/(n-p). Используя базовый граф 10a в качестве примера, если имеется два встроенных выколотых столбца, скорость кодирования составляет (17–7)/(17–2)=0.667, что составляет приблизительно 2/3.

[0061] Код LDPC, используемый в системе беспроводной связи, представляет собой код QC-LDPC. Часть бита четности в коде QC-LDPC имеет двухдиагональную структуру или структуру, подобную раптору. Это может упростить кодирование и поддерживать гибридное повторение с добавочной избыточностью. Декодер для кода QC-LDPC обычно использует сеть сдвига QC-LDPC (QSN), сеть Banyan или сеть Benes для информации циклического сдвига.

[0062] Базовый граф 200 для кода QC-LDPC, который имеет структуру, похожую на раптор, представляет собой матрицу из m строк и n столбцов. Базовый граф 200 может включать в себя пять подматриц A, B, C, D и E. Вес строки или столбца матрицы определяется количеством ненулевых элементов в строке или столбце. Вес строки (row weight) означает количество ненулевых элементов в строке, а вес столбца (column weight) означает количество ненулевых элементов в столбце. Следующее показано на базовом графе 200 на фиг. 2:

[0063] Подматрица A является матрицей строк mA и столбцов nA, а размер подматрицы A равен mA × nA. Каждый столбец соответствует Z системным битам в коде LDPC, а системный бит иногда упоминается как информационный бит.

[0064] Подматрица B является матрицей из строк mA и столбцов mA, а размер подматрицы B равен mA × mA. Каждый столбец соответствует Z битам четности в коде LDPC. Подматрица B включает в себя подматрицу B', имеющую двухдиагональную структуру, и столбец матрицы, вес столбца которого равен 3 (столбец c весом 3 для краткости). Столбец с весом 3 может быть расположен с левой стороны подматрицы B', как показано позицией 20a на фиг. 2. Подматрица B может дополнительно включать в себя один или несколько столбцов матрицы, вес столбца которых равен 1 (столбец с весом 1 для краткости). 20b и 20c на фиг. 2 - примеры возможных расположений столбцов с весом 1.

[0065] Обычно матрица, сгенерированная на основе подматриц A и B, может упоминаться как базовая матрица, которая может использоваться для поддержки кодирования с высокой кодовой скоростью.

[0066] Подматрица C является матрицей из всех нулей, а размер подматрицы C равен mA×mD.

[0067] Подматрица E является единичной матрицей, а размер подматрицы E равен mD×mD, где mD=m-mA.

[0068] Размер подматрицы D равен mD×(nA+mA), и обычно может использоваться для генерации битов четности с низкой кодовой скоростью.

[0069] Поскольку подматрицы C и E имеют относительно определенные структуры, структуры трех подматриц A, B и D являются одними из факторов, влияющих на производительность кодирования/декодирования кода LDPC.

[0070] Понятно, что вышеизложенное описывает структуру базового графа/базовой матрицы с точки зрения принципов. Разделение подматриц A, B, C, D и E просто для облегчения понимания с точки зрения принципов. Понятно, что разделение подматриц A, B, C, D и E не ограничивается вышеупомянутым способом разделения. В некоторой реализации, C является матрицей из всех нулей, E является единичной матрицей, и структуры C и E известны. Следовательно, матрица LDPC может быть представлена в упрощенной форме без использования всех подматриц A, B, C, D и E. Например, матрица LDPC может быть представлена в упрощенной форме подматрицами A, B и D, подматрицами A, B, C и D или подматрицами A, B, D и E. В другой реализации, поскольку подматрица B включает в себя один или несколько столбцов с весом 1, для одного или нескольких столбцов с весом 1 в подматрице B, структура относительно определена. Поэтому один или несколько столбцов с весом 1 не могут использоваться для представления матрицы LDPC. Например, подматрица A, некоторые столбцы в подматрице B и соответствующие столбцы в подматрице D могут использоваться для представления матрицы LDPC. Когда для кодирования используется матрица LDPC, имеющая подобную раптору структуру, возможная реализация состоит в том, что часть матрицы, включающая в себя подматрицы A и B, а именно базовую матрицу, может сначала использоваться в кодировании для получения одного или нескольких битов четности соответствующих подматрице B. Затем вся матрица LDPC используется в кодировании для получения одного или нескольких битов четности, соответствующих подматрице E. Поскольку подматрица B может включать в себя подматрицу B’ с двухдиагональной структурой и один или несколько столбцов с весом 1, во время кодирования сначала могут быть получены биты четности, соответствующие подматрице B’, и затем могут быть получены биты четности, соответствующие столбцам с весом 1.

[0071] Пример схемы кодирования приведен ниже. Предположим, что базовая матрица, включающая в себя подматрицы A и B, является Hcore. Последняя строка и последний столбец Hcore удаляются. Другими словами, столбец с весом 1 и строка, в которой расположен ненулевой элемент в столбце с весом 1, удаляются из Hcore для получения матрицы Hcore-dual. Часть битов четности в Hcore-dual представлена как He=[He1 He2], где He1 столбец с весом 3, а He2 имеет двухдиагональную структуру. Согласно определению матрицы LDPC, Hcore-dual⋅[S Pe]T=0, где S - входная последовательность и представлена вектором информационных битов, Pe - вектор битов четности, а [S Pe]T представляет собой транспонированную матрицу, образованную входной последовательностью S и Pe. Следовательно, биты четности, соответствующие Hcore-dual, могут быть сначала вычислены на основе входной последовательности S и Hcore-dual, где входная последовательность S включает в себя все информационные биты. Затем биты четности, соответствующие одному или нескольким столбцам с весом 1 в подматрице B, вычисляются на основе битов четности, соответствующих Hcore-dual, и входной последовательности S. В этом случае все биты четности, соответствующие подматрице B, могут быть получены. Биты четности, соответствующие подматрице E, получают путем кодирования подматрицы D на основе входной последовательности S и битов четности, соответствующих подматрице B, для получения всех информационных битов и всех битов четности. Эти биты составляют кодированную последовательность, а именно, кодовое слово LDPC.

[0072] Код LDPC может дополнительно включать в себя операцию сокращения (shortening) или операцию выкалывания в кодированной последовательности. Сокращенные биты или выколотые биты не отправляются.

[0073] Сокращение обычно выполняется, начиная с последнего бита из информационных битов, и может выполняться различными способами. Например, если количество сокращенных битов равно s0, последние s0 битов во входной последовательности S могут быть установлены как известные биты, например, равны 0, пустому значению или другому значению, чтобы получить входную последовательность S'. Затем входная последовательность S’ кодируется с использованием матрицы LDPC. В другом примере последние (s0 mod Z) биты во входной последовательности S могут альтернативно быть установлены как известные биты, например, установлены как 0, пустое значение или какое-либо другое значение, чтобы получить входную последовательность S’. Последние ⌊s0/Z⌋ столбцы в подматрице A удаляются для получения матрицы H’ LDPC, а входная последовательность S’ кодируется с использованием матрицы H’ LDPC; или последние ⌊s0/Z⌋ столбцы в подматрице A не участвуют в кодировании входной последовательности S’. После кодирования сокращенные биты не отправляются.

[0074] Выкалывание может быть выполнено на встроенном(ых) бите(ах) выкалывания или бите(ах) четности во входной последовательности. Выкалывание битов четности обычно выполняется, начиная с последнего бита в битах четности. В качестве альтернативы, выкалывание бита(ов) четности может выполняться в соответствии с предварительно установленным порядком выкалывания системы. Возможная реализация заключается в следующем: входная последовательность сначала кодируется, а затем последние p битов в битах четности выбирается/выбираются на основе количества p битов, которые должны быть выколоты, или p битов выбирается/выбираются на основе предварительно установленного порядка выкалывания системы. p битов не отправляется/ не отправляются. В другой возможной реализации альтернативно могут быть определены p столбцов в матрице, которые соответствуют выколотым битам, и p строк, в которых расположены ненулевые элементы в столбцах. Эти строки и столбцы не участвуют в кодировании, и соответствующие биты четности не генерируются.

[0075] Следует отметить, что реализация кодирования, описанная в данном документе, является просто примером, и другие реализации кодирования, известные специалисту в данной области техники, могут альтернативно использоваться на основе базового графа и/или базовой матрицы, предоставленных в вариантах осуществления этой заявки. В данной заявке это однозначно не ограничено. Декодирование в этой заявке может выполняться множеством способов декодирования, например, может использоваться способ декодирования с минимальной суммой (MS) или способ декодирования с доверительным распространением. Способ декодирования MS иногда упоминается как способ декодирования MS заливки (Flood MS). Например, входная последовательность инициализируется, а затем выполняется обработка итерации. Обнаружение жесткого решения выполняется после итерации, и выполняется проверка результата жесткого решения. Если результат декодирования удовлетворяет проверочному уравнению, декодирование завершается успешно, итерация заканчивается, и результат решения выводится. Если результат декодирования не удовлетворяет проверочному уравнению, обработка итерации выполняется снова в пределах максимального количества итераций. Если проверка все еще не проходит, когда достигнуто максимальное количество итераций, декодирование завершается неудачно. Принцип MS декодирования понятен специалисту в данной области техники, и подробности здесь не описаны.

[0076] Следует отметить, что способ декодирования, описанный здесь, является просто примером, и другие способы декодирования, известные специалисту в данной области техники, могут альтернативно использоваться на основе базового графа и/или базовой матрицы, предоставленной в этой заявке. Способ декодирования не ограничен в этой заявке.

[0077] Кодовое слово LDPC получается в зависимости от конструкции базового графа или базовой матрицы. Например, верхний предел производительности кода LDPC может быть определен путем выполнения эволюции плотности на базовом графе или базовой матрице. Минимальный уровень ошибки кода LDPC определяется на основе значения сдвига в базовой матрице. Эффективность кодирования или декодирования может быть улучшена, а минимальный уровень ошибок может быть уменьшен путем правильного проектирования базового графа или базовой матрицы. В системах беспроводной связи длина кода является гибкой, например, 2560 бит или 38400 бит. Фиг. 3a показывает пример базового графа для кода LDPC. Фиг. с 3b-1 по 3b-8 показывают примеры базовых матриц, соответствующих базовому графу на фиг. 3a. Базовые матрицы могут удовлетворять требованиям производительности множества длин блоков. Для простоты описания и понимания индексы столбцов и индексы строк соответственно показаны на самой верхней стороне и самой левой стороне на 3а и фиг. с 3b-1 по 3b-8.

[0078] Фиг. 4 - схематическая диаграмма производительности кода LDPC, показанного на фиг. 3a. На диаграмме производительности, показанной на фиг. 4, показаны кривые производительности кодирования с использованием любой из матриц, показанных на фиг. с 3b-1 до 3b-8. Горизонтальная координата представляет длину последовательности информационных битов в единицах битов, а вертикальная координата представляет собой отношение сигнал/шум (Es/N0) для символа, требуемого для достижения соответствующей частоты блочных ошибок (BLER). Две линии каждой кодовой скорости соответствуют двум BLER 0,01 и 0,0001. Для той же кодовой скорости 0,01 соответствует верхней кривой, а 0,0001 соответствует нижней кривой. Если кривые гладкие, это указывает на то, что матрица имеет относительно высокую производительность в случаях различных длин блока.

[0079] Фиг. 3a показывает пример базового графа кода LDPC. На базовом графе фиг. 3а, числа от 0 до 51 в самой верхней строке являются индексами столбцов и соответствуют столбцам от 0 до столбца 51 базового графа соответственно. Числа от 0 до 41 в крайнем левом столбце являются индексами строк и соответствуют от 0 до 41 строкам основного графа соответственно. То есть базовый граф имеет размер из 42 строк и 52 столбца.

[0080] В реализации комбинация подматрицы A и подматрицы B может рассматриваться как базовая матрица базового графа для кода LDPC, а базовая матрица может использоваться для кодирования с высокой кодовой скоростью. Как показано на фиг. 3a, матрица из 7 строк и 17 столбцов в верхнем углу базового графа может рассматриваться как базовая матрица базового графа. Базовая матрица включает в себя подматрицу A и подматрицу B. Подматрица A представляет собой матрицу из 7 строк и 10 столбцов и состоит из строки 0 - строки 6 и столбца 0 - столбца 9 базовой матрицы на фиг. 3a. Подматрица B представляет собой матрицу из 7 строк и 7 столбцов и состоит из строки 0 - строки 6 и столбца 10 - столбца 16 базовой матрицы на фиг. 3a.

[0081] В другой реализации матрица состоит из 7 строк и 14 столбцов, или матрица, состоящая из 7 строк и 15 столбцов, или матрица, состоящая из 7 строк и 16 столбцов, в верхнем левом углу базового графа, показанного на фиг. 3а, может рассматриваться как основная часть. Другими словами, в базовом графе, показанном на фиг. 3a, матрица, состоящая из строки 0 - строки 6 и столбца 0 - столбца 13, или матрица, состоящая из строки 0 - строки 6 и столбца 0 - столбца 14, или матрица, состоящая из строки 0 - строки 6 и столбца 0 - столбца 15, может рассматриваться как основная часть. Соответственно, часть в любой из матриц, показанных на фиг. с 3b-1 по 3b-8, которая соответствует основной части на базовом графе на фиг. 3a альтернативно может рассматриваться как основная часть.

[0082] В реализации подматрица A может включать в себя один или несколько встроенных выколотых столбцов. Например, подматрица A может включать в себя два встроенных выколотых столбца. В этом случае после выкалывания скорость кодирования, которая может поддерживаться базовой матрицей, составляет 2/3. Подматрица B может включать в себя один столбец с весом 1. Конкретнее, вес столбца первого столбца в подматрице B равен 3 (столбец 10 в базовой матрице). Вес столбца второго столбца в подматрице B равен 5 (столбец 11 в базовой матрице). Со второго столбца до четвертого столбца (от столбца 11 до столбца 13 в базовой матрице) и со строки 0 до строки 3 в подматрице B имеют двухдиагональную структуру, где веса столбцов третьего столбца и четвертого столбца (столбец 12 и столбец 13 в базовой матрице) равны 2. Подматрица B дополнительно включает в себя три столбца с весом 1 (столбцы с 14 по 16 в базовой матрице).

[0083] В реализации подматрица A может соответствовать системным битам, иногда также упоминается как информационные биты и имеет размер mA строк и 10 столбцов, где mA=5. Подматрица A состоит из элементов в строке от 0 до строки 4 и от столбца 0 до столбца 9 на базовом графе 30a на фиг. 3a.

[0084] В реализации подматрица B может соответствовать битам четности и иметь размер mA строк и mA столбцов. Подматрица B состоит из элементов в строке от 0 до строки 6 и от столбца 10 до столбца 16 на базовом графе 30a на фиг. 3a.

[0085] Чтобы получить гибкую кодовую скорость, подматрица C, подматрица D и подматрица E соответствующих размеров могут быть добавлены на основе базовой матрицы, чтобы получить разные кодовые скорости. Поскольку подматрица C является нулевой матрицей, подматрица E является единичной матрицей, а размеры подматриц в основном определяются на основе кодовых скоростей, структуры являются относительно фиксированными. На производительность кодирования/декодирования в основном влияют базовая матрица и подматрица D. Строки и столбцы добавляются на основе базовой матрицы, чтобы сформировать соответствующие части C, D и E, тем самым получая различные кодовые скорости.

[0086] Количество mD столбцов в подматрице D является суммой количеств столбцов в подматрице A и подматрице B. Количество строк в подматрице D главным образом связано с кодовой скоростью. Используя базовый граф 30a на фиг. 3a, например, подматрица D имеет 17 столбцов. Если скорость кодирования, поддерживаемая кодом LDPC, равна Rm, базовый граф или базовая матрица для кода LDPC имеет m строк и n столбцов, где n=nA/Rm+p, m=n-nA=nA/Rm+p-nA, а p - количество встроенных выколотых столбцов. Скорость кодирования, поддерживаемая кодом LDPC, может быть получена на основе формулы. Если самая низкая скорость кодирования равна Rm=1/3, а количество p встроенных выколотых столбцов равно 2, в примере базового графа 30a на фиг. 3a, например, n=52, m=42 и количество mD строк в подматрице D может составлять до m–mA=42–7=35, так что 0≤mD≤35.

[0087] Используя базовый граф 30a на фиг. 3a в качестве примера, подматрица D может включать в себя mD строк в строке с 7 по 41.

[0088] В этой заявке, если в каждом столбце имеется не более одного ненулевого элемента для двух смежных строк в базовом графе, эти две строки являются ортогональными. В других столбцах, отличающихся от некоторых столбцов для двух смежных строк в базовом графе, если в каждом столбце других столбцов для двух смежных строк содержится не более одного ненулевого элемента, две соседние строки являются квазиортогональными. Например, для двух смежных строк в каждом столбце, отличном от встроенных выколотых столбцов, если имеется только один ненулевой элемент, можно считать, что две смежные строки являются квазиортогональными.

[0089] Строка 7 - строка 41 на базовом графе 30a на фиг. 3a, могут включать в себя множество строк в квазиортогональной структуре и по меньшей мере две строки в ортогональной структуре. Например, строка 32 и строка 33 на базовом графе 30a на фиг. 3а являются ортогональными, строка 34 и строка 35 ортогональны, и строки 36, 37 и 38 являются ортогональными. Для любых двух смежных строк в других столбцах, отличных от встроенного выколотого столбца, если в каждом столбце имеется не более одного ненулевого элемента, две смежные строки удовлетворяют квазиортогональной структуре. Если включены встроенные выколотые столбцы, то в любом из столбцов имеется не более одного ненулевого элемента, две соседние строки удовлетворяют ортогональной структуре.

[0090] Если mD=15, подматрица D в базовом графе кода LDPC имеет 15 строк и 17 столбцов и может быть матрицей, состоящей из строки 7 - строки 21 и столбца 0 - столбца 16 в базовом графе 30a на фиг. 3a. Соответствующая скорость кодирования, поддерживаемая кодом LDPC, может быть получена на основе вышеупомянутой формулы вычисления.

[0091] Подматрица E является единичной матрицей из 15 строк и 15 столбцов, а подматрица C является матрицей из всех нулей из 7 строк и 15 столбцов.

[0092] Если mD=19, подматрица D в базовом графе кода LDPC имеет 19 строк и 17 столбцов и может быть матрицей, состоящей из строки 7 - строки 25 и столбца 0 - столбца 16 в базовом графе 30a на фиг. 3a. Соответствующая скорость кодирования, поддерживаемая кодом LDPC, может быть получена на основе вышеупомянутой формулы вычисления. При этой кодовой скорости базовый граф кода LDPC соответствует матрице, состоящей из строки 0 - строки 25 и столбца 0 - столбца 16 в базовом графе 30a на фиг. 3a. Подматрица E является единичной матрицей из 16 строк и 16 столбцов, а подматрица C является матрицей из всех нулей из 7 строк и 16 столбцов. То же самое верно, если mD - другое значение, детали не описаны.

[0093] В некотором исполнении перестановка строк/столбцов может выполняться на базовом графе и/или базовой матрице. Перестановка строк/столбцов может быть перестановкой строк, перестановкой столбцов или перестановкой строк и перестановок столбцов. Перестановка строк/столбцов не изменяет вес строки или вес столбца, а также не меняет количество ненулевых элементов. Следовательно, базовый граф и/или базовая матрица, полученные путем выполнения перестановки строк/столбцов, оказывает/оказывают ограниченное влияние на производительность системы. В целом, влияние на производительность системы из-за перестановки строк/столбцов является приемлемым и находится в пределах допуска. Например, производительность снижается в пределах допустимого диапазона в некоторых сценариях или в некоторых диапазонах, в то время как в некоторых сценариях или в некоторых диапазонах производительность улучшается до некоторой степени, и общая производительность не сильно изменяется.

[0094] Например, строку 34 и строку 36 базового графа 30a на фиг. 3a, можно переставлять, а столбец 44 и столбец 45 можно менять местами. В другом примере подматрица D включает в себя mD строк в матрице F. Перестановка строк может не выполняться в mD строках, или перестановка строк может выполняться в одной или нескольких из mD строк. Подматрица E по-прежнему имеет диагональную структуру, и на подматрице E не выполняется перестановка строк или перестановка столбцов. Например, перестановка строк выполняется в строке 27 и строке 29 в матрице F. Подматрица D включает в себя mD строк в матрице F, и подматрица E все еще имеют диагональную структуру. Понятно, что если базовый граф или базовая матрица включает в себя подматрицу D, то когда перестановка столбов выполняется на базовой матрице, перестановка столбцов должна выполняться соответственно на подматрице D.

[0095] Матрицы, показанные на фиг. с 3b-1 по 3b-8 являются примерами базовых матриц, соответствующих базовому графу 30a на фиг. 3a. Расположение ненулевого элемента в строке i и столбце j на базовом графе 30a на фиг. 3a является таким же, как в матрицах, показанных на фиг. с 3b-1 по 3b-8. Значение сдвига ненулевого элемента равно Vi,j. Нулевой элемент представлен как значение -1 или ноль в базовой матрице. Соответствующая часть подматрицы D в базовой матрице может включать в себя mD строк в строке с 7 по 41 в любой из базовых матриц, и значения mD могут выбираться на основе разных кодовых скоростей. Можно понять, что если базовый граф является матрицей, полученной путем выполнения преобразования строки/столбца на базовом графе 30a на фиг. 3a, соответственно, базовая матрица является соответствующей матрицей, полученной посредством выполнения преобразования строки/столбца.

[0096] В возможном исполнении, поскольку структуры подматриц C и E относительно фиксированы, базовый граф/базовая матрица кода LDPC может быть представлен с использованием подматриц A, B и D, то есть строк от строки 0 до строки 41 и столбцов от столбца 0 до столбца 16 в любой матрице, показанной на фиг. 3а или фиг. с 3b-1 по 3b-8.

[0097] В возможном исполнении, поскольку столбцы с 14 по 51 имеют относительно определенную структуру, базовый граф/базовая матрица кода LDPC может быть представлена в упрощенной форме с использованием строки 0 - строки 41 и столбца 0 - столбца 13 в любой из матриц, показанных на фиг. 3а или фиг. с 3b-1 по 3b-8.

[0098] В возможном исполнении базовый граф/базовая матрица кода LDPC может быть представлена с использованием строки от 0 до строки 41 и от столбца 0 до столбца 13, а также от некоторого из столбца 14 до столбца 51 в любой матрице, показанной на фиг. 3а или фиг. с 3b-1 по 3b-8. Например, базовый граф/базовая матрица кода LDPC может быть представлена с использованием строки 0 - строки 41 и столбца 0 - столбца 15 или строки 0 - строки 41 и столбца 0 - столбца 14 в любой из матриц, показанных на фиг. , 3а или фиг. с 3b-1 по 3b-8.

[0099] В возможном исполнении базовая матрица кода LDPC может включать в себя строки от 0 до строки 6 и от столбца 0 до столбца 16 в любой из матриц, показанных на фиг. с 3b-1 по 3b-8. В этом случае матрица, состоящая из строки 0 - строки 6 и столбца 0 - столбца 16 в любой из матриц, показанных на фиг. с 3b-1 по 3b-8 может использоваться в качестве основной части базовой матрицы. В этом исполнении структура другой части, например, подматрицы C, D и E базовой матрицы кода LDPC, не ограничена. Например, любая структура, показанная на фиг. от 3b-1 до 3b-8 или другая структура матрицы может использоваться.

[0100] В другом возможном исполнении базовая матрица кода LDPC может включать в себя матрицу, состоящую из строки от 0 до строки m-1 и от столбца 0 до столбца n-1 в любой из матриц, показанных на фиг. с 3b-1 по 3b-8, где 7≤m≤42, m - целое число, 18≤n≤52, и n - целое число.

[0101] В этой конструкции структура другой части базовой матрицы кода LDPC не ограничена. Например, любая структура, показанная на фиг. с 3b-1 до 3b-8 или другая структура матрицы может использоваться.

[0102] В еще одном возможном исполнении базовая матрица кода LDPC может включать в себя строки от 0 до строки 6 и некоторые столбцы от столбца 0 до столбца 16 в любой из матриц с 3b-1 по 3b-8, показанных на фиг. с 3b-1 по 3b-8. Например, основная часть (строка 0 - строка 6 и столбец 0 - столбец 16) матриц, показанных на фиг. с 3b-1 по 3b-8, могут быть сокращены и/или выколоты. В реализации базовая матрица кода LDPC может не включать в себя столбец (столбцы), соответствующий сокращенному и/или выколотому биту (битам).

[0103] В этом исполнении другая часть базовой матрицы кода LDPC не ограничена. Например, структура, показанная на фиг. с 3b-1 по 3b-8 может использоваться, могут использоваться и другие структуры.

[0104] В еще одном возможном исполнении базовая матрица кода LDPC может включать в себя матрицу, состоящую из строк от 0 до строки m-1 и некоторых столбцов из столбца 0 до столбца n-1 в любой из матриц, показанных на фиг. с 3b-1 по 3b-8, где 7≤m≤42, m - целое число, 18≤n≤52, а n - целое число. Например, операция сокращения и/или операция выкалывания может выполняться в строке от 0 до строки m-1 и от столбца 0 до столбца n-1 любой из матриц, показанных на фиг. с 3b-1 по 3b-8. В реализации базовая матрица кода LDPC может не включать в себя столбец (столбцы), соответствующий укороченному и/или выколотому биту (битам). В этом исполнении другая часть базовой матрицы кода LDPC не ограничена. Например, структура, показанная на любой из фиг. с 3b-1 по 3b-8 может использоваться, могут использоваться и другие структуры.

[0105] В реализации операция сокращения может быть сокращением информационных битов. Используя любую из матриц, показанных, например, на фиг. с 3b-1 по 3b-8, один или несколько столбцов из столбца 0 - столбца 9 сокращены. В этом случае базовая матрица кода LDPC может не включать в себя один или несколько сокращенных столбцов в любой из матриц, показанных на фиг. с 3b-1 по 3b-8. Например, если столбец 9 сокращен, базовая матрица кода LDPC может включать в себя столбцы от 0 до столбца 8 и от столбца 10 до столбца 16 в любой из матриц на фиг. с 3b-1 по 3b-8.

[0106] В другой реализации операция выкалывания может быть выкалыванием битов четности. Используя любую из матриц, показанных, например, на фиг. с 3b-1 по 3b-8, один или несколько столбцов от столбца 10 до столбца 16 выколоты. В этом случае базовая матрица кода LDPC может не включать в себя один или несколько выколотых столбцов в любой из матриц, показанных на фиг. с 3b-1 по 3b-8. Например, если столбец 16 выколот, базовая матрица кода LDPC может включать в себя столбцы с 0 по 15 в любой из матриц, показанных на фиг. с 3b-1 по 3b-8.

[0107] Чтобы поддерживать разные длины блоков, код LDPC требует разных коэффициентов Z подъема. В возможном исполнении могут использоваться разные базовые матрицы для разных коэффициентов подъема, чтобы достичь относительно высокой производительности. Например, коэффициент подъема составляет Z=a×2j, где 0≤j<7 и a∈{2,3,5,7,9,11,13,15}. В таблице 1 показан возможный поддерживаемый набор коэффициентов подъема { 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 18, 20, 22, 24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}. Каждая из ячеек, за исключением самой верхней строки и самого левого столбца, представляет значение Z, соответствующее значениям соответствующих a и j. Например, для столбца a=2 и строки j=1, Z равно 4. Для другого примера, для a=11 и j=3, Z равно 88. По аналогии подробности не описаны.

Таблица 1

[0108] Можно понять, что в таблице 1 просто показана форма описания набора коэффициентов подъема. Реальная реализация продукта не ограничена формой в Таблице 1, и факторы подъема могут иметь другую форму представления.

[0109] Например, каждое значение соответствует набору коэффициента подъема. Набор коэффициентов подъема может быть идентифицирован с помощью индекса набора. Например, таблица 1’ показывает другую форму представления набора коэффициентов подъема.

Таблица 1’

( Set of lifting sizes)

[0110] Набор коэффициентов подъема, поддерживаемый базовым графом, может включать в себя все коэффициенты подъема или некоторые коэффициенты подъема в Таблице 1 или Таблице 1’. Например, набор коэффициентов подъема может быть {24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}. Другими словами, Z больше или равно 24. В другом примере набор коэффициентов подъема может представлять собой набор объединений из {24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384} и один или несколько из {2, 3, 4, 5, 6, 7, 8 , 9, 10, 11, 12, 13, 14, 15, 16, 18, 20, 22}. Следует отметить, что это просто пример. Набор коэффициентов подъема, поддерживаемый базовым графом, может быть разделен на различные поднаборы на основе значения a. Например, если a=2, поднабор коэффициентов Z подъема может включать в себя один или несколько из {2, 4, 8, 16, 32, 64, 128, 256}; для другого примера, если a=3, подмножество коэффициентов Z подъема может включать в себя один или несколько из {3, 6, 12, 24, 48, 96, 192, 384}; и так далее.

[0111] Набор коэффициентов подъема, поддерживаемый базовым графом, может быть разделен на основе различных значений a, и определена соответствующая базовая матрица.

[0112] Если a=2 или значение коэффициента Z подъема равно одному из {2, 4, 8, 16, 32, 64, 128, 256}, базовая матрица может включать в себя строки от строки 0 до строки 6 и от столбца 0 до столбца 16 в любой из матриц, показанных на фиг. с 3b-1 по 3b-8; или базовая матрица включает в себя строки от строки 0 до строки m-1 и от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-1, где 7≤m≤42, m представляет собой целое число, 17≤n≤52 и n представляет собой целое число; или базовая матрица включает в себя строки от 0 до строки m-1 и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-1, где 7≤m≤42, m является целым числом, 17≤n≤52, а n является целым числом.

[0113] Если a=3 или значение коэффициента Z подъема равно одному из {3, 6, 12, 24, 48, 96, 192, 384}, базовая матрица может включать в себя строки от 0 до строки 6 и от столбца 0 до столбца 16 в матрице, показанной на фиг. 3b-2; или базовая матрица включает в себя строки от 0 до строки m-1 и от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-2, где 7≤m≤42, m представляет собой целое число, 17≤n≤52 и n представляет собой целое число; или базовая матрица включает в себя строки от 0 до строки m-1 и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-2, где 7≤m≤42, m является целым числом, 17≤n≤52, а n является целым числом.

[0114] Например, базовая матрица PCM включает в себя строки от 0 до строки 41 и столбцы от 0 до столбца 13, или от столбца 0 до столбца 14, или от столбца 0 до столбца 15 на фиг. 3b-2.

[0115] Если a=5 или значение коэффициента Z подъема равно одному из {5, 10, 20, 40, 80, 160, 320}, базовая матрица может включать в себя строки от 0 до 6 и столбцы от 0 до 16 в матрице, показанной на фиг. 3b-3; или базовая матрица включает в себя строки от 0 до строки m-1 и столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-3, где 7≤m≤42, m представляет собой целое число, 17≤n≤52 и n представляет собой целое число; или базовая матрица включает в себя строки от 0 до строки m-1 и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-3, где 7≤m≤42, m - целое число, 17≤n≤52, и n - целое число.

[0116] Если a=7 или значение коэффициента Z подъема равно одному из {7, 14, 28, 56, 112, 224}, базовая матрица может включать в себя строки от 0 до строки 6 и от столбца 0 до столбца 16 в матрице, показанной на фиг. 3b-4; или базовая матрица включает в себя строки от 0 до строки m-1 и от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-4, где 7≤m≤42, m - целое число, 17≤n≤52, и n - целое число; или базовая матрица включает в себя строки от 0 до строки m-1 и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-4, где 7≤m≤42, m - целое число, 17≤n≤52, и n - целое число.

[0117] Если a=9 или значение коэффициента Z подъема равно одному из {9, 18, 36, 72, 144, 288}, базовая матрица может включать в себя строки от 0 до 6 и столбцы от 0 до 16 в матрице, показанной на фиг. 3b-5; или базовая матрица включает в себя строки от 0 до строки m-1 и от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-5, где 7≤m≤42, m - целое число, 17≤n≤52, а n - целое число; или базовая матрица включает в себя строки от 0 до строки m-1 и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-5, где 7≤m≤42, m - целое число, 17≤n≤52 и n - целое число.

[0118] Если a=11 или значение коэффициента Z подъема равно одному из {11, 22, 44, 88, 176, 352}, базовая матрица может включать в себя строки от 0 до строки 6 и от столбца 0 до столбца 16 в матрице, показанной в фиг. 3b-6; или базовая матрица включает в себя строки от 0 до строки m-1 и от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-6, где 7≤m≤42, m - целое число, 17≤n≤52 и n - целое число; или базовая матрица включает в себя строки от 0 до строки m-1 и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-6, где 7≤m≤42, m - целое число, 17≤n≤52, и n - целое число.

[0119] Если a=13 или значение коэффициента Z подъема равно одному из {13, 26, 52, 104, 208}, базовая матрица может включать в себя строки с 0 по 6 и столбцы с 0 по 16 в матрице, показанной на фиг. 3b-7; или базовая матрица включает в себя строки от 0 до строки m-1 и от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-7, где 7≤m≤42, m - целое число, 17≤n≤52, а n - целое число; или базовая матрица включает в себя строки от 0 до строки m-1 и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-7, где 7≤m≤42, m - целое число, 17≤n≤52 и n - целое число.

[0120] Если a=15 или значение коэффициента Z подъема равно одному из {15, 30, 60, 120, 240}, базовая матрица может включать в себя строки от 0 до строки 6 и от столбца 0 до столбца 16 в матрице 3b-8; или базовая матрица включает в себя строки от 0 до строки m-1 и от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-8, где 7≤m≤42, m - целое число, 17≤n≤52 и n - целое число; или базовая матрица включает в себя и некоторые столбцы от столбца 0 до столбца n-1 в матрице, показанной на фиг. 3b-8, где 7≤m≤42, m - целое число, 17≤n≤52, а n - целое число.

[0121] Необязательно, для базовой матрицы кода LDPC значения сдвига ненулевых элементов в одном или нескольких столбцах могут быть увеличены или уменьшены на значение Offsets компенсации, без существенного влияния на производительность системы. Значения компенсации ненулевых элементов в разных столбцах могут быть одинаковыми или разными. Например, чтобы компенсировать один или несколько столбцов в матрице, значения компенсации для разных столбцов могут быть одинаковыми или разными. В данной заявке это однозначно не ограничено.

[0122] Незначительное влияние на производительность системы означает, что влияние на производительность системы является приемлемым и находится в допустимом диапазоне. Например, производительность снижается в пределах допустимого диапазона в некоторых сценариях или в некоторых диапазонах. Однако в некоторых сценариях или в некоторых диапазонах производительность улучшается до некоторой степени. Общая производительность не сильно страдает.

[0123] Например, значение Offsets компенсации добавляется или вычитается из каждого значения сдвига, большего или равного 0, в столбце s в любой из матриц, показанных на фиг. с 3b-1 по 3b-8, для получения скомпенсированной матрицы Hs, где Offsets - целое число, большее или равное 0, а s - целое число, большее или равное 0 и меньшее, чем 11. Значения Offsets компенсации для одного или нескольких столбцов могут быть одинаковыми или разными.

[0124] На диаграмме производительности, показанной на фиг. 4, на основе кривых производительности матриц кодирования, показанных на фиг. 3b-1 и фиг.3b-2 горизонтальная координата представляет длину последовательности информационных битов, а единица длины - бит, а вертикальная координата - отношение сигнал/шум символа (Es/N0), необходимое для достижения соответствующей BLER. Две линии каждой кодовой скорости соответствуют двум случаям BLER 0,01 и 0,0001. При той же кодовой скорости, 0,01 соответствует верхней кривой, а 0,0001 соответствует нижней кривой. Если кривые гладкие, это указывает на то, что матрица имеет относительно высокую производительность в случаях различных дин блоков.

[0125] Фиг. с 1 по фиг. 3а и фиг. с 3b-1 по 3b-8 показывают структуры базового графа и базовой матрицы, которые связаны с кодом LDPC. Для достаточного описания исполнений базового графа и/или базовой матрицы в реализациях настоящей заявки структура базовой матрицы может быть представлена в другой форме, которая может быть идентифицирована системой, например, в табличной форме.

[0126] В исполнении базовый граф, показанный позицией 10а на фиг. 1 представляет собой матрицу из 7 строк и 10 столбцов, и соответствующие параметры могут быть представлены в таблице 2.

Таблица 2

(индекс строки)

(степень строки/вес строки)

[0127] Понятно, что поскольку столбцы с 14 по 16 в базовом графе 10a являются столбцами, вес столбца которых равен 1, и местоположения столбцов относительно фиксированы или легко определяются, местоположения ненулевых элементов в столбцах 14 - 16 могут не быть записаны в таблице 2, но записаны в другой форме.

[0128] В одном исполнении с использованием базовых матриц, показанных, качестве примеров, на фиг. с 3b-1 по 3b-8, параметры, относящиеся к базовым матрицам, могут быть соответственно представлены в таблицах с 3b-1 по таблицу 3b-8.

Таблица 3b-1

Таблица 3b-2

Таблица 3b-3

Таблица 3b-4

Таблица 3b-5

Таблица 3b-6

Таблица 3b-7

Таблица 3b-8

[0129] Можно понять, что фиг. 3а, фиг. с 3b-1 по 3b-8, таблица 2 и таблицы с 3b-1 по 3b-8 предназначены для того, чтобы помочь понять исполнения базовых графов и базовых матриц, и их формы представления не ограничиваются этим. Другие возможные варианты также могут быть включены. Например, для вариаций Таблицы 3b-1 и Таблицы 3b-3 по Таблицу 3b-8 можно сослаться на форму Таблицы 3b-2’. Информация об элементах в столбцах, таких как столбцы с 14 по 51, которые имеют относительно определенные структуры и которые соответствуют значению 0 сдвига, может выборочно включаться в таблицу или не включаться в таблицу для экономии места для хранения.

[0130] В исполнении для части, имеющей относительно определенную структуру в базовом графе или базовой матрице, местоположения ненулевых элементов базового графа или базовой матрицы могут быть получены посредством вычисления на основе местоположения строки/столбца, и местоположения ненулевых элементов могут не быть сохранены. Используя фиг. 3b-2 и Таблицу 3b-2 в качестве примера, местоположения столбца 14 - столбца 51 в матрице, показанной на фиг. 3b-2, являются относительно определенными, а значения сдвига Vi,j все равны 0. Расположение ненулевых элементов может быть вычислено на основе известных ненулевых элементов. В Таблице 3b-2 информация о столбцах с 14 по 51 может быть не включена или информация о некоторых столбцах с 14 по 51 может быть не включена. Например, ненулевые элементы от столбца 16 до столбца 51 и соответствующие значения сдвига ненулевых элементов могут не быть включены. Например, матрица, показанная на фиг. 3b-2 альтернативно может быть представлена в таблице 3b-2’.

Таблица 3b-2’

[0131] Для другого примера, используя фиг. 3b-2, в качестве примера, значения Vi,j сдвига в строке 0 также равны 0, и информация о строке 0 может не сохраняться, но получается посредством вычисления.

[0132] В реализации параметр «вес строки» в таблице 2, таблицах с 3b-1 по 3b-8 и в таблице 3b-2’ альтернативно может быть опущен. Количество ненулевых элементов в строке может быть изучено на основе столбца, в котором расположены ненулевые элементы в строке. Таким образом, вес строки также изучен.

[0133] В реализации значения параметров в «столбец, в котором расположен ненулевой элемент» в таблице 2, таблицах с 3b-1 по таблицу 3b-8 и в таблице 3b-2’, могут не быть расположены в порядке возрастания, при условии, что значения параметров индексируются для столбцов, в которых расположены ненулевые элементы. Кроме того, значения параметров в «значение сдвига ненулевого элемента» в Таблице 2 и Таблице 3b-1 - Таблице 3b-8 могут не располагаться в порядке столбцов, при условии, что значения параметров в «значение сдвига ненулевого элемента» находятся в взаимно-однозначном соответствии со значениями параметров в «индекс столбца ненулевого элемента».

[0134] В реализации вышеупомянутые разные базовые матрицы могут быть объединены в одну или несколько таблиц для представления. Например, ненулевые элементы, соответствующие разным базовым матрицам, имеют одинаковое местоположение и одинаковый номер строки, но имеют разные значения Vi,j сдвига. Следовательно, множество базовых матриц может быть представлено с использованием одной таблицы путем перечисления номеров строк, индекса столбцов, в которых расположены ненулевые элементы, и значений сдвига множества групп ненулевых элементов. Например, значения сдвига двух групп ненулевых элементов могут быть перечислены в разных столбцах и указаны с использованием индексов.

[0135] В реализации базовый граф может использоваться для указания местоположения ненулевых элементов. Параметр «индекс столбца ненулевого элемента» в вышеприведенных таблицах может альтернативно быть необязательным.

[0136] В реализации матрицы, показанные на фиг. 3а и фиг. с 3b-1 по 3b-8 альтернативно могут быть представлены с использованием номеров столбцов (индексов столбцов), строк, в которых расположены ненулевые элементы, и значений сдвига ненулевых элементов. Необязательно вес столбца может быть включен.

[0137] В другой реализации 1 и 0 в каждой строке или каждом столбце в базовом графе или базовой матрице могут рассматриваться как двоичные числа, и сохранение двоичных чисел в десятичных или шестнадцатеричных числах может экономить место для хранения. Используя любой вышеприведенный базовый граф или базовую матрицу в качестве примера, местоположения ненулевых элементов в первых 14 столбцах или первых 17 столбцах могут быть сохранены с использованием шестнадцатеричных чисел. Например, если первые 14 столбцов в строке 0 являются 11110010011100, местоположения ненулевых элементов в строке 0 могут быть записаны как 0xF2 и 0x70. То есть каждые 8 столбцов образуют шестнадцатеричное число. Для последних двух столбцов соответствующие шестнадцатеричные числа могут быть получены путем заполнения нулей, чтобы получить целое число, кратное 8 битам. Альтернативно, соответствующее шестнадцатеричное число может быть получено путем заполнения нулей в первых двух столбцах для достижения целого числа, кратного 8 битам. То же самое относится и к другим строкам, и подробности здесь не описаны.

[0138] Фиг. 5 показывает блок-схему процесса обработки данных. Процесс обработки данных может быть реализован с использованием аппаратуры связи. Аппаратура связи может быть базовой станцией, терминалом или другим объектом, таким как микросхема связи, или кодером/декодером и т.д.

[0139] Этап 501: получить входную последовательность. В реализации входная последовательность для кодирования может быть последовательностью информационных битов, заполненной последовательностью информационных битов или последовательностью, полученной путем добавления битовой последовательности CRC к последовательности информационных битов. Иногда последовательность информационных битов также упоминается как кодовый блок, например, может быть выходной последовательностью, полученной посредством выполнения сегментации кодового блока на транспортном блоке. В реализации входная последовательность для декодирования может быть последовательностью программных значений кода LDPC.

[0140] Этап 502: кодировать/декодировать входную последовательность на основе матрицы LDPC. Базовая матрица матрицы LDPC может быть любой базовой матрицей, показанной в предыдущих примерах.

[0141] В реализации матрица LDPC может быть получена на основе коэффициента Z подъема и базовой матрицы.

[0142] В реализации параметры, связанные с матрицей LDPC, могут быть сохранены. Параметры включают в себя одно или несколько из следующего:

(а) Параметры, используемые для получения любой базовой матрицы, перечисленной в предыдущих реализациях. Базовая матрица может быть получена на основе параметров. Например, параметры могут быть одним или несколькими из следующего: индекс строки, вес строки, индекс столбца, вес столбца; местоположения ненулевых элементов (например, индексы строк ненулевых элементов или индексы столбцов ненулевых элементов), значения сдвига в базовой матрице, значения сдвига ненулевых элементов и соответствующие местоположения ненулевых элементов, значение компенсации, коэффициент Z подъема, базовый граф, скорость кодирования и т.п;

(b) базовая матрица, которая является одной из любых базовых матриц, перечисленных в предыдущих реализациях;

(c) матрица Hs компенсации, полученная путем компенсации по меньшей мере одного столбца для любой базовой матрицы, перечисленной в предыдущих реализациях;

(d) матрица, полученная поднятием (расширением) базовой матрицы или поднятием из матрицы Hs компенсации базовой матрицы;

(e) базовая матрица, полученная путем выполнения преобразования строки/столбца в любой базовой матрице или матрице Hs компенсации базовой матрицы, перечисленной в предыдущих реализациях;

(f) матрица, полученная поднятием базовой матрицы преобразованной строки/столбца или матрицы Hs компенсации преобразованной строки/столбца упомянутой базовой матрицы; и

(g) базовая матрица, полученная путем выполнения операции сокращения или выкалывания в отношении любой базовой матрицы или матрицы Hs компенсации упомянутой базовой матрицы, перечисленной в предыдущих реализациях.

[0143] В возможной реализации кодирование/декодирование входной последовательности на основе матрицы проверки четности с низкой плотностью (LDPC) может выполняться в процессе кодирования/декодирования одним или несколькими из следующих способов:

i. получение базовой матрицы на основе некоторых или всех параметров, перечисленных в предшествующем пункте (а), и затем:

кодирование/декодирование информации на основе полученной базовой матрицы; или

выполнение преобразования строки/столбца в полученной базовой матрице и кодирование/декодирование информации на основе преобразованной строки/столбца базовой матрицы; или

кодирование/декодирование информации на основе матрицы Hs компенсации упомянутой полученной базовой матрицы; или

кодирование/декодирование информации на основе матрицы, которая получается путем выполнения преобразования строки/столбца в матрице Hs компенсации базовой матрицы. Альтернативно, кодирование/декодирование информации на основе базовой матрицы или матрицы Hs компенсации может дополнительно включать в себя: кодирование/декодирование информации на основе базовой матрицы, поднятой из базовой матрицы, или матрицы Hs компенсации упомянутой базовой матрицы; или

кодирование/декодирование информации на основе матрицы, полученной путем выполнения операции сокращения или выкалывания на базовой матрице или матрице Hs компенсации.

ii. кодирование/декодирование информации на основе матрицы сохраненной в соответствии с предшествующим элементом (b), (c), (d) или (e). Матрица может быть сохраненной базовой матрицей, матрицей Hs компенсации базовой матрицы, матрицей, полученной путем выполнения преобразования строки/столбца в базовой матрице, или матрицей, полученной путем выполнения преобразования строки/столбца в матрице Hs компенсации. Альтернативно, преобразование строки/столбца выполняется в сохраненной базовой матрице, и кодирование/декодирование выполняется на основе матрицы, полученной посредством выполнения преобразования строки/столбца. Здесь, необязательно, кодирование/декодирование на основе базовой матрицы или матрицы Hs компенсации может дополнительно включать в себя: выполнение кодирования/декодирования на основе матрицы расширения базовой матрицы или матрицы расширения матрицы Hs компенсации; или выполнение кодирования/декодирования на основе матрицы, полученной после выполнения операции сокращения или выкалывания на базовой матрице или матрице Hs компенсации.

iii. кодирование/декодирование информации основано на матрице, описанной в вышеизложенном (d), (f) или (g).

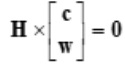

[0144] Этап 503: вывод закодированной/декодированной битовой последовательности. В схеме входная последовательность c = {c0, c1, c2, ..., cK-1} может быть закодирована для получения выходной последовательности d = {d0, d1, d2, ..., dN-1}, где K и N являются целыми числами больше 0. Выходная последовательность d включает в себя K0 битов во входной последовательности c и биты четности в последовательности w проверки четности, где K0 - целое число, и 0<K0≤K. Последовательность w четности и входная последовательность c удовлетворяют формуле

,

,

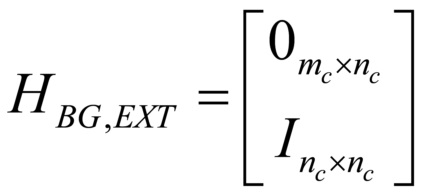

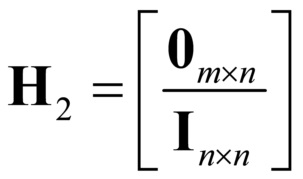

где cT=[c0,c1,c2, ..., cK-1]T - транспонированный вектор вектора, образованного битами во входной последовательности c, wT=[w0,w1,w2, ..., wN-K0-1]T - транспонированный вектор вектора, образованного битами в последовательности четности w; 0T является вектором столбца, а значения всех элементов в 0T равны 0; и H - матрица проверки четности с низкой плотностью (LDPC). Базовый граф H включает в себя HBG и HBG,EXT:

,

,

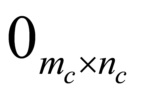

где  представляет собой матрицу из всех нулей размера mc × nc и

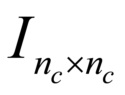

представляет собой матрицу из всех нулей размера mc × nc и  представляет единичную матрицу размера nc × nc; и HBG включает в себя столбцы, соответствующие Kb столбцам информационных битов в HBG2, и столбцы с 10 по 10+mA - 1 в HBG2, где количество столбцов в HBG2 равно 10+mA, 4≤mA≤7, где Kb∈ {6,8,9,10}. Для mc=7 и 0≤nc≤35 количество столбцов в HBG2 равно 17; или для mc=6 и 0≤nc≤36 количество столбцов в HBG2 равно 16; или для mc=5 и 0≤nc≤37 количество столбцов в HBG2 равно 15; или для mc=4 и 0≤nc≤38 количество столбцов в HBG2 равно 14.

представляет единичную матрицу размера nc × nc; и HBG включает в себя столбцы, соответствующие Kb столбцам информационных битов в HBG2, и столбцы с 10 по 10+mA - 1 в HBG2, где количество столбцов в HBG2 равно 10+mA, 4≤mA≤7, где Kb∈ {6,8,9,10}. Для mc=7 и 0≤nc≤35 количество столбцов в HBG2 равно 17; или для mc=6 и 0≤nc≤36 количество столбцов в HBG2 равно 16; или для mc=5 и 0≤nc≤37 количество столбцов в HBG2 равно 15; или для mc=4 и 0≤nc≤38 количество столбцов в HBG2 равно 14.

[0145] Фиг. 6 показывает блок-схему процесса обработки данных, который может быть применен к блоку (этапу) 502 на фиг. 5.

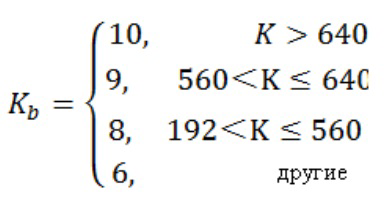

[0146] Этап 601: получить коэффициент Z подъема. В возможном исполнении заполнение может выполняться для последовательности информационных битов, чтобы получить входную последовательность. Длина входной последовательности K=Kb⋅Z, а Z=K/Kb. В другом возможном исполнении биты, которые должны быть выколоты или сокращены в последовательности информационных битов, могут быть заполнены. Другими словами, биты заполнения используются для замены битов, которые необходимо выколоть или сократить, чтобы после кодирования биты заполнения могли быть идентифицированы и не отправлены. Например, нулевое значение, значение 0, значение, согласованное в системе, или предварительно определенное значение могут использоваться в качестве значения бита заполнения. В исполнении биты, которые необходимо выкалывать, выкалываются без заполнения. Биты заполнения заполняются после последовательности информационных битов.

[0147] В реализации коэффициент Z подъема может быть определен на основе длины K входной последовательности. Например, минимум Z0, который соответствует Kb⋅Z0≥K, может быть определен из множества коэффициентов подъема в поддерживаемом наборе коэффициентов подъема и может использоваться как значение коэффициента Z подъема. В возможном исполнении Kb может быть количество столбцов информационных битов в базовой матрице кода LDPC. Для базового графа 30а на фиг. 3a количество столбцов информационных битов равно Kbmax=10. Предполагается, что набор коэффициентов подъема, поддерживаемый базовым графом 30a на фиг. 3а, следующий: {24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176 192, 208, 224, 240, 256, 288, 320, 352, 384}. Если длина входной последовательности равна K=529 бит, Z равен 26. Если длина входной последовательности K=5000 битов, Z равен 240. Следует отметить, что это просто пример в данном документе, который не ограничивается этим.

[0148] Для другого примера значение Kb может изменяться на значение K, но не превышает количество столбцов информационных битов в базовой матрице кода LDPC. Например, разные пороговые значения могут быть установлены для Кб.

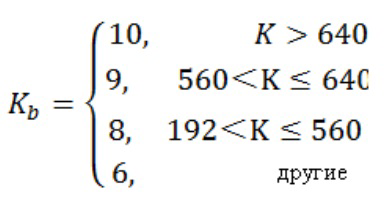

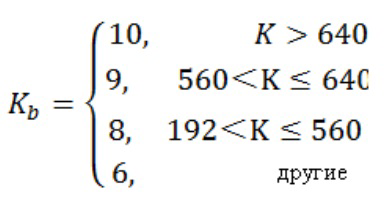

[0149] В исполнении следует отметить, что пороговые значения 640, 560 и 192 здесь являются просто примерами. В качестве альтернативы может быть задано другое значение в зависимости от требований к исполнению системы.

если (K>640), Kb=10;

или если (K>560), Kb=9;

или если (K>192), Kb=8;

или Kb=6; конец

[0150] Коэффициент Z подъема может быть определен аппаратурой связи на основе длины K входной последовательности или может быть получен аппаратурой связи от другого объекта (например, процессора).