Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся к области связи и, в частности, к способу обработки информации и устройству связи.

Уровень техники

Код с малой плотностью проверок на четность (low density parity check, LDPC) представляет собой тип линейного блочного кода, включающего в себя разреженную матрицу проверки на четность, и характеризуется гибкой структурой и низкой сложностью декодирования. Поскольку при декодировании LDPC кода используют частично параллельный алгоритм итеративного декодирования, LDPC код имеет более высокую производительность, чем обычный турбокод. LDPC код может быть использован в качестве кода с исправлением ошибок в системе связи для повышения надежности передачи канала и использования мощности. LDPC код может также широко применяться для космической связи, волоконно-оптической связи, персональной системы связи, ADSL, устройства магнитной записи и тому подобного. LDPC схема кода в настоящее время рассматривается как одна из схем канального кодирования в системах мобильной связи пятого поколения.

В практических применениях могут быть использованы LDPC матрицы, характеризующиеся различными специальными структурами. LDPC матрица Н, имеющая специальную структуру, может быть получена путем расширения LDPC базовой матрицы, имеющей квазициклическую (quasi cycle, QC) структуру.

Обычно длины кодируемых последовательностей информационных битов изменяются от десятков до сотен битов, и кодовые скорости, требуемые системой связи, также являются гибко изменяемыми. В настоящее время необходимо решить техническую задачу поддержки кодирования последовательностей информационных битов различной длины для удовлетворения требования системы к скорости кодирования.

Сущность изобретения

Варианты осуществления настоящего изобретения предоставляют способ обработки информации, устройство связи и систему связи для поддержки кодирования и декодирования последовательностей информационных битов различной длины и удовлетворения гибких требований к длине кода и кодовой скорости системы связи.

Согласно первому аспекту предоставлены способ кодирования и кодер. Кодер кодирует входную последовательность, используя LDPC матрицу кода с малой плотностью проверок на четность.

Согласно второму аспекту предоставлены способ декодирования и декодер. Декодер декодирует входную последовательность, используя LDPC матрицу кода с малой плотностью проверок на четность.

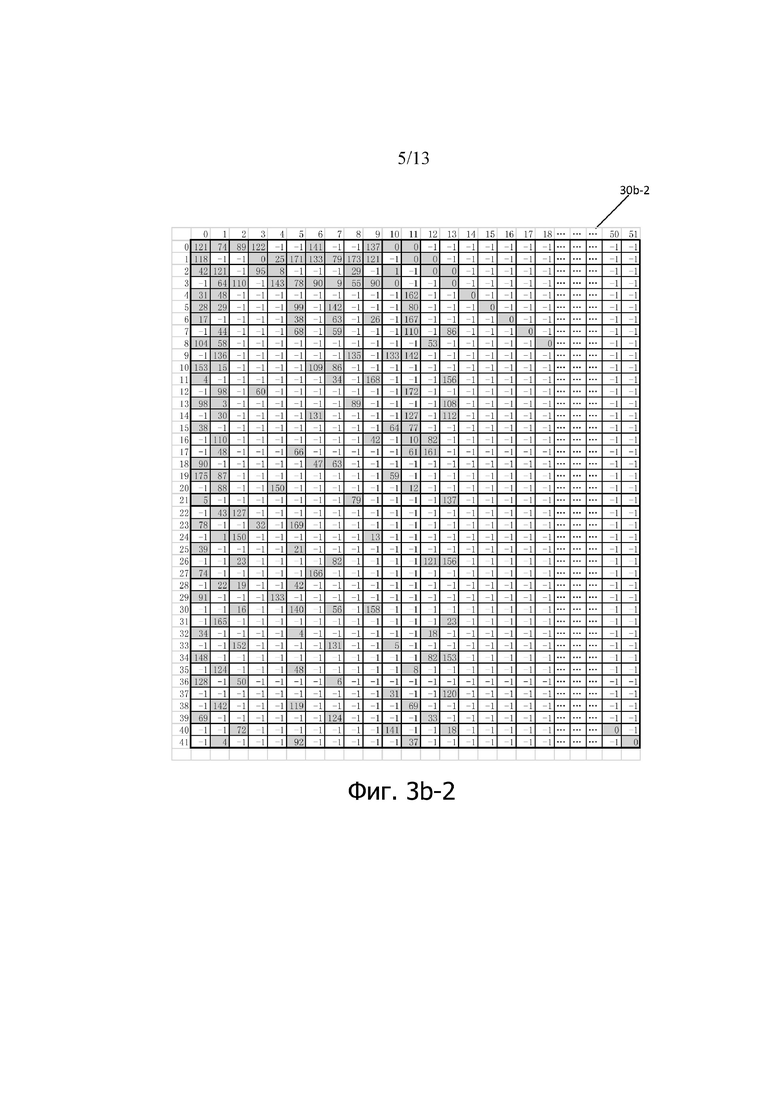

В первой реализации первого аспекта или второго аспекта LDPC матрицу получают на основании базового графа, и базовый граф включает в себя подматрицу A, подматрицу B, подматрицу C, подматрицу D и подматрицу E, где

подматрица A является матрицей, включающей в себя строки mA и столбцы nA, mA и nA являются положительными целыми числами, 4 ≤ mA ≤ 7 и nA = 10;

подматрица B представляет собой матрицу, включающую в себя строки mA и столбцы mA, и подматрица B включает в себя столбец с весом 3 и подматрицу B', имеющую двухдиагональную структуру;

подматрица D включает в себя строки mD в матрице F, матрица F представляет собой матрицу, включающую в себя строки mF и столбцы (mA + nA), mD и mF являются положительными целыми числами, 0≤ mD ≤ mF и 35≤ mF ≤ 38;

подматрица C является полностью нулевой матрицей, включающей в себя строки mA и столбцы mD; и

подматрица E является единичной матрицей, включающей в себя mD строки и mD столбцы.

На основании вышеизложенной реализации, в возможной реализации, любые две смежные строки в последних 10 строках базового графа взаимно ортогональны.

На основании вышеизложенных реализаций, в возможной реализации, последние 10 строк в базовом графе включают в себя, по меньшей мере, пять групп, каждая из, по меньшей мере, пяти групп включает в себя, по меньшей мере, две строки и, по меньшей мере, две строки являются взаимно ортогональными.

На основании любой из вышеизложенных реализаций в возможной реализации в матрице F веса девяти строк равны 3 и вес одной строки равен 2.

В реализации матрицы F вес одного столбца равен 16, вес одного столбца равен 18, вес одного столбца равен 11, вес двух столбцов равен 10, вес одного столбца равен 9. вес одного столбца равен 8, вес одного столбца равен 7, вес одного столбца равен 6, вес двух столбцов равен 4, вес одного столбца равен 3 и вес двух столбцов равен 2.

На основании первой реализации, в другой возможной реализации, количество строк, имеющих ортогональную структуру в матрице F, больше или равно 10 и в матрице F вес одного столбца равен 16, вес одного столбца равен 18, вес одного столбца равен 11, вес двух столбцов равен 10, вес одного столбца равен 9, вес одного столбца равен 8, вес одного столбца равен 7, вес одного столбец равен 6, вес двух столбцов равен 4, вес одного столбца равен 3 и вес двух столбцов равен 2.

В другой реализации в матрице F веса девяти строк равны 3 и вес одной строки равен 2.

В другой реализации матрица F включает в себя, по меньшей мере, 10 строк, и любые две смежные строки, по меньшей мере, в 10 строках являются взаимно ортогональными.

В другой реализации матрица F включает в себя, по меньшей мере, пять групп, каждая из, по меньшей мере, пяти групп включает в себя, по меньшей мере, две строки, и, по меньшей мере, две строки являются взаимно ортогональными. Возможно, по меньшей мере, две строки могут быть последовательными строками. Например, по меньшей мере, 10 строк могут быть последними 10 строками в базовом графе 30a.

В любой из вышеприведенных реализаций, если mA> 4, веса столбцов, отличных от столбцов mA в матрице F, равны 0.

Например, 10 строк, имеющих ортогональную структуру в матрице F, могут включать в себя, например, строки или столбцы матричного блока, включающего в себя строки с 25 по строку 34 и столбцы с 0 по столбец 13 в базовом графе 30a; или 10 строк, имеющих ортогональную структуру в матрице F, могут включать в себя, например, строки или столбцы матричного блока, включающего в себя строки с 25 по строку 34 и столбцы с 0 по столбец 16 в базовом графе 30a. В матрице F строки могут переключаться друг с другом, и столбцы также могут переключаться друг с другом.

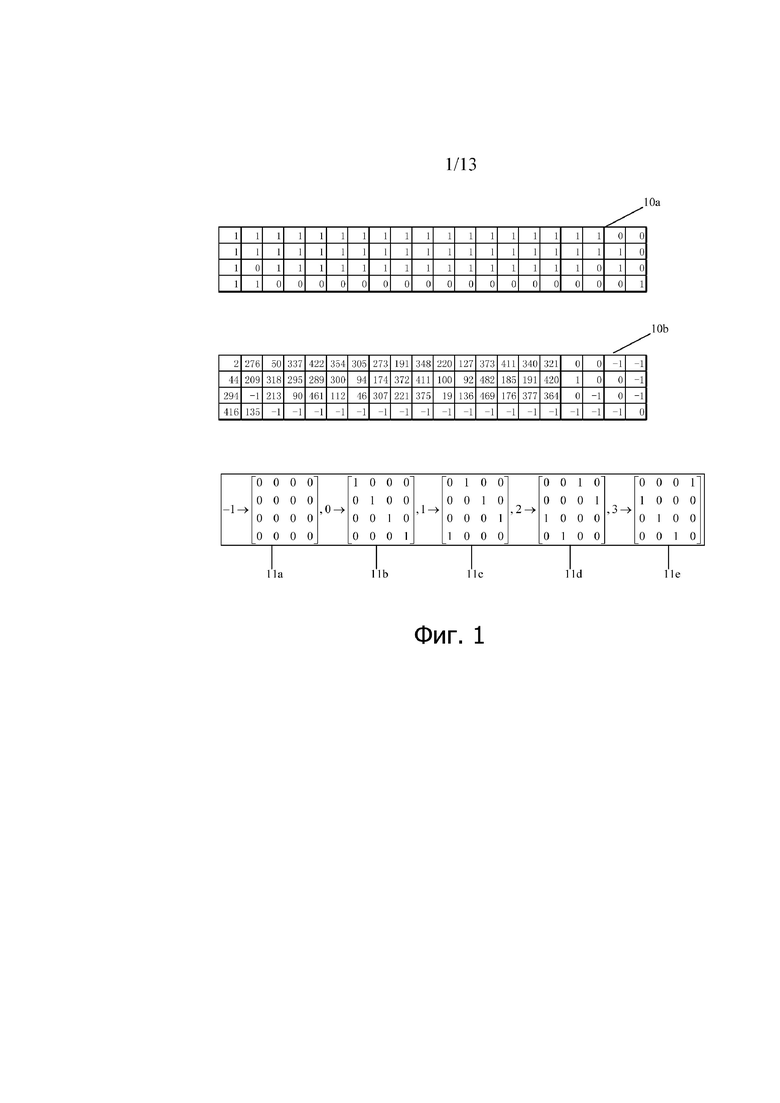

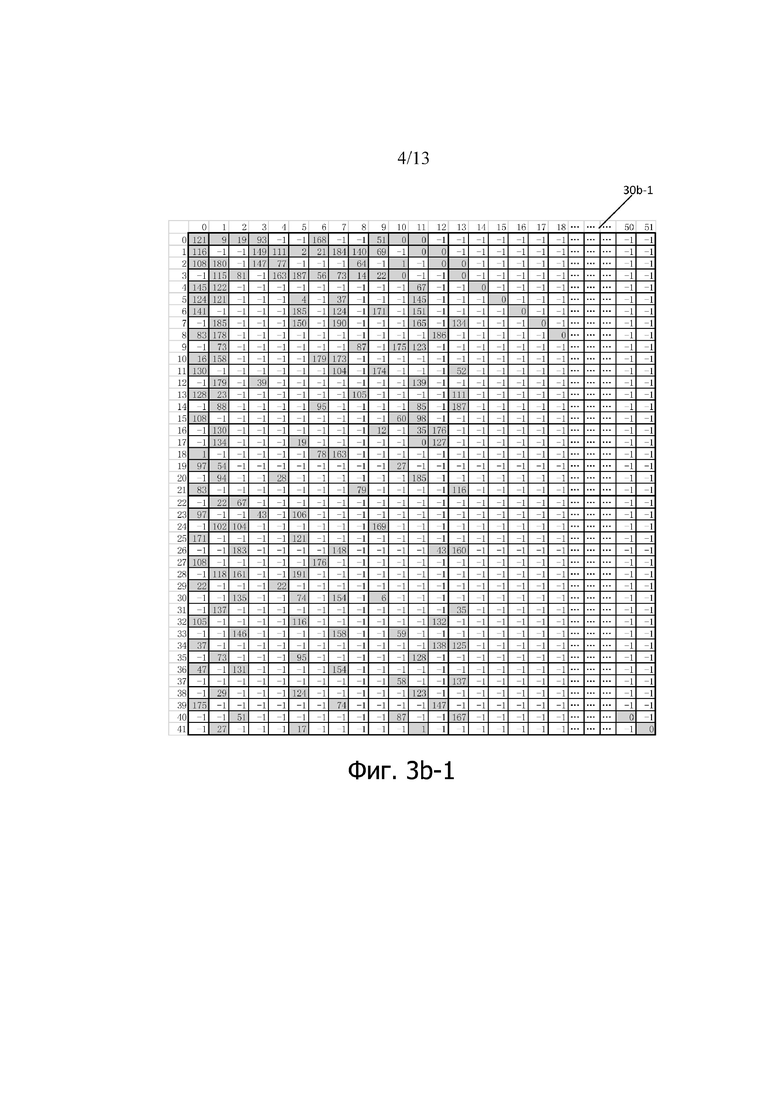

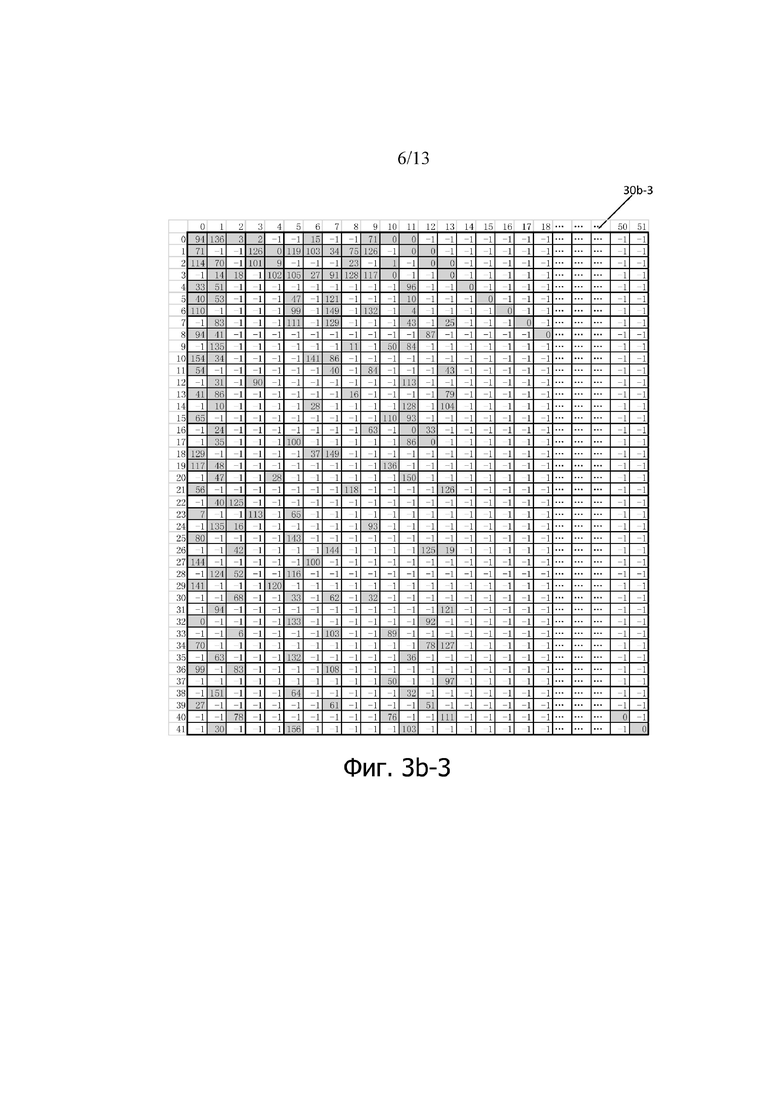

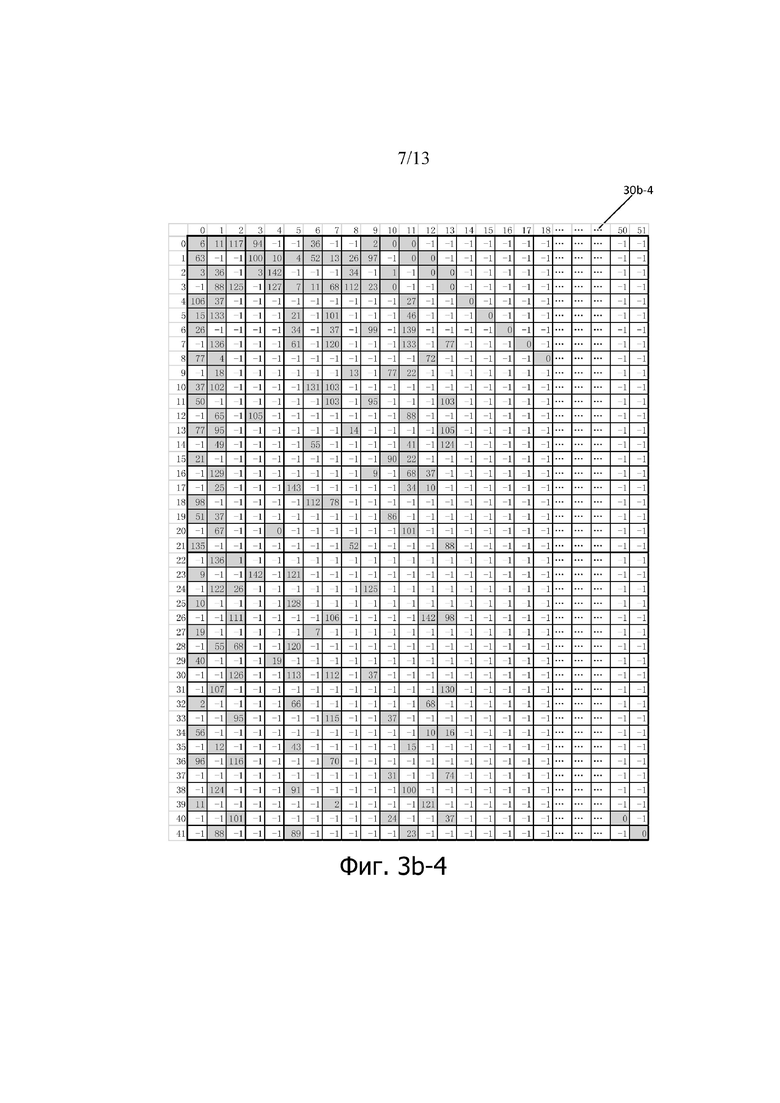

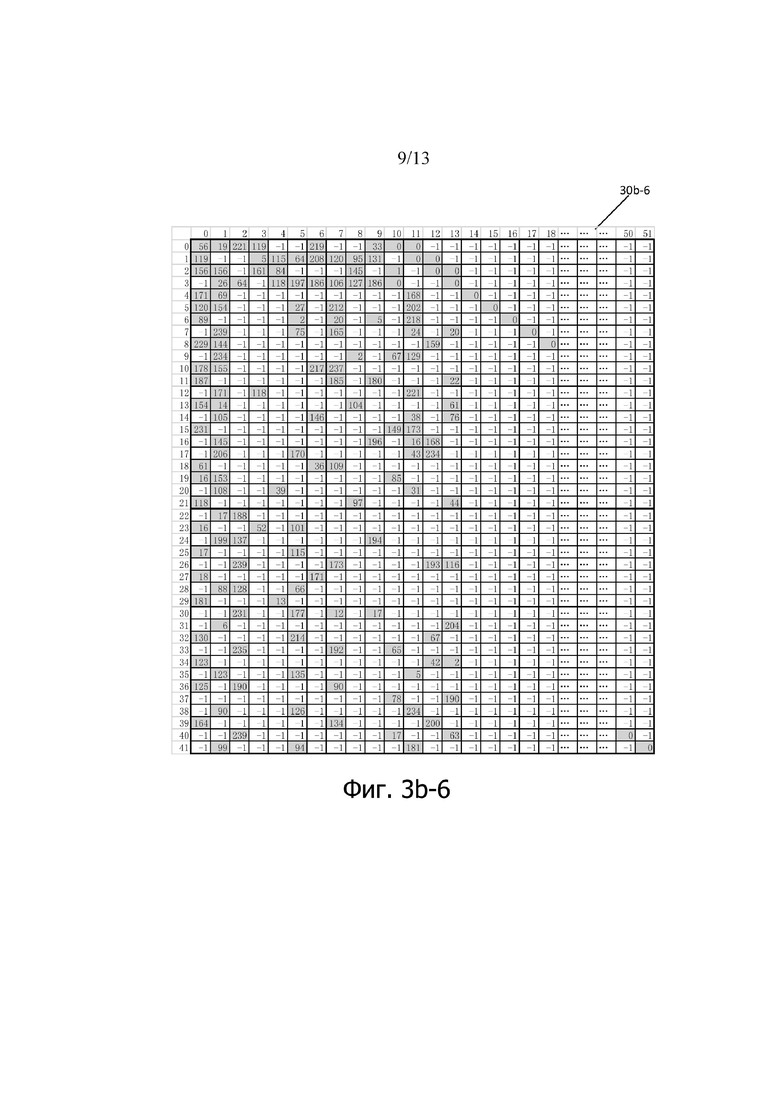

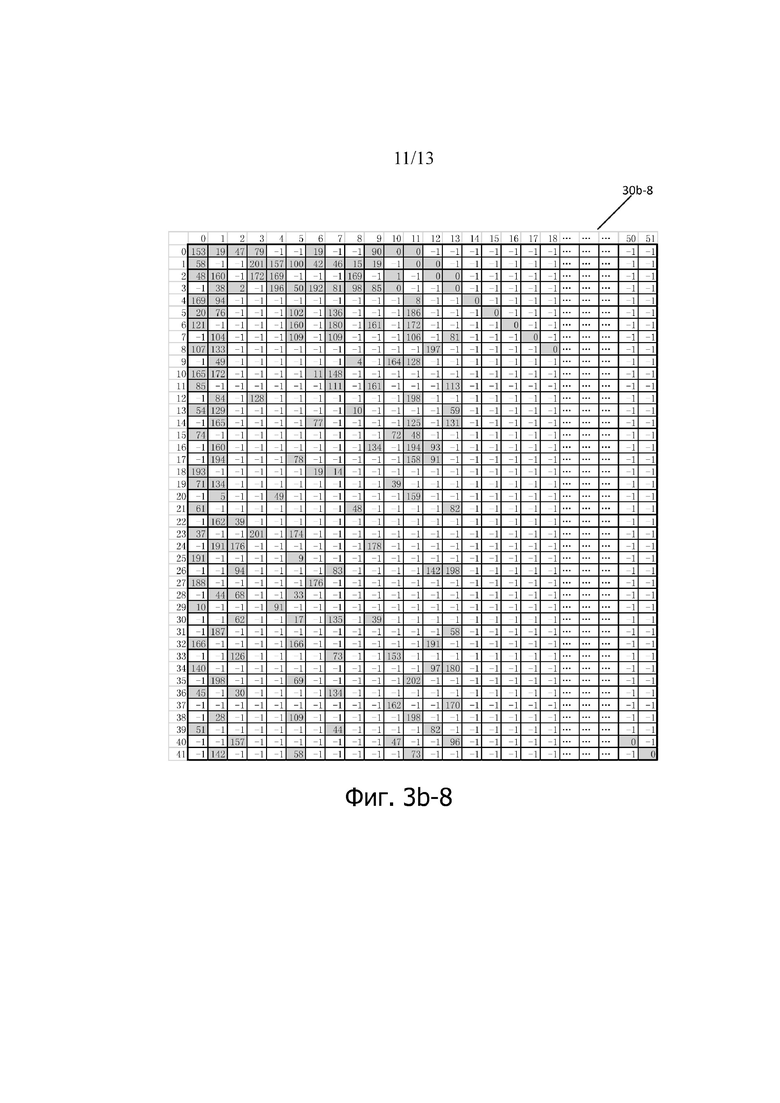

На основании вышеупомянутых реализаций базовой матрицей базового графа 30a может быть, например, любая из базовых матриц 30b-1, 30b-2, 30b-3, 30b-4, 30b-5, 30b-6, 30b-7 и 30b-8 или матрица, полученная путем выполнения перестановки строк/столбцов на любой из базовых матриц 30b-1, 30b-2, 30b-3, 30b-4, 30b-5, 30b-6 30b-7 и 30b-8.

На основании вышеизложенных реализаций матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строки 41 и столбцы от 0 до столбца 16 в любой матрице от 30b-1 до 30b-8, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, включающей в себя строки от 7 до строки 41 и столбцы от 0 до столбца 16 в любой матрице от 30b-1 до 30b-8; или матрица сдвига матрицы F может включать в себя матрицу, включающую в себя строки от 4 до строки 41 и от столбца 0 до столбца 14 в любой матрице от 30b-1 до 30b-8, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строку от 4 до строки 41 и столбец от 0 до столбца 14 в любой матрице от 30b-1 до 30b-8.

Для поддержки разных длин кодовых блоков для LDPC кода требуются разные коэффициенты Z поднятия. На основании вышеупомянутых реализаций в возможной реализации, основанной на различных коэффициентах Z поднятия, используют базовые матрицы, соответствующие различным коэффициентам Z поднятия. Например, Z = a × 2j, где а є {2, 3, 5, 7, 9, 11, 13, 15}.

Если коэффициент поднятия равен одному, удовлетворяющему Z = 2 × 2j, где j = 0, 1, 2, 3, 4, 5, 6, 7, матрица сдвига матрицы F может быть матрицей, включающей в себя строки с 7 по строку 41 и столбец 0 по столбец 16 в 30b-1, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 7 до строку 41 и столбец от 0 до столбца 16 в 30b-1; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 до столбца 14 в 30b-1, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строку от 4 до строки 41 и столбец от 0 до столбца 14 в 30b-1. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-1, или матрицей, полученной путем выполнения перестановки строк/столбцов для матрицы, показанной в 30b-1.

Если коэффициент поднятия равен одному, удовлетворяющему Z = 3 × 2j, где j = 0, 1, 2, 3, 4, 5, 6, 7, матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строку 41 и столбец 0 до столбца 16 в 30b-2, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строку от 7 до строки 41 и столбец от 0 до столбца 16 в 30b-2; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 строки по 41 строку и столбец от 0 до 14 столбца в 30b-2, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строку от 4 до строки 41 и столбец от 0 до столбца 14 в 30b-2. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-2, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-2.

Если коэффициент поднятия равен одному, удовлетворяющему Z = 5 × 2j, где j = 0, 1, 2, 3, 4, 5, 6, матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строки 41 и столбец от 0 до столбца 16 в 30b-3, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строку от 7 по строку 41 и столбец от 0 до столбца 16 в 30b-3; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 до строку 41 и столбцы от 0 до столбца 14 в 30b-3, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строку от 4 до строки 41 и столбец от 0 до столбца 14 в 30b-3. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-3, или матрицей, полученной путем выполнения перестановки строк/столбцов для матрицы, показанной в 30b-3.

Если коэффициент поднятия, удовлетворяющий одному в Z = 7 × 2j, где j = 0, 1, 2, 3, 4, 5, матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строки 41 и столбец от 0 до столбца 16 в 30b-4, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, включающей в себя строки от 7 до строки 41 и от столбца 0 до столбца 16 в 30b-4; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку 4 по строку 41 и столбец 0 по столбец 14 в 30b-4, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки 4 по строку 41 и столбец от 0 до столбца 14 в 30b-4. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-4, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-4.

Если коэффициент поднятия равен одному, удовлетворяющему Z = 9 × 2j, где j = 0, 1, 2, 3, 4, 5, матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строки 41 и столбец от 0 до столбца 16 в 30b-5, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, включающей в себя строки от 7 до строки 41 и от столбца 0 до столбца 16 в 30b-5; или матрица сдвига матрицы F может быть матрицей, включающей в себя строки 4 до строки 41 и столбцы от 0 до 14 в 30b-5, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 до строки 41 и столбец от 0 до столбца 14 в 30b-5. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-5, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-5.

Если коэффициент поднятия равен одному, удовлетворяющему Z = 11 × 2j, где j = 0, 1, 2, 3, 4, 5, матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строки 41 и столбец от 0 до столбца 16 в 30b-6, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, включающей в себя строки от 7 до строки 41 и от столбца 0 до столбца 16 в 30b-6; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку 4 по строку 41 и столбец 0 по столбец 14 в 30b-6, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строку 4 по строку 41 и столбец от 0 до столбца 14 в 30b-6. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной на 30b-6, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной на 30b-6.

Если коэффициент поднятия равен одному, удовлетворяющему Z = 13 × 2j, где j = 0, 1, 2, 3, 4, матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строки 41 и столбцы от 0 до столбца 16 в 30b-7 или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-7; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-7, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строку 41 и столбец от 0 до столбца 14 в 30b-7. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-7, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-7.

Если коэффициент поднятия равен одному, удовлетворяющему Z = 15 × 2j, где j = 0, 1, 2, 3, 4, матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 7 до строки 41 и столбцы от 0 до столбца 16 в 30b-8 или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-8; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-8, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-8. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-8, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-8.

Кроме того, возможно, на основании вышеупомянутых реализаций, для коэффициентов Z поднятия элемент Pi,j=f(Vi,j,Z) в строке i и столбце j в базовой матрице Z может дополнительно быть получен в соответствии с базовыми матрицами вышеупомянутых наборов, где Vi,j является элементом в строке i и столбце j в базовой матрице набора, к которому принадлежит коэффициент Z поднятия.

Например,

В другой возможной реализации базовый граф или базовая матрица может дополнительно включать в себя, по меньшей мере, один столбец, соответствующий встроенным выколотым битам.

В вышеприведенных реализациях базовый граф и базовая матрица LDPC матрицы могут удовлетворять требованиям к производительности кодовых блоков, длина блока которых составляет от 20 до 2560 битов.

На основании вышеизложенных аспектов или любой возможной реализации аспектов, в другой возможной реализации, способ дополнительно включает в себя: определение коэффициента Z поднятия. Например, значение коэффициента Z поднятия определяют в соответствии с длиной K входной последовательности. Например, если длина входной последовательности равна K, то минимальное значение, удовлетворяющее 10 × Z ≥ K, может быть определено из множества коэффициентов поднятия, определенных в системе.

Возможно, LDPC матрица может быть получена на основании базовой матрицы, соответствующей Z, или на основании матрицы сдвига, соответствующей Z.

Для устройства связи на передающей стороне кодирование входной последовательности с использованием LDPC матрицы включает в себя:

кодирование входной последовательности с использованием LDPC матрицы, соответствующей коэффициенту Z поднятия; или кодирование входной последовательности с использованием матрицы, при этом матрица получена путем выполнения перестановки строки/столбца в LDPC матрице, соответствующей коэффициенту Z поднятия. В настоящем изобретении перестановка строки/столбца относится к перестановке строк, перестановок столбцов или перестановок строк и перестановок столбцов.

Для устройства связи на приемной стороне декодирование входной последовательности с использованием LDPC матрицы включает в себя:

декодирование входной последовательности с использованием LDPC матрицы, соответствующей коэффициенту Z поднятия; или выполнение перестановки строки/столбца в LDPC матрице, соответствующей коэффициенту Z поднятия, и декодирование входной последовательности с использованием матрицы, полученной путем выполнения перестановки строки/столбца в LDPC матрице, соответствующей коэффициенту Z поднятия. В настоящем изобретении перестановка строки/столбца относится к перестановке строк, перестановке столбцов или перестановке строк и перестановке столбцов.

В возможной реализации LDPC матрица может быть сохранена в памяти, и входную последовательность кодируют с использованием LDPC матрицы; или LDPC матрицу, которую может быть использована для кодирования, получают путем выполнения перестановки (перестановка строк/столбцов) или поднятия на основании LDPC матрицы.

В другой возможной реализации параметры могут быть сохранены в памяти, и LDPC матрица, используемая для кодирования или декодирования, может быть получена в соответствии с параметрами, так что входная последовательность может быть кодирована или декодирована на основании LDPC матрицы. Параметры включают в себя, по меньшей мере, одно из следующего: базовый граф, базовую матрицу, переставленную матрицу, полученную путем выполнения перестановки строк/столбцов на базовом графе или базовой матрице, поднятую матрицу на основании базового графа или базовой матрицы, значение сдвига ненулевого элемента в базовой матрице или любой параметр, относящийся к получению LDPC матрицы.

В еще одном возможном варианте осуществления базовая матрица LDPC матрицы может храниться в памяти.

В еще одной возможной реализации базовый граф LDPC матрицы сохраняют в памяти, и значения сдвига ненулевых элементов в базовой матрице LDPC матрицы могут хранить в памяти.

На основании вышеизложенных возможных реализаций, в возможной реализации, по меньшей мере, один из базового графа и базовой матрицы, которые используют для LDPC кодирования или декодирования, получают путем выполнения перестановки строк, перестановки столбцов или перестановки строк и перестановки столбцов, по меньшей мере, на одном из базового графа и базовых матриц LDPC матрицы.

Согласно третьему аспекту предоставляют устройство связи. Устройство связи может включать в себя соответствующие модули, выполненные с возможностью выполнять вышеизложенный способ. Модули могут быть программными и/или аппаратными.

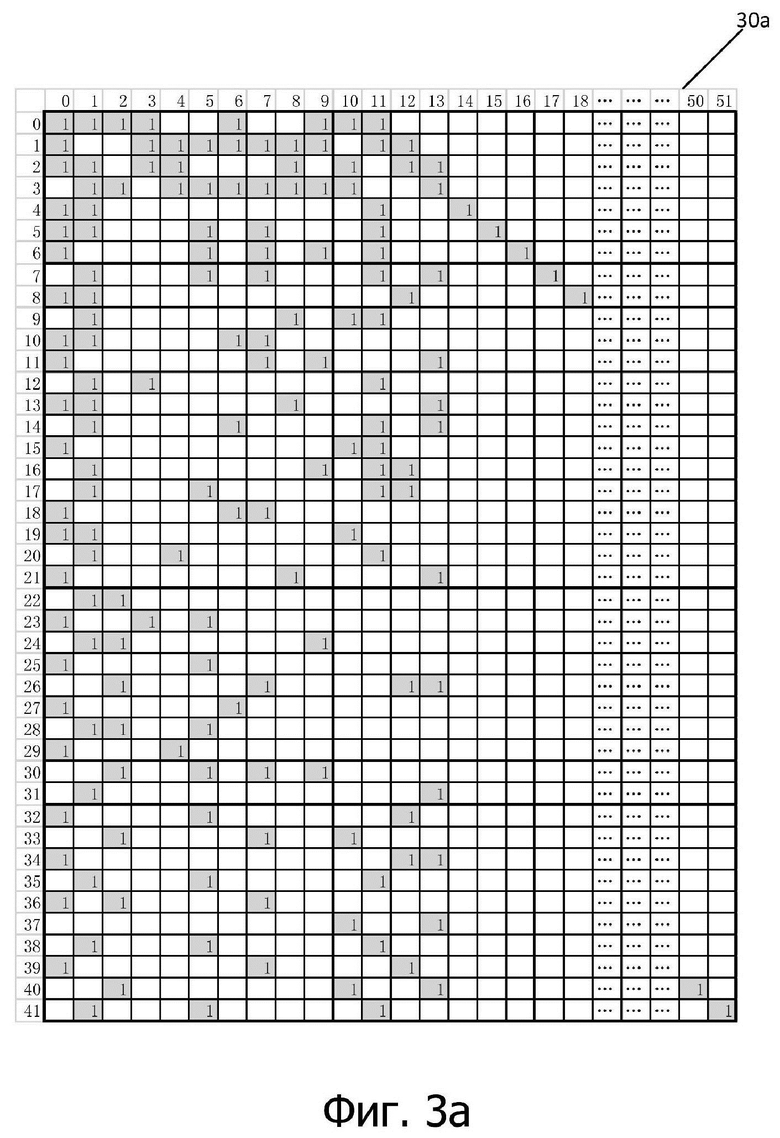

В возможной реализации устройство связи, предусмотренное в третьем аспекте, включает в себя процессор и компонент приемопередатчика, и процессор и компонент приемопередатчика могут быть выполнены с возможностью реализации функций в вышеупомянутом способе кодирования или декодирования. В данной реализации, если устройство связи является терминалом, базовой станцией или другим сетевым устройством, компонент приемопередатчика устройства связи может быть приемопередатчиком. Если устройство связи представляет собой микросхему основной полосы частот или плату обработки основной полосы частот, компонент приемопередатчика устройства связи может представлять собой схему ввода/вывода микросхемы основной полосы частот или платы обработки основной полосы частот и может быть выполнена с возможностью принимать/отправлять входной/выходной сигнал. Устройство связи может возможно включать в себя память, выполненную с возможностью хранить данные и/или инструкции.

В реализации процессор может включать в себя кодер в соответствии с вышеупомянутым первым аспектом и блок определения. Блок определения выполнен с возможностью определять коэффициент Z поднятия, необходимый для кодирования входной последовательности. Кодер выполнен с возможностью кодировать входную последовательность с использованием LDPC матрицы, соответствующей коэффициенту Z поднятия.

В другой реализации процессор может включать в себя декодер в соответствии с вышеупомянутым вторым аспектом и блок получения. Модуль получения выполнен с возможностью получать мягкие значения LDPC кода и коэффициент Z поднятия. Декодер выполнен с возможностью декодировать мягкие значения LDPC кода на основании базовой матрицы HB, соответствующей коэффициенту Z поднятия, для получения последовательности информационных битов.

Согласно четвертому аспекту предоставляют устройство связи. Устройство связи включает в себя один или несколько процессоров.

В возможной реализации один или более процессоров могут реализовывать функцию кодера в первом аспекте. В другом возможной реализации кодер в первом аспекте может быть частью процессора. В дополнение к функции кодера в первом аспекте, процессор может дополнительно реализовывать другие функции.

В возможной реализации один или более процессоров могут реализовывать функцию декодера во втором аспекте. В другой возможной реализации декодер во втором аспекте может быть частью процессора.

Возможно, устройство связи может дополнительно включать в себя приемопередатчик и антенну.

Возможно, устройство связи может дополнительно включать в себя компонент, выполненный с возможностью формировать CRC транспортный блок, компонент, используемый для сегментации кодового блока и CRC присоединения, перемежитель, используемый для перемежения, модулятор, используемый для обработки модуляции, или тому подобное.

Возможно, устройство связи может дополнительно включать в себя демодулятор, используемый для операции демодуляции, обращенный перемежитель, используемый для обратного перемежения, компонент, используемый для де-согласования скорости, или тому подобное. Функции компонентов могут быть реализованы с использованием одного или нескольких процессоров.

В возможной реализации функции компонентов могут быть реализованы с использованием одного или нескольких процессоров.

Краткое описание чертежей

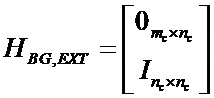

Фиг. 1 является схемой базового графа и базовой матрицы LDPC кода и матриц круговой перестановки базовой матрицы в LDPC схеме кода;

Фиг. 2 является схемой базового графа LDPC кода;

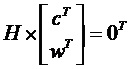

Фиг. 3a является схемой базового графа LDPC кода согласно варианту осуществления настоящего изобретения;

Фиг. 3b-1 –Фиг. 3b-8 является схемой базовых матриц базового графа, показанного на фиг. 3а;

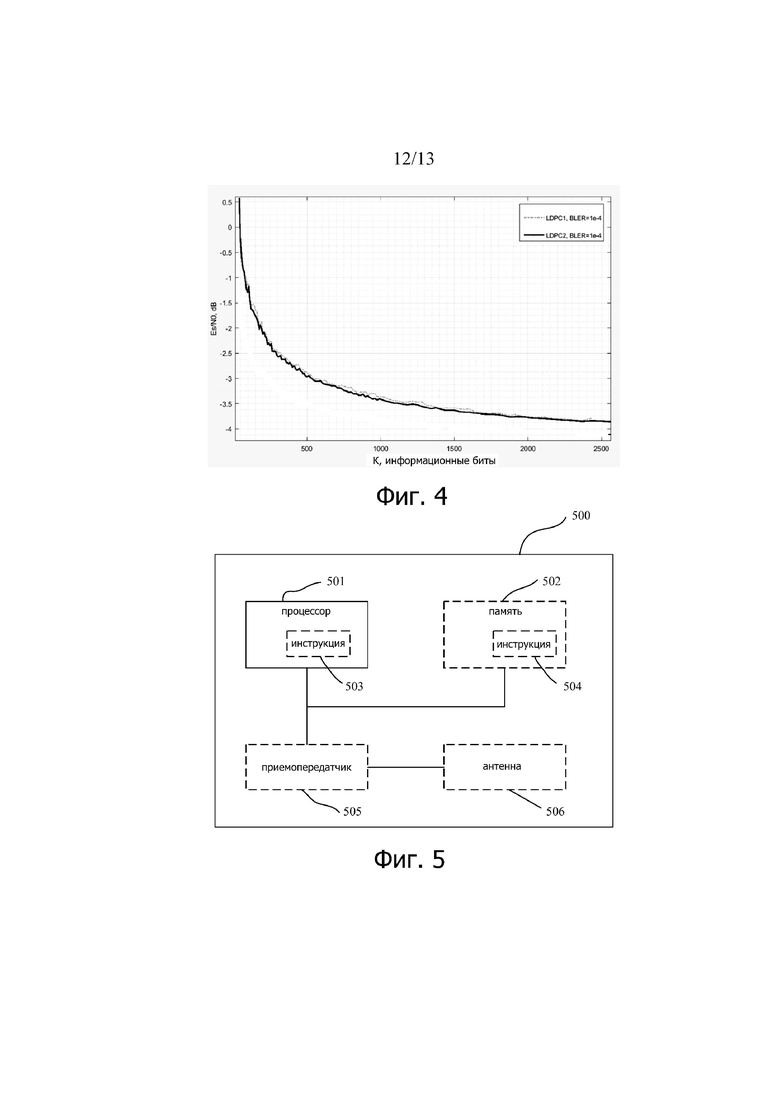

Фиг.4 является схемой производительности в соответствии с вариантом осуществления настоящего изобретения;

Фиг. 5 является схемой устройства обработки информации в соответствии с вариантом осуществления настоящего изобретения; и

Фиг.6 является схемой системы связи в соответствии с вариантом осуществления настоящего изобретения.

Описание вариантов осуществления

Далее приведено описание некоторых терминов в настоящем изобретении с целью облегчения понимания настоящего изобретения.

В настоящем изобретении термины «сеть» и «система» обычно взаимозаменяемы, и термины «устройство» и «приспособление» также обычно взаимозаменяемы. Однако специалист в данной области может понять их значения. «Устройство связи» может быть микросхемой (такой как микросхема основной полосы частот или микросхема цифровой обработки сигналов или микросхема общего назначения), терминалом, базовой станцией или другим сетевым устройством. Терминал является устройством, имеющим функцию связи. Терминал может включать в себя портативное устройство, автомобильное устройство, носимое устройство и вычислительное устройство, которое имеет функцию беспроводной связи, или другое устройство обработки, подключенное к беспроводному модему, или тому подобное. Терминал может иметь разные названия в разных сетях, например, устройство пользователя, мобильная станция, пользовательский блок, станция, сотовый телефон, персональный цифровой помощник, беспроводной модем, устройство беспроводной связи, портативное устройство, портативный компьютер, беспроводной телефонный аппарат и беспроводная локальная абонентская станция. Для простоты описания в настоящем изобретении для краткости устройства называют терминалами. Базовая станция (base station, BS), также называемая устройством базовой станции, представляет собой устройство, развернутое в сети радиодоступа для обеспечения функции беспроводной связи. В разных системах радиодоступа названия базовой станции могут быть разными. Например, базовая станция в сети универсальной системы мобильной связи (Universal Mobile Telecommunication System, UMTS) упоминается как узел B (NodeB), базовая станция в LTE сети упоминается как развитый узел B (evolved NodeB). eNB или eNodeB), базовая станция в сети «Новое радио» (new radio, NR) упоминается как точка приема передачи (transmission reception point, TRP) или узел B следующего поколения (generation nodeB, gNB) или базовая станция в различных других сетях также может иметь другие названия. Настоящее изобретение этим не ограничивается.

Далее описаны технические решения в вариантах осуществления настоящего изобретения со ссылкой на прилагаемые чертежи в вариантах осуществления настоящего изобретения.

Обычно LDPC код может быть определен с использованием матрицы H проверки на четность. Матрица H проверки на четность для LDPC кода может быть получена с использованием значений базового графа (base graph) и сдвига (shift). Обычно базовый граф может включать в себя m × n матричных элементов (запись). Базовый граф может быть представлен с использованием матрицы, включающей в себя m строк и n столбцов. Значение каждого матричного элемента равно 0 или 1. Элемент, значение которого равно 0, также иногда называют нулевым элементом, который можно заменить нулевой матрицей (zero matrix) размера Z × Z. Элемент, значение которого равно 1, также иногда называют ненулевым элементом, который может быть заменен матрицей круговой перестановки (circulant permutation matrix) размера Z × Z. Таким образом, каждый матричный элемент представляет собой полностью нулевую матрицу или матрицу круговой перестановки. Фиг. 1 показывает пример 10a базового графа LDPC кода, в котором m = 4 и n = 20 и который имеет QC структуру. Следует отметить, что в этой спецификации для простоты пояснения индексы строк и столбцов базового графа и матрицы нумеруют, начиная с 0. Понятно, что индексы строк и индексы столбцов могут альтернативно быть пронумерованы, начиная с 1, и соответствующие индексы строк и индексов столбцов увеличивают на 1 на основании индексов строк и индексов столбцов, показанных в этой спецификации.

Если значение элемента в строке i и столбце j в базовом графе равно 1, ему присваивается значение Pi,j сдвига. Pi,j представляет собой целое число, большее или равное 0, это указывает, что элемент 1 (ненулевой элемент) в строке i и столбце j может быть заменен матрицей круговой перестановки размера Z × Z, соответствующей Pi,j. Матрица круговой перестановки может быть получена путем кругового сдвига единичной матрицы размера Z × Z вправо Pi,j раз. Можно узнать, что в базовом графе каждый элемент, значение которого равно 0, заменяется нулевой матрицей размером Z × Z, и каждый элемент, значение которого равно 1, заменяется матрицей круговой перестановки размера Z × Z, соответствующей значению сдвига элемента, чтобы можно было получить матрицу проверки на четность LDPC кода. Базовый граф может быть использован для указания позиций значений сдвига, и каждый ненулевой элемент в базовом графе соответствует значению сдвига. Z представляет собой положительное целое число, также может упоминаться как коэффициент поднятия (lifting) и иногда может также упоминаться как размер поднятия, коэффициент поднятия или тому подобное. Z может быть определен в соответствии с размером кодового блока, который поддерживается системой, и размером информационных данных. Можно узнать, что матрица H проверки на четность имеет размер (m × Z) × (n × Z). Например, если коэффициент Z = 4 поднятия, каждый нулевой элемент заменяется на нулевую матрицу 11a 4 × 4. Если P2,3 = 2, ненулевой элемент в строке 2 и столбце 3 заменяют матрицей 11d круговой перестановки 4 × 4. Матрицу получают путем кругового сдвига 4 × 4 единичной матрицы 11b вправо дважды. Если P2,4 = 0, то ненулевой элемент в строке 2 и столбце 4 заменяют единичной матрицей 11b. Следует отметить, что в настоящем документе описаны только примеры, и примеры не являются ограничением.

Значение Pi,j может зависеть от коэффициента Z поднятия. Следовательно, для элемента 1 (ненулевой элемент) в строке i и столбце j базового графа Pi,j может отличаться для разных коэффициентов Z поднятия. Для простоты реализации обычно базовая матрица m × n (base matrix) определяется в системе. Каждый элемент в базовой матрице находится в однозначном соответствии с каждым элементом в базовом графе. Нулевой элемент в базовом графе имеет такую же позицию в базовой матрице, и этот элемент обозначен -1. Не ненулевой элемент, обозначенный 1 в строке i и столбце j в базовом графе, имеет одинаковую позицию в базовой матрице, и ненулевой элемент обозначен значением Vi,j где Vi,j может быть значение сдвига, определенное относительно предустановки или конкретного коэффициента Z поднятия, например, значение сдвига относительно максимального коэффициента Zmax поднятия в наборе, к которому принадлежит коэффициент Z поднятия. Таким образом, Vi,j может быть значением сдвига ненулевого элемента в строке i и столбце j, когда используется максимальный коэффициент Zmax поднятия в наборе, которому принадлежит Z. В этом варианте осуществления настоящего изобретения базовая матрица также иногда упоминается как матрица сдвига матрицы базового графа.

Pi,j может быть получен на основании Vi,j и Z. Например, может быть выражен как Pi,j=f(Vi,j,Z), где f(Vi,j,Z) является функцией используя Vi,j и Z в качестве параметров. Например,

Как показано на фиг. 1, 10b является базовой матрицей, соответствующей базовому графу 10a.

Обычно базовый граф или базовая матрица LDPC кода могут включать в себя p столбцов, соответствующих встроенным выколотым битам (built-in puncture), где p может быть целым числом от 0 до 2. Эти столбцы могут быть использованы при кодировании, но систематические биты, соответствующие встроенным выколотым битам, не отправляют. Кодовая скорость базовой матрицы LDPC кода удовлетворяет условию R=(n-m)/(n-p). Для базовой матрицы, включающей в себя 4 строки и 20 столбцов (4 × 20), при наличии двух столбцов, соответствующих встроенным выколотым битам, кодовая скорость составляет (20–4)/(20–2) = 8/9.

Для LDPC кода, используемого в системе беспроводной связи, матрица базового графа LDPC кода имеет размер m × n, и базовый граф может включать в себя пять подматриц: A, B, C, D и E. Вес матрицы определен количеством ненулевых элементов, вес строки (a row weight) относится к количеству ненулевых элементов в строке, и вес столбца (a column weight) относится к количеству ненулевых элементов в столбце.

Как показано в 200 на фиг. 2: подматрица A является матрицей, включающей в себя строки mA и столбцы nA, подматрица A имеет размер mA × nA. Каждый столбец соответствует Z систематических битов в LDPC коде и систематический бит иногда упоминается как информационный бит.

Подматрица B является квадратной матрицей строк mA и столбцов mA, и подматрица B имеет размер mA × mA. Каждый столбец соответствует Z битам четности в LDPC коде. Как показано в 20а на фиг. 2, подматрица B включает в себя подматрицу B' с двухдиагональной структурой и столбец матрицы, вес которого равен 3 (для краткости, столбец с весом 3), и столбец с весом 3 может быть расположен с левой стороны подматрицы B'. Подматрица B может дополнительно включать в себя один или несколько столбцов матрицы, вес столбца которых равен 1 (для краткости, столбец веса 1). Например, возможная реализация показана на 20b или 20c на фиг. 2.

Как правило, матрица, сгенерированная на основании подматриц A и B, является основной матрицей, которая может быть использована для поддержки высокоскоростного кодирования.

Продолжая на фиг. 2, подматрица C является нулевой матрицей, и подматрица C имеет размер mA × mD. Подматрица E является единичной матрицей, и подматрица E имеет размер mD × mD.

Подматрица D имеет размер mD x (nA + mA), и подматрица D может быть использована для генерации битов четности с низкой кодовой скоростью.

Очевидно, что базовый граф описан выше с точки зрения математического определения, и подматрица C является нулевой матрицей, и подматрица E является единичной матрицей. Следовательно, в возможной реализации матрица, включающая в себя подматрицу A и подматрицу B, или матрица, включающая в себя подматрицу A, подматрицу B и подматрицу D, могут быть использованы для представления базового графа матрицы при кодировании или декодировании.

Поскольку структуры подматрицы C и подматрицы E являются относительно фиксированными, структуры подматрицы A, подматрицы B и подматрицы D являются определяющими факторами, влияющими на производительность кодирования и декодирования LDPC кода.

Когда для кодирования используют LDPC матрицу с хищной структурой, в возможной реализации часть матрицы, включающая в себя подматрицу A и подматрицу B, а именно, основную матрицу, может сначала использоваться для кодирования для получения одного или несколько битов четности, соответствующих подматрице B. Затем вся матрица используется для кодирования, чтобы получить один или несколько битов четности, соответствующих подматрице E. Поскольку подматрица B может включать в себя подматрицу B' с двухдиагональной структурой и столбцом весом 1. Следовательно, во время кодирования сначала могут быть получены один или несколько битов четности, соответствующих двухдиагональной структуре, а затем получены один или несколько битов четности, соответствующих столбцу с весом 1.

Далее приведен пример способа кодирования. Предполагая, что основной матрицей, включающей в себя подматрицу A и подматрицу B, является Hcore, удаляют столбец веса 1 и строку, в которой расположен ненулевой элемент в столбце веса 1, из Hcore для получения матрицы Hcore-dual. Матричный блок в Hcore-dual, соответствующий битам четности, представлен He=[He1 He2], где He1 является столбцом весом 3, и He2 имеет двухдиагональную структуру. Согласно определению LDPC кодовой матрицы, Hcore-dual∙[S Pe]T=0, где S является входной последовательностью и является вектором, включающим в себя информационные биты, Pe является вектором, включающий в себя биты четности, и [S Pe]T указывает транспонированную матрицу, включающую в себя входную последовательность S и Pe. Следовательно, биты четности, соответствующие в себя Hcore-dual, могут быть вычислены первыми в соответствии с входной последовательностью S и Hcore-dual. Входная последовательность S включает в себя все информационные биты. Затем вычисляют биты четности, соответствующие столбцу веса 1 в подматрице B, согласно полученным битам четности, соответствующим Hcore-dual, и входной последовательности S. В этом случае, могут быть получены все биты четности, соответствующие подматрице B. Затем биты четности, соответствующие подматрице E, получают путем кодирования с использованием подматрицы D и на основании входной последовательности S и полученных битов четности, соответствующих подматрице B. Таким образом, получают все информационные биты и все биты четности. Эти биты образуют кодированную последовательность, то есть, LDPC кодовое слово (слова).

Возможно, LDPC кодирование может дополнительно включать в себя операции укорочения (shortening) и выкалывания (puncturing). Укороченные биты и выколотые биты не отправляют.

Укорочение обычно выполняют, начиная с последнего бита информационных битов, и может быть выполнено различными способами. Например, для количества укороченных битов, равного s0, последние s0 битов во входной последовательности S могут быть установлены как известные биты, например, равные 0 или нулевым, или другим значениям, для получения входной последовательности S', и затем входную последовательность S' кодируют с использованием LDPC матрицы. В другом примере, последние (s0 mod Z) биты во входной последовательности S могут быть установлены как известные биты, такие как 0 или нулевые, или другие значения, чтобы получить входную последовательность S', и удаляют последние

Выкалывание может быть выполнено для одного или нескольких столбцов, соответствующих встроенным выколотым битам, или одному или нескольким битам четности во входной последовательности. Обычно выкалывание одного или нескольких битов четности также происходит из последнего бита в битах четности. В качестве альтернативы, выкалывание бит (битов) четности может быть выполнено в системе в соответствии с заданным шаблоном выкалывания. В возможной реализации сначала кодируют входную последовательность и затем, на основании количества p битов, которые должны быть выколоты, выбирают последний p бит в битах четности или p бит выбирают в соответствии с заданным шаблоном выкалывания в системе, где биты p не отправляют. В другой возможной реализации могут быть определены p столбца (столбцов) матрицы, соответствующий выколотым битам, и p строк, в которых расположены ненулевые элементы в этих столбцах, и строки и столбцы не участвуют в кодировании, и поэтому не генерируют соответствующие биты четности.

Следует отметить, что реализации кодирования, описанные в данном документе, просто используют в качестве примеров. Другие известные реализации кодирования могут альтернативно быть использованы на основании базового графа и/или базовой матрицы, предоставленной в настоящем изобретении, и реализации кодирования не ограничены в настоящем документе. Декодирование в настоящем изобретении может быть выполнено различными способами декодирования, например, способом декодирования с минимальной суммой (MS) или способом декодирования с распространением степени уверенности. Способ MS-декодирования также иногда может называться лавинообразным MS способом декодирования. Например, инициализируют входную последовательность и выполняют итерацию. Выполняют обнаружение жесткого решения после итерации, и проверяют результат жесткого решения. Если результат декодирования соответствует проверочному уравнению, декодирование завершается успешно, итерация заканчивается, и выводят результат решения. Если результат декодирования не соответствует контрольному уравнению, итерация выполняется снова в течение максимального количества итераций. Если проверка по-прежнему не выполнена, при достижении максимального количества итераций, декодирование завершается неудачно. Очевидно, что принцип декодирования MS общеизвестен, и подробности в настоящем документе опущены.

Следует отметить, что способ декодирования используют только в качестве примера в данном документе, альтернативно могут быть использованы другие известные способы декодирования на основании базового графа и/или базовой матрицы, предоставленной в настоящем изобретении.

LDPC код может быть получен на основании базового графа и базовой матрицы, верхний предел производительности LDPC кода может быть определен путем выполнения эволюции плотности на базовом графе или базовой матрице. Минимальный уровень ошибки LDPC кода определяют на основании значения сдвига в базовой матрице. Улучшение производительности кодирования и производительности декодирования и снижение минимального уровня ошибок являются одними из задач проектирования базового графа и базовой матрицы. В системе беспроводной связи длины кода широко варьируются. Например, длина кода может составлять 40 бит, 1280 бит или тому подобное. Фиг. 3а и фиг. 3b-1 - фиг. 3b-8 являются примерами базового графа и базовых матриц базовой матрицы LDPC кода. Примеры могут соответствовать требованиям к производительности кодовых блоков, имеющих длину блока от 20 до 2560 битов. Для простоты описания и понимания индексы столбцов и индексы строк соответственно показаны на самой верхней стороне и самой левой стороне на фиг. 3а и фиг. 3b-1 - фиг. 3b-8 .

Фиг. 4 является схемой производительности на основании LDPC кода, показанного на фиг. 3а и фиг. 3b-1 - фиг. 3b-8. LDPC 1 указывает LDPC код, полученный путем кодирования на основании базовой матрицы, соответствующей базовому графу 30a, LDPC 2 указывает обычно используемый LDPC код, используемый для сравнения. Горизонтальная координата указывает длину последовательности информационных битов и единицей длины является бит. Вертикальная координата указывает отношение сигнал/шум символа (Es/N0). Кривые производительности указывают рабочие характеристики отношения сигнал/шум символа для LDPC 1 и LDPC 2 в случае различных длин последовательностей информационных битов, когда BLER равно 0,0001. Можно узнать, что при одном и том же BLER отношение сигнал/шум символа LDPC 1 меньше, чем у LDPC 2 в случае различных длин последовательностей информационных бит, то есть, производительность LDPC 1 лучше, чем что из LDPC 2.

На фиг.3а показан пример базового графа 30а LDPC кода. Матрица базового графа 30a имеет 42 строки и 52 столбца. На чертеже от 0 до 51 в самой верхней строке указывают индексы столбцов и от 0 до 41 в самой левой колонке указывают индексы строк.

На базовом графе 30a подматрица A соответствует систематическим битам и имеет строки mA и 10 столбцов, где 4≤ mA ≤ 7. Например, если mA = 4, подматрица A включает в себя элементы от строки 0 до строки 3 и от столбца 0 до столбца 9 в базовом графе 30a. В другом примере, если mA> 4, используя в качестве примера mA = 7, подматрица A включает в себя элементы в строках с 0 по 6 и в столбцах с 0 по 9 в базовом графе 30a.

Подматрица B соответствует битам четности, имеет строки mA и столбцы mA и включает в себя элементы от строки 0 до строки (mA-1) и от столбца 10 до столбца (10 + mA-1) на базовом графе 30a.

Подматрица A и подматрица B формируют основную матрицу базового графа LDPC кода, то есть матрицу, включающую в себя строки mA и столбцы (mA + nA). Матрица может использоваться для кодирования с высокой скоростью кодирования. Для простоты описания, используя mA = 7 в качестве примера ниже, основная матрица базового графа LDPC кода составляет 7 строк и 17 столбцов.

Подматрица A может включать в себя два столбца, соответствующих встроенным выколотым битам. После выкалывания кодовая скорость, которая может поддерживаться основной матрицей, равна 10 / (17–2) = 2/3.

Подматрица B включает в себя один столбец веса 3, то есть, вес столбца 0 подматрицы B (столбец 10 основной матрицы) равен 3. Матрица, включающая в себя столбцы 1 - столбец 3 (столбец 11 - столбец 13 в основной матрице), и строки от 0 до 3 в подматрице B имеют двухдиагональную структуру. Подматрица B дополнительно включает в себя три столбца веса 1.

Используя mA = 7 в качестве примера, основная матрица базового графа 30a включает в себя две строки с весами 10, две строки с весами 8, две строки с весами 6 и одну строку с весом 4. То есть, веса строк в основной матрице, включающей в себя подматрицу A и подматрицу B, соответственно составляют 8, 10, 8, 10, 4, 6 и 6. Следует отметить, что строки в основной матрице могут переключаться, например, строка 0 переключается со строкой 2, строка 1 переключается со строкой 3 и т.п. Каждая из строк в основной матрице может быть одной из строк, показанных в строке от 0 до строки 6 и от столбца 0 до столбца 16 в основной матрице базового графа 30a. Строки могут переключаться друг с другом, и столбцы также могут переключаться друг с другом. Например, столбец 8 может быть переключен со столбцом 14 в основной матрице. Следует отметить, что в настоящем документе приведены только примеры. В реальной реализации перестановка столбцов и перестановок строк может быть гибко разработана на основе требований системы.

Понятно, что поскольку в матрице строки могут переключаться друг с другом, столбцы также могут переключаться друг с другом, перестановка строк не меняет вес столбцов, и перестановка столбцов не меняет вес строк, количество ненулевых элементов в матрице не меняется. После перестановки строк и перестановок столбцов веса строк в базовом графе не изменяются. Использование базового графа, полученного после перестановки строк, перестановок столбцов или перестановок строк и перестановок столбцов, не влияет на производительность.

Следует отметить, что в настоящем изобретении производительность не подвержена влиянию: в целом, воздействие является приемлемым и находится в пределах допуска. Например, в некоторых сценариях или в некоторых диапазонах производительность снижается в допустимом диапазоне. Однако в некоторых сценариях или некоторых диапазонах производительность улучшается. В целом, это мало влияет на производительность.

Обычно для данного базового графа или данной базовой матрицы LDPC кода влияние на производительность, вызванное несколькими модификациями матричных элементов, является приемлемым. Например, в реализации несколько модификаций могут быть сделаны на основе базовой матрицы базового графа 30a. Например, вес одного ряда больше или равен 2 и меньше или равен 5, а вес других шести рядов больше или равен 6 и меньше или равен 12. Можно понимать, что для решения, представленного в настоящем изобретении, веса некоторых строк могут быть увеличены или уменьшены на 1 или 2. Это не ограничено в настоящем изобретении.

Для получения гибких кодовых скоростей, подматрица C, подматрица D и подматрица E соответствующих размеров могут быть добавлены на основании основной матрицы. Поскольку подматрица C является нулевой матрицей и подматрица является единичной матрицей, размеры матриц определяются согласно скоростям кода, и структуры матриц являются относительно фиксированными. На производительность кодирования и производительность декодирования в основном влияют основная матрица и подматрица D. Различные скорости кодирования могут быть получены путем добавления строк и столбцов на основе основной матрицы для формирования соответствующих подматриц C, D и E. Например, основная матрица базового графа 30a может использоваться в качестве основной матрицы, и соответствующие подматрицы C, D и E добавляются для удовлетворения требований кодирования или декодирования для различных кодовых скоростей.

Число mD столбцов подматрицы D является суммой количества столбцов подматрицы A и количества столбцов подматрицы B, и количество строк подматрицы D, главным образом, связано с кодовой скоростью. Используя базовый граф 30a в качестве примера, если mA = 4, соответствующее количество столбцов подматрицы D равно (nA + mA) = 14 или, если mA = 7, соответствующее количество столбцов подматрицы D равно (nA + mA) = 17. Если кодовая скорость, поддерживаемая LDPC кодом, равна Rm, базовый граф или базовая матрица LDPC кода имеет размер m × n, где n = nA/Rm + p и m = n-nA = nA/Rm + р - nА. Если минимальная кодовая скорость Rm = 1/5 и количество столбцов p, соответствующих встроенным выколотым битам, равно 2, используя базовый граф 30a в качестве примера, n = 52 и m = 42. Число строк mD подматрицы D может составлять до m – mA = 42– mA, и, если mA = 4, 0≤ mD ≤ 38 или, если mA = 7, 0≤ mD ≤ 35.

Для простоты описания, может быть определена матрица F строк mF и столбцов (mA + nA), так что подматрица D может включать в себя строки mD в матрице F, где 0≤ mD ≤ mF и 35≤ mF ≤ 38. По-прежнему используя mA = 7 в качестве примера, в базовом графе 30a mA + mD = 42. Если mD = 35, соответственно, подматрица D включает в себя 35 строк и 17 столбцов. В частности, подматрица D является матрицей F, и кодовая скорость, поддерживаемая соответствующим LDPC кодом, составляет 10/50 = 1/5. Можно узнать, что для mA = 7 матрица, включающая в себя строку 7 в строку 41 и столбец 0 - столбец 17 в базовом графе 30a, является матрицей F. Для mA = 4 матрица включает в себя строку от 4 по строку 41 и столбец от 0 до столбца 13 на базовом графе 30a представлена матрица F. Следует отметить, что в настоящем документе представлены только примеры, и настоящее изобретение этим не ограничивается. В качестве альтернативы, mA может быть любым целочисленным значением от 4 до 7, и количество столбцов матрицы F также соответственно изменяется.

В настоящем изобретении, если в одном и том же столбце в двух смежных строках базового графа содержится не более одного ненулевого элемента, эти две строки взаимно ортогональны. В других столбцах, отличающихся от некоторых столбцов для двух смежных строк в базовом графе, если в одном и том же столбце других столбцов содержится не более одного ненулевого элемента для двух смежных строк в базовом графе, эти две строки являются квазиортогональными.

Матрица F может включать в себя множество строк, имеющих квазиортогональную структуру и, по меньшей мере, две строки, имеющие ортогональную структуру. Например, матрица F включает в себя, по меньшей мере, 15 строк, удовлетворяющих квазиортогональной структуре. В столбцах, отличных от столбцов f, соответствующих встроенным выколотым битам в любых двух смежных строках в 15 строках, в одном и том же столбце имеется не более одного ненулевого элемента, то есть, матричный блок, включающий в себя столбцы, отличные от столбцов, соответствующих встроенным выколотым битам, по меньшей мере, в 15 строках в матрице F, имеет ортогональную структуру. Матрица F может дополнительно включать в себя от 10 до 20 строк, удовлетворяющих ортогональной структуре. В этих строках не более одного ненулевого элемента в одном и том же столбце в любых двух соседних строках. Чтобы быть точным, во встроенном выколотом столбце также есть не более одного ненулевого элемента.

Например, используя базовый граф 30a в качестве примера, последние 10 строк в матрице F имеют ортогональную структуру, веса девяти строк равны 3, и веса одной строки равны 2. Распределение веса столбца матрицы F может быть: вес одного столбца равен 16, вес одного столбца равен 18, вес одного столбца равен 11, вес двух столбцов равен 10, вес одного столбца равен 9, вес одного столбца равен 8, вес одного столбца равен 7, вес одного столбца равен 6, вес двух столбцов равен 4, вес одного столбца равен 3 и вес двух столбцов равен 2. Если mA> 4, веса других столбцов в матрица F равны 0.

Используя mA = 7 в качестве примера, в примере матрицы F в базовом графе 30a, веса строк матрицы F составляют 5, 3, 4, 4, 4, 3, 4, 4, 3, 4, 4, 3, 3, 3, 3, 2, 3, 3, 2, 4, 2, 3, 2, 4, 2, 3, 3, 3, 3, 3, 2, 3, 3, 3 и 3 в последовательности.

Поскольку подматрица E является единичной матрицей, веса строк в базовом графе 30a составляют соответственно 8, 10, 8, 10, 4, 6, 6, 6, 4, 5, 5, 5, 4, 5, 5, 4, 5, 5, 4, 4, 4, 4, 3, 4, 4, 3, 5, 3, 4, 3, 5, 3, 4, 4, 4, 4, 4, 4, 3, 4, 4, 4 и 4.

По-прежнему используя mA = 7 в качестве примера, если mD = 15, подматрица D в базовом графе LDPC кода может включать в себя 15 строк и 17 столбцов. Подматрица D может быть матрицей, включающей строки от 0 до строки 14 в матрице F в базовом графе 30a, то есть, строки от 7 до строки 21, и столбцы от 0 до столбца 16 в базовом графе 30a. Кодовая скорость, поддерживаемая соответствующим LDPC кодом, составляет 10/30 = 1/3. Таким образом, при кодовой скорости базовый граф LDPC кода соответствует матрице, включающей в себя строки от 0 до строки 21 и от столбца 0 до столбца 31 в базовом графе 30a. Подматрица E представляет собой единичную матрицу, включающую в себя 15 строк и 15 столбцов, и подматрица C представляет собой нулевую матрицу, включающую в себя 7 строк и 15 столбцов.

Если mD = 25, подматрица D в базовом графе LDPC кода имеет 25 строк и 17 столбцов. Подматрица D может быть матрицей, включающей в себя строки от 0 до строки 24 в матрице F в базовом графе 30a, то есть, строки от 7 до строки 31 и столбцы от 0 до столбца 16 в базовом графе 30a. Кодовая скорость, поддерживаемая соответствующим LDPC кодом, составляет 10/40 = 1/4. Таким образом, при кодовой скорости базовый граф LDPC кода соответствует матрице, включающей в себя строки от 0 до строки 31 и от столбца 0 до столбца 41 в базовом графе 30a. Подматрица E представляет собой единичную матрицу, включающую в себя 25 строк и 25 столбцов, и подматрица C представляет собой нулевую матрицу, включающую в себя 7 строк и 25 столбцов.

Остальные могут быть выведены по аналогии, и подробности не описаны по одному.

Следует отметить, что в базовом графе и базовой матрице LDPC кода строки могут переключаться друг с другом, и столбцы также могут переключаться друг с другом. Например, в базовом графе 30a строка 34 может быть переключена строкой 36, и столбец 44 может быть переключен столбцом 45. В другом примере, подматрица D включает в себя строки mD в матрице F, строки mD могут не переключаться, или может быть переключена одна или несколько строк mD, подматрица E все еще имеет диагональную структуру, и в подматрице E не выполняется ни перестановка строк, ни перестановка столбцов. Например, строка 27 переключается со строкой 29 в матрице F подматрица D включает в себя строки в матрице F, и подматрица E все еще имеет диагональную структуру. Матрица F является квазиортогональной матрицей перед перестановкой строк и все еще является квазиортогональной матрицей, выполняя перестановку строк. Понятно, что, если базовый граф или базовая матрица включает в себя подматрицу D, когда столбцы в базовой матрице переключаются, соответствующие столбцы в подматрице D также необходимо переключать.

Как показано на фиг. 3b-1 - фиг. 3b-8 , базовые матрицы 30b-1-30b-8 являются примерами множества базовых матриц базового графа 30a. Ненулевой элемент в строке i и столбце j в базовом графе 30a имеет одинаковую позицию в каждой из базовых матриц с 30b-1 по 30b-8, и значение ненулевого элемента представляет собой величину Vi,j сдвига. Нулевой элемент в матрице сдвига представлен с помощью –1 или нуля. Часть, соответствующая подматрице D в базовой матрице, может включать в себя строки mD в матрице сдвига матрицы F, и значения mD могут быть выбраны в соответствии с различными кодовыми скоростями. Матрица сдвига, соответствующая подматрице D, включает в себя mD строк в матрице сдвига матрицы F.

В возможной реализации матрица сдвига матрицы F может быть матрицей, включающей строки от 7 до строки 41 и столбцы от 0 до столбца 16 в любой из матриц с 30b-1 по 30b-8, или матрицу, полученную путем выполнения перестановка строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в любой из матриц с 30b-1 по 30b-8; или матрица сдвига матрицы F может включать в себя матрицу, включающую в себя строки от 4 до строки 41 и от столбца 0 до столбца 14 в любой из матриц с 30b-1 по 30b-8, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в любой из матриц с 30b-1 по 30b-8.

Для поддержки разных длин блоков, для LDPC кода требуются разные коэффициенты Z поднятия. Например, коэффициенты поднятия Z = a × 2j, где а є {2, 3, 5, 7, 9, 11, 13, 15} может быть разделено на восемь наборов, показанных в таблице 1:

Таблица 1

Для обеспечения производительности LDPC кода при разных длинах блоков на основании наборов разных коэффициентов Z поднятия могут использоваться отдельные матрицы, соответствующие наборам различных коэффициентов Z поднятия.

В возможной реализации:

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 1, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-1, или матрицей, полученной посредством выполнения перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-1; или матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 4 по строки 41 и столбцы от 0 по столбцы 14 в 30b-1, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строки 41 и столбец от 0 до столбца 14 в 30b-1. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-1, или матрицей, полученной путем выполнения перестановки строк/столбцов для матрицы, показанной в 30b-1.

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 2, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-2, или матрицей, полученной посредством выполнения перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-2; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-2, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строку 41 и столбец от 0 до столбца 14 в 30b-2. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-2, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-2.

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 3, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-3, или матрицей, полученной посредством перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-3; или матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 4 по строки 41 и столбцы от 0 по столбцы 14 в 30b-3, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строки 41 и столбец от 0 до столбца 14 в 30b-3. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-3, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-3.

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 4, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-4, или матрицей, полученной посредством перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-4; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-4, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строку 41 и столбец от 0 до столбца 14 в 30b-4. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-4, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-4.

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 5, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-5, или матрицей, полученной посредством выполнение перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-5; или матрица сдвига матрицы F может быть матрицей, включающей в себя строки от 4 по строки 41 и столбцы от 0 по столбцы 14 в 30b-5, или матрицей, полученной путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строки 41 и столбец от 0 до столбца 14 в 30b-5. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-5, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-5.

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 6, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-6, или матрицей, полученной посредством перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-6; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-6, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строку 41 и столбец от 0 до столбца 14 в 30b-6. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной на 30b-6, или матрицей, полученной путем выполнения перестановки строк/столбцов на матрице, показанной на 30b-6.

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 7, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-7, или матрицей, полученной посредством перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-7; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-7, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строку 41 и столбец от 0 до столбца 14 в 30b-7. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-7, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-7.

Если коэффициент Z поднятия является одним коэффициентом поднятия в наборе 8, матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 7 по строку 41 и столбец от 0 по столбец 16 в 30b-8, или матрицей, полученной посредством перестановки строк/столбцов в матрице, включающей в себя строки от 7 по строку 41 и столбцы от 0 по столбец 16 в 30b-8; или матрица сдвига матрицы F может быть матрицей, включающей в себя строку от 4 по строку 41 и столбец от 0 по столбец 14 в 30b-8, или матрицу, полученную путем выполнения перестановки строки/столбца в матрице, включающей в себя строки от 4 по строку 41 и столбец от 0 до столбца 14 в 30b-8. Соответственно, базовая матрица базового графа 30a может быть матрицей, показанной в 30b-8, или матрицей, полученной путем выполнения перестановки строк/столбцов в матрице, показанной в 30b-8.

Например, значение коэффициента Z поднятия определяют на основании длины K входной последовательности. Например, если длина входной последовательности равна K, минимальное значение, которое соответствует 10× Z≥K, может быть определено из множества коэффициентов поднятия, определенных в системе и используемых в качестве значения коэффициента поднятия матрицы. Кроме того, соответствующая базовая матрица может быть выбрана в соответствии с определенным коэффициентом поднятия.

Аналогично, строки в базовой матрице также могут переключаться друг с другом, и столбцы в базовой матрице также могут переключаться друг с другом. Если, выполняют, по меньшей мере, одну из перестановок строк или столбцов на базовом графе, такая же перестановка также выполняется на соответствующих строках или столбцах в базовой матрице.

Понятно, что в настоящем изобретении квазиортогональная структура не ограничена только двумя соседними строками. Матрица, включающая в себя квазиортогональную структуру, может альтернативно быть разработана так, чтобы включать в себя множество групп, каждая группа включает в себя, по меньшей мере, две строки, например, 3 строки или 4 строки, и строки, включенные в каждую группу, являются квазиортогональными.

На диаграмме кривой производительности, показанной на фиг..4 LDPC 1 указывает, что LDPC код получают путем кодирования на основании базовой матрицы, соответствующей базовому графу 30a, и LDPC 2 указывает обычно используемый LDPC код, используемый для сравнения. Горизонтальная координата указывает длину последовательности информационных битов и единицей длины является бит. Вертикальная координата представляет отношение сигнал/шум символа (Es/N0). Кривые производительности указывают рабочие характеристики отношения сигнал/шум символа для LDPC 1 и LDPC 2 в случае различной длины последовательности информационных битов, когда значение BLER равно 0,0001. Можно узнать, что при одном и том же BLER отношение сигнал/шум символа LDPC 1 меньше, чем LDPC 2, в случае разных длин последовательностей информационных битов, то есть, производительность LDPC 1 лучше, чем LDPC. 2.

В способе кодирования, предусмотренном в варианте осуществления настоящего изобретения, кодер кодирует входную последовательность с использованием LDPC матрицы. Базовый граф LDPC матрицы может быть любым базовым графом в вышеприведенных примерах, и базовая матрица LDPC матрицы может быть любой базовой матрицей в вышеприведенных примерах. Входная последовательность кодера может быть последовательностью информационных битов или может быть последовательностью информационных битов, полученной посредством, по меньшей мере, одного типа следующей обработки: присоединение CRC битов или вставка битов-заполнителей.

Кроме того, способ включает в себя: определение коэффициента Z поднятия. Значение коэффициента Z поднятия может быть определено на основе длины K входной последовательности. Последовательность информационных битов также может иногда называться кодовым блоком (code block) и может быть получена посредством сегментации кодового блока в транспортном блоке. Если длина последовательности информационных битов равна K, то минимальное значение, которое соответствует 10 × Z≥K, может быть определено из множества коэффициентов поднятия, определенных в системе, как значение коэффициента Z поднятия. Например, если K = 128 и коэффициенты поднятия, определенные в системе, включают в себя коэффициенты поднятия в наборах в таблице 1, например, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16 , 18, 20, 22, 24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144 160, 176, 192, 208, 224, 240 и 256, может быть определено, что Z равен 13 и находится в наборе 7. Следует отметить, что в данном документе представлены только примеры, и примеры не составляют ограничение.

В другом возможном варианте Kb может быть количеством столбцов, соответствующих информационным битам в базовой матрице LDPC кода. В поддерживаемом наборе коэффициентов поднятия минимальное значение Z0, которое удовлетворяет Kb ∙ Z0≥K, может быть определено, как значение коэффициента Z поднятия. На базовом графе 30a число столбцов Kbmax столбцов, соответствующих информационным битам, равно 10, и предполагают, что набор коэффициентов поднятия, поддерживаемый базовым графом 30a, равен {24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}.

Если длина K входной последовательности составляет 529 битов, Z равен 26. Если длина K входной последовательности составляет 5000 битов, Z равен 240. Следует отметить, что в настоящем документе представлены только примеры, и примеры не является ограничением.

В другом примере значение Kb также может изменяться со значением K, но значение Kb не превышает количество столбцов, соответствующих информационным битам в базовой матрице LDPC кода. Например, для Кb могут быть установлены различные пороговые значения.

Возможной реализацией может быть следующая: следует отметить, что пороговые значения 640, 560 или 192 в данном документе являются только примерами. Другие значения могут быть разработаны в соответствии с требованиями к проектированию системы.

если (K> 640), Kb = 10;

или же если (K> 560), Kb = 9;

или же если (K> 192), Kb = 8;

еще Кб = 6; завершение

При этом, коэффициент Z поднятия может быть определен кодером в соответствии с длиной K входной последовательности или может быть получен кодером из других объектов (таких как процессор).

В возможной реализации значение бита-заполнителя может быть нулевым, или 0, или другими значениями, определенными в системе. После кодирования биты-заполнители могут быть идентифицированы и не отправлены. Настоящее изобретение этим не ограничивается.

Кодирование кодером входной последовательности с использованием LDPC матрицы H может быть кодированием входной последовательности с использованием LDPC матрицы H, соответствующей коэффициенту Z поднятия.

В возможной реализации входная последовательность представляет собой c = {c0, c1, c2,…, cK-1}, длина входной последовательности c равна K, и выходная последовательность, полученная после кодирования входной последовательности c кодером является d = {d0, d1, d2,…, d N-1}, где K является целым числом больше 0 и K может быть целым кратным коэффициенту Z поднятия.

Выходная последовательность d включает в себя биты K0 во входной последовательности c и биты четности в последовательности w битов четности, где K0 представляет собой целое число, большее 0 и меньшее или равное K. Длина последовательности w битов четности равна N- K0, где w = {w0, w1, w2,…, wN-K0-1}.

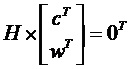

Последовательность w битовой четности и входная последовательность c соответствуют формуле (1):

где cT=[c0, c1, c2, …, cK-1]T, cT является транспонированным вектором вектора, включающего в себя биты во входной последовательности, и wT=[w0, w1, w2, …, wN-K0-1]T , wT является транспонированным вектором вектора, включающего в себя биты в битовой последовательности четности, где 0T является вектором столбца и значения всех элементов 0T равны 0.

H представляет собой LDPC матрицу, полученную на основе любого базового графа, описанного в предшествующих вариантах осуществления, базовый граф H имеет m строк и n столбцов и может быть базовым графом 30a, упомянутым в предшествующих вариантах осуществления.

В реализации базовый граф H включает в себя p встроенных выколотых столбцов, где p представляет собой целое число, большее или равное 0, и информационные биты, соответствующие p встроенным выколотым столбцам, не выводятся, и выходная последовательность не включает в себя информационные биты, соответствующие p встроенным выколотым столбцов. В этом случае, K0 = K- p ∙ Z. Например, если p = 2, K0 = K- 2∙Z и длина последовательности w битов четности равна N + 2 ∙ Z - K. Если в кодировании участвуют p встроенные выколотые столбцы, то K0 = K и длина последовательности w битов четности равна N - K.

Соответственно, H может иметь M строк и (N + p Z) столбцов или M строк и N столбцов, и размер базового графа H равен: m = M / Z строк и n =

Базовый граф LDPC матрицы H может быть представлен как [HBG HBG, EXT], где

В возможной реализации,

В другой возможной реализации, поскольку столбцы с 14 по 16 являются столбцами с весом 1, и ненулевые элементы в этих столбцах находятся в строках с 4 по 6, поэтому mc = 6, 0≤nc≤36 и количество столбцов в HBG2 составляет 16; или mc = 5, 0≤nc≤37, и количество столбцов в HBG2 равно 15; или mc = 4, 0≤nc≤38, и количество столбцов в HBG2 равно 14.

Соответственно, LDPC матрица H может быть представлена как H = [H1 H2].

H1 может быть получена путем замены каждого нулевого элемента в HBG нулевой матрицей размером Z × Z и замены каждого ненулевого элемента матрицей hi,j круговой перестановки размера Z × Z, где матрицу hi,j круговой перестановки получают путем кругового сдвига единичной матрицы размера Z × Z вправо Pi,j раз, и hi,j также может быть представлена I(Pi,j), где i является индексом строки и j является индексом столбца. В возможном варианте Pi,j = mod (Vi,j, Z), где Vi,j является ненулевым элементом в строке i и столбце j в базовой матрице, соответствующей индексу набора коэффициентов поднятия, соответствующему Z.

Н2 может быть получена путем замены каждого нулевого элемента в HBG, EXT нулевой матрицей размером Z × Z и замены каждого ненулевого элемента на единичную матрицу размера Z × Z.

Кодер может выполнять кодирование и вывод множеством способов. Базовый граф 30a, упомянутый в предшествующих вариантах осуществления, далее используют в качестве примера для описания. Базовый граф имеет максимум 42 строки и максимум 52 столбца и включает в себя два встроенных выколотых столбца. Для простоты описания в настоящем изобретении базовый граф, который имеет наибольшее количество строк и наибольшее количество столбцов, иногда называют полным базовым графом.

Способ 1

Кодирование выполняют на основании полного базового графа, так что может быть получено как можно больше битов четности. В этом случае, m = 42 и n = 52, которые соответствуют от строки 0 до строки 41 и от столбца 0 до столбца 51 в предшествующем базовом графе.

Соответственно, для LDPC матрицы Н М равно 42 × Z и, если выходная последовательность включает в себя информационные биты, соответствующие столбцам, соответствующим встроенным выколотым битам, N = (42 + Кb) × Z; или, если выходная последовательность не включает в себя 2 × Z информационных битов, соответствующих встроенным выколотым битам, N = (40 + Кb) ∙ Z.

Информационные биты и биты четности, которые должны быть отправлены, могут быть определены из выходной последовательности, сгенерированной кодером во время последующей обработки.

Способ 2

Кодирование выполняют на основании некоторых строк и некоторых столбцов в полном базовом графе. Строки и столбцы могут быть выбраны на основе кодовой скорости, подлежащие отправке, или количества информационных битов и количества битов четности, которые должны быть отправлены, или тому подобное, из полного базового графа для кодирования.

Например, кодовая скорость составляет 2/3, m = 7 и n = 17, то есть, кодирование выполняют на основании строки от 0 до строки 6 и столбца от 0 до столбца 16 в вышеупомянутом базовом графе 30a.

Соответственно, для LDPC матрицы H, M=7×Z и, если выходная последовательность включает в себя информационные биты, соответствующие встроенным выколотым столбцам, N = 17 × Z; или, если выходная последовательность не включает в себя информационные биты, соответствующие встроенным выколотым столбцам, N = 15 × Z.

Для другого примера кодовая скорость составляет 5/6, m = 4 и n = 14.

Для другого примера кодовая скорость составляет 1/5, m = 42 и n = 52.

Можно узнать, что размер базового графа H составляет 4≤m≤42 и 14≤n≤52. Соответственно, для LDPC матрицы H, 4×Z≤M≤42×Z и (4 + Кb)×Z≤N≤ (42+Кb)×Z.

Например, если Z равно 13 и в наборе 7, кодирование выполняется для входной последовательности с использованием LDPC матрицы, полученной на основе базовой матрицы 3b-7, соответствующей набору 7.

В другой реализации элемент Pi,j в строке i и столбце j базовой матрицы коэффициента Z поднятия также может удовлетворять следующему соотношению:

Vi,j может быть значением сдвига элемента в строке i и столбце j в базовой матрице набора, к которому принадлежит Z, то есть, значением сдвига ненулевого элемента в строке i и столбца j в базовой матрице максимального коэффициента поднятия в наборе, к которому принадлежит Z.

Например, используя пример, в котором Z равен 13, элемент Pi,j в строке i и столбце j в базовой матрице Z удовлетворяет:

Vi,j может быть значением сдвига ненулевого элемента в строке i и столбце j в базовой матрице 3b-7.

Следует отметить, что в данном документе представлены только примеры, и примеры не составляют ограничение в настоящем изобретении.

В вышеприведенных реализациях базовой матрицей HB LDPC матрицы H может быть любая базовая матрица, упомянутая в предшествующих вариантах осуществления, или базовая матрица, полученная путем выполнения перестановки строк, или перестановки столбцов, или перестановки строк и перестановок столбцов на любой базовой матрице, описанной выше. Базовый граф LDPC матрицы включает в себя, по меньшей мере, подматрицу A и подматрицу B и может дополнительно включать в себя подматрицу C, подматрицу D и подматрицу E. Описание каждой подматрицы может быть сделано со ссылкой на описания в вышеприведенных вариантах осуществления, и подробности не описано здесь снова. Конечно, базовая матрица HB может альтернативно быть базовой матрицей, базовый граф которой такой же, как базовый граф 30a. Настоящее изобретение этим не ограничивается.

В возможной реализации базовая матрица HB LDPC кода может быть сохранена в памяти, и кодер получает LDPC матрицу, соответствующую коэффициенту Z поднятия, для кодирования входной последовательности. В другой возможной реализации, поскольку существует множество базовых матриц HB LDPC кода, относительно большое пространство памяти занято, когда базовые матрицы хранятся в соответствии с матричными структурами. Базовый граф LDPC кода может альтернативно храниться в памяти, и значения сдвига ненулевых элементов в базовых матрицах могут храниться построчно или столбец за столбцом, и затем LDPC матрица может быть получена на основе базового графа и значения сдвига базовой матрицы, соответствующие коэффициенту Z поднятия.

Базовый граф может указывать позиции ненулевых элементов в каждой базовой матрице. В другой возможной реализации сохранение базового графа может сохранять позиции ненулевых элементов в базовом графе. Позиция ненулевого элемента может указываться строкой и столбцом, в котором расположен ненулевой элемент, например, позицией столбца ненулевого элемента в строке или позицией строки ненулевого элемента в столбце. В другой возможной реализации сохранение базового графа также может сохранять позиции нулевых элементов в базовом графе. Аналогично, позиция нулевого элемента может также указываться строкой и столбцом, в котором расположен нулевой элемент, например, позицией столбца нулевого элемента в строке или позицией строки нулевой элемент в столбце. Следовательно, позиции ненулевых элементов могут быть получены путем исключения позиций нулевых элементов. Следует отметить, что в настоящем документе представлены только примеры, и примеры не составляют ограничение в настоящем изобретении.

В реализации параметры, относящиеся к базовому графу или базовой матрице, могут быть выражены в таблице. Например, относящиеся параметры или таблицы могут храниться в одной или нескольких ячейках памяти. Соответствующие параметры, такие как индекс строки в базовом графе или базовой матрице и индекс столбца, в котором расположен ненулевой элемент, считываются из памяти, чтобы получить базовый граф или базовую матрицу. Возможно, могут быть сохранены вес строки каждой строки и значение сдвига ненулевого элемента в каждой строке.

В качестве примера для описания используют фиг. 3а. Описание другого базового графа или базовой матрицы, представленной в настоящем документе, может быть понятно со ссылкой на аналогичное описание реализации.

Например, параметры в базовом графе 30a могут быть выражены в таблице 2.

Таблица 2

(индекс строки)

(степень строки/вес строки)

(позиция столбца ненулевого элемента в строке)

Следует отметить, что в данном документе представлены только примеры, и примеры не являются ограничением. Ассоциированные параметры другого базового графа или базовой матрицы, представленные в настоящем описании, также могут быть выражены в аналогичной таблице. Следует понимать, что вышеупомянутые базовый граф 30a и таблица 2 предназначены для облегчения понимания структуры базового графа и базовой матрицы. Формы представления базового графа и базовой матрицы не ограничиваются только формами представления вышеупомянутого базового графа 30a и таблицы 2. Могут быть использованы другие возможные варианты.