Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с малыми значениями э.д.с. смещения нуля (ОУ) и повышенным коэффициентом усиления по напряжению).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах [1-45], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (HA2520, HA5190, AD797, AD8631, AD8632, OP90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ, на их модификации выдано более 50 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

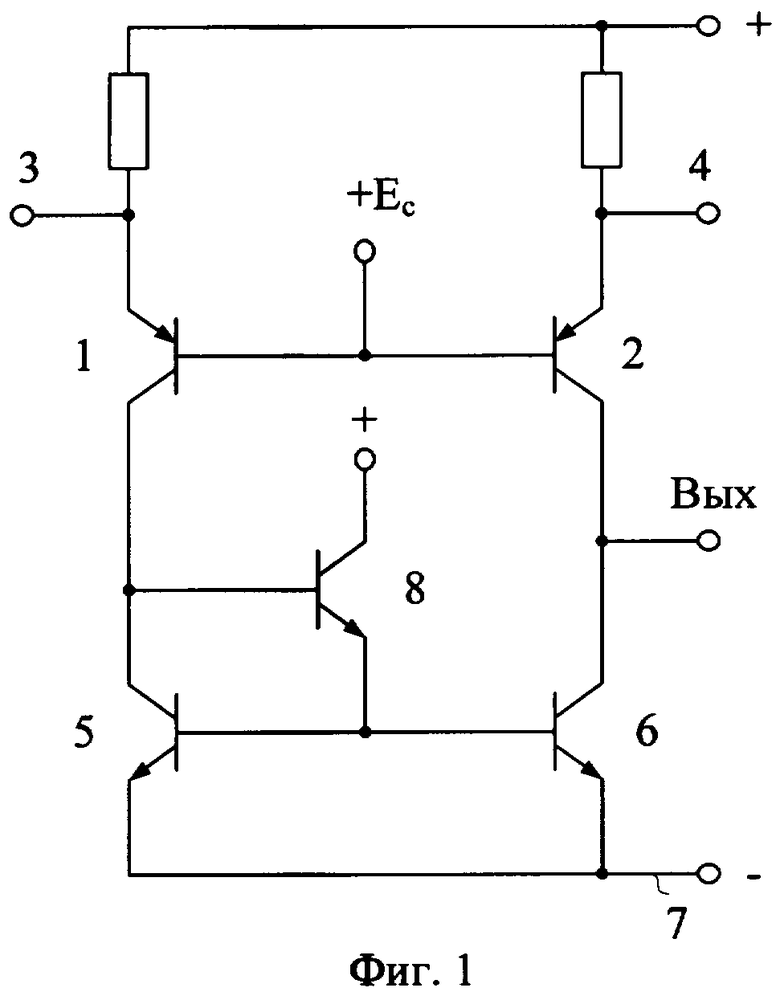

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте фирмы Analog Devices (США) №6.483.382, фиг.1, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых являются токовыми входами дифференциального усилителя 3 и 4, первый 5 и второй 6 выходные транзисторы с объединенными базами, эмиттеры которых связаны с шиной 7 источника питания, коллектор первого выходного транзистора 5 соединен с коллектором первого 1 входного транзистора, коллектор второго выходного транзистора 6 соединен с коллектором второго 2 входного транзистора, причем в схеме имеется вспомогательный транзистор 8.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он имеет сравнительно большое напряжение смещения нуля (Uсм) (единицы милливольт), а также невысокий коэффициент усиления по напряжению (Ку). Это отрицательно сказывается на параметрах аналоговых устройств на его основе, например операционных усилителей.

Основная цель предполагаемого изобретения состоит в уменьшении Uсм и повышении Ку.

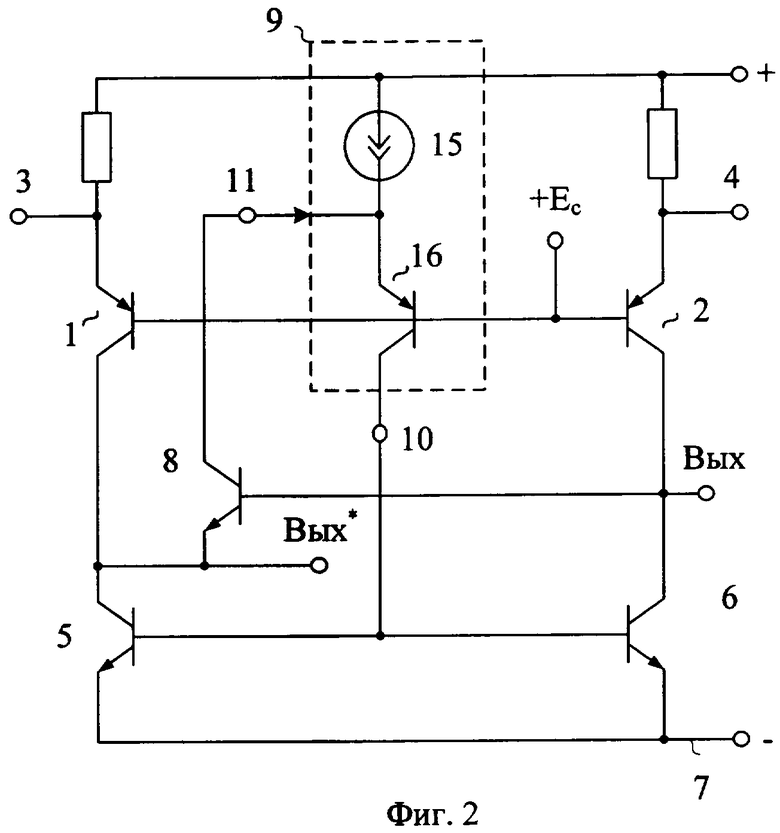

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе, фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых являются токовыми входами дифференциального усилителя 3 и 4, первый 5 и второй 6 выходные транзисторы с объединенными базами, эмиттеры которых связаны с шиной 7 источника питания, коллектор первого выходного транзистора 5 соединен с коллектором первого 1 входного транзистора, коллектор второго выходного транзистора 6 соединен с коллектором второго 2 входного транзистора, вспомогательный транзистор 8, предусмотрены новые элементы и связи - в схему введен неинвертирующий усилитель 9, выход которого 10 связан с объединенными базами первого 5 и второго 6 выходных транзисторов, вход 11 подключен к коллектору вспомогательного транзистора 8, коллектор первого выходного транзистора 5 соединен с эмиттером вспомогательного транзистора 8, база которого подключена к коллектору второго 6 выходного транзистора.

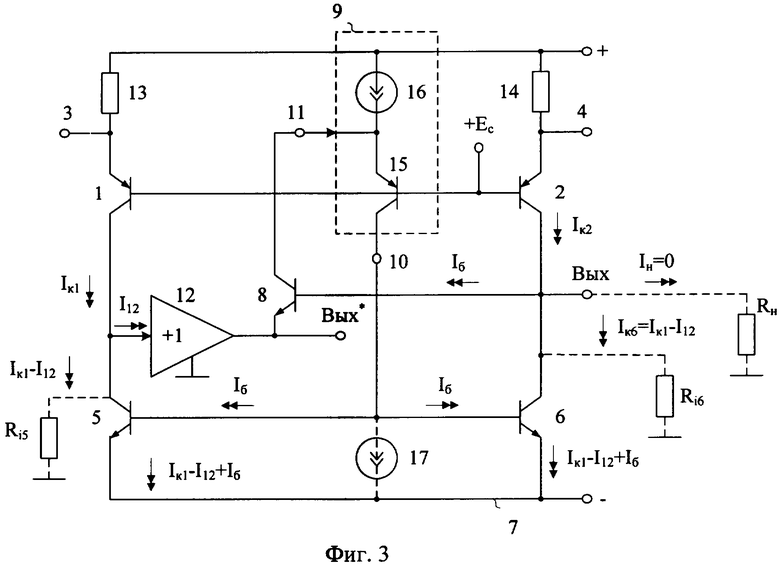

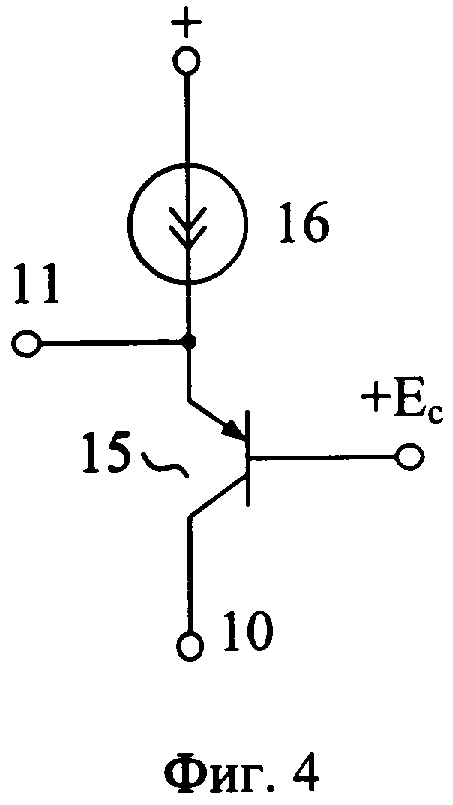

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1, п.3 формулы изобретения. На фиг.3 показана схема заявляемого устройства в соответствии с п.2 и п.3 формулы изобретения. На фиг.4 изображен вариант построения неинвертирующего усилителя 9, соответствующего п.3 формулы изобретения.

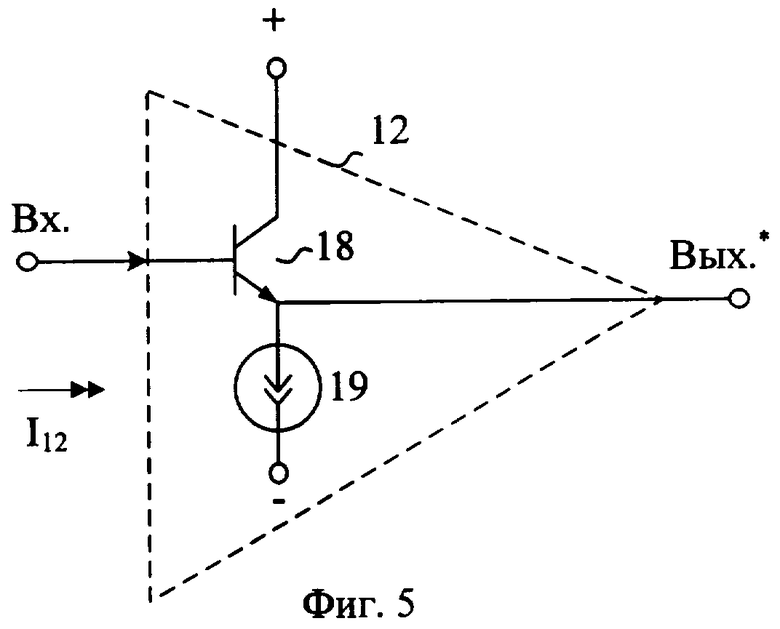

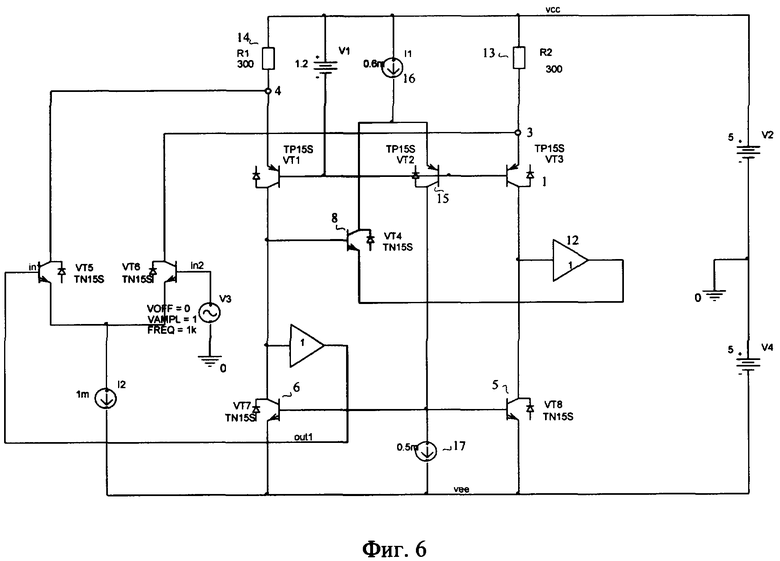

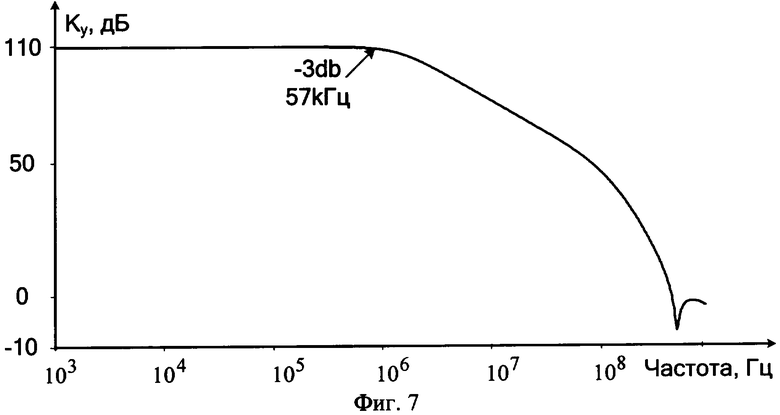

На фиг.5 изображен вариант построения буферного усилителя 12. На фиг.6 показана схема фиг.3 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.7 - результаты расчета ее амплитудно-частотной характеристики Ку.

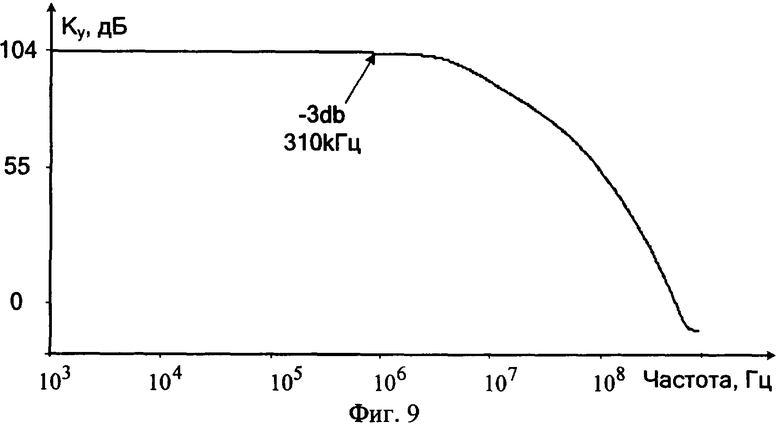

На фиг.8 изображен заявляемый КДУ фиг.3 в среде компьютерного моделирования PSpice для случая, когда буферный усилитель выполнен по схеме фиг.5, а на фиг.9 - результаты расчета его амплитудно-частотной характеристики Ку.

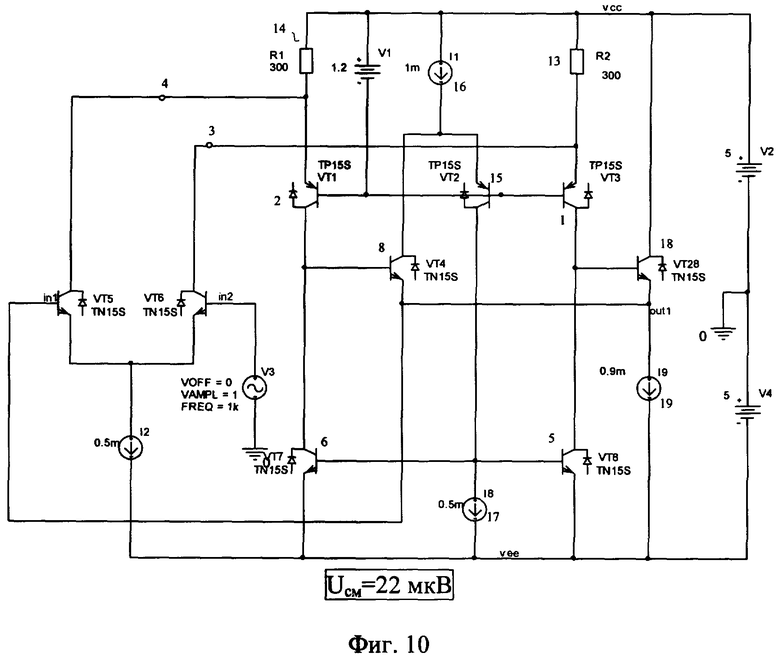

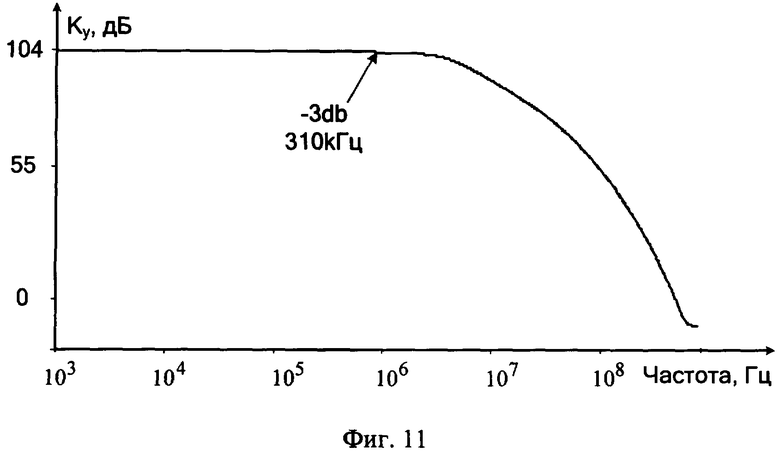

На фиг.10 изображен заявляемый КДУ фиг.3 (п.4 формулы изобретения) в среде компьютерного моделирования PSpice, а на фиг.11 - результаты расчета его амплитудно-частотной характеристики Ку.

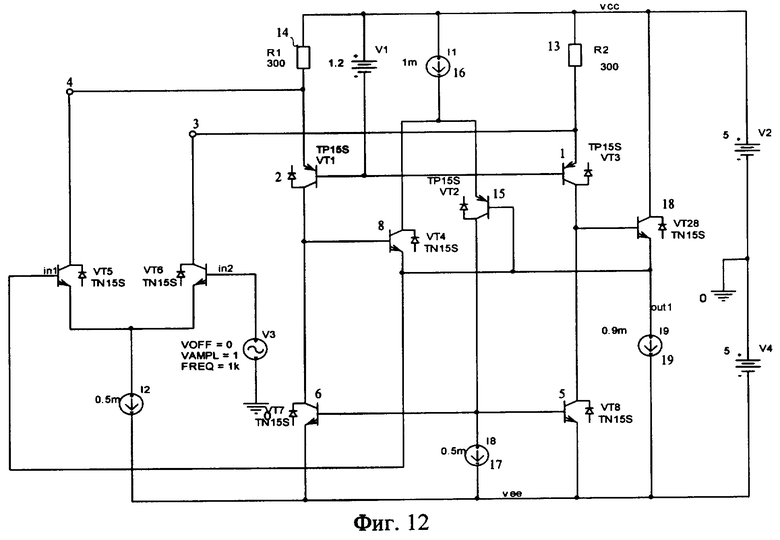

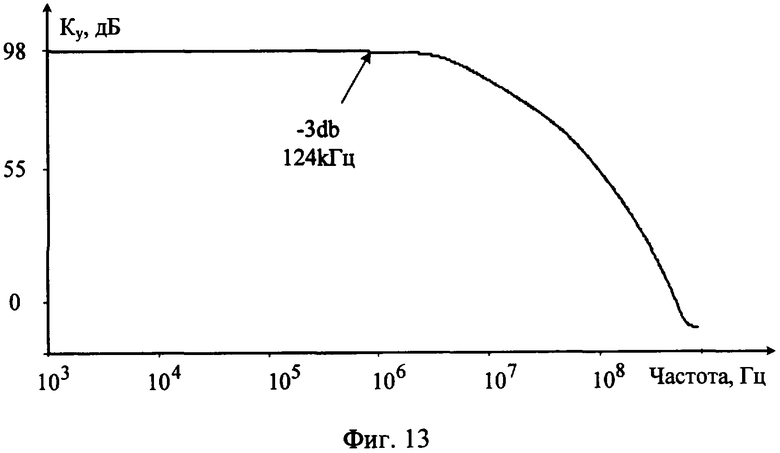

На фиг.12 представлена схема заявляемого КДУ фиг.3, соответствующая п.2 формулы изобретения для случая, когда буферный усилитель 12 выполнен в соответствии с фиг.5, а неинвертирующий усилитель тока 9 реализован по другой схеме. На фиг.13 - результаты расчета амплитудно-частотной характеристики КДУ фиг.12.

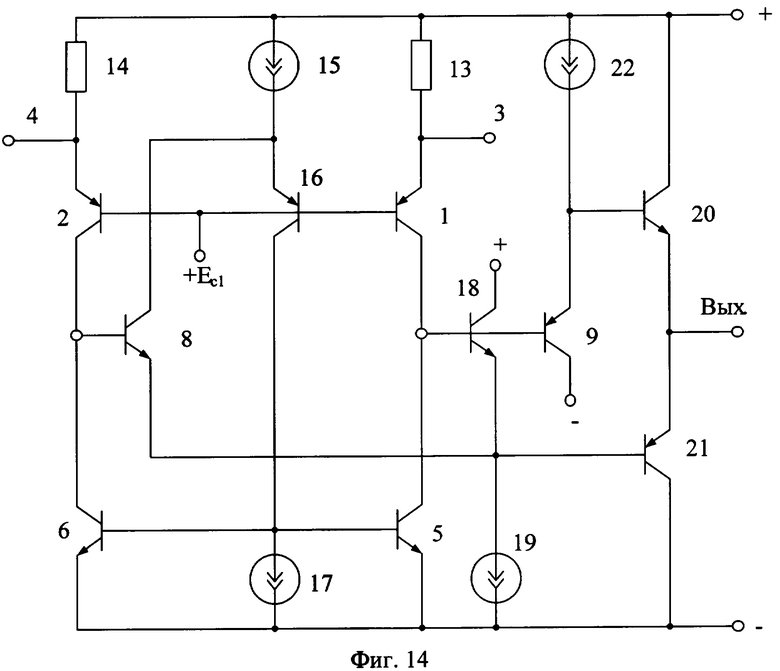

Фиг.14 иллюстрирует другой частный вариант построения буферного усилителя 12 с использованием транзистора 18 в структуре классического комплементарного выходного каскада операционного усилителя на транзисторах 18-21 и двухполюсниках 22, 19.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых являются токовыми входами дифференциального усилителя 3 и 4, первый 5 и второй 6 выходные транзисторы с объединенными базами, эмиттеры которых связаны с шиной 7 источника питания, коллектор первого выходного транзистора 5 соединен с коллектором первого 1 входного транзистора, коллектор второго выходного транзистора 6 соединен с коллектором второго 2 входного транзистора, вспомогательный транзистор 8. В схему введен неинвертирующий усилитель 9, выход которого 10 связан с объединенными базами первого 5 и второго 6 выходных транзисторов, вход 11 подключен к коллектору вспомогательного транзистора 8, коллектор первого выходного транзистора 5 соединен с эмиттером вспомогательного транзистора 8, база которого подключена к коллектору второго 6 выходного транзистора.

На фиг.3 в соответствии с п.2 формулы изобретения коллектор первого выходного транзистора 5 соединен с эмиттером вспомогательного транзистора 8 через буферный усилитель 12. В частном случае в эмиттерную цепь транзисторов 1 и 2 могут быть включены резисторы 13, 14. В ряде случаев на входы 3 и 4 может подаваться потенциальный сигнал, например, от входных эмиттерных повторителей.

Кроме этого на фиг.3, а также фиг.4 в соответствии с п.3 формулы изобретения неинвертирующий усилитель 9 выполнен на основе дополнительного транзистора 15 с включением по схеме с общей базой и двухполюснике 16, причем эмиттер дополнительного транзистора 15 является входом 11 неинвертирующего усилителя тока 9, а его коллектор - выходом 10 неинвертирующего усилителя 9.

На фиг.5 в соответствии с п.4 формулы изобретения буферный усилитель 12 реализован в виде эмиттерного повторителя, содержащего входной транзистор 18 и токостабилизирующий двухполюсник 19.

Рассмотрим работу заявляемого каскодного дифференциального усилителя на примере анализа схемы фиг.3. При этом будем считать, что на входы 3 и 4 КДУ подаются токовые сигналы, например, от классического параллельно-балансного каскада (фиг.6.).

Условие получения близкого к нулю напряжения смещения нуля операционных усилителей на базе КДУ фиг.3 является равенство токов коллектора транзистора 2 и транзистора 6: Iк2= Iк6, то есть выполнение условия

где Iк1 - коллекторный ток транзистора 1.

Если обозначить входной ток буферного усилителя 12 через I12, а ток базы всех n-p-n транзисторов как Iб, то в соответствии с основными токовыми соотношениями в транзисторе в элементах схемы фиг.3 установятся токи, показанные на фиг.3.

Поэтому для обеспечения равенства

необходимо, чтобы

Последнее условие легко реализуется за счет построения буферного усилителя 12 на базе эмиттерного повторителя фиг.5. В результате Uсм, обусловленное структурными ошибками усиления сигналов, существенно уменьшается. Данный вывод подтверждается данными компьютерного моделирования (фиг.8, фиг.10) - здесь систематическая составляющая напряжения смещения нуля измеряется микровольтами (12 мкВ, 22 мкВ).

Повышение Ку на один-два порядка реализуется в схеме фиг.3 за счет взаимной компенсации влияния на Ку сравнительно больших выходных проводимостей транзисторов 5 и 6, которые зависят от их напряжения Эрли (Uэ) и статических токов коллектора:

В результате эквивалентное сопротивление нагрузки в КДУ фиг.3 повышается на один-два порядка, что во столько же раз повышает коэффициент Ку (в сравнении с КДУ-прототипом, фиг.1).

Представленные на чертежах фиг.7, фиг.9, фиг.11, фиг.13 результаты компьютерного моделирования подтверждают преимущества заявляемых схем - в отличие от прототипа новая схема обеспечивает на порядок более высокое усиление и малое напряжение смещения нуля. Это создает условия для улучшения многих параметров аналоговых микросхем на ее основе.

Источники информации

1. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. Л., 1979, 148 с.

2. Матавкин В.В. Быстродействующие операционные усилители. М.: Радио и связь, 1989, с.74, рис.4.15, стр.98, рис.6.7.

3. Патент США №6.218.900, фиг.1.

4. Патентная заявка US 2002/0196079.

5. Патент США №6.788.143.

6. Патент США №3.644.838, фиг.2.

7. Патент США Re 30.587.

8. Патент ЕР 1.227.580.

9. Патент США №6.714.076.

10. Патент США №5.786.729.

11. Патент США №5.327.100.

12. Патентная заявка US 2004/0090268 A1.

13. Патент США №4.274.061.

14. Патент США №5.422.600, фиг.2.

15. Патент США №6.788.143, фиг.2.

16. Патент США №4.959.622, фиг.1.

17. Патент США №4.406.990, фиг.4.

18. Патент США №5.418.491.

19. Патент США №6.018.268.

20. Патент США №5.952.882.

21. Патент США №4.723.111.

22. Патент США №4.293.824.

23. Патент США №6.580.325.

24. Патент США №6.965.266.

25. Патент США №6.867.643.

26. Патент США №6.236.270.

27. Патент США №5.323.121.

28. Патент США №6.229.394.

29. Патент США №5.734.296.

30. Патент США №5.477.190.

31. Патент США №5.091.701.

32. Патент США №6.717.474.

33. Патент США №6.084.475.

34. Патент США №3.733.559.

35. Патентная заявка US 2005/0001682 A1.

36. Патент США №6.300.831.

37. Патент США №4.600.893.

38. Патентная заявка US 2001/0026193.

39. Патент США №6.529.076.

40. Патент США №6.448.853.

41. Патент США №6.362.686.

42. Патент США №6.501.333.

43. Патент США №6.710.654.

44. Патент США №6.537.919.

45. Патентная заявка US 2003/0090321.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2310268C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390912C2 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319294C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402871C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2455756C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2365029C1 |

| КАСКОДНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2337471C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Технический результат - уменьшение значений э.д.с. смещения нуля и повышение коэффициента усиления по напряжению. Каскодный дифференциальный усилитель (КДУ) содержит первый (1) и второй (2) входные транзисторы, эмиттеры которых являются токовыми входами (3 и 4) КДУ, первый (5) и второй (6) выходные транзисторы с объединенными базами, эмиттеры которых связаны с шиной (7) источника питания, коллектор первого выходного транзистора (5) соединен с коллектором первого (1) входного транзистора, коллектор второго выходного транзистора (6) соединен с коллектором второго (2) входного транзистора, вспомогательный транзистор (8). В схему введен неинвертирующий усилитель (9), выход (10) которого связан с объединенными базами первого (5) и второго (6) выходных транзисторов, вход (11) подключен к коллектору вспомогательного транзистора (8), коллектор первого выходного транзистора (5) соединен с эмиттером вспомогательного транзистора (8), база которого подключена к коллектору второго (6) выходного транзистора. 3 з.п. ф-лы, 14 ил.

1. Каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых являются токовыми входами (3) и (4) дифференциального усилителя, первый (5) и второй (6) выходные транзисторы с объединенными базами, эмиттеры которых связаны с шиной (7) источника питания, коллектор первого выходного транзистора (5) соединен с коллектором первого (1) входного транзистора, коллектор второго выходного транзистора (6) соединен с коллектором второго (2) входного транзистора, вспомогательный транзистор (8), отличающийся тем, что в схему введен неинвертирующий усилитель (9), выход которого (10) связан с объединенными базами первого (5) и второго (6) выходных транзисторов, вход (11) подключен к коллектору вспомогательного транзистора (8), коллектор первого выходного транзистора (5) соединен с эмиттером вспомогательного транзистора (8), база которого подключена к коллектору второго (6) выходного транзистора.

2. Устройство по п.1, отличающееся тем, что коллектор первого выходного транзистора (5) соединен с эмиттером вспомогательного транзистора (8) через буферный усилитель (12).

3. Устройство по п.1, отличающееся тем, что неинвертирующий усилитель (9) выполнен на основе дополнительного транзистора (15) с включением по схеме с общей базой и двухполюснике (16), причем эмиттер дополнительного транзистора (15) является входом (11) неинвертирующего усилителя тока (9), а его коллектор - выходом (10) неинвертирующего усилителя (9).

4. Устройство по п.2, отличающееся тем, что буферный усилитель (12) реализован в виде эмиттерного повторителя, содержащего входной транзистор (18) и токостабилизирующий двухполюсник (19).

| US 6483382 B1, 19.11.2002 | |||

| Операционный усилитель | 1984 |

|

SU1224969A1 |

| Повторитель тока | 1987 |

|

SU1529410A1 |

| US 6144234 A, 07.11.2000 | |||

| US 6304143 B1, 16.10.2001. | |||

Авторы

Даты

2009-09-20—Публикация

2008-02-01—Подача