Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы каскодных усилителей (КУ) на n-р-n (р-n-р) транзисторах, которые стали основой схемотехники более чем 20 серийных ОУ, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 100 патентов в различных странах. Предлагаемое изобретение относится к данному подклассу устройств.

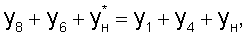

Одной из модификаций каскодных усилителей (КУ) является схема фиг.1, представленная в публикациях [1-12]. Она используется в ОУ ряда зарубежных фирм (НА2539, ОР-90, ОР-42), а также в отечественных микросхемах 140УД30.

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный усилитель, описанный в патенте США №6542030, содержащий первый входной транзистор 1, эмиттер которого соединен с первым входом 2 каскодного усилителя и первым вспомогательным резистором 3, первый двухполюсник нагрузки 4, который соединен с коллектором первого входного транзистора 1 и первым выходом 5 каскодного усилителя, второй вспомогательный транзистор 6, эмиттер которого соединен со вторым вспомогательным резистором 7, база подключена к базе первого входного транзистора 1, а коллектор связан со вторым двухполюсником нагрузки 8.

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно высокий предельный коэффициент усиления по напряжению Kу.max.

Основная цель предлагаемого изобретения состоит в повышении предельного коэффициента усиления по напряжению Kу.max.

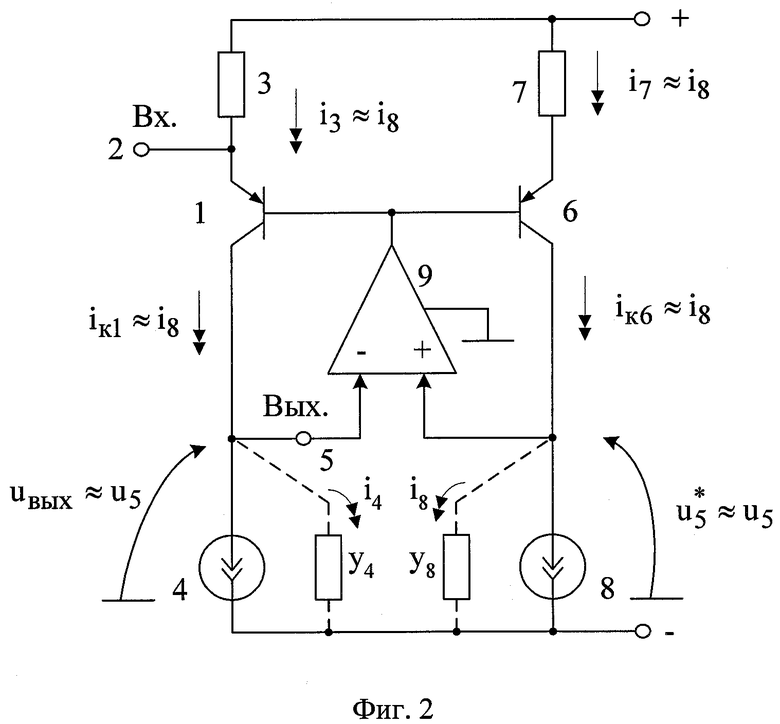

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый входной транзистор 1, эмиттер которого соединен с первым входом 2 каскодного усилителя и первым вспомогательным резистором 3, первый двухполюсник нагрузки 4, который соединен с коллектором первого входного транзистора 1 и первым выходом 5 каскодного усилителя, второй вспомогательный транзистор 6, эмиттер которого соединен со вторым вспомогательным резистором 7, база подключена к базе первого входного транзистора 1, а коллектор связан со вторым двухполюсником нагрузки 8, предусмотрены новые элементы и связи - в схему введен дополнительный дифференциальный каскад 9, неинвертирующий вход которого подключен к коллектору второго входного транзистора 6 и второму двухполюснику нагрузки 8, инвертирующий вход 4 связан с выходом каскодного усилителя 5, а выход подключен к базам первого 1 и второго 6 входных транзисторов.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

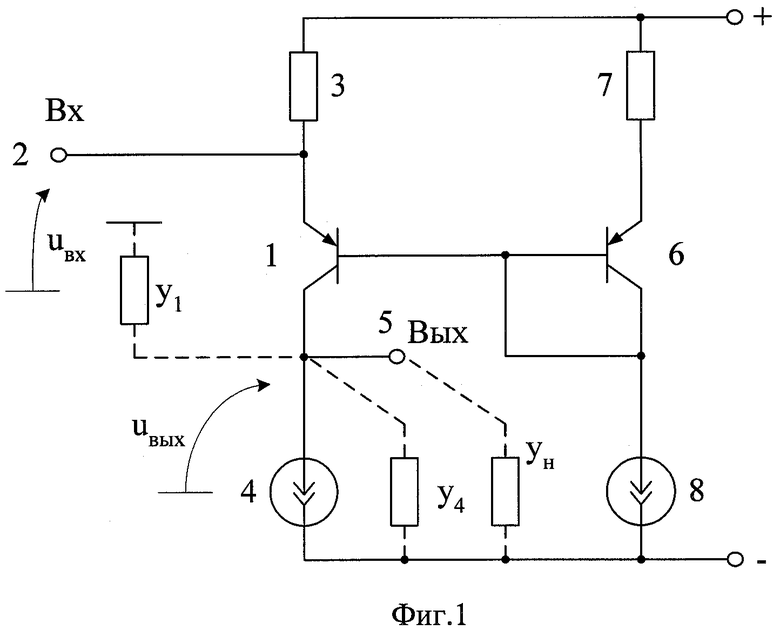

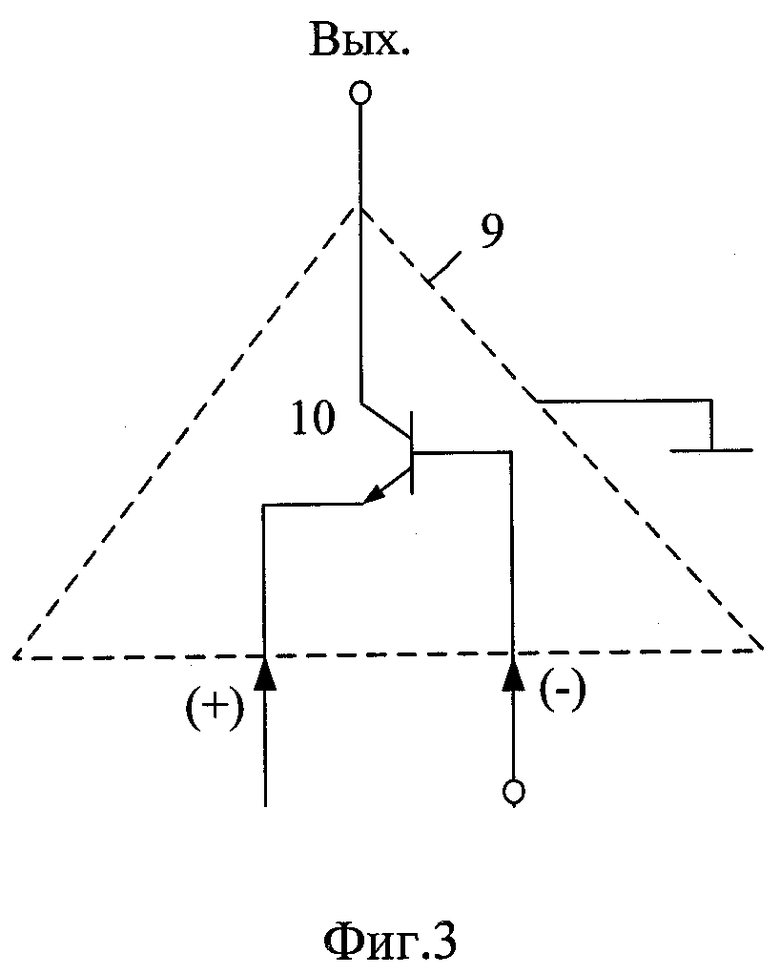

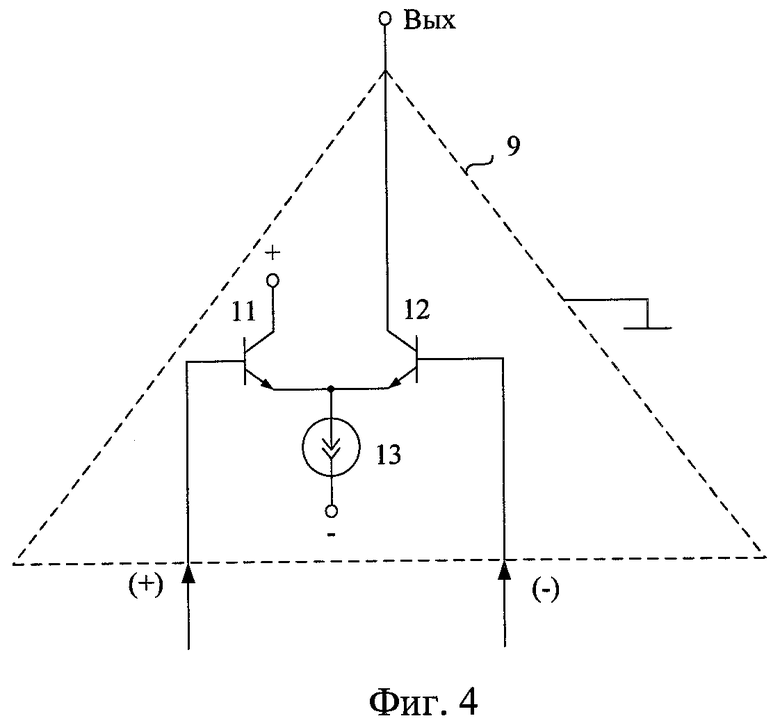

На фиг.3 и 4 показаны частные варианты построения дополнительного дифференциального каскада 9, соответствующие п.2 и п.3 формулы изобретения.

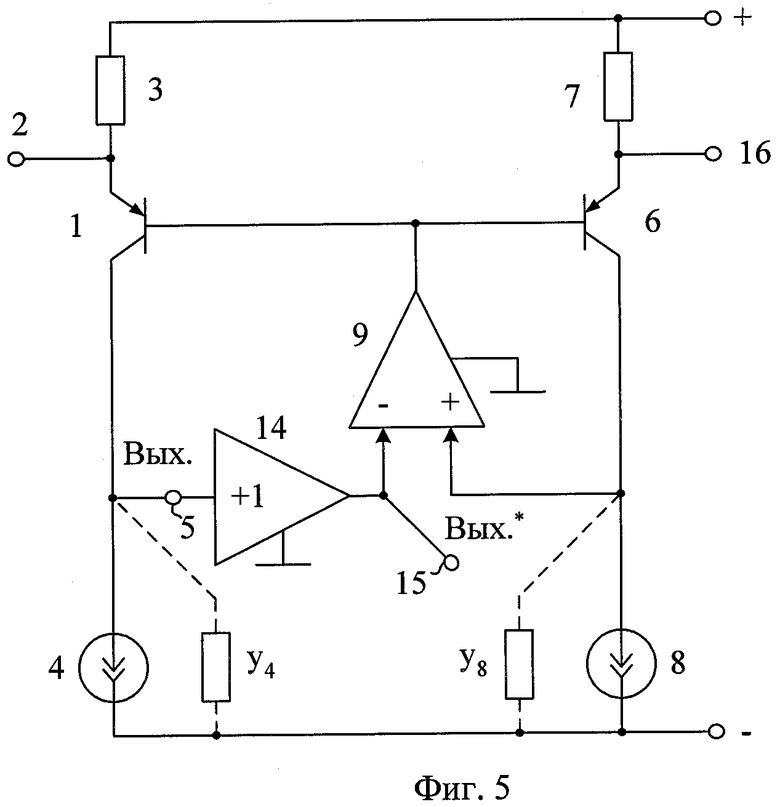

На фиг.5 представлен КУ, соответствующий п.4 формулы изобретения.

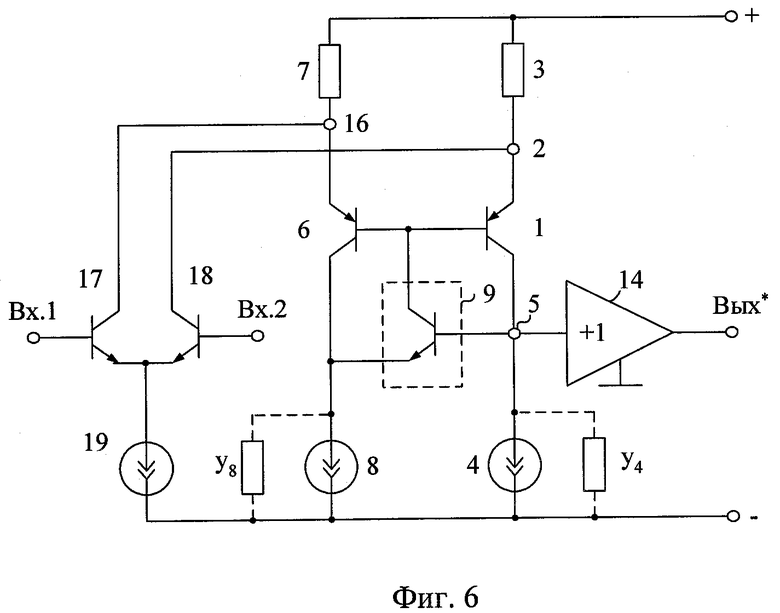

На фиг.6 показана схема операционного усилителя на основе заявляемого КУ для случая, когда дополнительный дифференциальный каскад 9 выполнен на основе фиг.3 (п.2 формулы изобретения).

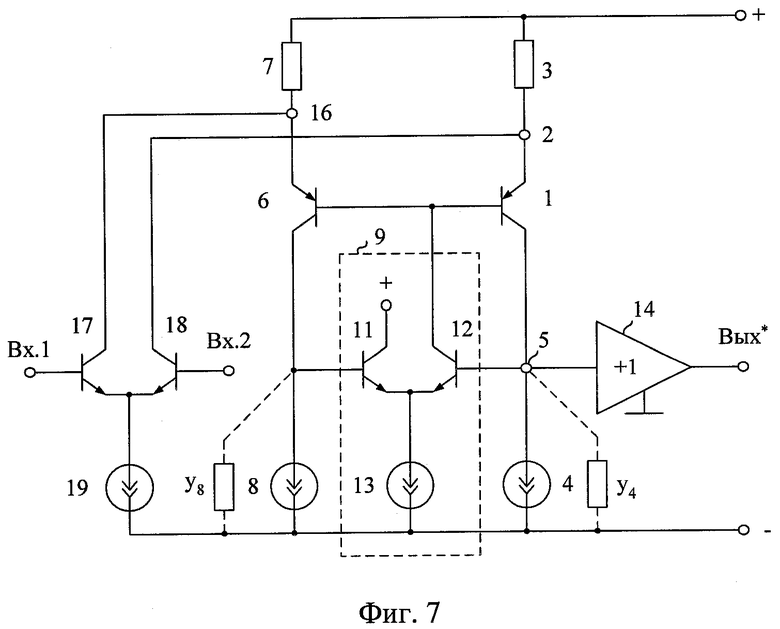

На фиг.7 показана схема операционного усилителя на основе заявляемого КУ для случая, когда дополнительный дифференциальный каскад 9 выполнен на основе фиг.4 (п.3 формулы изобретения).

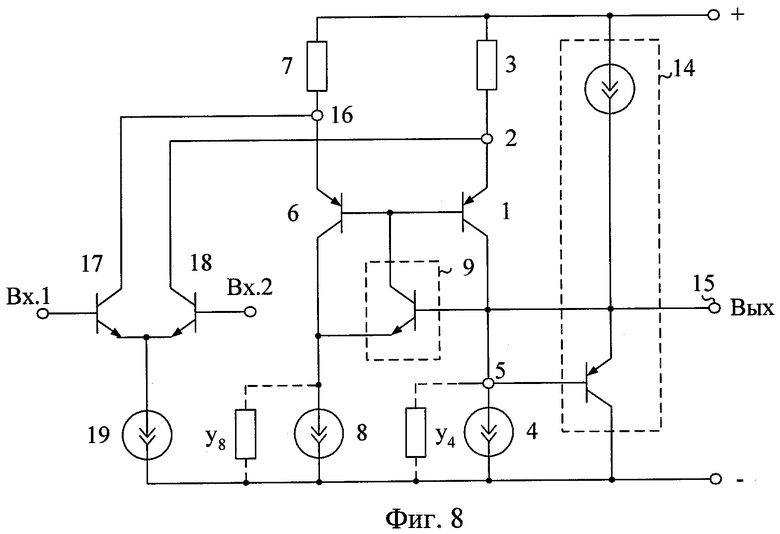

На фиг.8 показана схема операционного усилителя на основе заявляемого КУ, соответствующего структурной схеме фиг.5 (п.4 формулы изобретения).

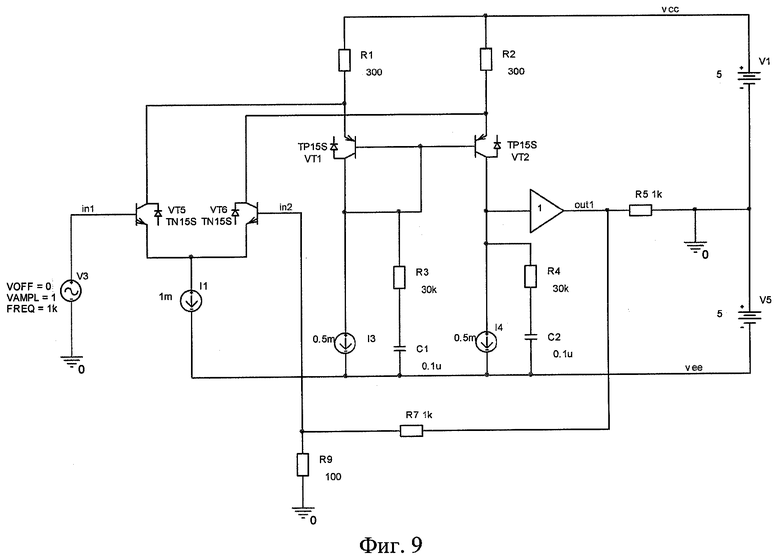

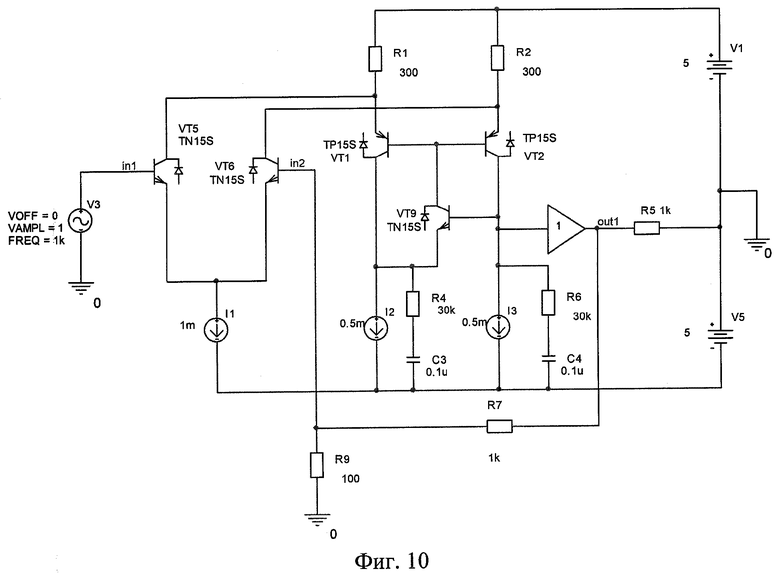

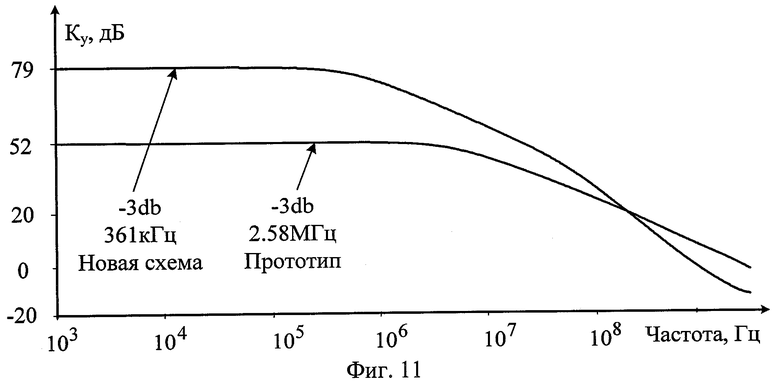

На фиг.9 и 10 показаны схемы операционного усилителя на основе известного КУ-прототипа (фиг.9) и предлагаемого КУ (фиг.10) в среде компьютерного моделирования PSpice, а на фиг.11 представлены результаты их компьютерного моделирования.

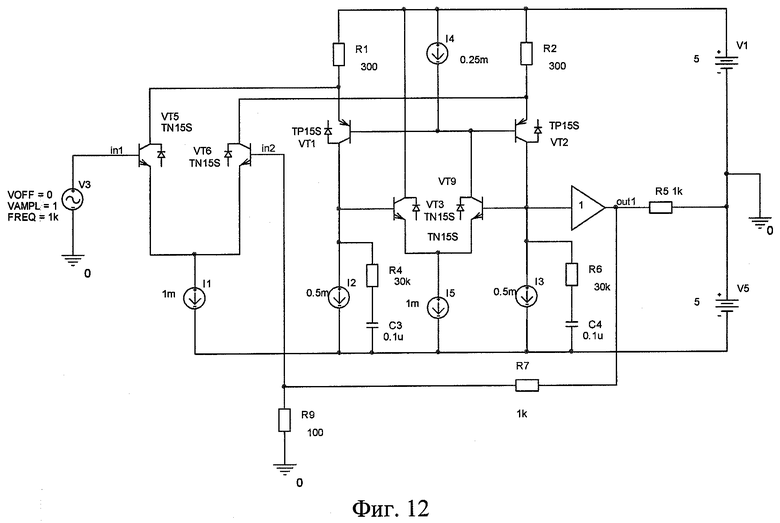

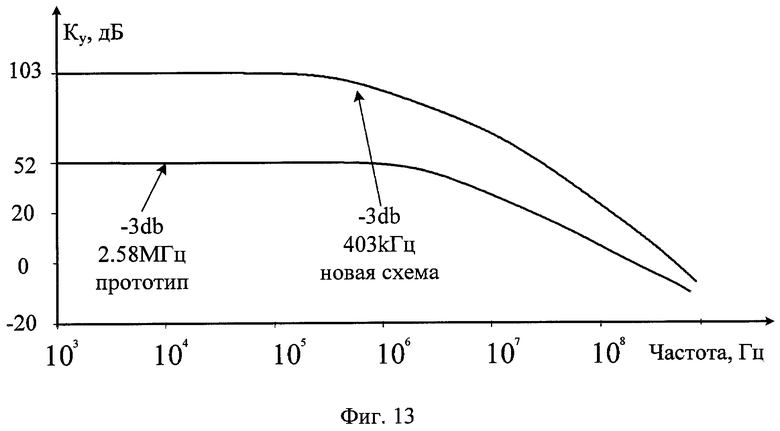

На фиг.12 показана схема операционного усилителя, соответствующего фиг.7 в среде компьютерного моделирования PSpice, а на фиг.13 представлены результаты компьютерного моделирования данной схемы, а также схемы КУ-прототипа фиг.9.

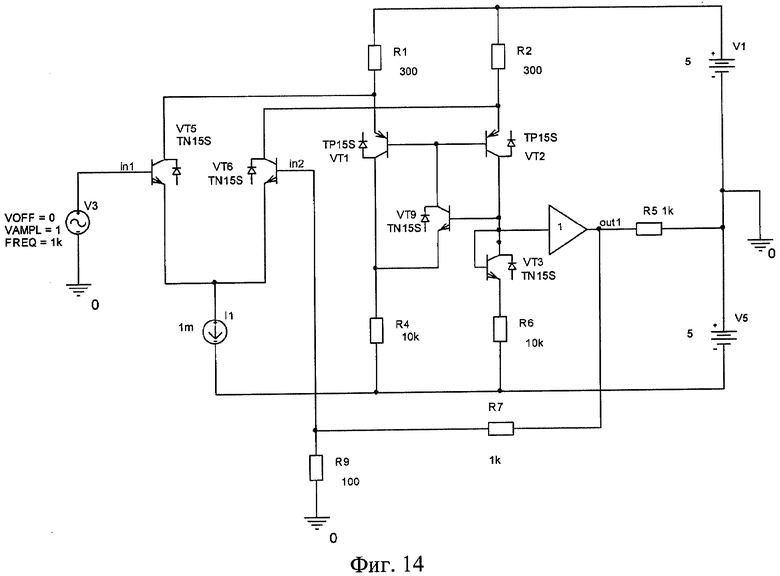

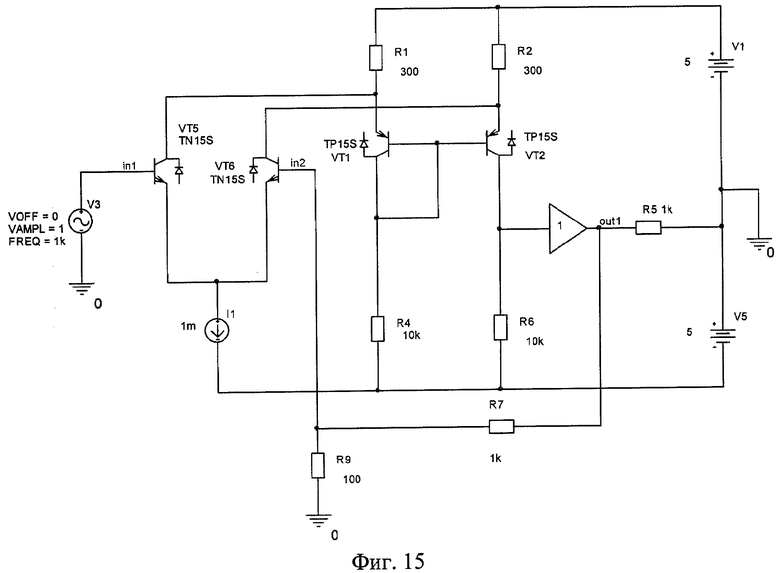

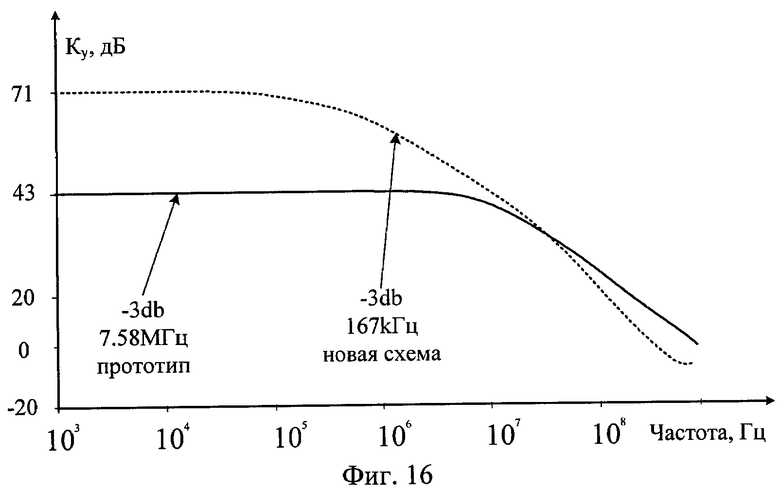

На фиг.14 и 15 показаны схемы предлагаемого (фиг.14) и известного (фиг.15) КУ в структуре операционных усилителей для случая, когда в качестве двухполюсников нагрузки 4 и 8 используются резисторы, а на фиг.16 представлены сравнительные результаты их компьютерного моделирования.

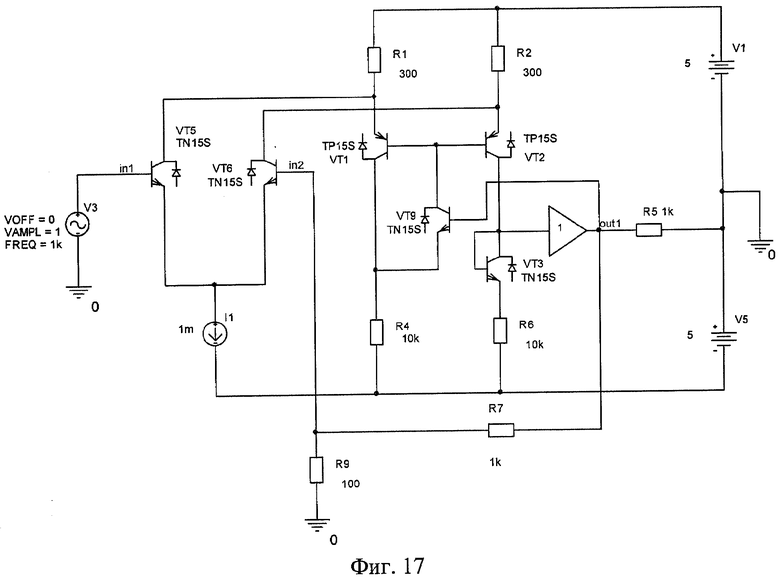

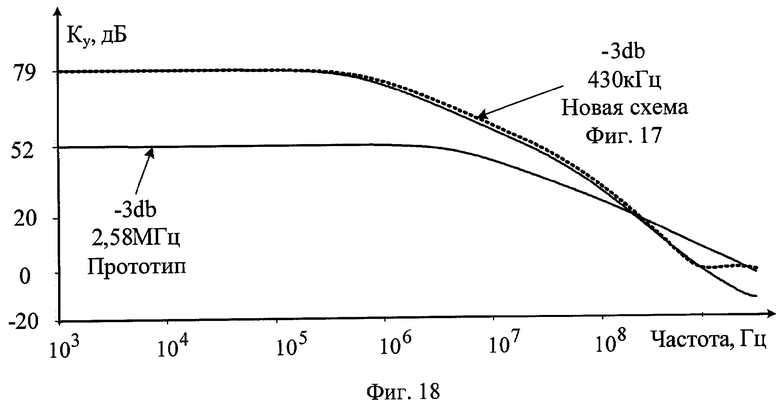

На фиг.17 представлена схема одного из вариантов предлагаемого (фиг.8) КУ в структуре операционного усилителя в среде компьютерного моделирования PSpice, а на фиг.18 представлены результаты расчета амплитудно-частотных характеристик сравниваемых КУ.

Дифференциальный усилитель фиг.2 содержит первый входной транзистор 1, эмиттер которого соединен с первым входом 2 каскодного усилителя и первым вспомогательным резистором 3, первый двухполюсник нагрузки 4, который соединен с коллектором первого входного транзистора 1 и первым выходом 5 каскодного усилителя, второй вспомогательный транзистор 6, эмиттер которого соединен со вторым вспомогательным резистором 7, база подключена к базе первого входного транзистора 1, а коллектор связан со вторым двухполюсником нагрузки 8. В схему введен дополнительный дифференциальный каскад 9, неинвертирующий вход которого подключен к коллектору второго входного транзистора 6 и второму двухполюснику нагрузки 8, инвертирующий вход связан с выходом каскодного усилителя 5, а выход подключен к базам первого 1 и второго 6 входных транзисторов.

В частном случае на фиг.3 в соответствии с п.2 формулы изобретения дополнительный дифференциальный каскад выполнен на основе первого дополнительного транзистора 10, коллектор которого является выходом дополнительного дифференциального каскада, эмиттер - неинвертирующим входом дополнительного дифференциального каскада, а база - инвертирующим входом дополнительного дифференциального каскада.

На фиг.4 в соответствии с п.3 формулы изобретения дополнительный дифференциальный каскад выполнен на основе второго 11 и третьего 12 дополнительных транзисторов, объединенные эмиттеры которых подключены к источнику опорного тока 13, причем база второго дополнительного транзистора является неинвертирующим входом дополнительного дифференциального каскада, база третьего дополнительного транзистора 12 является инвертирующим входом дополнительного дифференциального каскада, а коллектор третьего дополнительного транзистора 12 - выходом дополнительного дифференциального каскада.

На фиг.5 в соответствии с п.4 формулы изобретения инвертирующий вход дополнительного дифференциального каскада 1 связан с выходом 5 каскодного усилителя через дополнительный буферный усилитель 14, выход которого 15 является вспомогательным выходом расходного усилителя.

На фиг.6, 7 и 8, которые иллюстрируют применение предлагаемого КУ в схемах различных операционных усилителей, ко входам 2 и 16 КУ подключен входной дифференциальный каскад на транзисторах 17, 18 и источнике тока 19.

Рассмотрим работу заявляемого ДУ.

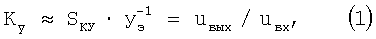

Коэффициент усиления по напряжению ДУ-прототипа фиг.1 зависит от величины эквивалентной выходной проводимости уэ узла 5:

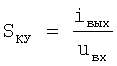

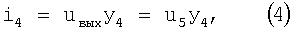

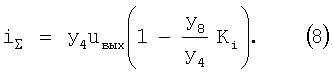

где  - крутизна усиления сигнала со входа 2 КУ на выход 5 при коротком замыкании по выходу.

- крутизна усиления сигнала со входа 2 КУ на выход 5 при коротком замыкании по выходу.

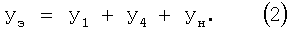

Проводимость уэ складывается из трех составляющих (фиг.1) - выходной проводимости транзистора 1 (у1), выходной проводимости двухполюсника нагрузки (у4), обеспечивающего статический режим транзистора 1, и проводимости собственной нагрузки ун:

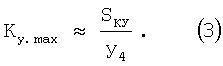

При высокоомной нагрузке (ун=0) и типовом построении двухполюсника нагрузки 4 на современных (например, SiGe) транзисторах с малым напряжением Эрли преобладает составляющая у4, так как при R3>>ϕт/Iэ1 выполняется условие у4>>y1, где ϕт=26 мВ - температурный потенциал, Iэ1 - статический ток эмиттера транзистора 1, R3 - сопротивление резистора 3. Поэтому в данных условиях предельный коэффициент усиления по напряжению ДУ-прототипа

В заявляемом устройстве фиг.2 обеспечивается взаимная компенсация в узле 5 двух идентичных проводимостей у4 и у8 двухполюсников нагрузки 4 и 8. Действительно, изменение выходного напряжения в узле 5 на величину uвых=u5 передается (с единичным коэффициентом усиления по напряжению) в коллектор транзистора 6 ( ), что порождает в схеме фиг.2 появление токов

), что порождает в схеме фиг.2 появление токов

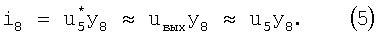

При идентичных сопротивлениях резисторов 3 и 7 (R3=R7) приращение тока i8 за счет отрицательной обратной связи по петле «усилитель 9 - транзистор 6» передается в коллектор транзистора 6 (iк6≈i8) и создает затем в коллекторной цепи транзистора 1 приращение тока iк1≈i8, которое компенсирует приращение тока i4 через выходную проводимость у4:

где Ki≈1 - коэффициент передачи по току i8 от вывода коллектора транзистора 6 на выход 5 КУ.

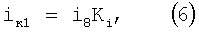

В результате в узле 5 суммарное приращение тока уменьшается

Или после преобразований формулы (7)

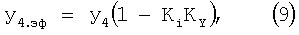

Таким образом, эффективное значение выходной проводимости двухполюсника 4

где Ki≈1;

КY=у8/у4≈1 - коэффициент асимметрии выходных проводимостей двухполюсников нагрузки 4 и 8.

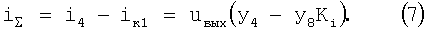

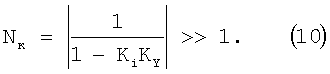

Так как двухполюсники нагрузки 4 и 8 выполняются идентичными, то KY≈1. Поэтому выигрыш по предельному коэффициенту усиления, который реализуется в заявленной схеме при данных ограничениях на ун и у1, достигает значений Nк>>1, где

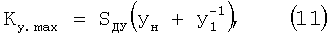

В этих условиях предельные значения Ку.max в схеме фиг.2 ограничивается величиной

где ун - проводимость нагрузки, y1 - выходная проводимость транзистора 1. Однако при рациональном выборе параметров элементов у4, ун, у1 и у8 в предлагаемой схеме обеспечивается дальнейшее повышение Kу.max.

Действительно, первая существенная особенность предлагаемого КУ состоит в том, что в нем обеспечивается взаимная компенсация не только выходных проводимостей двухполюсников нагрузки 8 и 4, но и выходных проводимостей транзисторов 1 и 6, а также выходной проводимости ун, подключаемой к выходному узлу 5.

Общее условие минимизации влияния ун, у1, у4 на Ку.max имеет следующий вид:

где  - проводимость дополнительной нагрузки (эквивалента ун), специально подключаемой к коллектору транзистора 6 для минимизации влияния ун на Ку.max.

- проводимость дополнительной нагрузки (эквивалента ун), специально подключаемой к коллектору транзистора 6 для минимизации влияния ун на Ку.max.

Учитывая, что у8=у4, у1=у6,  , в схеме фиг.2 обеспечивается полная компенсация всех паразитных импедансов, определяющих предельный коэффициент усиления Ку.

, в схеме фиг.2 обеспечивается полная компенсация всех паразитных импедансов, определяющих предельный коэффициент усиления Ку.

Вторая существенная особенность КУ фиг.4 - возможность применения резисторов в качестве двухполюсников 4 и 8 (фиг.14).

Третья существенная особенность предлагаемого КУ - высокая симметрия статического режима транзисторов 1 и 6 по напряжению коллектор-базы. В сравнении с прототипом и другими известными схемами КУ это существенно уменьшает э.д.с. смещения нуля ОУ на его основе.

Четвертая существенная особенность заявляемого КУ - высокая симметрия статического режима транзисторов 1 и 6 по величине коллекторного тока. Это обеспечивается, например, применением в качестве подсхемы 9 дифференциального каскада фиг.4 с одинаковыми токами базы входных транзисторов. В целом это уменьшает статические погрешности ОУ на основе предлагаемого устройства.

Источники информации

1. Патент США №4600893.

2. Операционные усилители и компараторы [Текст]. - М.: Издательский дом «Додэка-XXI», 2001. - С.243-244.

3. Матавкин В.В. Быстродействующие операционные усилители [Текст] / В.В.Матавкин. - М., «Радио и связь», 1989.

4. Патент США №6456162.

5. Патент США №6501333.

6. Патент США №6542030.

7. Патент США №4293824.

8. Патент США №5734296.

9. Патент США №5420540.

10. Патент США №5523718.

11. Патент США №4644295.

12. Ежков Ю.С. Справочник по схемотехнике усилителей. - М., Радиософт, 2002. - С.87, рис.5.20, 5.21.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2368066C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2257001C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2006 |

|

RU2319287C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321159C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2310268C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321158C1 |

| КАСКОДНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2428786C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390912C2 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319294C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Технический результат заключается в повышении предельного коэффициента усиления по напряжению. Каскодный усилитель (КУ) содержит первый входной транзистор (Т) (1), эмиттер которого соединен с первым входом (2) КУ и первым вспомогательным резистором (Р) (3), первый двухполюсник нагрузки (4), который соединен с коллектором Т (1) и первым выходом (5) КУ, второй вспомогательный Т (6), эмиттер которого соединен со вторым вспомогательным Р (7), база подключена к базе Т (1), а коллектор связан со вторым двухполюсником нагрузки (8). В схему введен дополнительный дифференциальный каскад (9), неинвертирующий вход которого подключен к коллектору Т (6) и второму двухполюснику нагрузки (8), инвертирующий вход связан с выходом 5 КУ, а выход подключен к базам Т (1) и Т (6). 4 з.п. ф-лы, 18 ил.

| US 6542030 В2, 01.04.2003 | |||

| Дифференциальный усилитель | 1975 |

|

SU566304A1 |

| US 6229394 B1, 08.05.2001 | |||

| US 5559470 A, 24.09.1996 | |||

| US 5422600 A, 06.06.1995. | |||

Авторы

Даты

2008-10-27—Публикация

2007-07-30—Подача