Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления ВЧ и СВЧ аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

В современной аналоговой микроэлектронике широко применяются так называемые комплементарные каскодные дифференциальные усилители на n-p-n и p-n-p транзисторах с архитектурой операционного усилителя µА741 [1-30]. Их основное достоинство в сравнении с классическим дифференциальным каскадом - более широкий частотный диапазон, что делает их особенно привлекательными при построении аналоговых устройств СВЧ-диапазона.

В рамках собственных программ развития ряд ведущих микроэлектронных фирм, в т.ч. российских, начинают использовать технологическое оборудование для 0,25 мкм SiGe-технологии SGB25VD, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы Х диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако технология SGB25VD накладывает дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в невозможности использования комплементарных транзисторов и относительно низковольтных режимов их работы (Uкэ.max = 2,9 В или напряжение двуполярного питания ±1,5 В). Создание IP блоков для SiGe технологии SGB25VD является (наряду с ее освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем. Предлагаемое изобретение относится к данному направлению развития микроэлектроники.

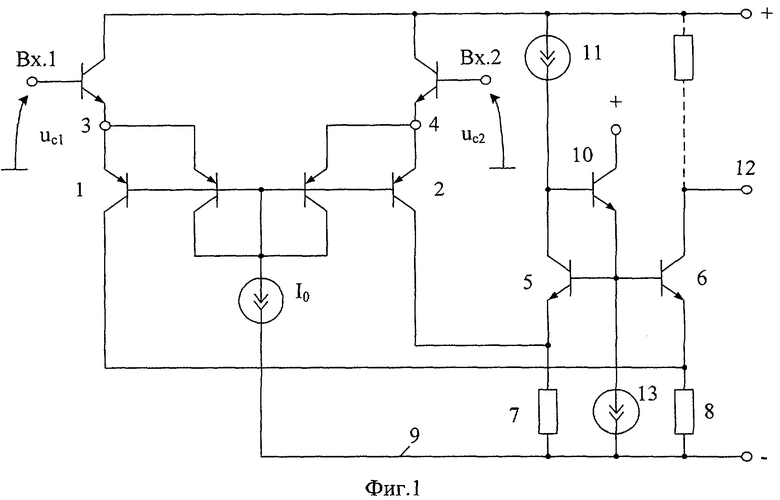

Ближайшим прототипом (фиг.1) заявляемого устройства является КДУ, описанный в патенте США №5521552, содержащий первый 1 и второй 2 входные транзисторы с объединенными базами (затворами), эмиттеры (истоки) которых подключены к соответствующим первому 3 и второму 4 входам каскодного дифференциального усилителя, а коллекторы - соединены с эмиттерами первого 5 и второго 6 выходных транзисторов и через первый 7 и второй 8 токостабилизирующие двухполюсники соединены с первой шиной 9 источника питания, третий выходной транзистор 10, база которого связана с коллектором первого выходного транзистора 5 и первым выводом вспомогательного двухполюсника 11, эмиттер - подключен к объединенным базам первого 5 и второго 6 выходных транзисторов, причем коллектор второго выходного транзистора 6 связан с выходом 12 каскодного дифференциального усилителя, а второй вывод вспомогательного двухполюсника 11 связан со второй 9* шиной источника питания.

Существенный недостаток известного КДУ состоит в том, что он имеет повышенное токопотребление, что обусловлено наличием в его архитектуре (фиг.1) потребляющей некоторый ток I0 цепи установления статического режима, которая непосредственно не участвует в усилении входного сигнала. Исключение этой цепи позволит уменьшить (при прочих равных условиях) энергопотребление КДУ.

Основная задача предлагаемого изобретения состоит в уменьшении потребляемого от источников питания статического тока.

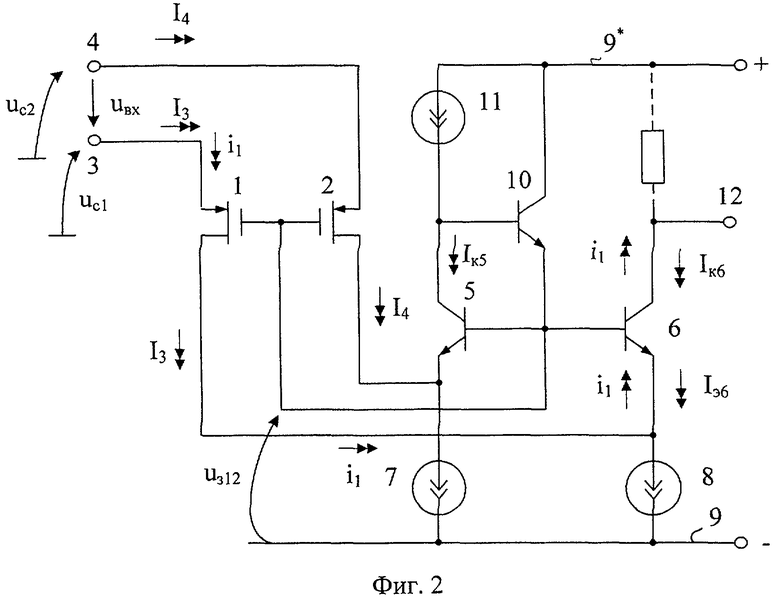

Поставленная задача достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы с объединенными базами (затворами), эмиттеры (истоки) которых подключены к соответствующим первому 3 и второму 4 входам каскодного дифференциального усилителя, а коллекторы - соединены с эмиттерами первого 5 и второго 6 выходных транзисторов и через первый 7 и второй 8 токостабилизирующие двухполюсники соединены с первой шиной 9 источника питания, третий выходной транзистор 10, база которого связана с коллектором первого выходного транзистора 5 и первым выводом вспомогательного двухполюсника 11, эмиттер - подключен к объединенным базам первого 5 и второго 6 выходных транзисторов, причем коллектор второго выходного транзистора 6 связан с выходом 12 каскодного дифференциального усилителя, а второй вывод вспомогательного двухполюсника 11 связан со второй 9* шиной источника питания, предусмотрены новые элементы и связи - базы (затворы) первого 1 и второго 2 входных транзисторов соединены с объединенными базами первого 5 и второго 6 выходных транзисторов.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения.

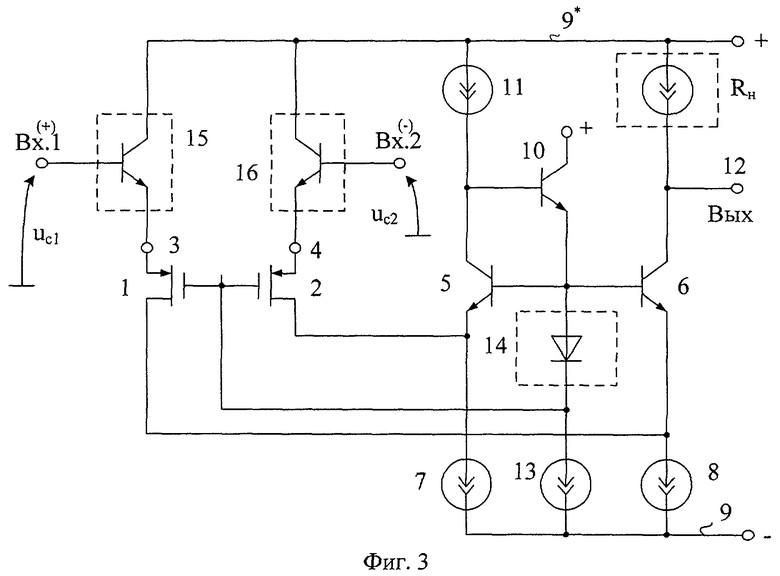

На фиг.3 показана схема заявляемого КДУ в соответствии с п.2 и п.3 формулы изобретения.

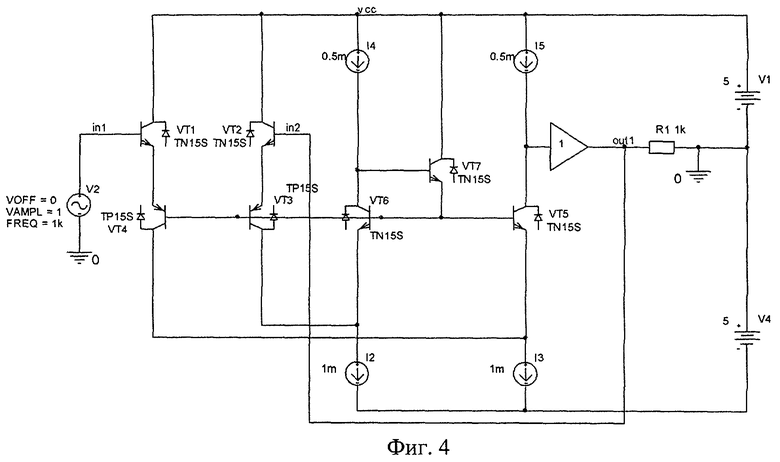

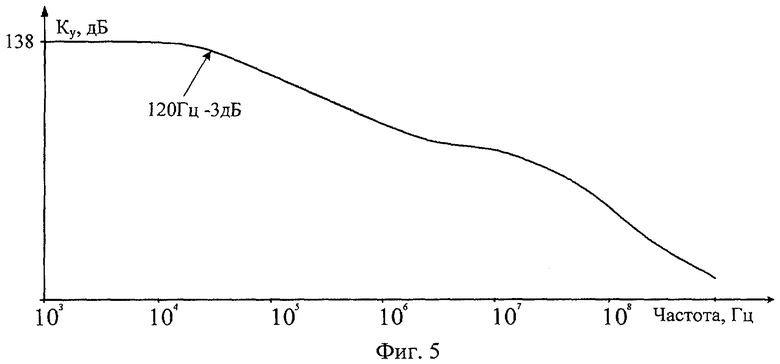

На фиг.4 представлена схема КДУ, соответствующая фиг.3 (без двухполюсника 13) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.5 - ее амплитудно-частотная характеристика при «идеальных» двухполюсниках 7, 8 и нагрузке (I5).

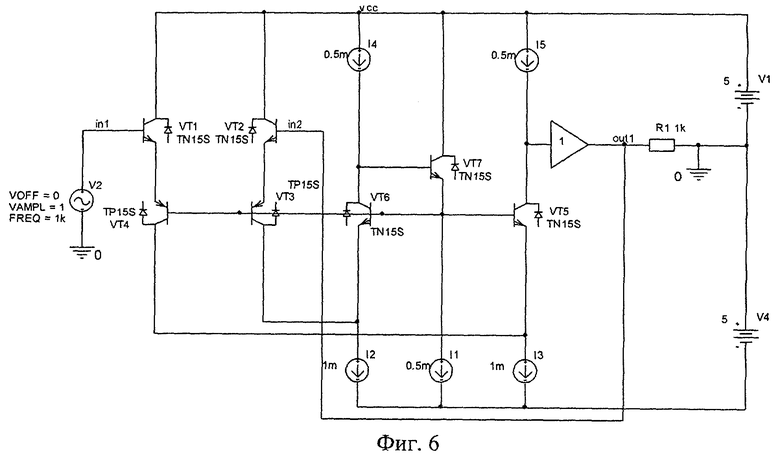

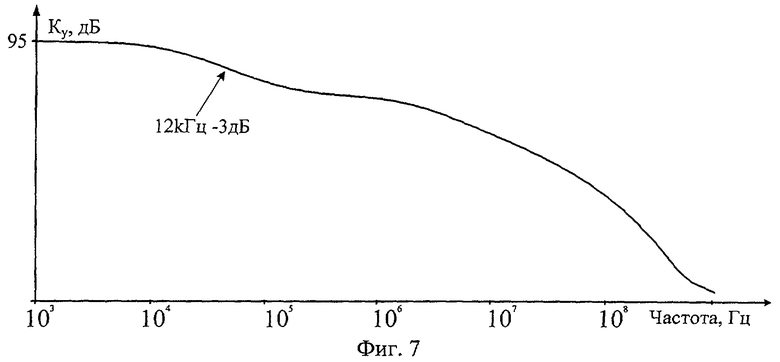

Схема фиг.6 в среде PSpice соответствует фиг.3 (без цепи согласования 14) в среде PSpice, а результаты ее моделирования коэффициента усиления изображены на фиг.7.

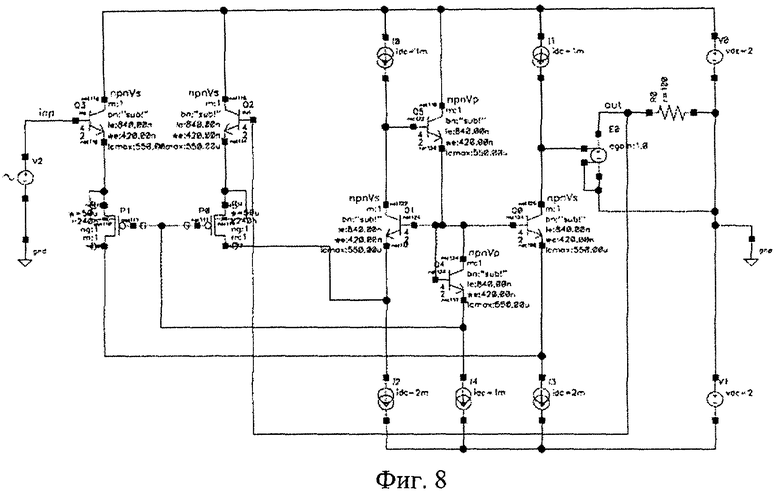

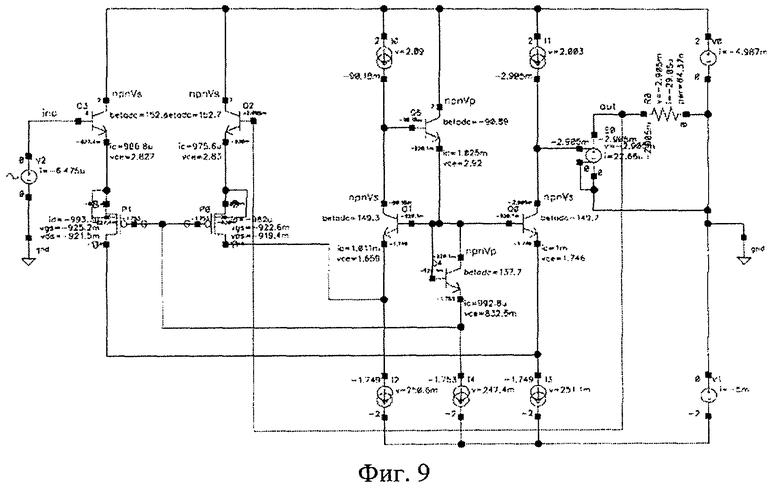

Схемы фиг.8 и фиг.9 полностью соответствуют фиг.3. Они представляют собой компьютерную модель КДУ в среде Cadance на моделях SiGe транзисторов.

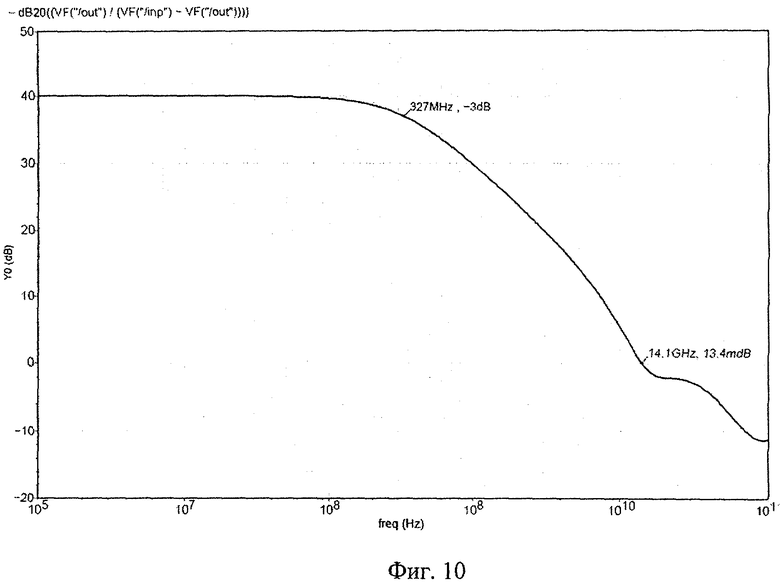

Результаты расчета зависимости коэффициента усиления Ку от частоты этих схем даны на фиг.10.

Каскодный дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы с объединенными базами (затворами), эмиттеры (истоки) которых подключены к соответствующим первому 3 и второму 4 входам каскодного дифференциального усилителя, а коллекторы - соединены с эмиттерами первого 5 и второго 6 выходных транзисторов и через первый 7 и второй 8 токостабилизирующие двухполюсники соединены с первой шиной 9 источника питания, третий выходной транзистор 10, база которого связана с коллектором первого выходного транзистора 5 и первым выводом вспомогательного двухполюсника 11, эмиттер - подключен к объединенным базам первого 5 и второго 6 выходных транзисторов, причем коллектор второго выходного транзистора 6 связан с выходом 12 каскодного дифференциального усилителя, а второй вывод вспомогательного двухполюсника 11 связан со второй 9* шиной источника питания. Базы (затворы) первого 1 и второго 2 входных транзисторов соединены с объединенными базами первого 5 и второго 6 выходных транзисторов.

На фиг.3, соответствующей п.2 формулы изобретения, в схему введен третий 13 токостабилизирующий двухполюсник, подключенный к базам (затворам) первого 1 и второго 2 входных транзисторов, которые соединены с объединенными базами первого 5 и второго 6 выходных транзисторов через цепь согласования потенциалов 14.

Кроме этого на фиг.3, соответствующей п.3 формулы изобретения, между дифференциальным источником входного сигнала и первым 3, а также вторым 4 входами каскодного дифференциального усилителя включены первый 15 и второй 16 эмиттерные (истоковые) повторители напряжения.

Рассмотрим работу схемы фиг.2 (фиг.3).

В статическом режиме через источник входного дифференциального сигнала uc1 и uc2 протекают токи истока транзисторов 1 и 2, численные значения которых устанавливаются первым 7 и вторым 8 токостабилизирующими двухполюсниками, а также вспомогательным двухполюсником 11:

где Ii - статические токи двухполюсников 7, 8 и 11;

Iэ6 - ток эмиттера транзистора 6.

Ток эмиттера транзистора 10 устанавливается в схеме фиг.3 третьим токостабилизирующим двухполюсником 13 (Iэ10=I13). В цепи нагрузки КДУ (резистор или источник опорного тока), которая подключается к выходу 12 КДУ, протекает ток коллектора транзистора 6 Iк6. Потенциал затворов транзисторов 1 и 2 (uз12) (в соответствии с п.1 формулы изобретения) устанавливается как потенциал баз транзисторов 5 и 6.

Изменение синфазной составляющей входных напряжений uc=(uc1+uc2)/2 приводит к такому же изменению напряжений на базах транзисторов 5, 6 и 10, так как токи I4 и I3 в соответствии с (1) и (2) не изменяются. Таким образом, схема фиг.2 имеет высокое ослабление синфазных сигналов.

Если между входами 3 и 4 подается дифференциальное напряжение uвх=uс1-uс2, то это создает приращение тока i3, которое определяется крутизной S1 входного полевого транзистора 1:

Ток i1 поступает в цепь эмиттера транзистора 6, и далее на выход 12 в цепь нагрузки КДУ. Таким образом, вход 3 является неинвертирующим входом КДУ.

Следует заметить, что изменение uвх не приводит к изменению тока истока транзистора 2, что вытекает из уравнения (1). Таким образом, по данному входу 4 КДУ всегда имеет высокое входное сопротивление.

За счет «двойной каскодной архитектуры» (транзистор 1 и транзистор 6) предлагаемая схема обладает предельным значением верхней граничной частоты и может применяться в СВЧ-диапазоне в рамках техпроцесса SGVD25 IHP (Германия).

Первая особенность схемы фиг.3 состоит в том, что потенциал затвора транзисторов 1 и 2 здесь смещен к шине отрицательного источника питания 9 на величину напряжения на двухполюснике 14. Это уменьшает статическое напряжение между затворами транзисторов 1, 2 и базами транзисторов 5 и 6, расширяет динамический диапазон усиливаемых сигналов.

Вторая особенность схемы фиг.3 - наличие (в соответствии с п.3 формулы изобретения) эмиттерных повторителей 15 и 16, которые уменьшают входные токи КДУ фиг.3 и повышают его входное сопротивление по неинвертирующему входу.

Характерной особенностью схем заявляемого КДУ является отсутствие источника тока I0 (фиг.1), который ухудшает на 1÷2 мА (20÷25%) показатели известного КДУ (фиг.1) по токопотреблению, не принимает участие в обеспечении статического тока транзисторов, обеспечивающих усиление входного сигнала.

Таким образом, предлагаемое схемотехническое решение позволяет использовать СВЧ SiGe-транзисторы техпроцесса SGB25VD с относительно низким напряжением питания 2,9 В в структуре не только различных аналоговых устройств, но и СФ блоков систем на кристалле. Этот важный результат расширяет область практического использования SGB25VD технологии и, следовательно, повышает технико-экономические показатели микроэлектронных изделий. Так, например, создание новой (под указанную технологию) схемотехники широкодиапазонных операционных усилителей позволит не только повысить качественные показатели СВЧ-фильтров, квадратурных модуляторов, демодуляторов и других устройств нового поколения, образующих СФ блоки СВЧ РЭА, но и создать новую номенклатуру ИС широкого функционального применения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3786362.

2. Патент США №4030044.

3. Патент США №4059808, фиг.5.

4. Патент США №4286227.

5. Авт.свид. СССР №375754, H03F 3/38.

6. Авт.свид. СССР №843164, H03F 3/30.

7. Патент США №3660773.

8. Патент США №4560948.

9. Патент РФ №2930041, H03F 1/32.

10. Патент Японии №57-5364, H03F 3/343.

11. Патент ЧССР №134845, кл.21a2 18/08.

12. Патент ЧССР №134849, кл.21a2 18/08.

13. Патент ЧССР №135326, кл.21а2 18/08.

14. Патент США №4389579.

15. Патент Англии №1543361, Н3Т.

16. Патент США №5521552 (фиг.3а).

17. Патент США №4059808.

18. Патент США №5789949.

19. Патент США №4453134.

20. Патент США №4760286.

21. Авт.свид. СССР №1283946.

22. Патент РФ №2019019.

23. Патент США №4389579.

24. Патент США №4453092.

25. Патент США №3566289.

26. Патент США №4059808 (фиг.2).

27. Патент США №3649926.

28. Патент США №4714894 (фиг.1).

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2374755C2 |

| КОМПЛЕМЕНТАРНЫЙ ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2370879C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2469465C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439780C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441314C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2455756C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2008 |

|

RU2384934C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374760C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления ВЧ и СВЧ аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Технический результат: уменьшение потребляемого статического тока. Каскодный дифференциальный усилитель (КДУ) содержит первый (1) и второй (2) транзисторы (Т) с объединенными базами (затворами), эмиттеры (истоки) которых подключены к соответствующим первому (3) и второму (4) входам КДУ, а коллекторы - соединены с эмиттерами первого (5) и второго (6) выходных Т и через первый (7) и второй (8) токостабилизирующие двухполюсники соединены с шиной (9) источника питания, третий выходной Т (10), база которого связана с коллектором первого выходного Т (5) и вспомогательным двухполюсником I11, эмиттер - подключен к объединенным базам первого (5) и второго (6) выходных Т, причем коллектор второго выходного Т (6) связан с выходом (12) КДУ. Базы (затворы) первого (1) и второго (2) входных Т соединены с объединенными базами первого (5) и второго (6) выходных Т. 2 з.п. ф-лы, 10 ил.

1. Каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы с объединенными базами (затворами), эмиттеры (истоки) которых подключены к соответствующим первому (3) и второму (4) входам каскодного дифференциального усилителя, а коллекторы соединены с эмиттерами первого (5) и второго (6) выходных транзисторов и через первый (7) и второй (8) токостабилизирующие двухполюсники соединены с шиной (9) источника питания, третий выходной транзистор (10), база которого связана с коллектором первого выходного транзистора (5) и вспомогательным двухполюсником (11), эмиттер подключен к объединенным базам первого (5) и второго (6) выходных транзисторов, причем коллектор второго выходного транзистора (6) связан с выходом (12) каскодного дифференциального усилителя, отличающийся тем, что базы (затворы) первого (1) и второго (2) входных транзисторов соединены с объединенными базами первого (5) и второго (6) выходных транзисторов.

2. Устройство по п.1, отличающееся тем, что в схему введен третий (13) токостабилизирующий двухполюсник, подключенный к базам (затворам) первого (1) и второго (2) входных транзисторов, которые соединены с объединенными базами первого (5) и второго (6) выходных транзисторов через цепь согласования потенциалов (14).

3. Устройство по п.1, отличающееся тем, что между дифференциальным источником входного сигнала и первым (3), а также вторым (4) входами каскодного дифференциального усилителя включены первый (15) и второй (16) эмиттерные (истоковые) повторители напряжения.

| US 5521552 А, 28.05.1996 | |||

| Операционный усилитель | 1983 |

|

SU1193773A1 |

| US 6144234 А, 07.11.2000 | |||

| US 6483382 В1, 19.11.2002. | |||

Авторы

Даты

2010-05-27—Публикация

2008-04-04—Подача