Предлагаемое изобретение предназначено для использования в системах связи, применяемых для передачи информации по каналам связи с межсимвольной интерференцией (МСИ), например по многолучевым коротковолновым (KB) каналам, в тех случаях, когда требуется высокая достоверность передачи данных.

Как правило, в существующих системах связи данная цель (высокая достоверность передачи данных) достигается:

1) использованием помехоустойчивого кода и методов борьбы с МСИ в модеме передачи данных;

2) использованием канального протокола, работающего «поверх» помехоустойчивого кода.

Работа канального протокола заключается в разбиении передаваемой информации на фрагменты и добавлении к каждому из них контрольной суммы (CRC кода), т.е. канальный протокол использует собственный код с низкой избыточностью - CRC код, способный обнаруживать, но не исправлять ошибки. На приемной стороне фрагменты с неправильными контрольными суммами бракуются (в частности, они могут быть перезапрошены по каналу обратной связи в текущем или последующем сеансах обмена сообщениями).

В настоящее время наиболее эффективным способом борьбы с МСИ является использование турбоэквалайзеров, представляющих собой устройства, состоящие из: 1) собственно, эквалайзера с «мягким» входом и выходом - SISO эквалайзера; 2) SISO декодера с «мягким» входом и выходом. Турбоэквалайзер производит итеративную обработку реализации сигнала, соответствующей одному кодовому слову. Выходная информация о принятых из канала битах (или символах), полученная на каждой ступени обработки (на выходе SISO декодера или SISO эквалайзера) в форме отношения логарифмов правдоподобия (LLR), является входной информацией на каждой последующей ступени обработки.

На данном принципе основаны многие способы обработки сигнала и устройства, их реализующие, например приведенные в статьях [1-3].

Недостатком известных технических решений является то, что обработка на обоих уровнях иерархии происходит полностью независимо: информация, заложенная в избыточности CRC кода на уровне канального протокола, никак не используется на стадии обработки сигнала эквалайзером модема, осуществляющим устранение искажений, вызванных МСИ, а также декодером помехоустойчивого кода. Кроме того, в случае отсутствия канального протокола верхнего уровня нет возможности оценить достоверность принимаемой информации, а также ускорить ее обработку при высокой достоверности.

Наиболее близким по технической сущности к предлагаемому способу (первый вариант) является способ, представленный в статье [4], принятый за прототип.

Способ-прототип заключается в следующем.

В передающей части системы связи исходная последовательность бит sk (входная информация) разбивается на фрагменты, к каждому из которых добавляется CRC код, формируется последовательность бит  . Далее последовательность бит

. Далее последовательность бит  кодируется помехоустойчивым кодом, формируется последовательность бит

кодируется помехоустойчивым кодом, формируется последовательность бит  , которая перемешивается по определенному закону, формируется последовательность бит

, которая перемешивается по определенному закону, формируется последовательность бит  . Последовательность бит

. Последовательность бит  модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии (символам).

модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии (символам).

В приемной части системы связи принимаемый из канала связи сигнал y(t) (входная информация) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии (принятым символам). Демодулированный сигнал уn подвергается эквалайзингу с учетом априорных значений LLR бит  (на первой итерации равны нулю), формируется последовательность LLR бит

(на первой итерации равны нулю), формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  деперемешивается, формируется последовательность LLR бит

деперемешивается, формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  декодируется, формируется последовательность LLR бит

декодируется, формируется последовательность LLR бит  . Если заданное количество итераций еще не закончилось, последовательность LLR бит

. Если заданное количество итераций еще не закончилось, последовательность LLR бит  перемешивается, формируется последовательность LLR бит

перемешивается, формируется последовательность LLR бит  , которая является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, последовательность LLR бит

, которая является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, последовательность LLR бит  детектируется, формируется последовательность предварительных оценок бит

детектируется, формируется последовательность предварительных оценок бит  . Последовательность предварительных оценок бит

. Последовательность предварительных оценок бит  разбивается на фрагменты, в которых проверяется CRC, формируется выходная последовательность бит

разбивается на фрагменты, в которых проверяется CRC, формируется выходная последовательность бит  . Причем благодаря CRC коду известно, какие фрагменты

. Причем благодаря CRC коду известно, какие фрагменты  приняты с ошибками, а какие - без.

приняты с ошибками, а какие - без.

Недостатком способа-прототипа является то, что информация, заложенная в избыточности CRC кода канального протокола, никак не используется на стадии обработки сигнала эквалайзером модема, осуществляющим устранение искажений, вызванных МСИ, а также декодером помехоустойчивого кода.

Для устранения указанного недостатка в способе, заключающемся в том, что в передающей части системы связи исходная последовательность бит sk разбивается на фрагменты, к каждому из которых добавляется CRC код, формируется последовательность бит  , которая кодируется помехоустойчивым кодом, формируется последовательность бит

, которая кодируется помехоустойчивым кодом, формируется последовательность бит  , которая перемешивается по определенному закону, формируется последовательность бит

, которая перемешивается по определенному закону, формируется последовательность бит  , которая модулируется, формируется выходная последовательность комплексных чисел хn, соответствующих точкам в сигнальном созвездии, в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии, далее демодулированный сигнал уn подвергается эквалайзингу с учетом априорных значений LLR бит

, которая модулируется, формируется выходная последовательность комплексных чисел хn, соответствующих точкам в сигнальном созвездии, в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии, далее демодулированный сигнал уn подвергается эквалайзингу с учетом априорных значений LLR бит  , которые на первой итерации равны нулю, формируется последовательность LLR бит

, которые на первой итерации равны нулю, формируется последовательность LLR бит  , которая деперемешивается, формируется последовательность LLR бит

, которая деперемешивается, формируется последовательность LLR бит  которая декодируется, формируется последовательность LLR бит

которая декодируется, формируется последовательность LLR бит  , если заданное количество итераций еще не закончилось, то последовательность LLR бит

, если заданное количество итераций еще не закончилось, то последовательность LLR бит  перемешивается, формируется последовательность LLR бит

перемешивается, формируется последовательность LLR бит  , которая является априорной информацией для SISO эквалайзера, согласно изобретению, в приемной части детектируют последовательность LLR бит

, которая является априорной информацией для SISO эквалайзера, согласно изобретению, в приемной части детектируют последовательность LLR бит  , формируют последовательность предварительных оценок бит

, формируют последовательность предварительных оценок бит  , разбивают на фрагменты последовательность предварительных оценок бит

, разбивают на фрагменты последовательность предварительных оценок бит  , в которых проверяют CRC, фрагменты последовательности LLR бит

, в которых проверяют CRC, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, детектируют последовательность LLR бит

, для которых CRC совпала, заменяют значениями ∞, детектируют последовательность LLR бит  , формируют последовательность предварительных оценок бит

, формируют последовательность предварительных оценок бит  , далее ее разбивают на фрагменты, в которых проверяют CRC, формируют последовательность оценок бит

, далее ее разбивают на фрагменты, в которых проверяют CRC, формируют последовательность оценок бит  , фрагменты последовательности LLR бит

, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, после окончания заданного количества итераций полученная после проверки CRC последовательность оценок бит

, для которых CRC совпала, заменяют значениями ∞, после окончания заданного количества итераций полученная после проверки CRC последовательность оценок бит  становится выходной, причем благодаря CRC коду выявляют фрагменты, принятые с ошибками.

становится выходной, причем благодаря CRC коду выявляют фрагменты, принятые с ошибками.

Предлагаемый способ итеративной обработки сигнала для последовательного модема заключается в следующем.

В передающей части системы связи исходная последовательность бит sk (входная информация) разбивается на фрагменты, к каждому из которых добавляется CRC код, формируется последовательность бит  . Далее последовательность бит

. Далее последовательность бит  кодируется помехоустойчивым кодом, формируется последовательность бит

кодируется помехоустойчивым кодом, формируется последовательность бит  , которая перемешивается по определенному закону, формируется последовательность бит

, которая перемешивается по определенному закону, формируется последовательность бит  . Последовательность бит

. Последовательность бит  модулируется, формируется выходная последовательность комплексных чисел хn, соответствующих точкам в сигнальном созвездии (символам). То есть в передающей части предлагаемый способ совпадает со способом-прототипом.

модулируется, формируется выходная последовательность комплексных чисел хn, соответствующих точкам в сигнальном созвездии (символам). То есть в передающей части предлагаемый способ совпадает со способом-прототипом.

В приемной части системы связи принимаемый из канала связи сигнал y(t) (входная информация) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии (принятым символам). Далее демодулированный сигнал уn подвергается эквалайзингу с учетом априорных значений LLR бит  (на первой итерации равны нулю), формируется последовательность LLR бит

(на первой итерации равны нулю), формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  деперемешивается, формируется последовательность LLR бит

деперемешивается, формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  детектируется, формируется последовательность предварительных оценок бит

детектируется, формируется последовательность предварительных оценок бит  . Последовательность предварительных оценок бит

. Последовательность предварительных оценок бит  разбивается на фрагменты, в которых проверяется CRC. Фрагменты последовательности LLR бит

разбивается на фрагменты, в которых проверяется CRC. Фрагменты последовательности LLR бит  , для которых CRC совпала, заменяются значениями LLR, соответствующими надежности решений на выходе устройства проверки контрольных сумм CRC кода, т.е.

, для которых CRC совпала, заменяются значениями LLR, соответствующими надежности решений на выходе устройства проверки контрольных сумм CRC кода, т.е.  где perr - вероятность ошибки в бите фрагмента с правильной контрольной суммой CRC кода. Т.е., практически, можно считать решения о принятых битах, принадлежащих фрагментам с правильными контрольными суммами, абсолютно надежными и полагать их равными ∞. Последовательность LLR бит

где perr - вероятность ошибки в бите фрагмента с правильной контрольной суммой CRC кода. Т.е., практически, можно считать решения о принятых битах, принадлежащих фрагментам с правильными контрольными суммами, абсолютно надежными и полагать их равными ∞. Последовательность LLR бит  декодируется, формируется последовательность LLR бит

декодируется, формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  детектируется, формируется последовательность предварительных оценок бит

детектируется, формируется последовательность предварительных оценок бит  . Последовательность предварительных оценок бит

. Последовательность предварительных оценок бит  разбивается на фрагменты, в которых проверяется CRC, формируется последовательность оценок бит

разбивается на фрагменты, в которых проверяется CRC, формируется последовательность оценок бит  . Фрагменты последовательности LLR бит

. Фрагменты последовательности LLR бит  , для которых CRC совпала, заменяются значениями ∞ (LLR для известных бит). Если заданное количество итераций еще не закончилось, последовательность LLR бит

, для которых CRC совпала, заменяются значениями ∞ (LLR для известных бит). Если заданное количество итераций еще не закончилось, последовательность LLR бит  перемешивается. Формируется последовательность LLR бит

перемешивается. Формируется последовательность LLR бит  , которая является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, полученная после проверки CRC последовательность оценок бит

, которая является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, полученная после проверки CRC последовательность оценок бит  становится выходной. Причем благодаря CRC коду известно, какие фрагменты

становится выходной. Причем благодаря CRC коду известно, какие фрагменты  приняты с ошибками, а какие - без. В случае, если на какой-либо итерации турбо эквалайзера все биты окажутся декодированы правильно, итерации можно прекратить досрочно.

приняты с ошибками, а какие - без. В случае, если на какой-либо итерации турбо эквалайзера все биты окажутся декодированы правильно, итерации можно прекратить досрочно.

Таким образом, предлагаемый способ (первый вариант) позволяет использовать информацию, заложенную в избыточности CRC кода на уровне канального протокола, как при обработке сигнала эквалайзером модема, так и в процессе декодирования помехоустойчивого кода, и может быть использован для обработки сигналов в системах связи, изначально не рассчитанных на его применение. В результате чего достигается совместимость приемной аппаратуры, использующей предлагаемый способ, с прежним парком передающих устройств, но с достижением более высоких характеристик качества связи и скорости работы в новой приемной аппаратуре.

Наиболее близким по технической сущности к предлагаемому устройству (первый вариант) является устройство, описанное в [4], принятое за прототип.

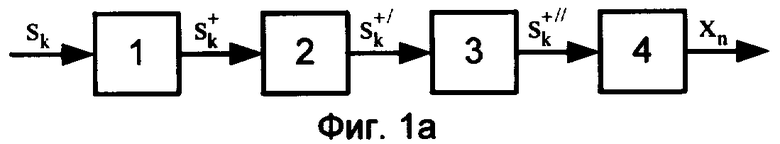

Устройство-прототип состоит из двух частей: передающей и приемной, его блок-схема приведена на фиг.1а, б.

Блок-схема передающей части устройства-прототипа представлена на фиг.1а, где обозначено:

1 - блок добавления CRC;

2 - кодер;

3 - перемежитель;

4 - модулятор;

sk - исходная последовательность бит;

- последовательность бит с добавлением CRC;

- последовательность бит с добавлением CRC;

- закодированная последовательность бит;

- закодированная последовательность бит;

- перемешанная последовательность бит;

- перемешанная последовательность бит;

xn - последовательность комплексных чисел, соответствующих точкам в сигнальном созвездии (символам).

Передающая часть устройства-прототипа содержит последовательно соединенные блок добавления CRC 1, кодер 2, перемежитель 3 и модулятор 4, выход которого является выходом устройства. Вход блока добавления CRC 1 является входом передающей части.

Передающая часть устройства-прототипа работает следующим образом.

На вход устройства поступает последовательность бит sk от какого-либо источника информации. Блок добавления CRC 1 делит ее на фрагменты, добавляя к ним CRC. Полученная последовательность бит  поступает на кодер 2, который производит кодирование этой последовательности помехоустойчивым кодом, в результате чего образуется новая последовательность бит

поступает на кодер 2, который производит кодирование этой последовательности помехоустойчивым кодом, в результате чего образуется новая последовательность бит  , которая поступает на перемежитель 3, где происходит ее перемешивание по определенному закону. Перемешанная последовательность бит

, которая поступает на перемежитель 3, где происходит ее перемешивание по определенному закону. Перемешанная последовательность бит  поступает на модулятор 4, формирующий последовательность символов в виде комплексных чисел xn, соответствующих точкам в выбранном сигнальном созвездии. В дальнейшем эта последовательность символов преобразуется передающей аппаратурой в сигнал, передаваемый по какому-либо каналу связи с МСИ, например по KB каналу с многолучевым распространением.

поступает на модулятор 4, формирующий последовательность символов в виде комплексных чисел xn, соответствующих точкам в выбранном сигнальном созвездии. В дальнейшем эта последовательность символов преобразуется передающей аппаратурой в сигнал, передаваемый по какому-либо каналу связи с МСИ, например по KB каналу с многолучевым распространением.

Блок-схема приемной части устройства-прототипа представлена на фиг.1б, где обозначено:

3 - перемежитель;

5 - согласованный фильтр демодулятора;

6 - SISO эквалайзер;

7 - деперемежитель;

8 - SISO декодер;

9 - переключатель;

10 - детектор;

11 - блок проверки CRC;

y(t) - сигнал, принимаемый из канала связи;

уn - последовательность комплексных чисел на выходе демодулятора;

- последовательность LLR бит на выходе SISO эквалайзера;

- последовательность LLR бит на выходе SISO эквалайзера;

- то же после деперемежителя;

- то же после деперемежителя;

- то же после SISO декодера;

- то же после SISO декодера;

- то же после перемежителя;

- то же после перемежителя;

- последовательность оценок бит после детектора;

- последовательность оценок бит после детектора;

- последовательность окончательных оценок принятых информационных бит.

- последовательность окончательных оценок принятых информационных бит.

Приемная часть устройства-прототипа содержит последовательно соединенные согласованный фильтр демодулятора 5, SISO эквалайзер 6, деперемежитель 7 и SISO декодер 8, выход которого соединен с входом переключателя 9, первый выход которого через детектор 10 соединен с входом блока проверки CRC 11, выход которого является выходом приемной части. Второй выход переключателя 9 через перемежитель 3 соединен со вторым входом SISO эквалайзера 6. Вход согласованного фильтра демодулятора 5 является входом приемной части.

Приемная часть устройства-прототипа работает следующим образом.

Принятый из канала связи сигнал y(t), искаженный МСИ, в смеси с шумом поступает на согласованный фильтр демодулятора 5, где преобразуется в последовательность входных отсчетов в виде комплексных чисел уn. Затем SISO эквалайзер 6 формирует из них последовательность LLR бит  . Деперемежитель 7 восстанавливает исходный порядок следования LLR бит

. Деперемежитель 7 восстанавливает исходный порядок следования LLR бит  , соответствующий исходной закодированной последовательности бит

, соответствующий исходной закодированной последовательности бит  . SISO декодер 8 декодирует последовательность LLR бит

. SISO декодер 8 декодирует последовательность LLR бит  , формируя на своем выходе новую последовательность LLR бит

, формируя на своем выходе новую последовательность LLR бит  , более правдоподобную, благодаря исправляющим свойствам используемого помехоустойчивого кода. Последовательность LLR бит

, более правдоподобную, благодаря исправляющим свойствам используемого помехоустойчивого кода. Последовательность LLR бит  через переключатель 9 подается на перемежитель 3, который формирует перемешанную последовательность LLR бит

через переключатель 9 подается на перемежитель 3, который формирует перемешанную последовательность LLR бит  , которая подается на второй вход SISO эквалайзера 6 в качестве априорных LLR бит. SISO эквалайзер 6 вновь формирует (уже уточненные) LLR бит

, которая подается на второй вход SISO эквалайзера 6 в качестве априорных LLR бит. SISO эквалайзер 6 вновь формирует (уже уточненные) LLR бит  и т.д. Данная итеративная процедура (турбоэквалайзинг) повторяется заданное количество раз, после чего переключатель 9 переводится в другое положение, и выход SISO декодера 8 подается на детектор 10, который формирует последовательность оценок бит

и т.д. Данная итеративная процедура (турбоэквалайзинг) повторяется заданное количество раз, после чего переключатель 9 переводится в другое положение, и выход SISO декодера 8 подается на детектор 10, который формирует последовательность оценок бит  , подаваемую на блок проверки CRC 11. Последовательность окончательных оценок принятых информационных бит

, подаваемую на блок проверки CRC 11. Последовательность окончательных оценок принятых информационных бит  с выхода блока проверки CRC 11 затем передается в какой-либо приемник информации. Фрагменты информации, для которых CRC не совпала, будут перезапрошены у приемной стороны канальным протоколом верхнего уровня.

с выхода блока проверки CRC 11 затем передается в какой-либо приемник информации. Фрагменты информации, для которых CRC не совпала, будут перезапрошены у приемной стороны канальным протоколом верхнего уровня.

На каждой стадии обработки сигнала турбоэквалайзером (оценивании символов SISO эквалайзером 6 или декодировании составляющих символы бит SISO декодером 8) выполняется так называемая «мягкая» оценка символа или бита, передаваемая на следующую ступень обработки в качестве входной (для SISO декодера 8) или априорной (для SISO эквалайзера 6) информации. При этом информация, содержащаяся в проверочных битах CRC кода, никак не принимается в расчет, а используется только после окончания процесса работы турбоэквалайзера, исключительно, для обнаружения допущенных ошибок, но не исправления их.

Таким образом, недостатком устройства-прототипа является то, что информация, заложенная в избыточности CRC кода канального протокола, никак не используется на стадии обработки сигнала эквалайзером модема, осуществляющим устранение искажений, вызванных МСИ, а также декодером помехоустойчивого кода.

Для устранения указанного недостатка в устройство итеративной обработки сигнала для последовательного модема, состоящее из передающей и приемной части, передающая часть содержит последовательно соединенные блок добавления CRC, кодер, перемежитель и модулятор, выход которого является выходом передающей части, а ее вход - входом блока добавления CRC, приемная часть содержит последовательно соединенные согласованный фильтр демодулятора, SISO эквалайзер и деперемежитель, а также SISO декодер, выход которого подсоединен к первому входу первого переключателя, выход которого через перемежитель соединен со вторым входом SISO эквалайзера, последовательно соединенные первый детектор и первый блок проверки CRC, вход согласованного фильтра демодулятора является входом приемной части, согласно изобретению, введены в приемную часть - последовательно соединенные второй детектор и второй блок проверки CRC, а также второй и третий переключатели, причем выход второго блока проверки CRC соединен с первым входом второго переключателя, второй вход которого является входом для значений LLR известных бит, а выход соединен с входом SISO декодера, второй вход первого переключателя является входом для значений LLR известных бит, кроме того, выход деперемежителя подсоединен к третьему входу второго переключателя, выход SISO декодера соединен с входом первого детектора, первый выход первого блока проверки CRC подсоединен к входу третьего переключателя, выход которого является выходом приемной части устройства, второй выход первого блока проверки CRC соединен с третьим входом первого переключателя, выход деперемежителя подсоединен к входу второго детектора.

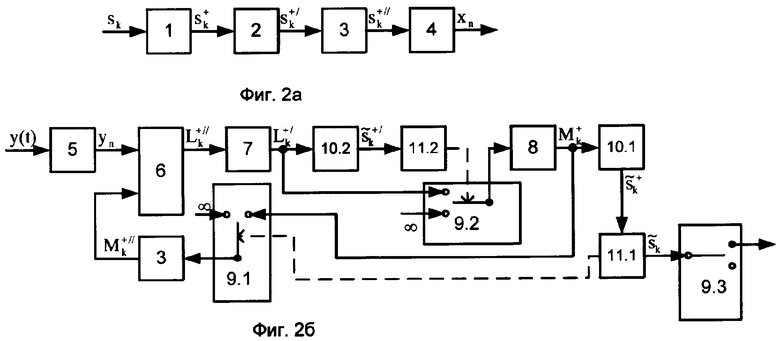

Предлагаемое устройство состоит из двух частей: передающей и приемной, его блок-схема приведена на фиг.2а, б.

Передающая часть предлагаемого устройства полностью совпадает с передающей частью устройства-прототипа (фиг.2а), ее работа также аналогична работе передающей части устройства-прототипа.

Блок-схема приемной части предлагаемого устройства (турбоэквалайзера) представлена на фиг.2б, где обозначено:

3,5 - 8 - как на схеме прототипа;

9.1, 9.2, 9.3 - первый, второй и третий переключатели;

10.1, 10.2 - первый и второй детекторы;

11.1,11.2 - первый и второй блоки проверки CRC;

- последовательность предварительных оценок бит;

- последовательность предварительных оценок бит;

остальные последовательности и сигналы - как на схеме прототипа;

∞ - значение LLR для известных бит.

Приемная часть предлагаемого устройства содержит последовательно соединенные согласованный фильтр демодулятора 5, SISO эквалайзер 6, деперемежитель 7, второй детектор 10.2, второй блок проверки CRC 11.2, выход которого подсоединен к первому входу второго переключателя 9.2, выход которого через последовательно соединенные SISO декодер 8, первый детектор 10.1 и первый блок проверки CRC 11.1 соединен с входом третьего переключателя 9.3, выход которого является выходом приемной части предлагаемого устройства. Кроме того, выход SISO декодера 8 подсоединен к первому входу первого переключателя 9.1, выход которого через перемежитель 3 соединен со вторым входом SISO эквалайзера 6, а второй вход первого переключателя 9.1 является входом для значений LLR известных бит. Выход деперемежителя 7 подсоединен к третьему входу второго переключателя 9.2, второй вход которого является входом для значений LLR известных бит. Второй выход первого блока проверки CRC 11.1 соединен с третьим входом первого переключателя 9.1. При этом вход согласованного фильтра демодулятора 5 является входом приемной части предлагаемого устройства.

Приемная часть предлагаемого устройства работает аналогично приемной части устройства-прототипа, за исключением двух моментов.

Во-первых, последовательность LLR бит  , сформированная в деперемежителе 7, поступает на вход второго детектора 10.2, где преобразуется в последовательность предварительных оценок бит

, сформированная в деперемежителе 7, поступает на вход второго детектора 10.2, где преобразуется в последовательность предварительных оценок бит  . Второй блок проверки CRC 11.2 проверяет CRC отдельных фрагментов бит данной последовательности и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через второй переключатель 9.2 на SISO декодер 8 последовательность LLR бит

. Второй блок проверки CRC 11.2 проверяет CRC отдельных фрагментов бит данной последовательности и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через второй переключатель 9.2 на SISO декодер 8 последовательность LLR бит  (т.е. в точности, как в прототипе). Если же CRC совпала, то на SISO декодер 8 подаются значения LLR, соответствующие, практически, точно известным битам информации, т.е. ∞. Во-вторых, последовательность LLR

(т.е. в точности, как в прототипе). Если же CRC совпала, то на SISO декодер 8 подаются значения LLR, соответствующие, практически, точно известным битам информации, т.е. ∞. Во-вторых, последовательность LLR  , сформированная в SISO декодере 8, в отличие от прототипа, поступает на вход первого детектора 10.1, где преобразуется в последовательность предварительных оценок бит

, сформированная в SISO декодере 8, в отличие от прототипа, поступает на вход первого детектора 10.1, где преобразуется в последовательность предварительных оценок бит  . Первый блок проверки CRC 11.1 проверяет CRC отдельных фрагментов бит и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через первый переключатель 9.1 на перемежитель 3 последовательность LLR

. Первый блок проверки CRC 11.1 проверяет CRC отдельных фрагментов бит и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через первый переключатель 9.1 на перемежитель 3 последовательность LLR  (в точности, как в прототипе). Если же CRC совпала, то на перемежитель 3 подаются LLR, соответствующие, практически, точно известным битам информации, т.е. ∞. В случае, если на какой-либо итерации турбоэквалайзера все биты окажутся декодированы правильно, итерации можно прекратить досрочно и перевести третий переключатель 9.3 в положение, при котором на выход устройства будет подана последовательность окончательных оценок принятых информационных бит

(в точности, как в прототипе). Если же CRC совпала, то на перемежитель 3 подаются LLR, соответствующие, практически, точно известным битам информации, т.е. ∞. В случае, если на какой-либо итерации турбоэквалайзера все биты окажутся декодированы правильно, итерации можно прекратить досрочно и перевести третий переключатель 9.3 в положение, при котором на выход устройства будет подана последовательность окончательных оценок принятых информационных бит  .

.

Таким образом, предлагаемое устройство (первый вариант) позволяет использовать информацию, заложенную в избыточности CRC кода на уровне канального протокола, как при обработке сигнала эквалайзером модема, так и в процессе декодирования помехоустойчивого кода, и может быть использован для обработки сигналов в системах связи, изначально не рассчитанных на его применение. В результате чего достигается совместимость приемной аппаратуры, использующей предлагаемый способ, с прежним парком передающих устройств, но с достижением более высоких характеристик качества связи и скорости работы в новой приемной аппаратуре.

При разработке новой аппаратуры и в других случаях, когда не требуется совместимость новой приемной аппаратуры с прежним парком передающих устройств, а также в ситуациях, когда требуется сохранить независимость обработки информации на различных уровнях иерархии (канальный протокол, помехоустойчивый код), например при предоставлении аппаратурой связи «сквозного» канала для какой-либо другой аппаратуры, возможен другой вариант предлагаемого способа и построения устройства, при котором CRC код добавляется на уровне помехоустойчивого кода и SISO эквалайзера.

Наиболее близким по технической сущности к предлагаемому способу (второй вариант) является способ, приведенный в статье [5], принятый за прототип.

Способ-прототип заключается в следующем.

В передающей части системы связи исходная последовательность бит sk (входная информация) кодируется помехоустойчивым кодом, формируется последовательность бит  , которая перемешивается по определенному закону, формируется последовательность бит

, которая перемешивается по определенному закону, формируется последовательность бит  . Последовательность бит

. Последовательность бит  модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии (символам).

модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии (символам).

В приемной части системы связи принимаемый из канала связи сигнал y(t) (входная информация) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии (принятым символам). Демодулированный сигнал уn подвергается эквалайзингу с учетом априорных значений LLR бит  (на первой итерации равны нулю), формируется последовательность LLR бит

(на первой итерации равны нулю), формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  деперемешивается, формируется последовательность LLR бит

деперемешивается, формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  декодируется, формируется последовательность LLR бит Мк. Если заданное количество итераций еще не закончилось, последовательность LLR бит Мк перемешивается, формируется последовательность LLR бит

декодируется, формируется последовательность LLR бит Мк. Если заданное количество итераций еще не закончилось, последовательность LLR бит Мк перемешивается, формируется последовательность LLR бит  , которая является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, последовательность LLR бит Мк детектируется, формируется выходная последовательность бит

, которая является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, последовательность LLR бит Мк детектируется, формируется выходная последовательность бит  .

.

Недостатком способа-прототипа является отсутствие возможности оценки достоверности принимаемой информации, а также ускорения ее обработки, если эта достоверность высока.

Для устранения указанного недостатка в способе, заключающемся в том, что в передающей части системы связи исходная последовательность бит sk кодируется помехоустойчивым кодом, формируется последовательность бит  , которая перемешивается по определенному закону, формируется последовательность бит

, которая перемешивается по определенному закону, формируется последовательность бит  , в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии, последовательность LLR бит

, в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии, последовательность LLR бит  деперемешивается, формируется последовательность LLR бит

деперемешивается, формируется последовательность LLR бит  , которая декодируется, формируется последовательность LLR бит Мк, если заданное количество итераций закончилось, то полученная после декодирования последовательность LLR бит Мк детектируется, формируется последовательность окончательных оценок бит

, которая декодируется, формируется последовательность LLR бит Мк, если заданное количество итераций закончилось, то полученная после декодирования последовательность LLR бит Мк детектируется, формируется последовательность окончательных оценок бит  , являющаяся выходной, согласно изобретению, в передающей части последовательность бит

, являющаяся выходной, согласно изобретению, в передающей части последовательность бит  разбивают на фрагменты, к каждому из которых добавляют CRC код, формируют последовательность бит

разбивают на фрагменты, к каждому из которых добавляют CRC код, формируют последовательность бит  , которую модулируют, формируют выходную последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии, в приемной части демодулированный сигнал уn подвергают эквалайзингу с учетом априорных значений LLR бит

, которую модулируют, формируют выходную последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии, в приемной части демодулированный сигнал уn подвергают эквалайзингу с учетом априорных значений LLR бит  , которые на первой итерации равны нулю, формируют последовательность LLR бит

, которые на первой итерации равны нулю, формируют последовательность LLR бит  , детектируют последовательность LLR бит

, детектируют последовательность LLR бит  , формируют последовательность предварительных оценок бит

, формируют последовательность предварительных оценок бит  , ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит

, ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, если заданное количество итераций еще не закончилось, то последовательность LLR бит Мк перемешивают, формируют последовательность LLR бит

, для которых CRC совпала, заменяют значениями ∞, если заданное количество итераций еще не закончилось, то последовательность LLR бит Мк перемешивают, формируют последовательность LLR бит  , которую детектируют, формируют последовательность предварительных оценок бит

, которую детектируют, формируют последовательность предварительных оценок бит  , ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит

, ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, последовательность LLR бит

, для которых CRC совпала, заменяют значениями ∞, последовательность LLR бит  является априорной информацией для SISO эквалайзера.

является априорной информацией для SISO эквалайзера.

Предлагаемый способ итеративной обработки сигнала для последовательного модема заключается в следующем.

В передающей части системы связи исходная последовательность бит sk (входная информация) кодируется помехоустойчивым кодом, формируется последовательность бит  , которая перемешивается по определенному закону, формируется последовательность бит

, которая перемешивается по определенному закону, формируется последовательность бит  . Последовательность бит

. Последовательность бит  разбивается на фрагменты, к каждому из которых добавляется CRC код, формируется последовательность бит

разбивается на фрагменты, к каждому из которых добавляется CRC код, формируется последовательность бит  . Последовательность бит

. Последовательность бит  модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии (символам).

модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии (символам).

В приемной части системы связи принимаемый из канала связи сигнал y(t) (входная информация) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии (принятым символам). Затем демодулированный сигнал уn подвергается эквалайзингу с учетом априорных значений LLR бит  (на первой итерации равны нулю), формируется последовательность LLR бит

(на первой итерации равны нулю), формируется последовательность LLR бит  . Последовательность LLR бит

. Последовательность LLR бит  детектируется, формируется последовательность предварительных оценок бит

детектируется, формируется последовательность предварительных оценок бит  . Она разбивается на фрагменты, в которых проверяется CRC. Фрагменты последовательности LLR бит

. Она разбивается на фрагменты, в которых проверяется CRC. Фрагменты последовательности LLR бит  (

( за вычетом LLR, соответствующих битам CRC), для которых CRC совпала, заменяются значениями ∞ (LLR для известных бит). Последовательность LLR бит

за вычетом LLR, соответствующих битам CRC), для которых CRC совпала, заменяются значениями ∞ (LLR для известных бит). Последовательность LLR бит  деперемешивается, формируется последовательность LLR бит

деперемешивается, формируется последовательность LLR бит  , которая декодируется. Формируется последовательность LLR бит Мк. Если заданное количество итераций еще не закончилось, последовательность LLR бит Мк перемешивается, формируется последовательность LLR бит

, которая декодируется. Формируется последовательность LLR бит Мк. Если заданное количество итераций еще не закончилось, последовательность LLR бит Мк перемешивается, формируется последовательность LLR бит  (с вновь добавленными LLR, соответствующими битам CRC кода). Последовательность LLR бит

(с вновь добавленными LLR, соответствующими битам CRC кода). Последовательность LLR бит  детектируется, формируется последовательность предварительных оценок бит

детектируется, формируется последовательность предварительных оценок бит  , она разбивается на фрагменты, в которых проверяется CRC. Фрагменты последовательности LLR бит

, она разбивается на фрагменты, в которых проверяется CRC. Фрагменты последовательности LLR бит  , для которых CRC совпала, заменяются значениями ∞ (LLR для известных бит). Последовательность

, для которых CRC совпала, заменяются значениями ∞ (LLR для известных бит). Последовательность  является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, полученная после декодирования последовательность LLR бит Мк детектируется, формируется последовательность окончательных оценок принятых информационных бит

является априорной информацией для SISO эквалайзера. Если заданное количество итераций закончилось, полученная после декодирования последовательность LLR бит Мк детектируется, формируется последовательность окончательных оценок принятых информационных бит  , являющаяся выходной.

, являющаяся выходной.

Таким образом, предлагаемый способ (второй вариант) позволяет оценивать достоверность принимаемой информации в процессе турбоэквалайзинга, повышая скорость ее обработки и улучшая характеристики качества связи. При этом сохраняется независимость уровней обработки информации.

Наиболее близким по технической сущности к предлагаемому устройству (второй вариант) является устройство, приведенное в статье [5], принятое за прототип.

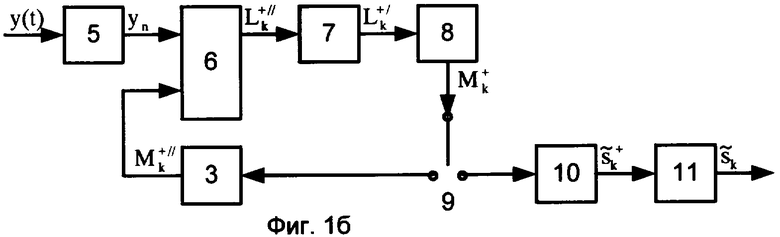

Устройство-прототип состоит из двух частей: передающей и приемной, его блок-схема приведена на фиг.3а, б.

Блок-схема передающей части устройства-прототипа представлена на фиг.3а, где обозначено:

2 - кодер;

3 - перемежитель;

4 - модулятор;

sk - исходная последовательность бит;

- закодированная последовательность бит;

- закодированная последовательность бит;

- перемешанная последовательность бит;

- перемешанная последовательность бит;

xn - последовательность комплексных чисел, соответствующих точкам в сигнальном созвездии (символам).

Передающая часть устройства-прототипа содержит последовательно соединенные кодер 2, перемежитель 3 и модулятор 4, выход которого является выходом передающей части устройства-прототипа, входом которой является вход кодера 2.

Передающая часть устройства-прототипа работает следующим образом.

На вход передающей части устройства поступает последовательность бит sk от какого-либо источника информации. Кодер 2 производит кодирование этой последовательности помехоустойчивым кодом, в результате чего образуется новая последовательность бит  , которая поступает на перемежитель 3, где происходит ее перемешивание по определенному закону. Перемешанная последовательность бит

, которая поступает на перемежитель 3, где происходит ее перемешивание по определенному закону. Перемешанная последовательность бит  поступает на модулятор 4, формирующий последовательность символов в виде комплексных чисел xn, соответствующих точкам в выбранном сигнальном созвездии (символам). В дальнейшем эта последовательность символов преобразуется передающей аппаратурой в сигнал, передаваемый по какому-либо каналу связи с МСИ, например по KB каналу с многолучевым распространением.

поступает на модулятор 4, формирующий последовательность символов в виде комплексных чисел xn, соответствующих точкам в выбранном сигнальном созвездии (символам). В дальнейшем эта последовательность символов преобразуется передающей аппаратурой в сигнал, передаваемый по какому-либо каналу связи с МСИ, например по KB каналу с многолучевым распространением.

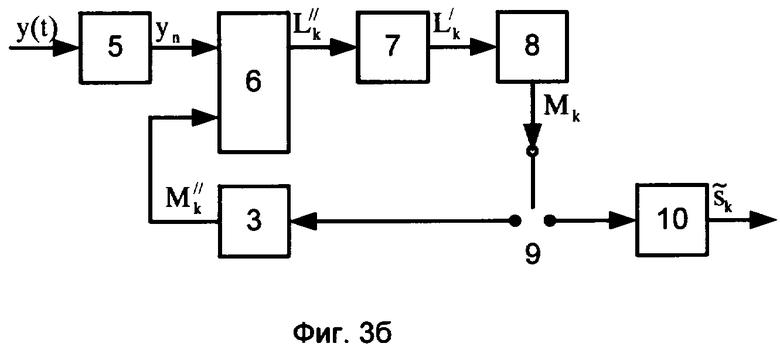

Блок-схема приемной части устройства-прототипа представлена на фиг.3б, где обозначено:

3 - перемежитель;

5 - согласованный фильтр демодулятора;

6 - SISO эквалайзер;

7 - деперемежитель;

8 - SISO декодер;

9 - переключатель;

10 - детектор;

y(t) - сигнал, принимаемый из канала связи;

уn - последовательность комплексных чисел на выходе демодулятора;

- последовательность LLR бит на выходе SISO эквалайзера;

- последовательность LLR бит на выходе SISO эквалайзера;

- то же после деперемежителя;

- то же после деперемежителя;

Мк - то же после SISO декодера;

- то же после перемежителя;

- то же после перемежителя;

- последовательность окончательных оценок принятых информационных бит.

- последовательность окончательных оценок принятых информационных бит.

Приемная часть устройства-прототипа содержит последовательно соединенные согласованный фильтр демодулятора 5, SISO эквалайзер 6, деперемежитель 7 и SISO декодер 8, выход которого соединен с входом переключателя 9, первый выход которого соединен с входом детектора 10, выход которого является выходом приемной части. Второй выход переключателя 9 через перемежитель 3 соединен со вторым входом SISO эквалайзера 6. Вход согласованного фильтра демодулятора 5 является входом приемной части.

Приемная часть устройства-прототипа работает следующим образом.

Принятый из канала связи сигнал y(t), искаженный МСИ, в смеси с шумом поступает на согласованный фильтр демодулятора 5, где преобразуется в последовательность входных отсчетов в виде комплексных чисел уn. Затем SISO эквалайзер 6 формирует из них последовательность LLR бит  . Деперемежитель 7 восстанавливает исходный порядок следования LLR бит

. Деперемежитель 7 восстанавливает исходный порядок следования LLR бит  , соответствующий исходной закодированной последовательности бит

, соответствующий исходной закодированной последовательности бит  . SISO декодер 8 декодирует последовательность LLR бит

. SISO декодер 8 декодирует последовательность LLR бит  , формируя на своем выходе новую последовательность LLR бит Мк, более правдоподобную, благодаря исправляющим свойствам используемого помехоустойчивого кода. Последовательность LLR бит Мк через переключатель 9 подается на перемежитель 3, который формирует перемешанную последовательность LLR бит

, формируя на своем выходе новую последовательность LLR бит Мк, более правдоподобную, благодаря исправляющим свойствам используемого помехоустойчивого кода. Последовательность LLR бит Мк через переключатель 9 подается на перемежитель 3, который формирует перемешанную последовательность LLR бит  , которая подается на второй вход SISO эквалайзера 6 в качестве априорных LLR бит. SISO эквалайзер 6 вновь формирует (уже уточненные) LLR бит

, которая подается на второй вход SISO эквалайзера 6 в качестве априорных LLR бит. SISO эквалайзер 6 вновь формирует (уже уточненные) LLR бит  и т.д. Данная итеративная процедура (турбоэквалайзинг) повторяется заданное количество раз, после чего переключатель 9 переводится в другое положение, и выход SISO декодера 8 подается на детектор 10, который формирует последовательность окончательных оценок принятых информационных бит

и т.д. Данная итеративная процедура (турбоэквалайзинг) повторяется заданное количество раз, после чего переключатель 9 переводится в другое положение, и выход SISO декодера 8 подается на детектор 10, который формирует последовательность окончательных оценок принятых информационных бит  , которая затем передается в какой-либо приемник информации, например на уровень канального протокола.

, которая затем передается в какой-либо приемник информации, например на уровень канального протокола.

Недостатком устройства-прототипа является отсутствие возможности оценки достоверности принимаемой информации, а также ускорения ее обработки, если эта достоверность высока.

Для устранения указанного недостатка в устройство итеративной обработки сигнала для последовательного модема, состоящее из передающей и приемной части, передающая часть содержит последовательно соединенные кодер, перемежитель, а также модулятор, выход которого является выходом передающей части, а ее вход является входом кодера, приемная часть - последовательно соединенные согласованный фильтр демодулятора и SISO эквалайзер, последовательно соединенные деперемежитель, SISO декодер и первый переключатель, первый выход которого соединен с входом первого детектора, второй выход первого переключателя подсоединен к входу перемежителя, причем вход согласованного фильтра демодулятора является входом приемной части, а ее выходом - выход первого детектора, согласно изобретению, введены в передающую часть - блок добавления CRC, выход которого соединен с входом модулятора, а выход перемежителя соединен с входом блока добавления CRC, в приемную часть - второй и третий детекторы, первый и второй блоки проверки CRC, второй и третий переключатели, причем выход SISO эквалайзера через последовательно соединенные третий детектор и первый блок проверки CRC соединен с первым входом второго переключателя, второй вход которого является входом для значений LLR известных бит, выход соединен с входом деперемежителя, а третий вход второго переключателя подсоединен к выходу SISO эквалайзера, выход перемежителя через последовательно соединенные второй детектор и второй блок проверки CRC соединен с первым входом третьего переключателя, второй вход которого является входом для значений LLR известных бит, а выход соединен со вторым входом SISO эквалайзера, выход перемежителя соединен с третьим входом третьего переключателя.

Предлагаемое устройство состоит из двух частей: передающей и приемной, его блок-схема приведена на фиг.4а, б.

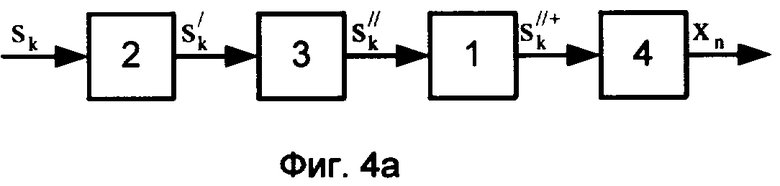

Блок-схема передающей части предлагаемого устройства представлена на фиг.4а, где обозначено:

1 - блок добавления CRC;

2 - 4 - как на схеме прототипа;

- последовательность закодированных и перемешанных бит с добавлением CRC;

- последовательность закодированных и перемешанных бит с добавлением CRC;

остальные последовательности и сигналы - как на схеме прототипа.

Передающая часть предлагаемого устройства содержит последовательно соединенные кодер 2, перемежитель 3, блок добавления CRC 1 и модулятор 4, выход которого является выходом передающей части, а ее входом - вход кодера 2.

Передающая часть предлагаемого устройства работает аналогично прототипу, за исключением одного момента.

Перемешанная в перемежителе 3 последовательность бит  поступает на блок добавления CRC 1, который делит ее на фрагменты, добавляя к ним CRC. Полученная при этом последовательность бит

поступает на блок добавления CRC 1, который делит ее на фрагменты, добавляя к ним CRC. Полученная при этом последовательность бит  поступает на модулятор 4, формирующий последовательность символов в виде комплексных чисел xn, соответствующих точкам в выбранном сигнальном созвездии.

поступает на модулятор 4, формирующий последовательность символов в виде комплексных чисел xn, соответствующих точкам в выбранном сигнальном созвездии.

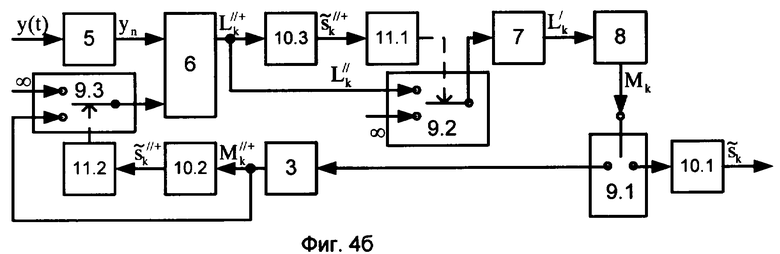

Блок-схема приемной части предлагаемого устройства представлена на фиг.4б, где обозначено:

3,5 - 8 - как на схеме прототипа;

9.1, 9.2, 9.3 - первый, второй и третий переключатели;

10.1, 10.2, 10.3 - первый, второй и третий детекторы;

11.1, 11.2 - первый и второй блоки проверки CRC;

- последовательность LLR бит на выходе SISO эквалайзера;

- последовательность LLR бит на выходе SISO эквалайзера;

- то же, за вычетом LLR, соответствующих битам CRC;

- то же, за вычетом LLR, соответствующих битам CRC;

- то же, после SISO декодера и перемежителя;

- то же, после SISO декодера и перемежителя;

- последовательность предварительных оценок бит;

- последовательность предварительных оценок бит;

остальные последовательности и сигналы - как на схеме прототипа.

Приемная часть предлагаемого устройства содержит последовательно соединенные согласованный фильтр демодулятора 5, SISO эквалайзер 6, третий детектор 10.3, первый блок проверки CRC 11.1, выход которого подсоединен к первому входу второго переключателя 9.2, выход которого через последовательно соединенные деперемежитель 7 и SISO декодер 8 соединен с входом первого переключателя 9.1, первый выход которого соединен с входом первого детектора 10.1, выход которого является выходом приемной части. Второй выход первого переключателя 9.1 через последовательно соединенные перемежитель 3, второй детектор 10.2 и второй блок проверки CRC 11.2 соединен с первым входом третьего переключателя 9.3, выход которого соединен со вторым входом SISO эквалайзера 6, выход которого соединен с третьим входом второго переключателя 9.2, второй вход которого является входом для значений LLR известных бит. При этом выход перемежителя 3 подсоединен к третьему входу третьего переключателя 9.3, второй вход которого является входом для значений LLR известных бит. Вход согласованного фильтра демодулятора 5 является входом приемной части предлагаемого устройства.

Приемная часть предлагаемого устройства работает аналогично прототипу, за исключением двух моментов.

Во-первых, SISO эквалайзер 6 формирует из комплексных чисел уn последовательность LLR бит  , которая поступает на вход третьего детектора 10.3, где преобразуется в последовательность предварительных оценок бит

, которая поступает на вход третьего детектора 10.3, где преобразуется в последовательность предварительных оценок бит  . Первый блок проверки CRC 11.1 проверяет CRC отдельных порций бит (фрагментов) и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через второй переключатель 9.2 на деперемежитель 7 последовательность LLR бит

. Первый блок проверки CRC 11.1 проверяет CRC отдельных порций бит (фрагментов) и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через второй переключатель 9.2 на деперемежитель 7 последовательность LLR бит  (

( за вычетом LLR, соответствующих битам CRC, т.е. в точности, как в прототипе). Если же CRC совпала, то на деперемежитель 7 подаются LLR, соответствующие известным битам информации, т.е. ∞, что существенно повысит качество декодирования остальных бит на текущей итерации турбоэквалайзера. Во-вторых, последовательность LLR бит

за вычетом LLR, соответствующих битам CRC, т.е. в точности, как в прототипе). Если же CRC совпала, то на деперемежитель 7 подаются LLR, соответствующие известным битам информации, т.е. ∞, что существенно повысит качество декодирования остальных бит на текущей итерации турбоэквалайзера. Во-вторых, последовательность LLR бит  , сформированная в перемежителе 3, подается на вход второго детектора 10.2, где преобразуется в последовательность предварительных оценок бит

, сформированная в перемежителе 3, подается на вход второго детектора 10.2, где преобразуется в последовательность предварительных оценок бит  . Второй блок проверки CRC 11.2 проверяет CRC отдельных порций бит (фрагментов) и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через переключатель 9.3 на SISO эквалайзер 6 последовательность LLR бит

. Второй блок проверки CRC 11.2 проверяет CRC отдельных порций бит (фрагментов) и, если CRC не совпала (т.е. фрагмент принят с ошибками), передает через переключатель 9.3 на SISO эквалайзер 6 последовательность LLR бит  . Если же CRC совпала, то на SISO эквалайзер 6 подаются LLR, соответствующие известным битам информации, т.е. ∞, что также повысит качество декодирования остальных бит на следующей итерации турбоэквалайзера. SISO эквалайзер 6 вновь формирует (уже уточненные) LLR

. Если же CRC совпала, то на SISO эквалайзер 6 подаются LLR, соответствующие известным битам информации, т.е. ∞, что также повысит качество декодирования остальных бит на следующей итерации турбоэквалайзера. SISO эквалайзер 6 вновь формирует (уже уточненные) LLR  для каждого бита и т.д. В случае, если на какой-либо итерации турбоэквалайзера все биты окажутся декодированы правильно, итерации можно прекратить досрочно и перевести первый переключатель 9.1 в соответствующее положение. Очевидно, что для фрагментов информации, для которых данная итеративная процедура не была завершена досрочно, CRC не совпала. Это значит, что они будут приняты с ошибками, либо, при наличии протокола верхнего уровня (со своим CRC), - перезапрошены.

для каждого бита и т.д. В случае, если на какой-либо итерации турбоэквалайзера все биты окажутся декодированы правильно, итерации можно прекратить досрочно и перевести первый переключатель 9.1 в соответствующее положение. Очевидно, что для фрагментов информации, для которых данная итеративная процедура не была завершена досрочно, CRC не совпала. Это значит, что они будут приняты с ошибками, либо, при наличии протокола верхнего уровня (со своим CRC), - перезапрошены.

Таким образом, предлагаемое устройство (второй вариант) позволяет оценивать достоверность принимаемой информации в процессе турбоэквалайзинга, повышая скорость ее обработки и улучшая характеристики качества связи. При этом сохраняется независимость уровней обработки информации.

Следует иметь ввиду, что CRC код, используемый в первом варианте предлагаемого технического решения, является частью канального протокола верхнего уровня, в то время как CRC код, используемый во втором варианте предлагаемого технического решения, является дополнительным (новым) звеном обработки сигнала на уровне помехоустойчивого кода и никак не связанным с канальным протоколом.

Таким образом, предлагаемое техническое решение (второй вариант) может также использоваться с канальным протоколом, включающим свой CRC код. При этом CRC коды двух разных уровней будут действовать параллельно и независимо.

Предлагаемые способ и устройство повышают вероятность правильного приема информации, улучшая помехоустойчивость аппаратуры связи, а также уменьшают время обработки сигнала турбоэквалайзером последовательного модема за счет уменьшения числа итераций, уменьшая тем самым необходимое количество вычислительных ресурсов.

Первый вариант предлагаемого технического решения более предпочтителен с точки зрения совместимости с эксплуатируемой в настоящий момент аппаратурой связи.

Второй вариант является более предпочтительным с точки зрения степени улучшения качества связи и сохранения независимости уровней обработки информации.

Источники информации

1. Douillard, С, Jézéquel, М., Веrrоu, С, Picart, A., Didier, P. and Glavieux, А.: 1995, Iterative correction of intersymbol interference: Turbo-equalization, Eur. Trans. Telecommunications 6(5), 507-511.

2. Glavieux, A., Laot, C. and Labat, J.: 1997, Turbo equalization over a frequency selective channel, Proc. Int. Symp on Turbo Codes & Related Topics, ENST Bretagne, Brest, France, pp.96-102.

3. Nieto, J.W.: 2005, Iterative equalization and decoding of STANAG 4539 9600 bps HF waveforms.

4. Otnes, R. and Tüchler, M.: 2001, Block SISO linear equalizers for turbo equalization in serial-tone HF modems.

5. Tüchler, M., Koetter, R. and Singer, A. C: 2002, Turbo equalization: Principles and new results, IEEE Trans. Communications 50(5), 754-767.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ МОДЕМ С КОМБИНИРОВАННОЙ ОБРАТНОЙ СВЯЗЬЮ | 2009 |

|

RU2405274C1 |

| ПЕРЕДАЧА С ИНКРЕМЕНТНОЙ ИЗБЫТОЧНОСТЬЮ В СИСТЕМЕ СВЯЗИ MIMO | 2004 |

|

RU2502197C2 |

| ПЕРЕДАЧА С ИНКРЕМЕНТНОЙ ИЗБЫТОЧНОСТЬЮ В СИСТЕМЕ СВЯЗИ MIMO | 2004 |

|

RU2369021C2 |

| ТУРБО-ПЕРЕМЕЖИТЕЛЬ ДЛЯ ВЫСОКИХ СКОРОСТЕЙ ПЕРЕДАЧИ ДАННЫХ | 2007 |

|

RU2435298C2 |

| ИЕРАРХИЧЕСКОЕ КОДИРОВАНИЕ С ИСПОЛЬЗОВАНИЕМ МНОЖЕСТВА АНТЕНН В СИСТЕМЕ РАДИОСВЯЗИ | 2004 |

|

RU2316900C1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА | 2008 |

|

RU2427095C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТУРБОКОДОВ | 2007 |

|

RU2369961C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2656830C2 |

| СПОСОБ ИТЕРАТИВНОГО ДЕТЕКТИРОВАНИЯ И ДЕКОДИРОВАНИЯ СИГНАЛА В СИСТЕМАХ СВЯЗИ С MIMO КАНАЛОМ | 2012 |

|

RU2523190C1 |

Изобретение предназначено для использования в системах связи, применяемых для передачи информации по каналам связи с межсимвольной интерференцией, когда требуется высокая достоверность передачи данных. Технический результат - повышение вероятности правильного приема информации, улучшение помехоустойчивости аппаратуры связи, уменьшение времени обработки сигнала турбоэквалайзером последовательного модема за счет уменьшения числа итераций и уменьшения необходимого количества вычислительных ресурсов. В способе итеративной обработки сигнала для последовательного модема (первый вариант) в приемной части детектируют последовательности LLR бит после деперемежителя и SISO декодера, формируют последовательности предварительных оценок бит, в которых проверяют CRC. В устройство (первый вариант) введены в приемную часть последовательно соединенные второй детектор и второй блок проверки CRC, а также второй и третий переключатели. Второй вариант способа включает в передающей части - добавление CRC кода после перемежителя, в приемной части - детектирование последовательности LLR бит после SISO эквалайзера и перемежителя, формирование последовательности предварительных оценок бит и проверку в них CRC. Во втором варианте устройства введены в передающую часть - блок добавления CRC, в приемную часть - второй и третий детекторы, первый и второй блоки проверки CRC, второй и третий переключатели. 4 н.п. ф-лы, 4 ил.

1. Способ итеративной обработки сигнала для последовательного модема, заключающийся в том, что в передающей части системы связи исходная последовательность бит sk разбивается на фрагменты, к каждому из которых добавляется CRC код, формируется последовательность бит  , которая кодируется помехоустойчивым кодом, формируется последовательность бит

, которая кодируется помехоустойчивым кодом, формируется последовательность бит  , которая перемешивается по определенному закону, формируется последовательность бит

, которая перемешивается по определенному закону, формируется последовательность бит  , которая модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии, в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии, далее демодулированный сигнал yn подвергается эквалайзингу с учетом априорных значений LLR бит

, которая модулируется, формируется выходная последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии, в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел уn, соответствующих точкам в сигнальном созвездии, далее демодулированный сигнал yn подвергается эквалайзингу с учетом априорных значений LLR бит  , которые на первой итерации равны нулю, формируется последовательность LLR бит

, которые на первой итерации равны нулю, формируется последовательность LLR бит  , которая деперемешивается, формируется последовательность LLR бит

, которая деперемешивается, формируется последовательность LLR бит  , которая декодируется, формируется последовательность LLR бит

, которая декодируется, формируется последовательность LLR бит  , если заданное количество итераций еще не закончилось, то последовательность LLR бит

, если заданное количество итераций еще не закончилось, то последовательность LLR бит  перемешивается, формируется последовательность LLR бит

перемешивается, формируется последовательность LLR бит  , которая является априорной информацией для SISO эквалайзера, отличающийся тем, что в приемной части детектируют последовательность LLR бит

, которая является априорной информацией для SISO эквалайзера, отличающийся тем, что в приемной части детектируют последовательность LLR бит  , формируют последовательность предварительных оценок бит

, формируют последовательность предварительных оценок бит  , разбивают на фрагменты последовательность предварительных оценок бит

, разбивают на фрагменты последовательность предварительных оценок бит  , в которых проверяют CRC, фрагменты последовательности LLR бит

, в которых проверяют CRC, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, детектируют последовательность LLR бит

, для которых CRC совпала, заменяют значениями ∞, детектируют последовательность LLR бит  , формируют последовательность предварительных оценок бит

, формируют последовательность предварительных оценок бит  , далее ее разбивают на фрагменты, в которых проверяют CRC, формируют последовательность оценок бит

, далее ее разбивают на фрагменты, в которых проверяют CRC, формируют последовательность оценок бит  , фрагменты последовательности LLR бит

, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, после окончания заданного количества итераций полученная после проверки CRC последовательность оценок бит

, для которых CRC совпала, заменяют значениями ∞, после окончания заданного количества итераций полученная после проверки CRC последовательность оценок бит  становится выходной, причем благодаря CRC коду, выявляют фрагменты, принятые с ошибками.

становится выходной, причем благодаря CRC коду, выявляют фрагменты, принятые с ошибками.

2. Устройство итеративной обработки сигнала для последовательного модема, состоящее из передающей и приемной части, при этом: передающая часть содержит последовательно соединенные блок добавления CRC, кодер, перемежитель и модулятор, выход которого является выходом передающей части, а ее вход - входом блока добавления CRC, приемная часть содержит последовательно соединенные согласованный фильтр демодулятора, SISO эквалайзер и деперемежитель, а также SISO декодер, выход которого подсоединен к первому входу первого переключателя, выход которого через перемежитель соединен со вторым входом SISO эквалайзера, последовательно соединенные первый детектор и первый блок проверки CRC, вход согласованного фильтра демодулятора является входом приемной части, отличающееся тем, что введены в приемную часть последовательно соединенные второй детектор и второй блок проверки CRC, а также второй и третий переключатели, причем выход второго блока проверки CRC соединен с первым входом второго переключателя, второй вход которого является входом для значений LLR известных бит, а выход соединен с входом SISO декодера, второй вход первого переключателя является входом для значений LLR известных бит, кроме того, выход деперемежителя подсоединен к третьему входу второго переключателя, выход SISO декодера соединен с входом первого детектора, первый выход первого блока проверки CRC подсоединен к входу третьего переключателя, выход которого является выходом приемной части устройства, второй выход первого блока проверки CRC соединен с третьим входом первого переключателя, выход деперемежителя подсоединен к входу второго детектора.

3. Способ итеративной обработки сигнала для последовательного модема, заключающийся в том, что в передающей части системы связи исходная последовательность бит кодируется помехоустойчивым кодом, формируется последовательность бит s'k, которая перемешивается по определенному закону, формируется последовательность бит  , в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел yn, соответствующих точкам в сигнальном созвездии, последовательность LLR бит

, в приемной части системы связи принимаемый из канала связи сигнал y(t) демодулируется, формируется последовательность комплексных чисел yn, соответствующих точкам в сигнальном созвездии, последовательность LLR бит  деперемешивается, формируется последовательность LLR бит

деперемешивается, формируется последовательность LLR бит  , которая декодируется, формируется последовательность LLR бит Мk, если заданное количество итераций закончилось, то полученная после декодирования последовательность LLR бит Mk детектируется, формируется последовательность окончательных оценок бит

, которая декодируется, формируется последовательность LLR бит Мk, если заданное количество итераций закончилось, то полученная после декодирования последовательность LLR бит Mk детектируется, формируется последовательность окончательных оценок бит  , являющаяся выходной, отличающийся тем, что в передающей части последовательность бит

, являющаяся выходной, отличающийся тем, что в передающей части последовательность бит  разбивают на фрагменты, к каждому из которых добавляют CRC код, формируют последовательность бит

разбивают на фрагменты, к каждому из которых добавляют CRC код, формируют последовательность бит  , которую модулируют, формируют выходную последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии, в приемной части демодулированный сигнал yn подвергают эквалайзингу с учетом априорных значений LLR бит

, которую модулируют, формируют выходную последовательность комплексных чисел xn, соответствующих точкам в сигнальном созвездии, в приемной части демодулированный сигнал yn подвергают эквалайзингу с учетом априорных значений LLR бит  , которые на первой итерации равны нулю, формируют последовательность LLR бит

, которые на первой итерации равны нулю, формируют последовательность LLR бит  , детектируют последовательность LLR бит

, детектируют последовательность LLR бит  , формируют последовательность предварительных оценок бит

, формируют последовательность предварительных оценок бит  , ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит

, ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, если заданное количество итераций еще не закончилось, то последовательность LLR бит Мk перемешивают, формируют последовательность LLR бит

, для которых CRC совпала, заменяют значениями ∞, если заданное количество итераций еще не закончилось, то последовательность LLR бит Мk перемешивают, формируют последовательность LLR бит  , которую детектируют, формируют последовательность предварительных оценок бит

, которую детектируют, формируют последовательность предварительных оценок бит  , ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит

, ее разбивают на фрагменты, в которых проверяют CRC, фрагменты последовательности LLR бит  , для которых CRC совпала, заменяют значениями ∞, последовательность LLR бит

, для которых CRC совпала, заменяют значениями ∞, последовательность LLR бит  является априорной информацией для SISO эквалайзера.

является априорной информацией для SISO эквалайзера.

4. Устройство итеративной обработки сигнала для последовательного модема, состоящее из передающей и приемной части, при этом: передающая часть содержит последовательно соединенные кодер, перемежитель, а также модулятор, выход которого является выходом передающей части, а ее вход является входом кодера, приемная часть - последовательно соединенные согласованный фильтр демодулятора и SISO эквалайзер, последовательно соединенные деперемежитель, SISO декодер и первый переключатель, первый выход которого соединен с входом первого детектора, второй выход первого переключателя подсоединен к входу перемежителя, причем вход согласованного фильтра демодулятора является входом приемной части, а ее выходом - выход первого детектора, отличающееся тем, что введены в передающую часть - блок добавления CRC, выход которого соединен с входом модулятора, а выход перемежителя соединен с входом блока добавления CRC, в приемную часть - второй и третий детекторы, первый и второй блоки проверки CRC, второй и третий переключатели, причем выход SISO эквалайзера через последовательно соединенные третий детектор и первый блок проверки CRC соединен с первым входом второго переключателя, второй вход которого является входом для значений LLR известных бит, выход соединен с входом деперемежителя, а третий вход второго переключателя подсоединен к выходу SISO эквалайзера, выход перемежителя через последовательно соединенные второй детектор и второй блок проверки CRC соединен с первым входом третьего переключателя, второй вход которого является входом для значений LLR известных бит, а выход соединен со вторым входом SISO эквалайзера, выход перемежителя соединен с третьим входом третьего переключателя.

| СПОСОБ РАЗНЕСЕННОЙ ПЕРЕДАЧИ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2001 |

|

RU2208911C2 |

| СПОСОБ СВАРКИ Л^ЕТАЛЛОВ | 0 |

|

SU182488A1 |

| WO 03092170 A1, 06.11.2003. | |||

Авторы

Даты

2009-09-27—Публикация

2008-04-14—Подача