Область техники, к которой относится изобретение

Данная технология относится к устройству обработки данных и способу обработки данных и, в частности, относится к устройству обработки данных и способу обработки данных, которые способны обеспечить хорошее качество связи при передаче данных с использованием, например, LDPC-кода.

Уровень техники

Код разреженного контроля четности (LDPC) имеет высокую способность коррекции ошибки и в последние годы широко использовался в схеме передачи, включающей в себя цифровое широковещание, такое как, например, европейский стандарт цифрового телевизионного вещания (DVB)-S.2, DVB-T.2 и DVB-C.2 (например, смотри NPL 1).

Последние исследования показывают, что при увеличении длины кода LDPC-код имеет характеристики, близкие к пределу Шеннона и аналогичные турбокодам или т.п. В дополнение к этому, поскольку LDPC-код имеет свойства минимального расстояния, пропорционального длине кода, LDPC-код имеет преимущество в том, что характеристика вероятности блочной ошибки является хорошей, и так называемое явление минимального уровня ошибок, которое наблюдается как свойство декодирования турбо-кода или т.п., почти не возникает в виде свойства.

Перечень цитируемой литературы

Непатентная литература

NPL 1: DVB-S.2: ETSI EN 302307 V1.2.1 (2009-08)

Сущность изобретения

Техническая задача

При передаче данных с использованием, например, LDPC-кода, LDPC-код формируется в символе квадратурной модуляции (цифровой модуляции), такой как квадратурная фазовая манипуляция (QPSK) (символизируется), и символ передается путем отображения в сигнальную точку квадратурной модуляции.

Такая передача данных с использованием LDPC-кода становится широко распространенной во всем мире, и остается востребованным обеспечение хорошего качества связи.

Данная технология была выполнена с учетом таких обстоятельств, и задача изобретения состоит в том, чтобы обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

Решение технической задачи

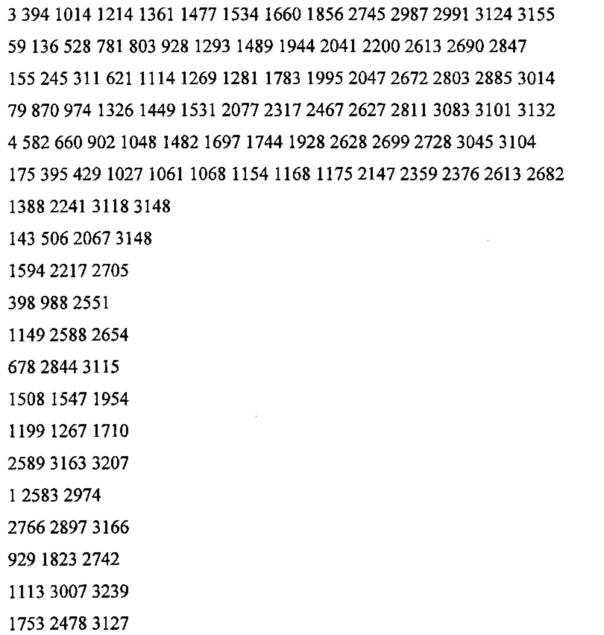

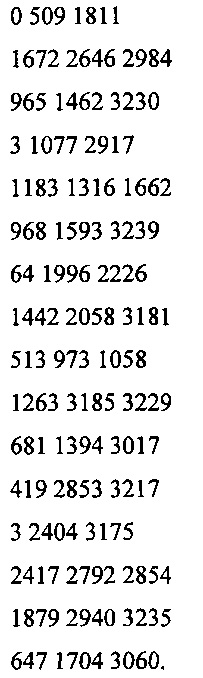

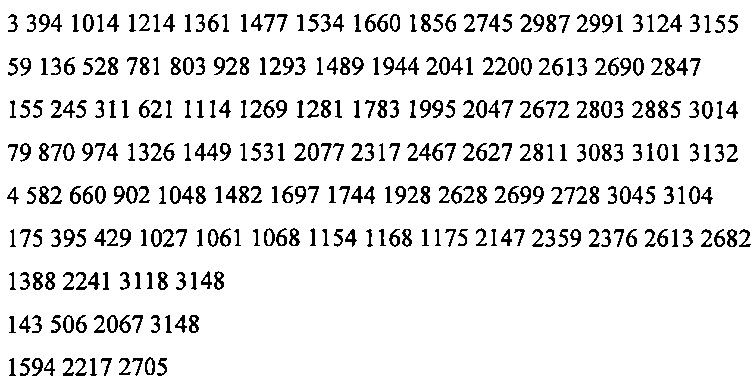

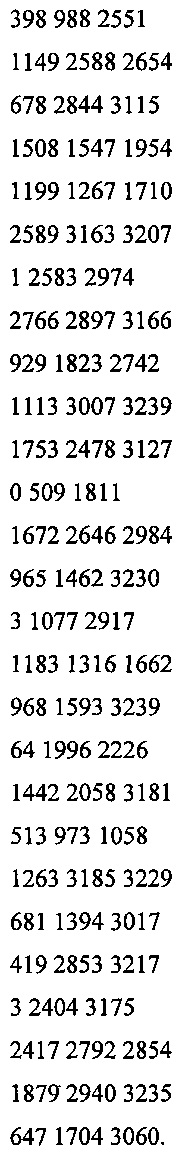

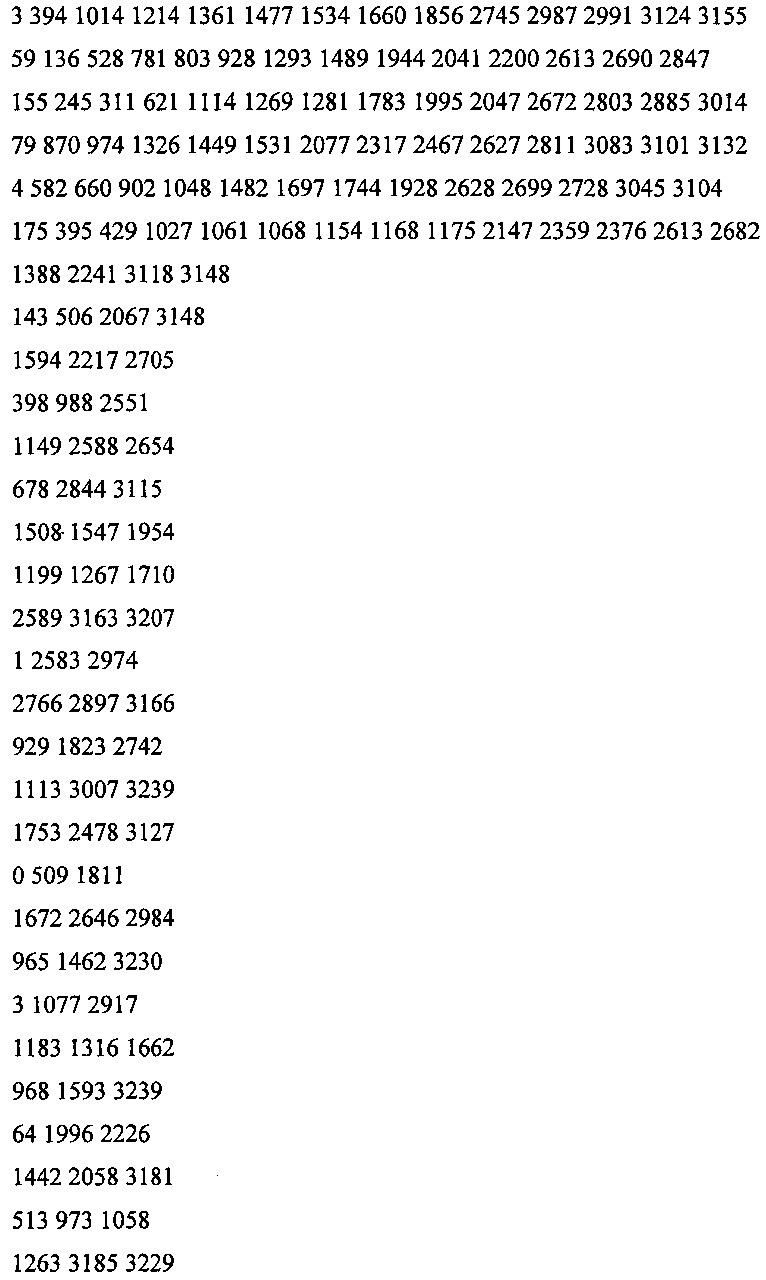

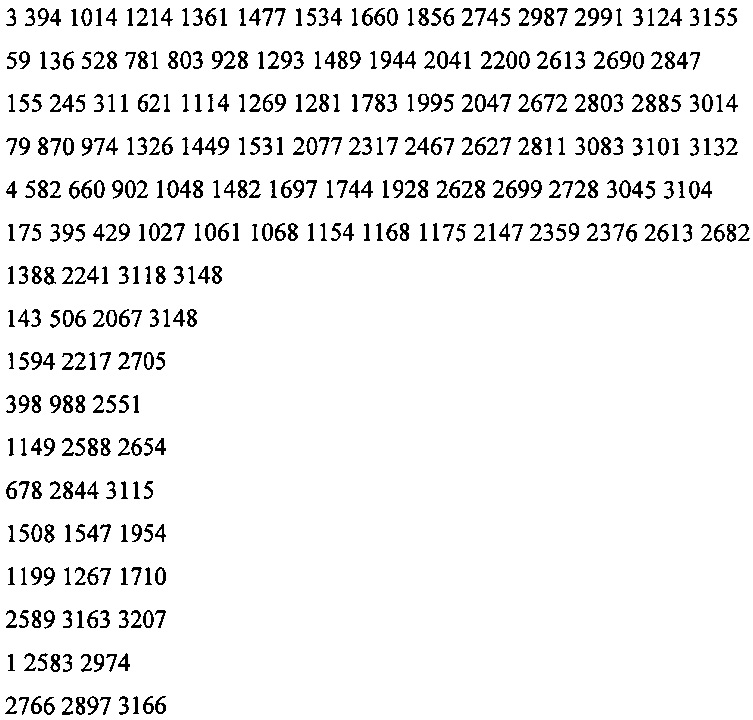

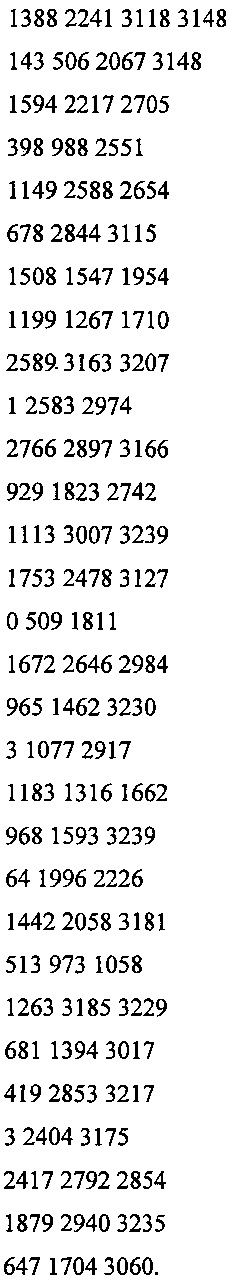

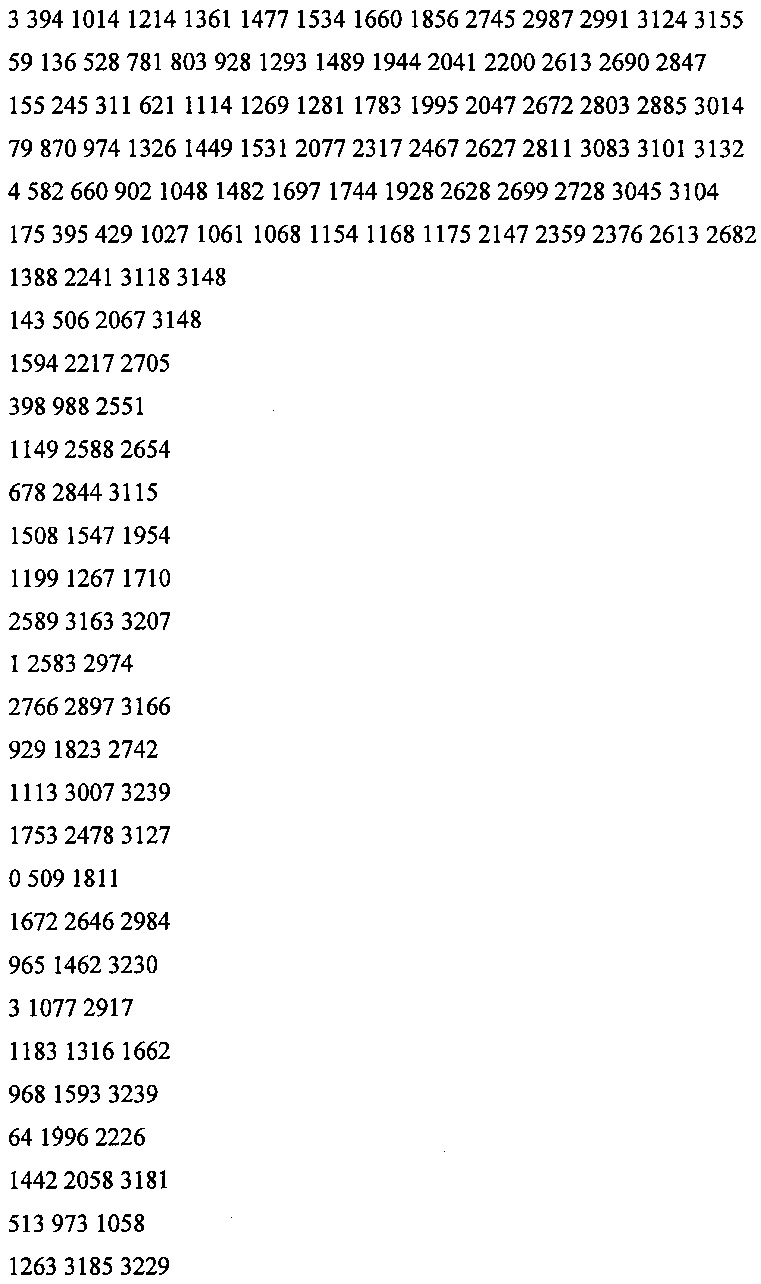

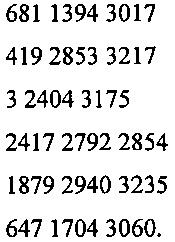

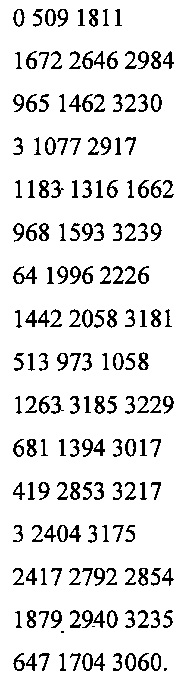

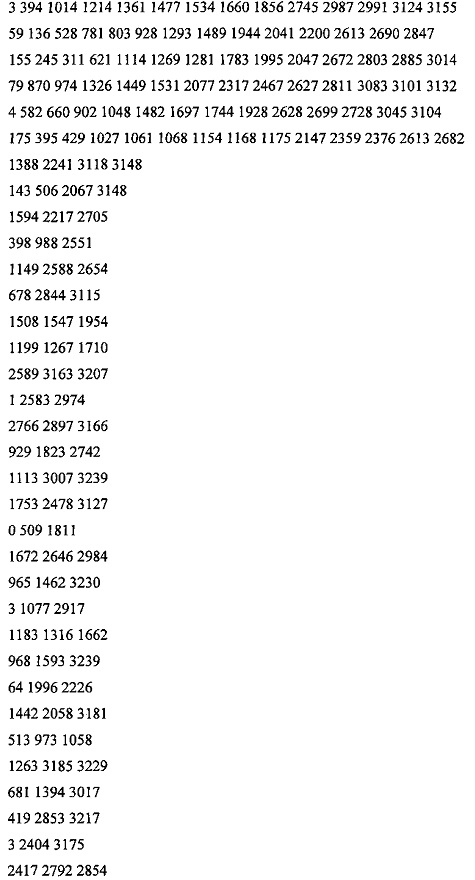

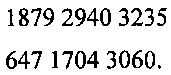

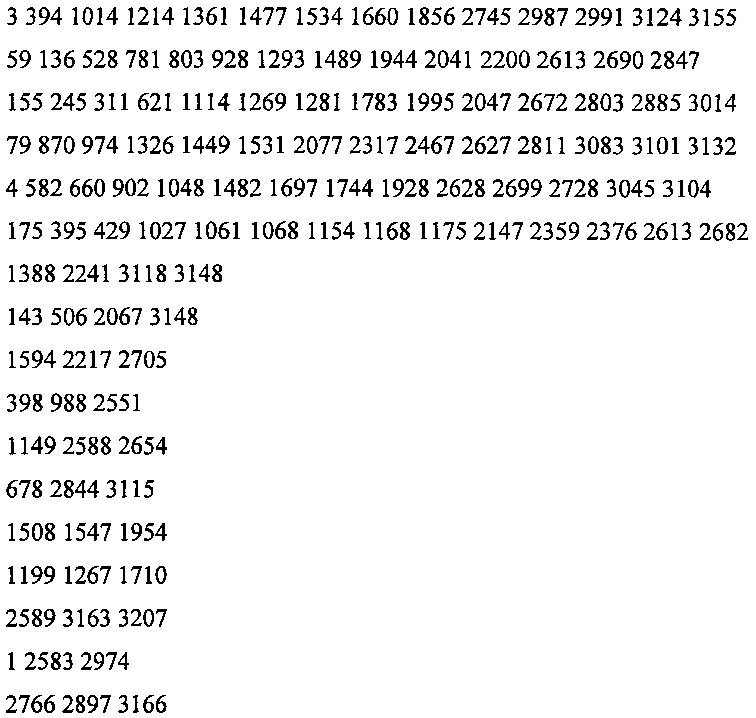

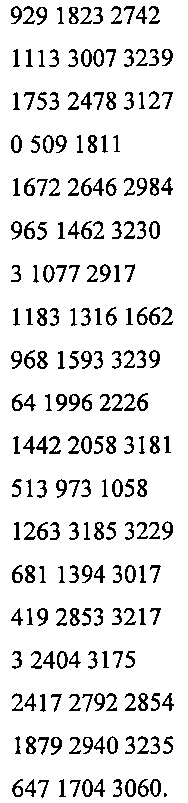

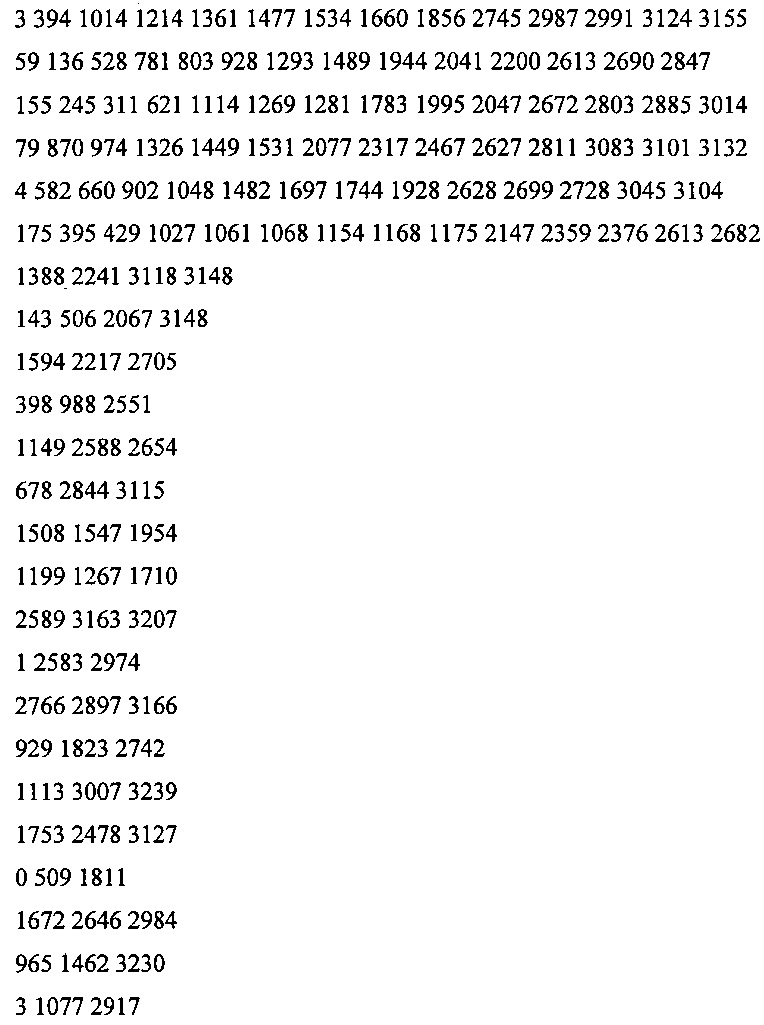

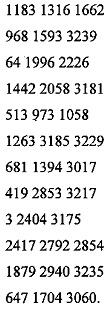

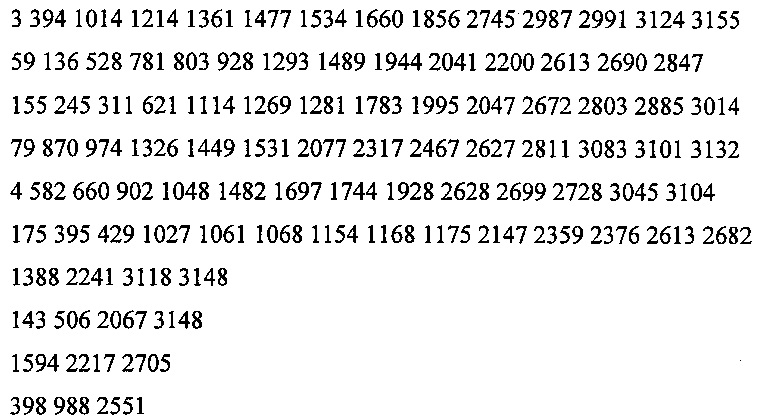

Первое устройство обработки данных (способ обработки данных) данной технологии включает в себя блок кодирования (этап кодирования), который кодирует информационный бит в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

В первом устройстве обработки данных/способе обработки данных, информационный бит кодируется в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC). LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

Второе устройство обработки данных (способ обработки данных) данной технологии включает в себя блок декодирования (этап декодирования), который декодирует LDPC-код, полученный из данных, которые передаются из передающего устройства, включающего в себя блок кодирования, который кодирует информационный бит в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

Во втором устройстве обработки данных/способе обработки данных декодируется LDPC-код, который получается из данных, переданных из передающего устройства, причем передающее устройство включает в себя блок кодирования (этап кодирования) который кодирует информационный бит в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

Третье устройство обработки данных данной технологии включает в себя блок декодирования, который декодирует LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

В третьем устройстве обработки данных LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, декодируется на основании матрицы контроля четности кода разреженного контроля четности (LDPC). LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

В дополнение, устройство обработки данных может представлять собой независимое устройство или может представлять собой внутренний блок, конфигурирующий одно устройство.

Преимущественные эффекты изобретения

Согласно настоящему изобретению можно обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

В дополнение к этому, эффекты, описанные в данном документе, являются только иллюстративными, при этом эффекты данной технологии не предназначены для ограничения эффектов, которые описаны в данном документе, и могут существовать дополнительные эффекты.

Краткое описание чертежей

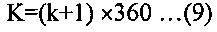

Фиг. 1 - схема, изображающая матрицу Н контроля четности LDPC-кода.

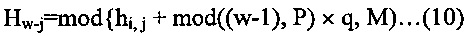

Фиг. 2 - блок-схема последовательности операций, иллюстрирующая процедуру декодирования LDPC-кода.

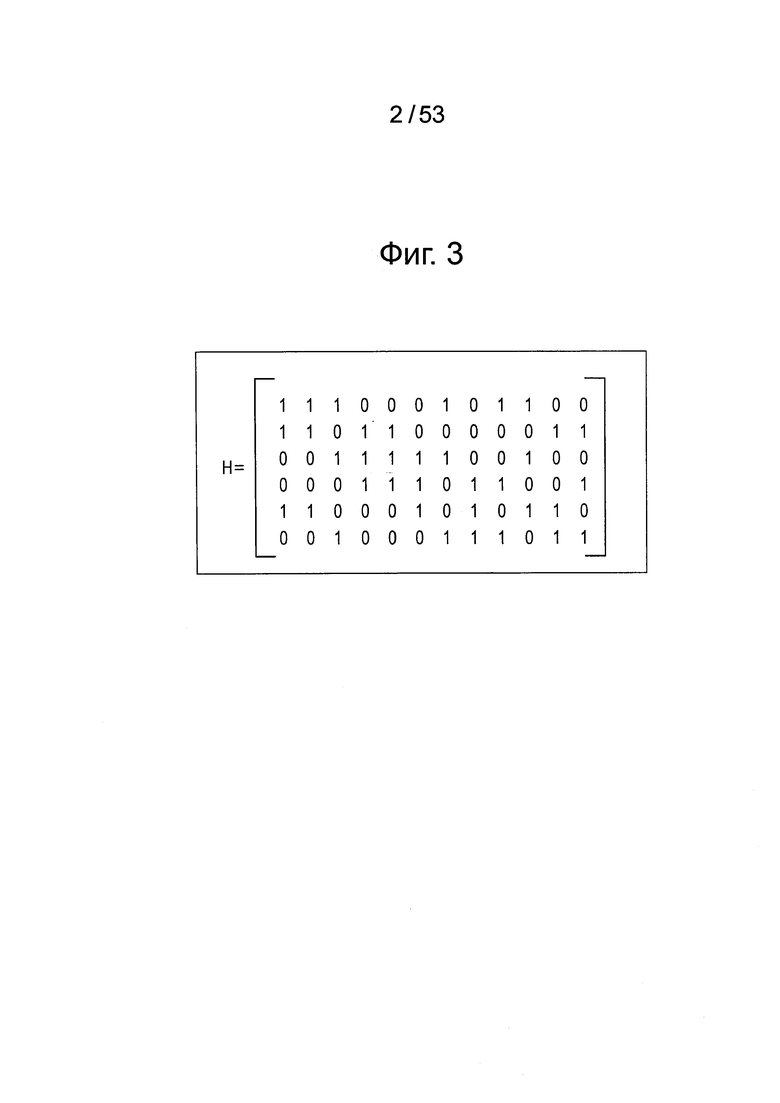

Фиг. 3 - схема, иллюстрирующая пример матрицы контроля четности LDPC-кода.

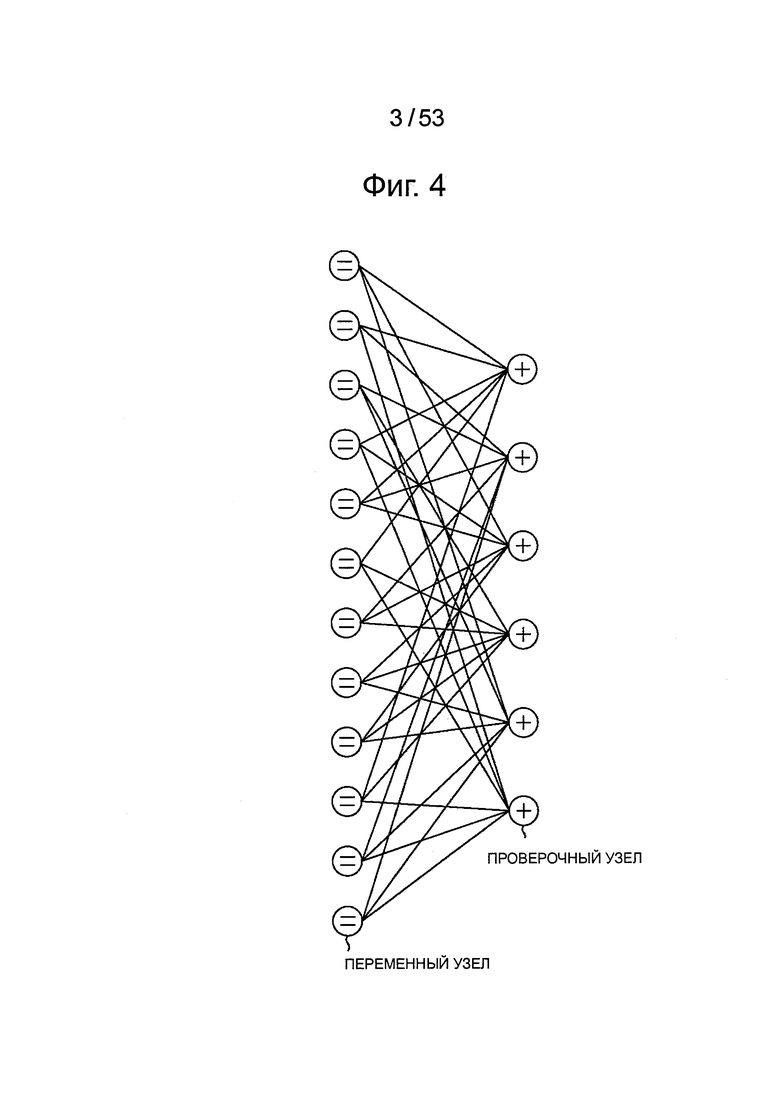

Фиг. 4 - схема, иллюстрирующая график Таннера матрицы контроля четности.

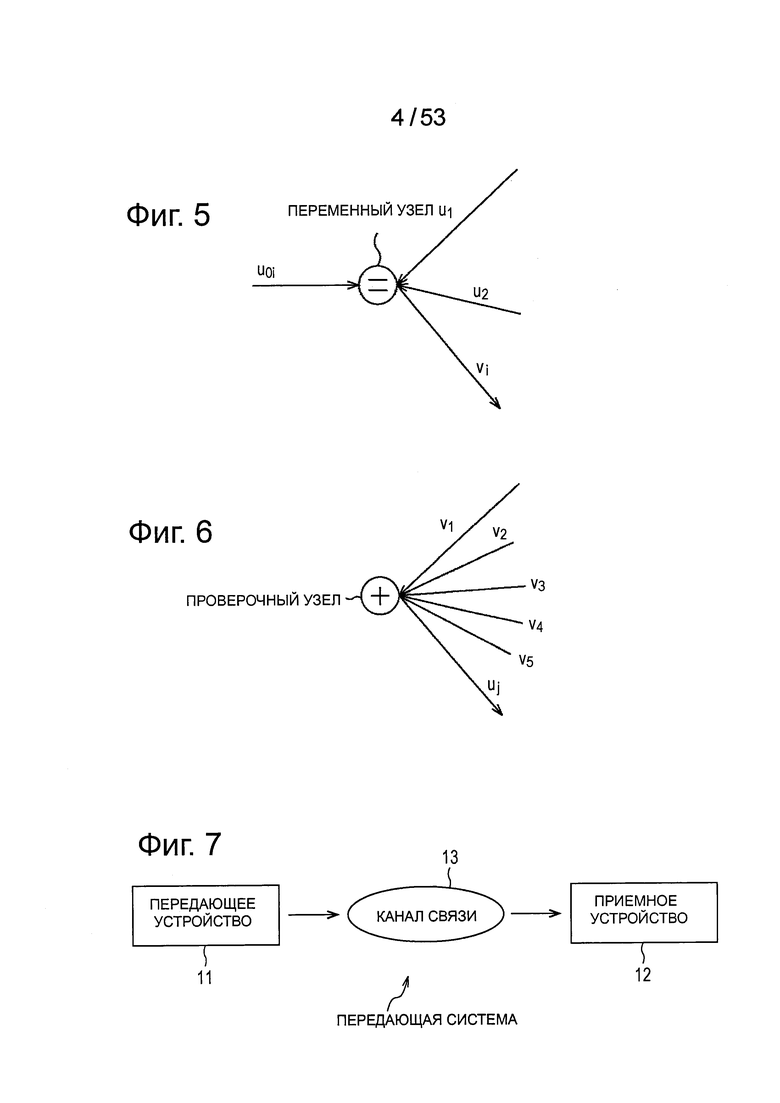

Фиг. 5 - схема, иллюстрирующая переменный узел.

Фиг. 6 - схема, иллюстрирующая контрольный узел.

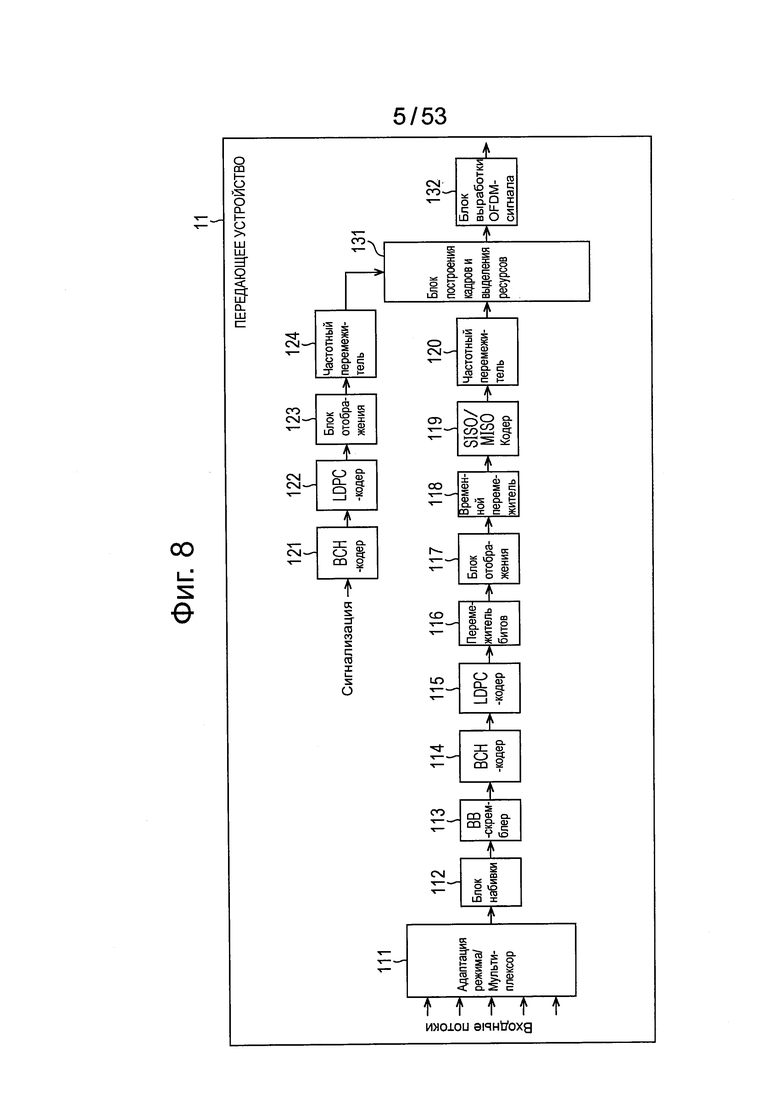

Фиг. 7 - схема, иллюстрирующая пример конфигурации варианта осуществления передающей системы, в которой применяется данная технология.

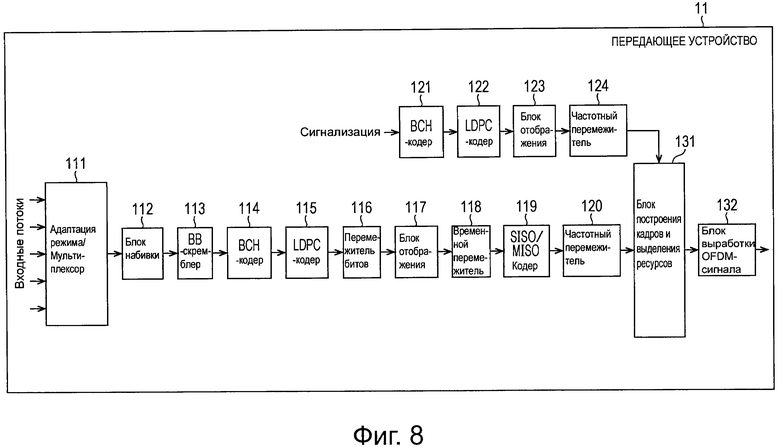

Фиг. 8 - схема, иллюстрирующая пример конфигурации передающего устройства 11.

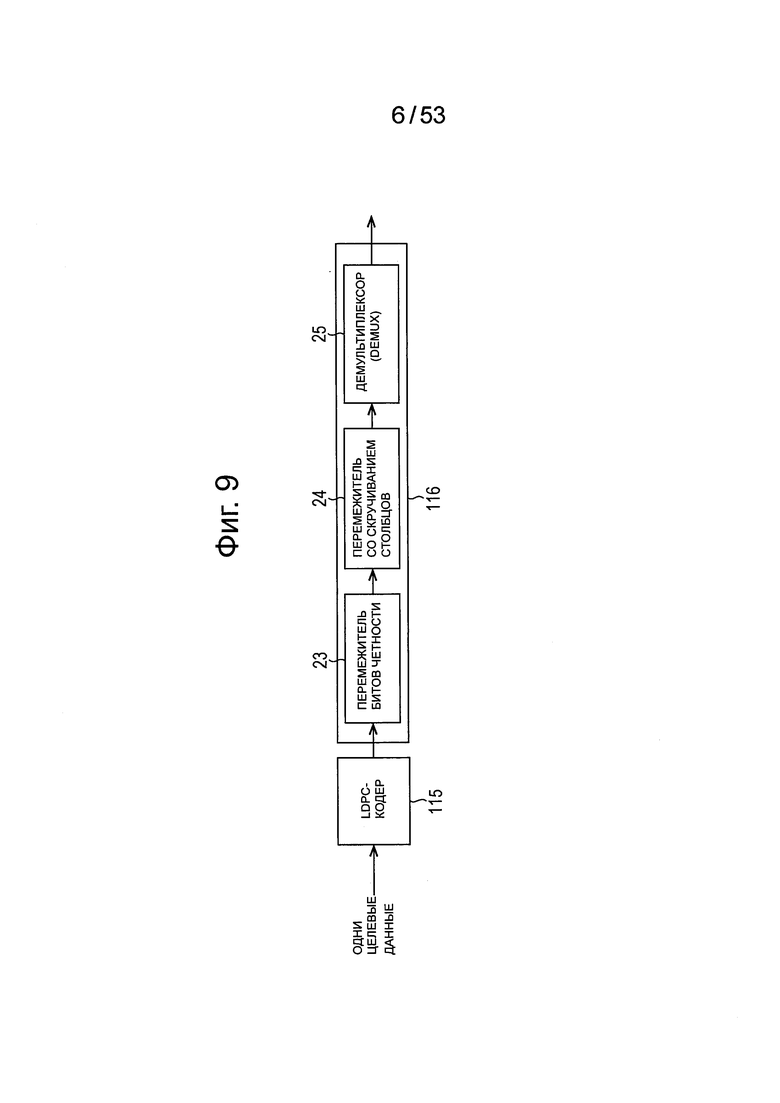

Фиг. 9 - блок-схема, иллюстрирующая пример конфигурации перемежителя 116 битов.

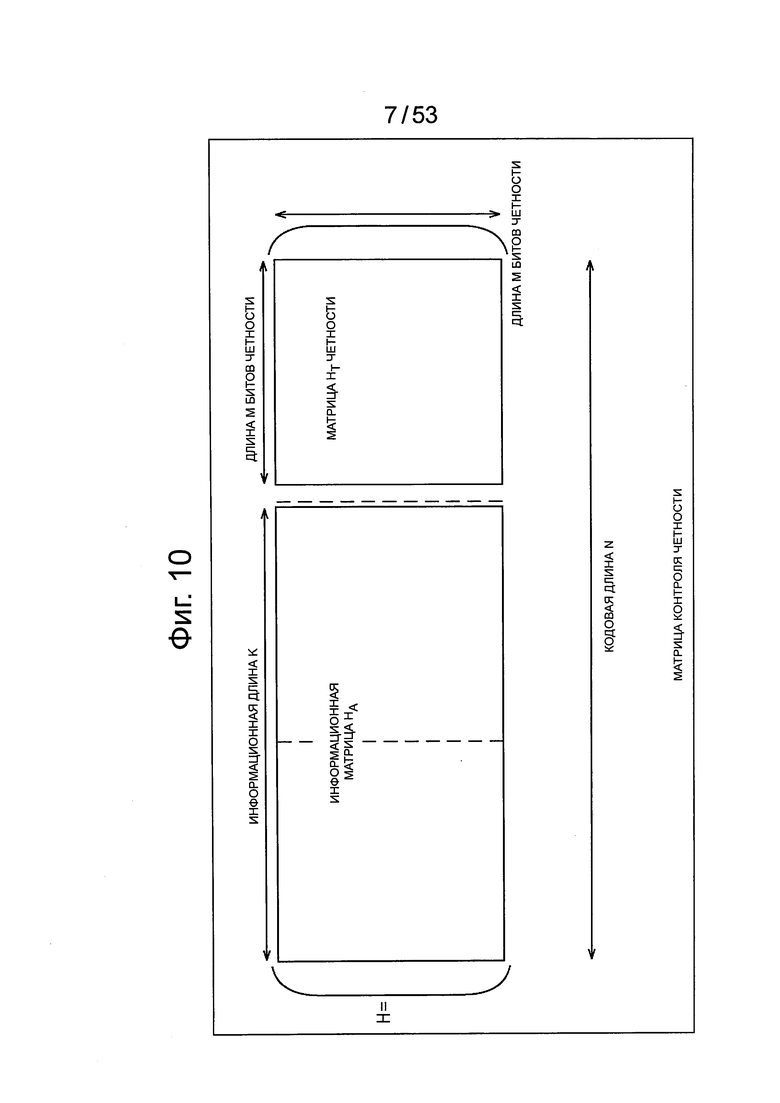

Фиг. 10 - схема, иллюстрирующая матрица контроля четности.

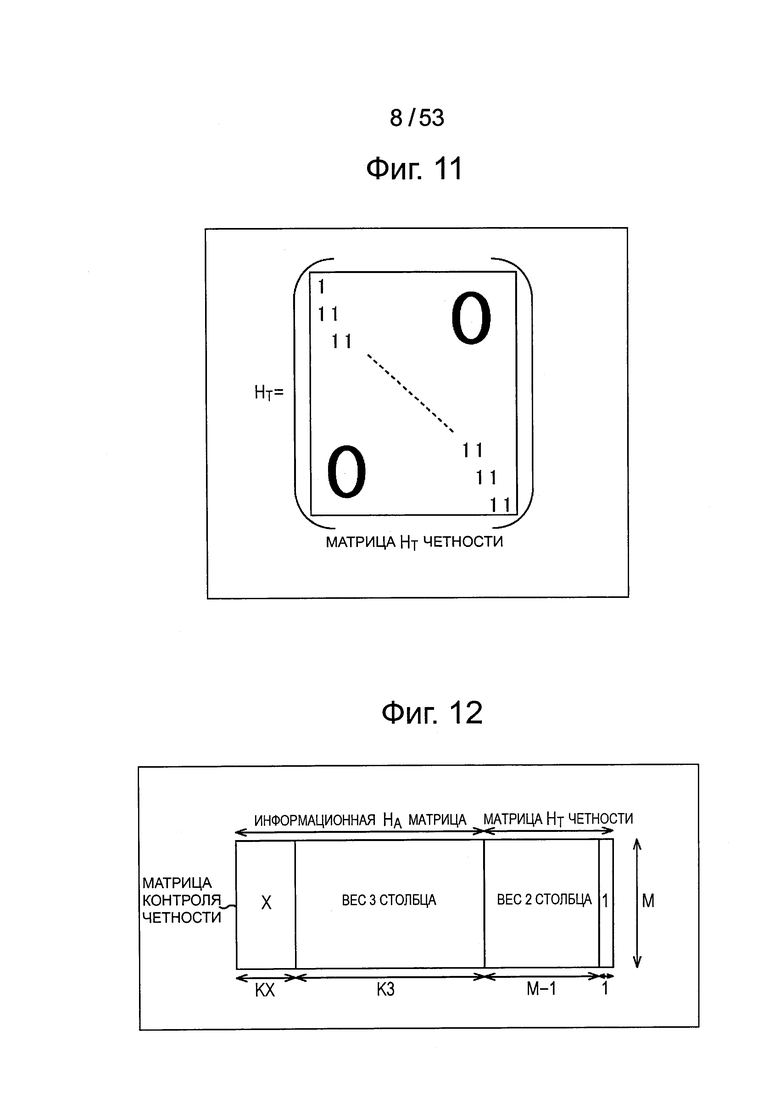

Фиг. 11 - схема, иллюстрирующая матрицу четности.

Фиг. 12 - схема, иллюстрирующая матрицу контроля четности LDPC-кода, который определен в стандарте DVB-S.2.

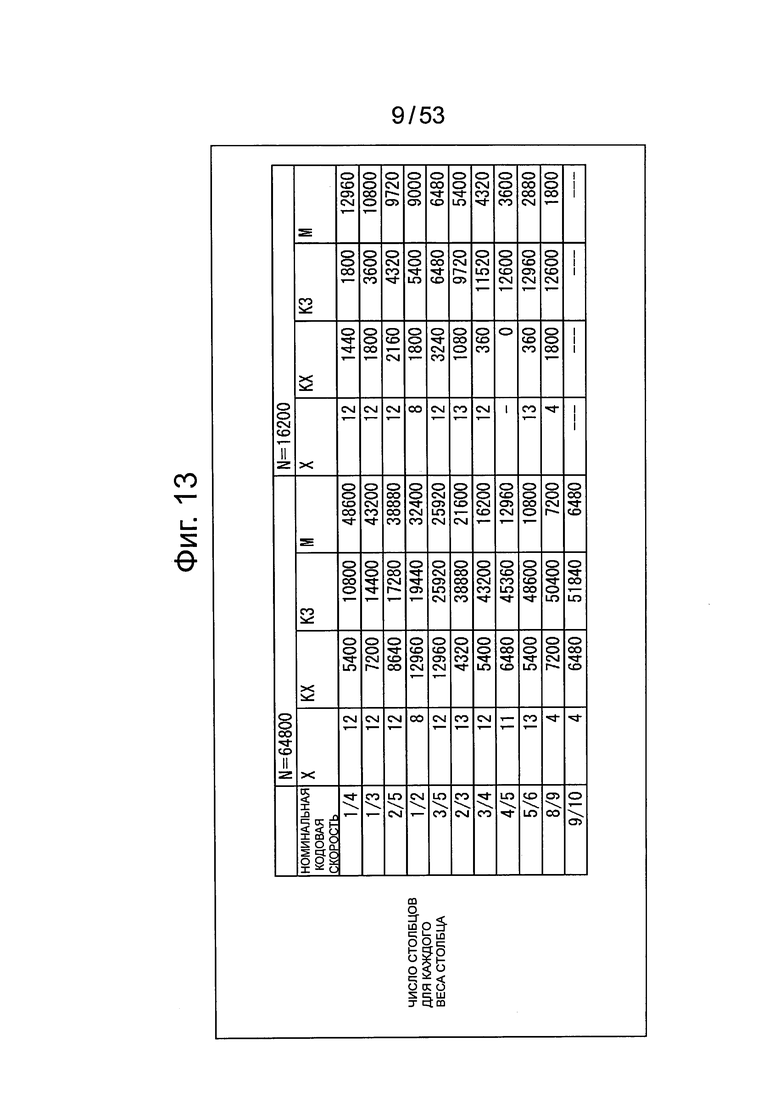

Фиг. 13 - схема, изображающая матрицу контроля четности LDPC-кода, который определен в стандарте DVB-S.2.

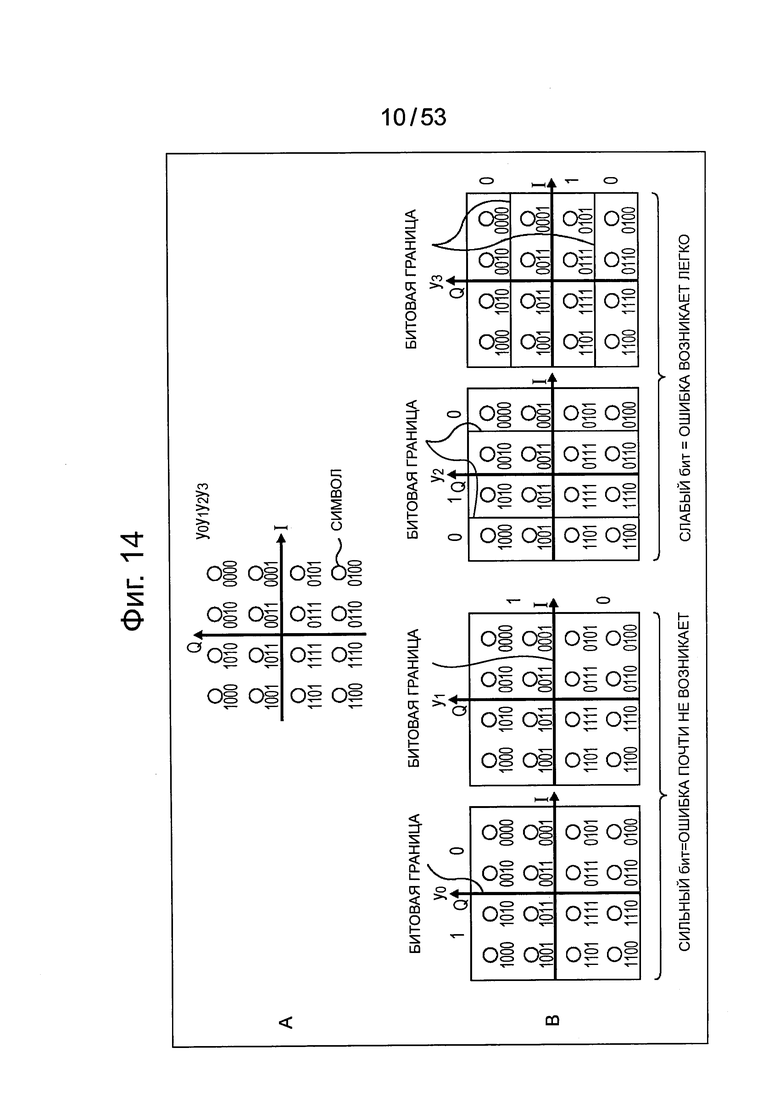

Фиг. 14 - схема, иллюстрирующая размещение сигнальных точек 16QAM.

Фиг. 15 - схема, иллюстрирующая размещение сигнальных точек 64QAM.

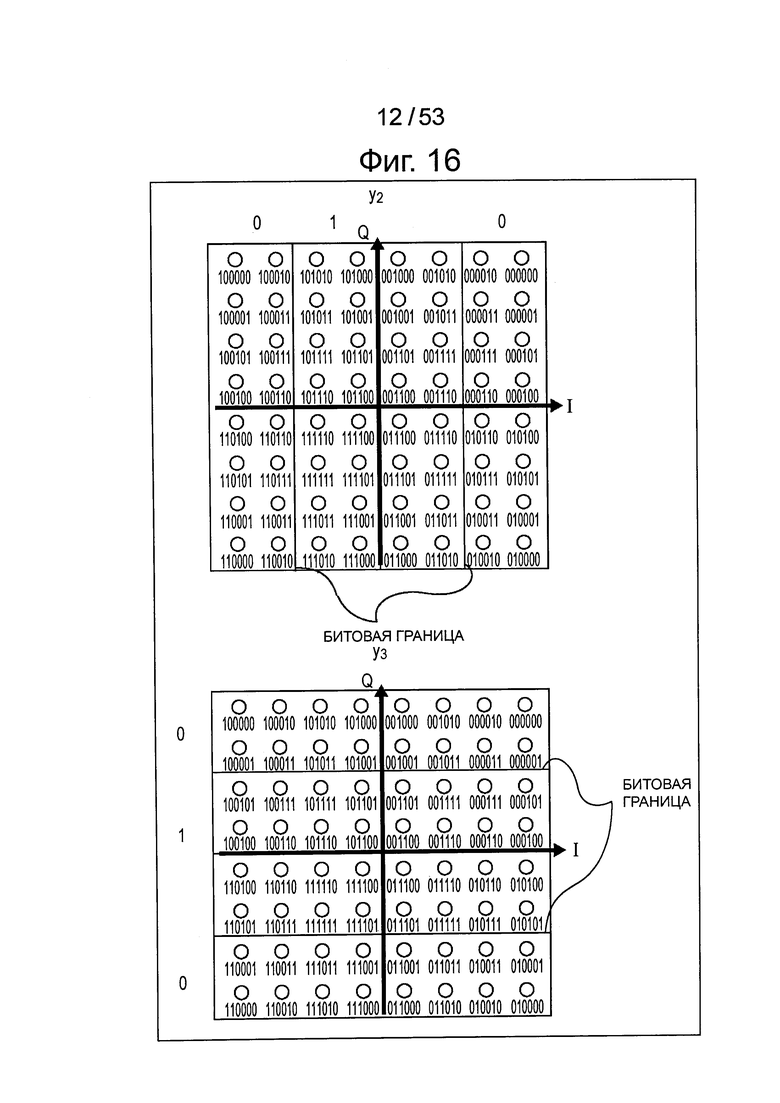

Фиг. 16 - схема, иллюстрирующая размещение сигнальных точек 64QAM.

Фиг. 17 - схема, иллюстрирующая размещение сигнальных точек 64QAM.

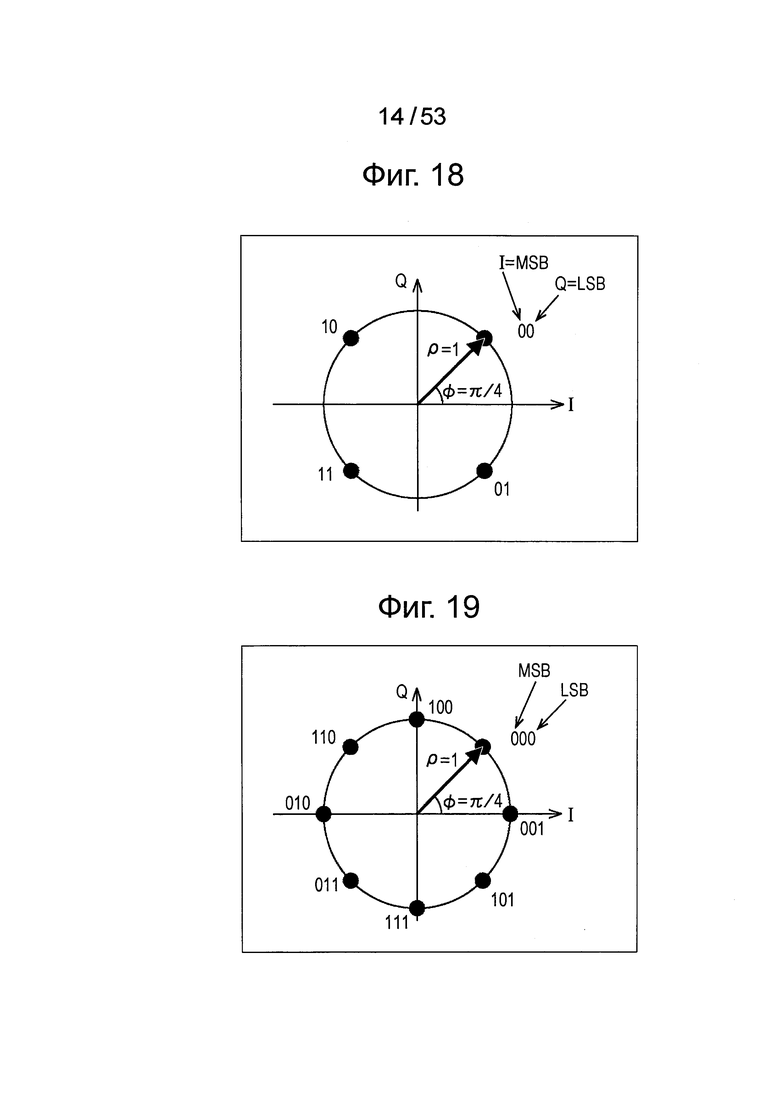

Фиг. 18 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

Фиг. 19 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

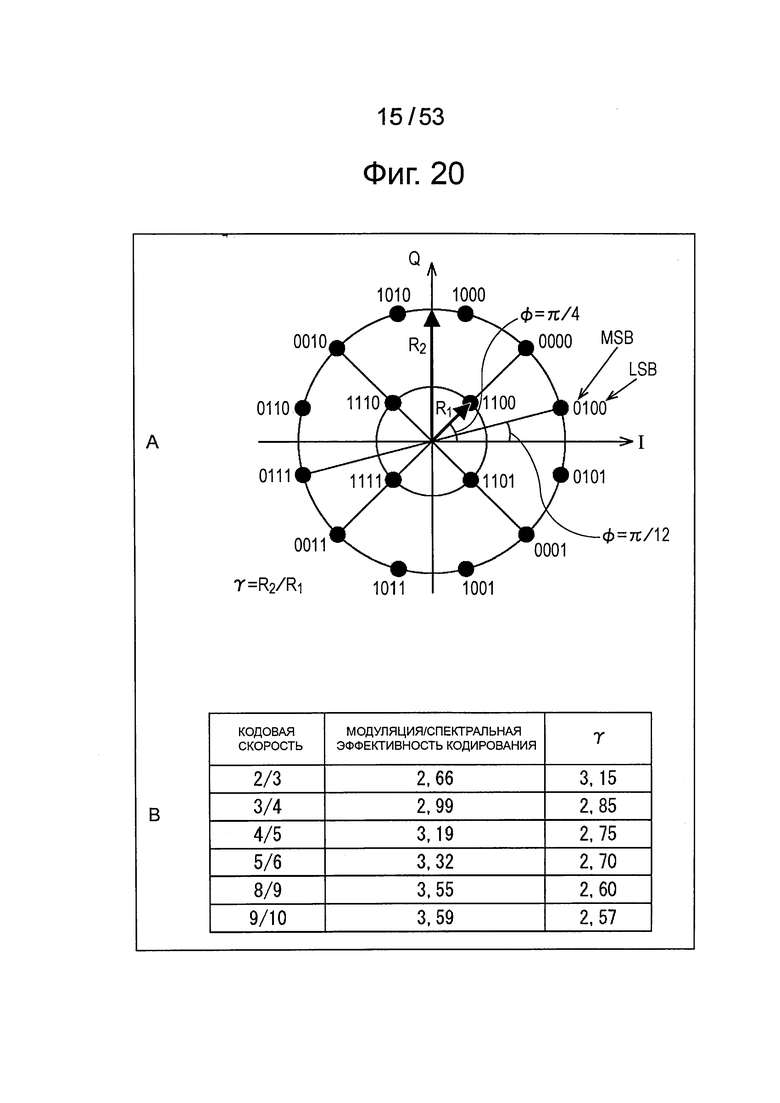

Фиг. 20 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

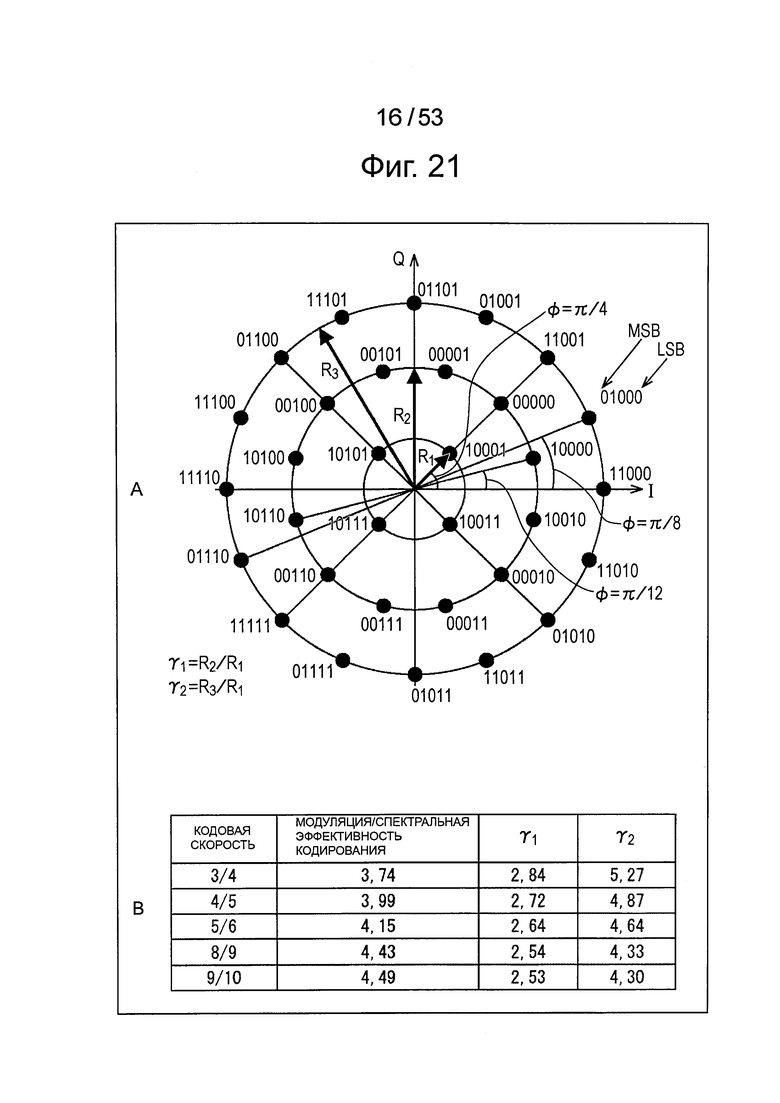

Фиг. 21 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

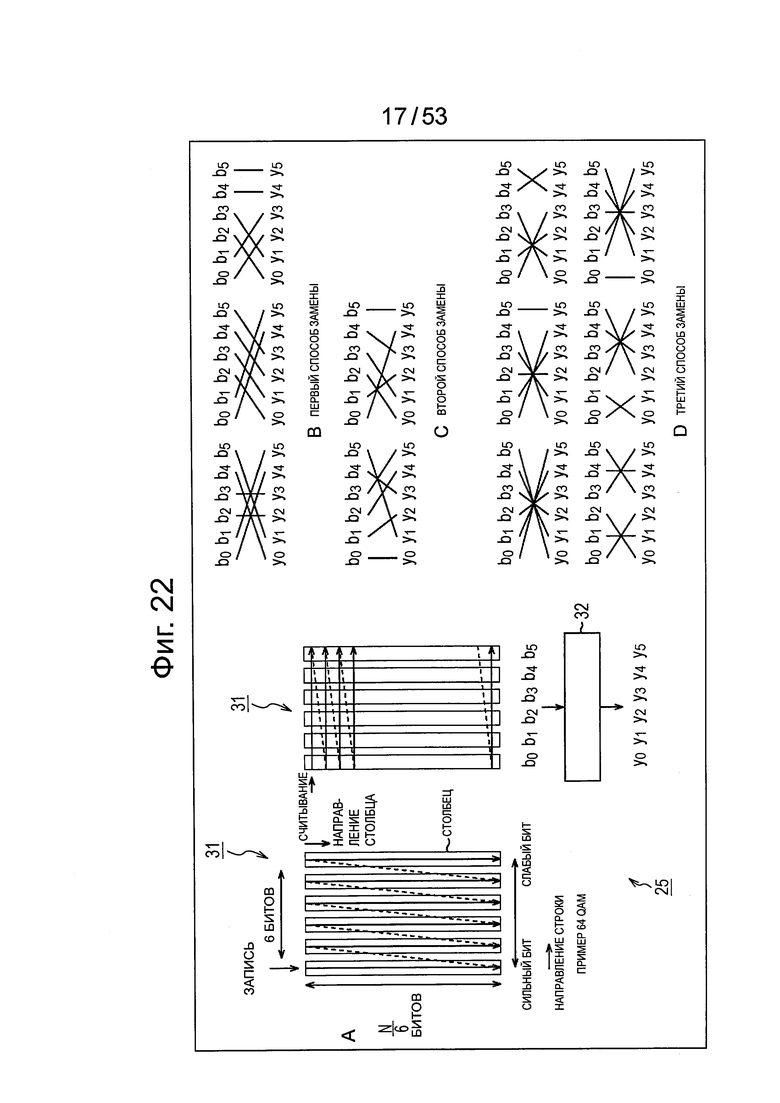

Фиг. 22 - схема, изображающая процесс, выполняемый демультиплексором 25.

Фиг. 23 - схема, изображающая процесс, выполняемый демультиплексором 25.

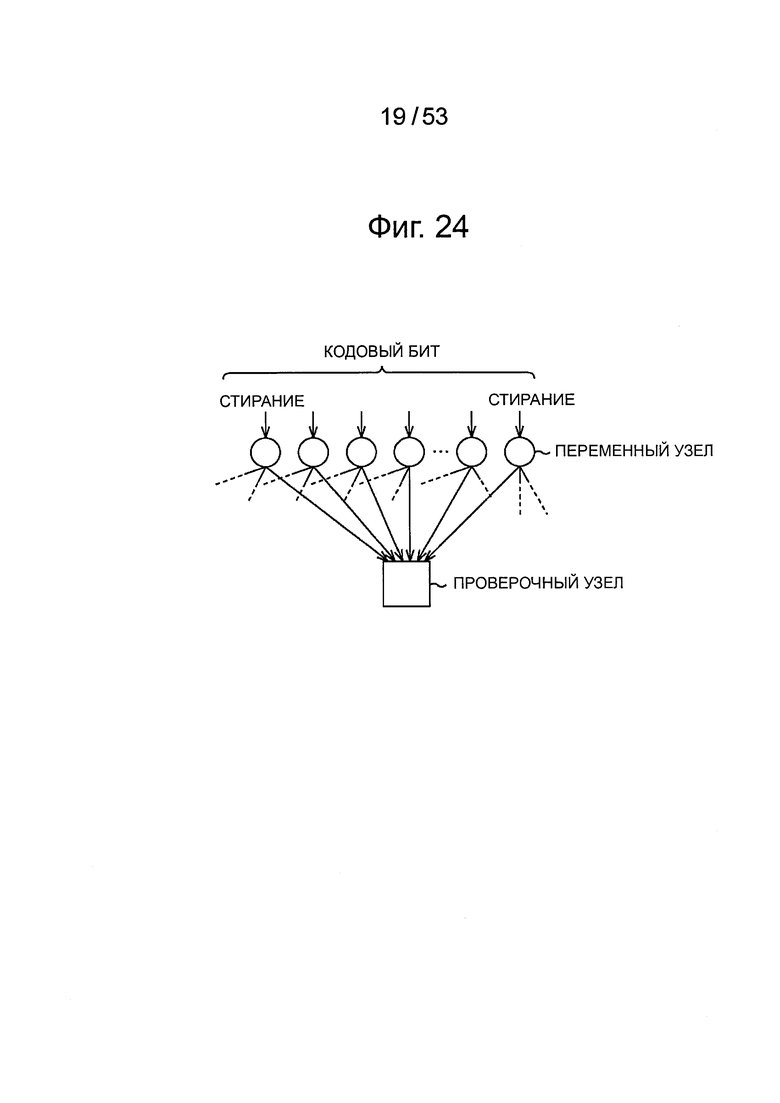

Фиг. 24 - схема, иллюстрирующая график Таннера для декодирования LDPC-кода.

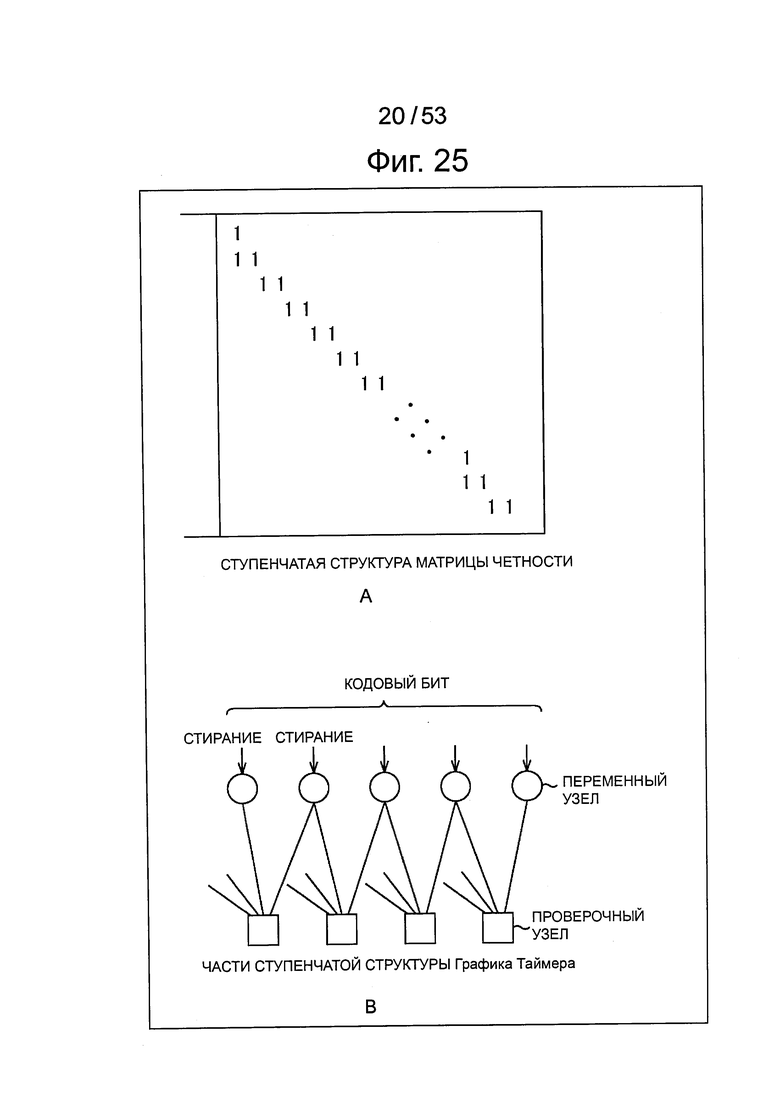

Фиг. 25 - схема, иллюстрирующая матрицу HT четности имеющий ступенчатую структуру и график Таннера, соответствующий матрице HT четности.

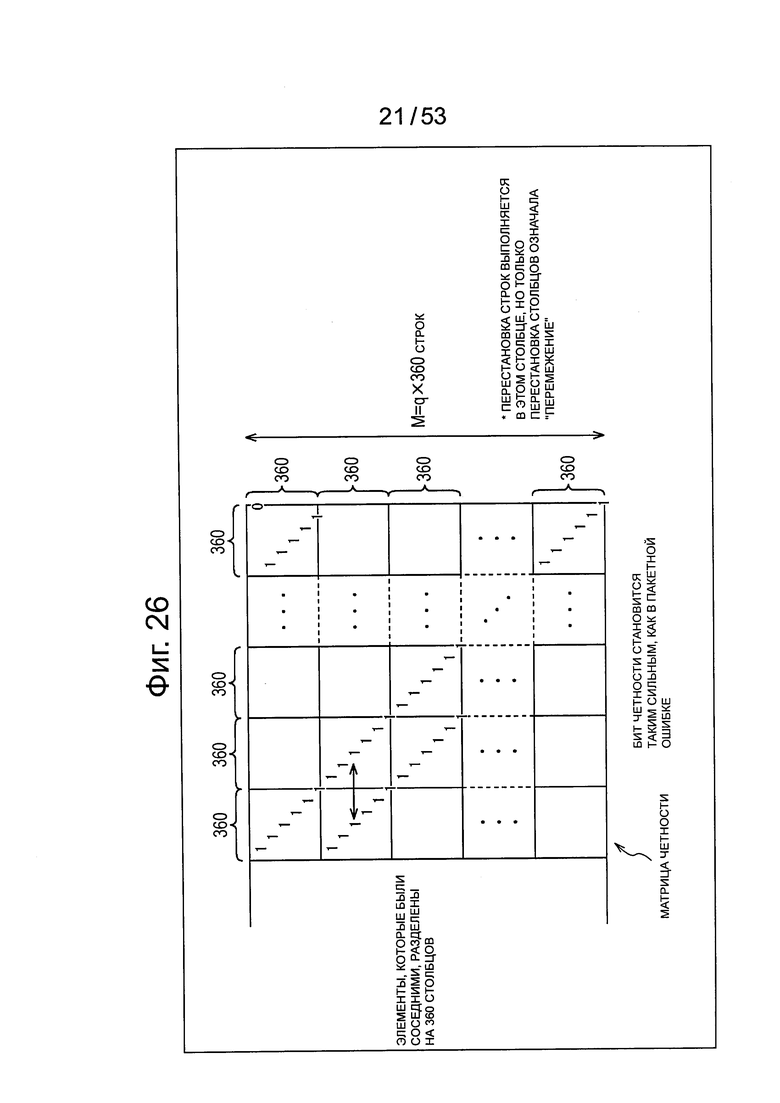

Фиг. 26 - схема, иллюстрирующая матрицу HT четности матрицы H контроля четности, соответствующей LDPC-коду после перемежения четности.

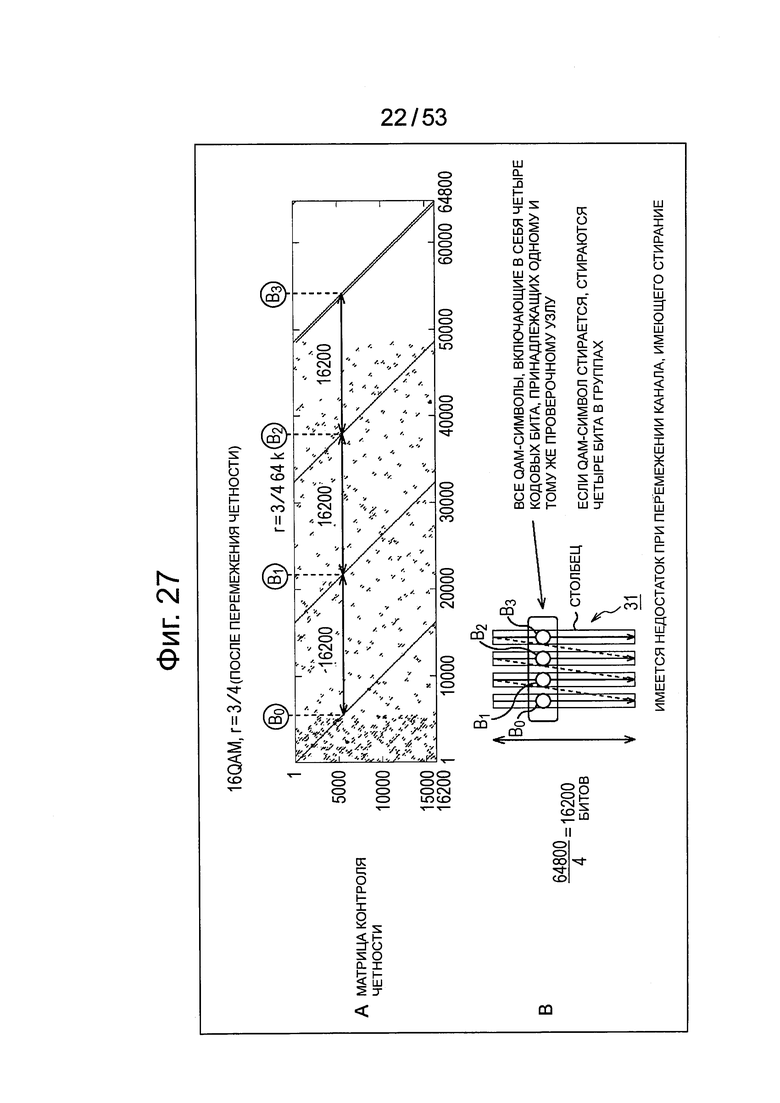

Фиг. 27 - схема, иллюстрирующая матрицу контроля четности преобразования.

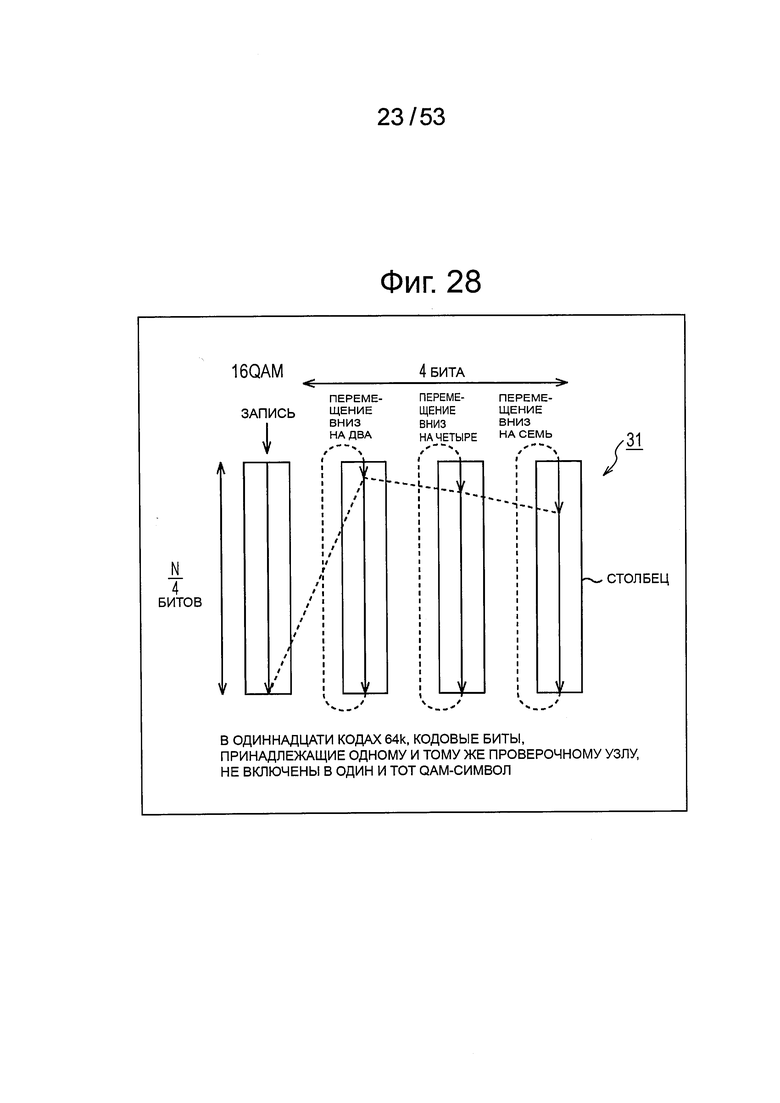

Фиг. 28 - схема, изображающая процесс, выполняемый перемежителем 24 со скручиванием столбцов.

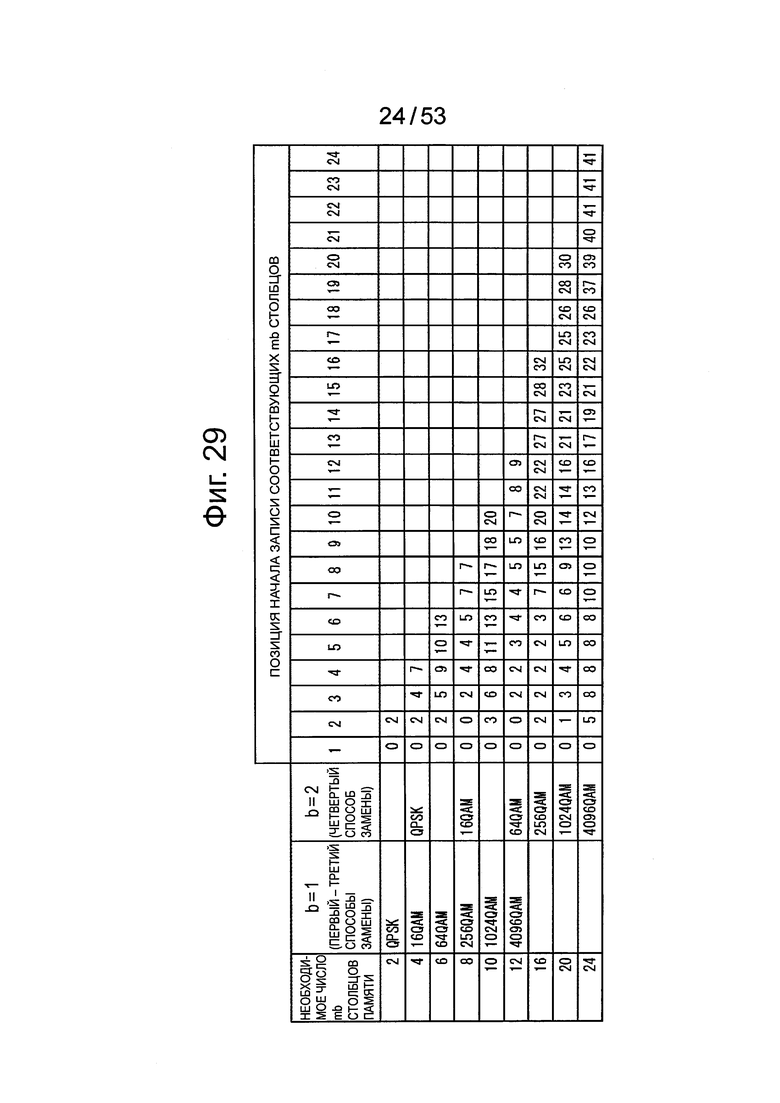

Фиг. 29 - схема, иллюстрирующая число столбцов и адрес позиции начала записи памяти 31, которая требуется для перемежения со скручиванием столбцов.

Фиг. 30 - схема, иллюстрирующая число столбцов и адрес позиции начала записи памяти 31, которая требуется для перемежения со скручиванием столбцов.

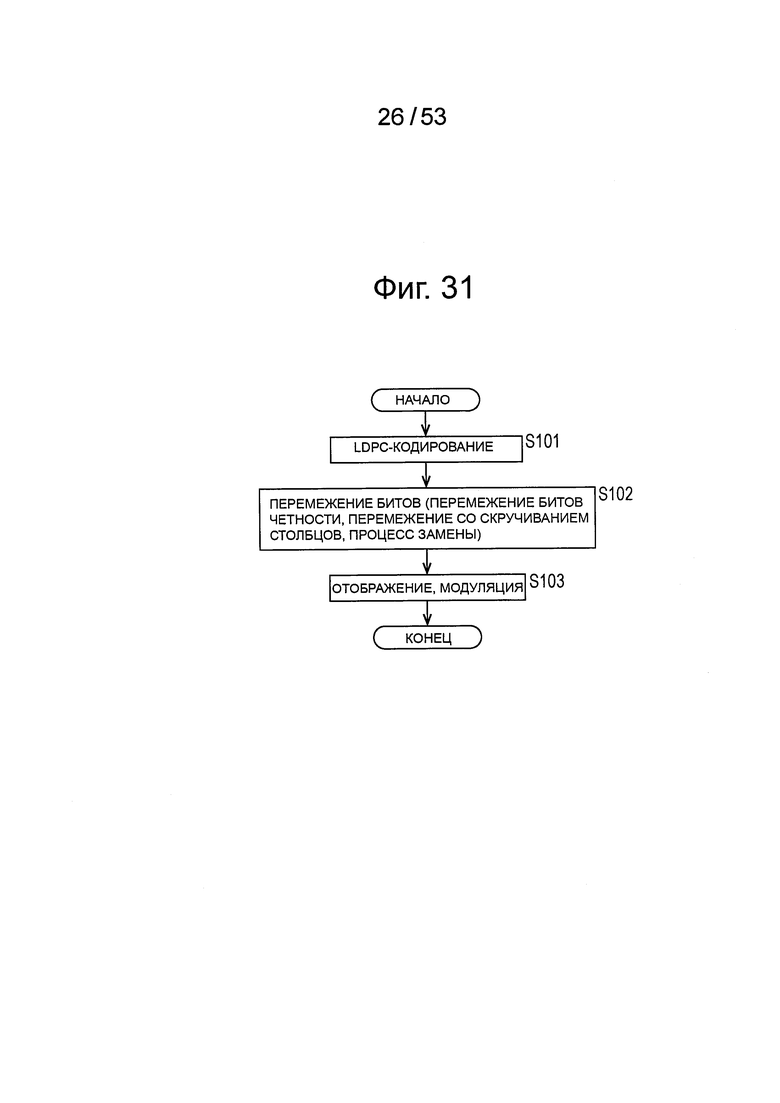

Фиг. 31 - блок-схема последовательности операций, иллюстрирующая процесс, выполняемый в перемежителе 116 битов и устройстве 117 отображения.

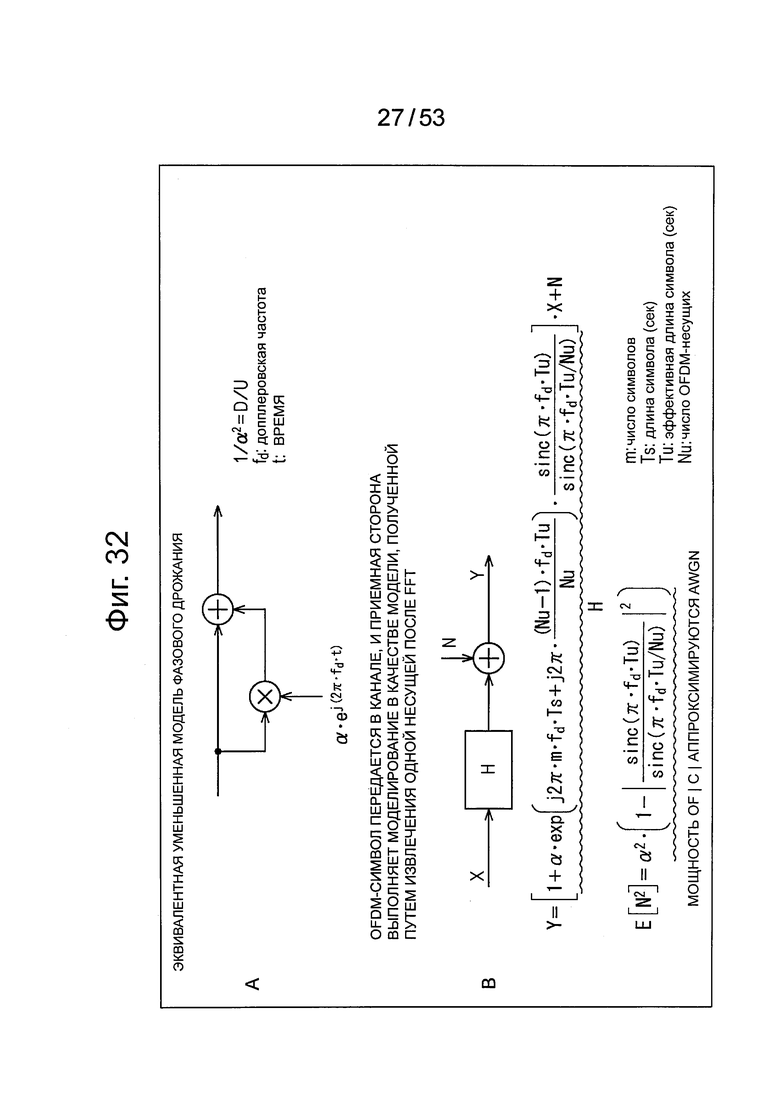

Фиг. 32 - схема, иллюстрирующая модель канала связи, используемую при моделировании.

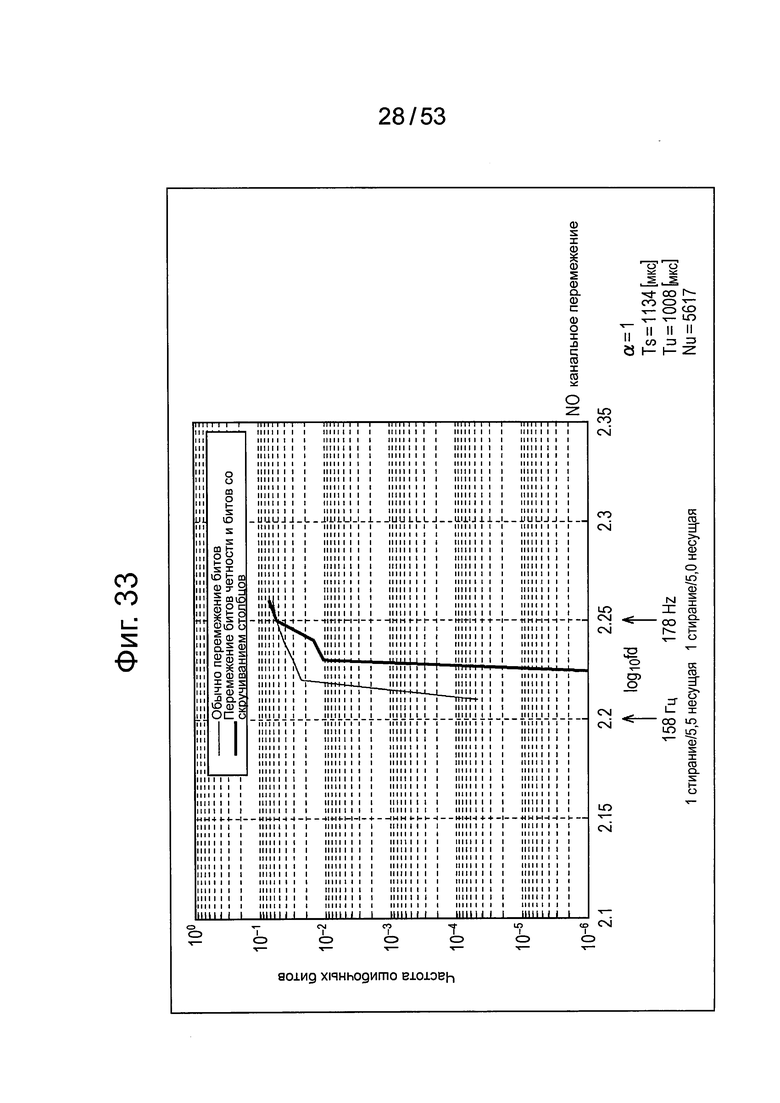

Фиг. 33 - схема, иллюстрирующая зависимость между частотой появления ошибок, полученной путем моделирования, и доплеровской частотой fd фазового дрожания.

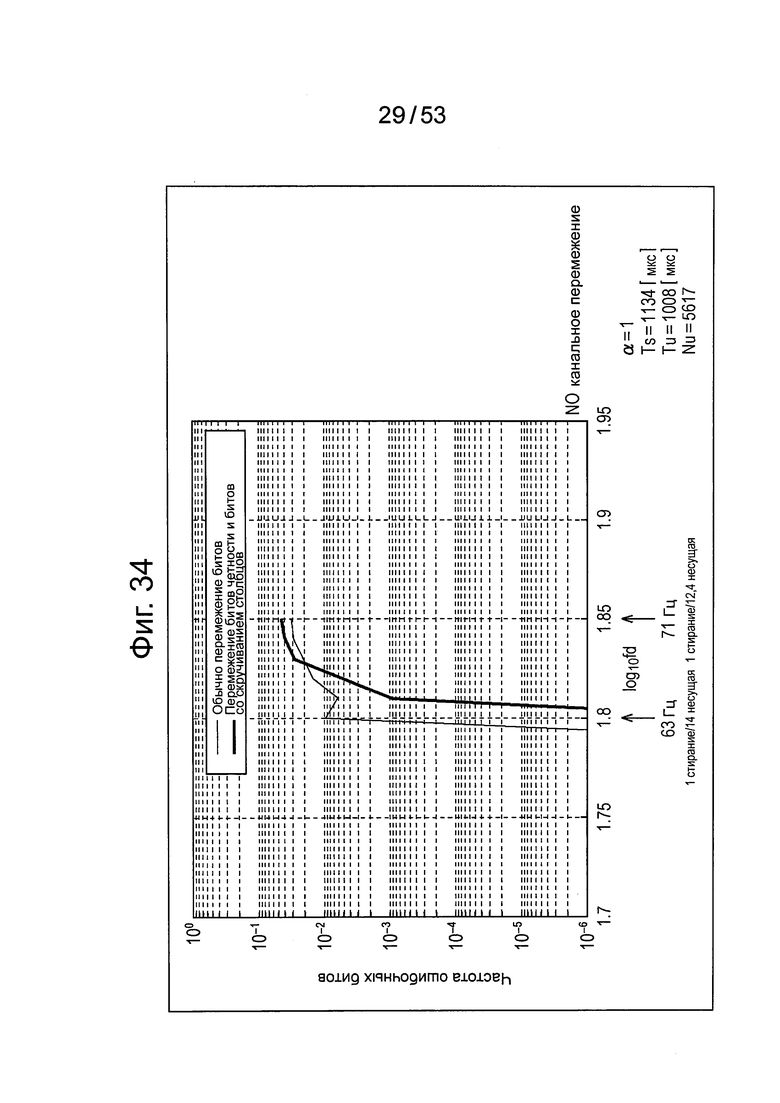

Фиг. 34 - схема, иллюстрирующая зависимость между частотой появления ошибок, полученной путем модуляции, и доплеровской частотой fd фазового дрожания.

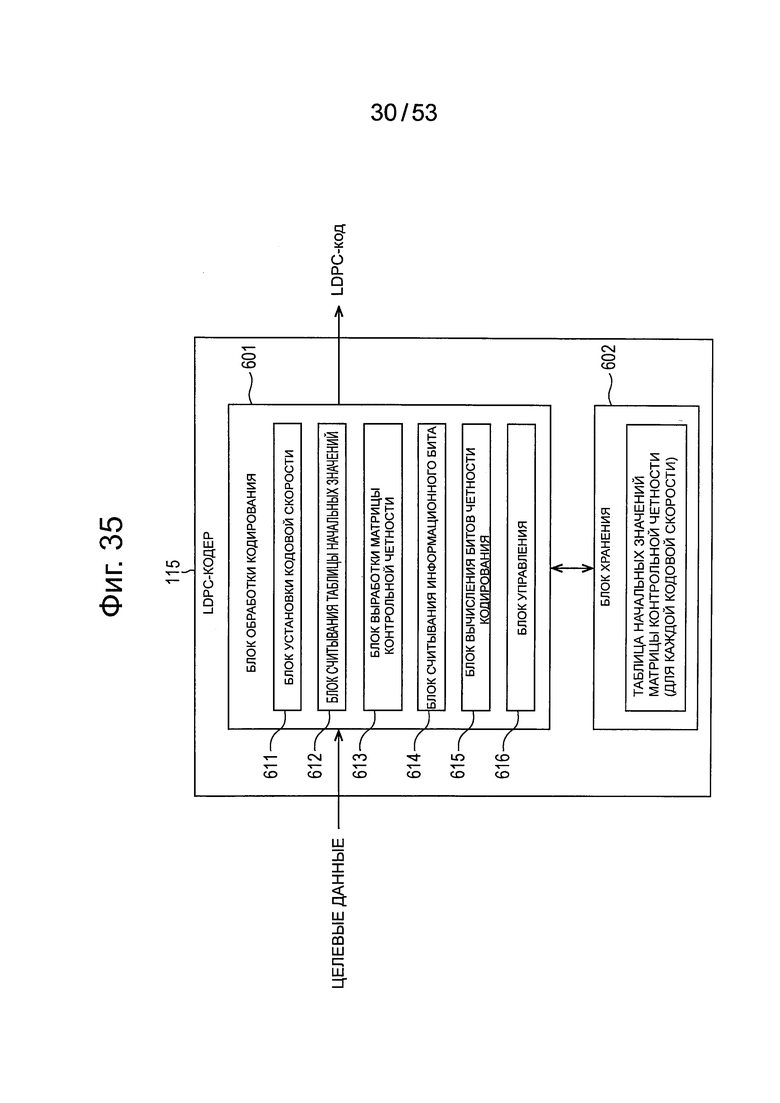

Фиг. 35 - блок-схема, иллюстрирующая пример конфигурации LDPC-кодера 115.

Фиг. 36 - блок-схема последовательности операций, иллюстрирующая процесс LDPC-кодера 115.

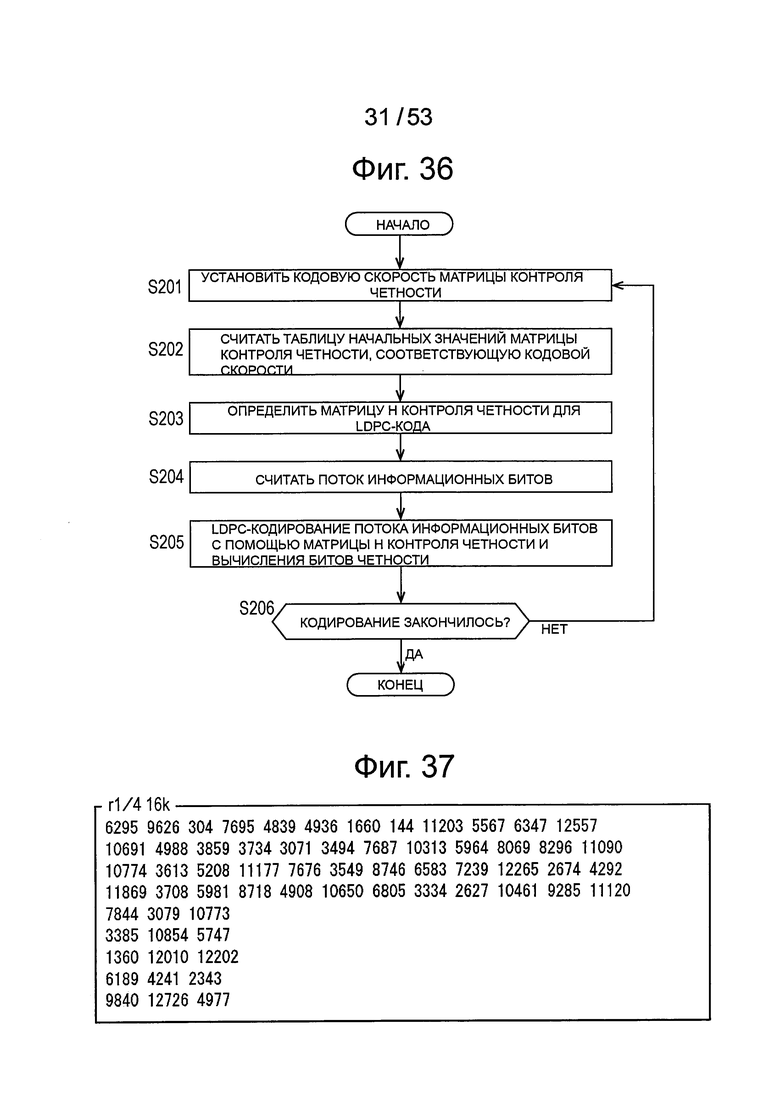

Фиг. 37 - схема, иллюстрирующая пример таблицы начальных значений матрицы контроля четности, в которой кодовая скорость равна 1/4, и длина кода равна 16200.

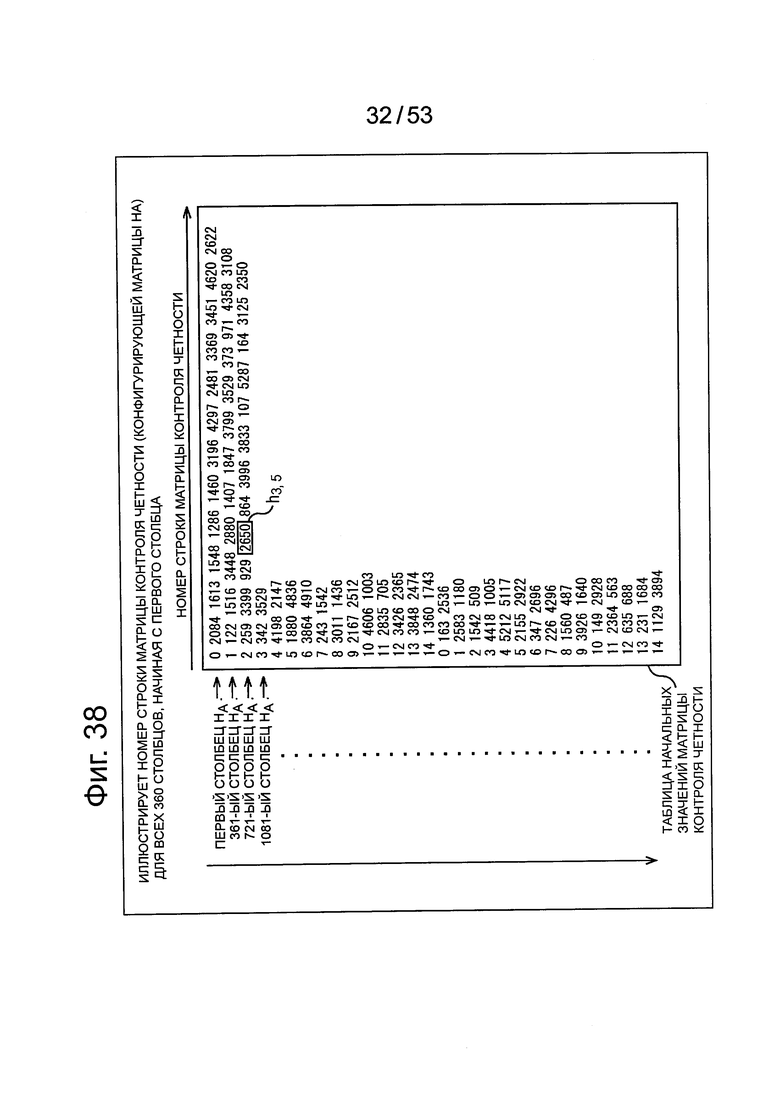

Фиг. 38 - схема, изображающая способ получения матрицы H контроля четности из таблицы начальных значений матрицы контроля четности.

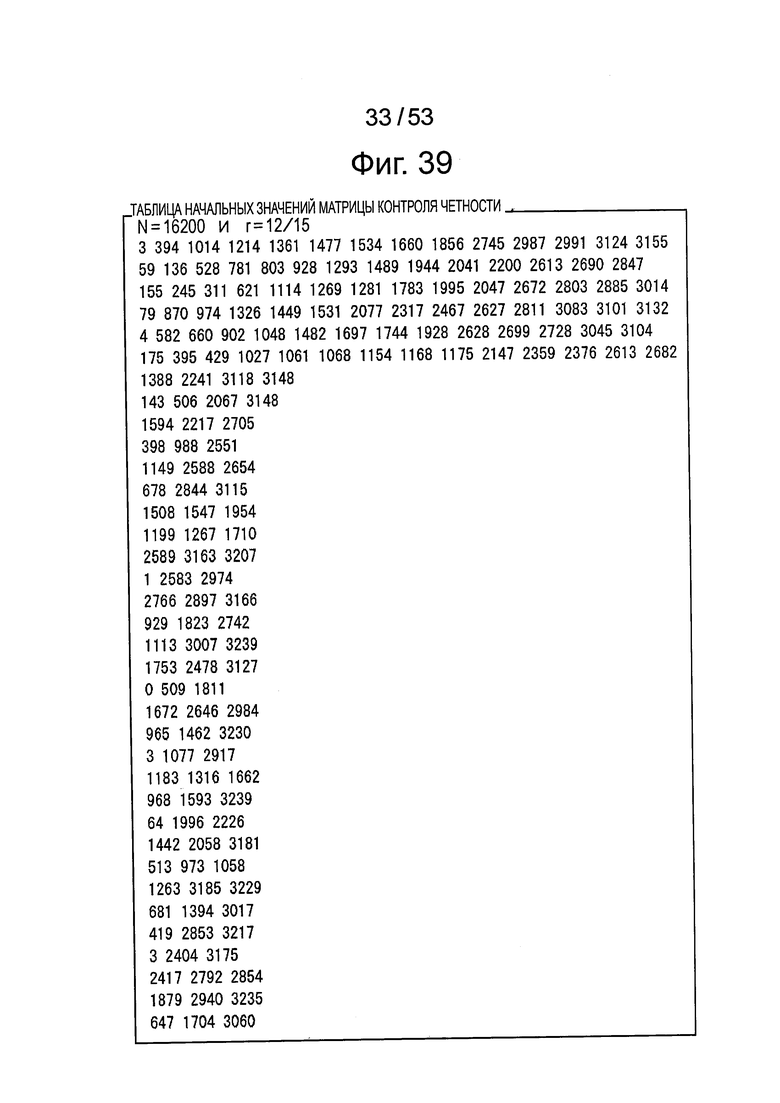

Фиг. 39 - схема, иллюстрирующая пример таблицы начальных значений матрицы контроля четности кода 16k с r=12/15.

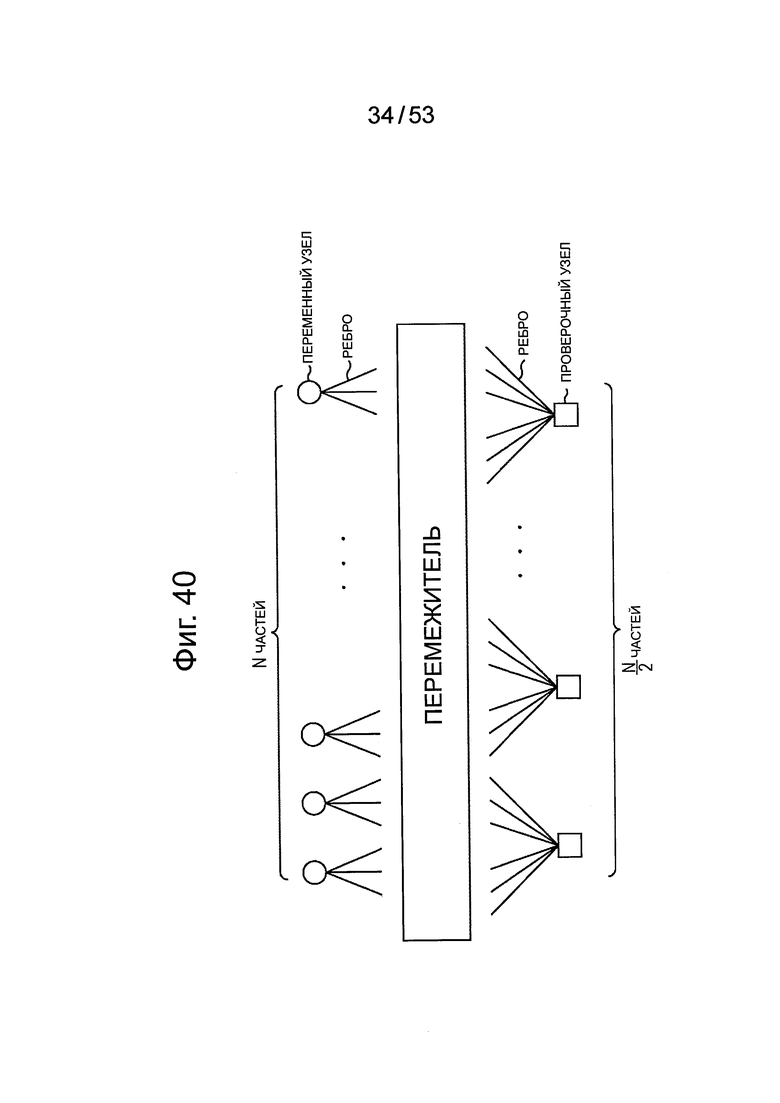

Фиг. 40 - схема, иллюстрирующая пример график Таннера ансамбля степенной последовательности, в которой вес столбца равен 3, и вес строки равен 6.

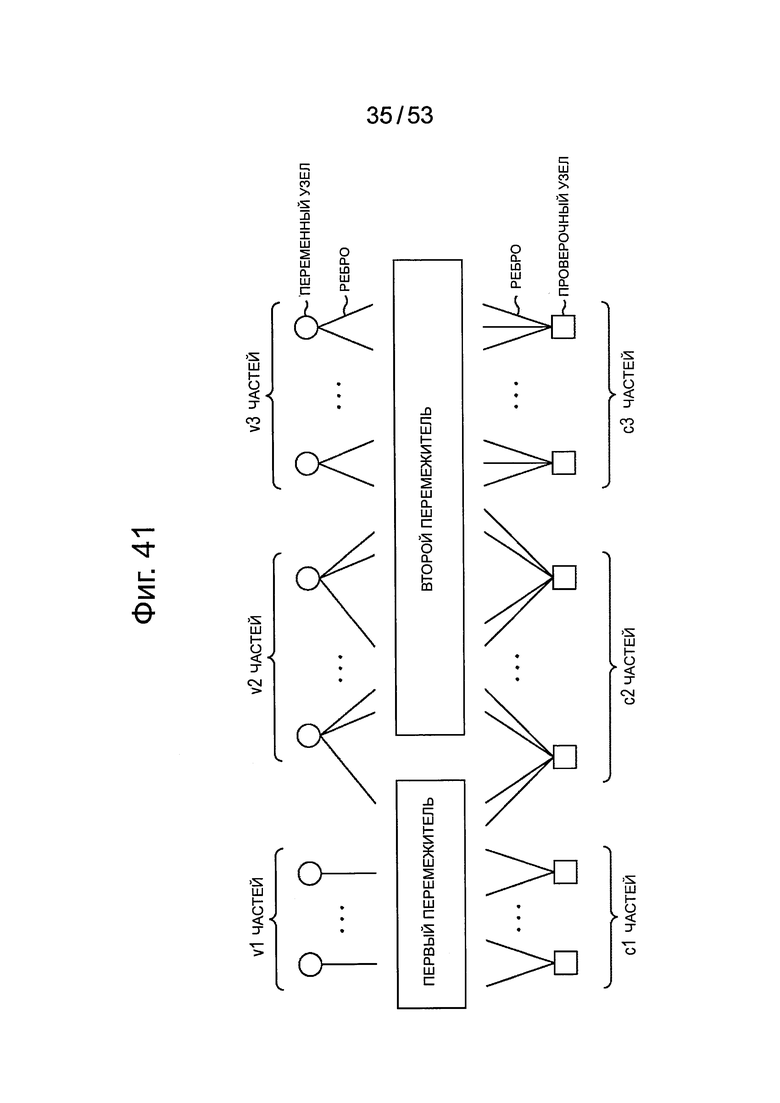

Фиг. 41 - схема, иллюстрирующая пример графика Таннера ансамбля многореберного типа.

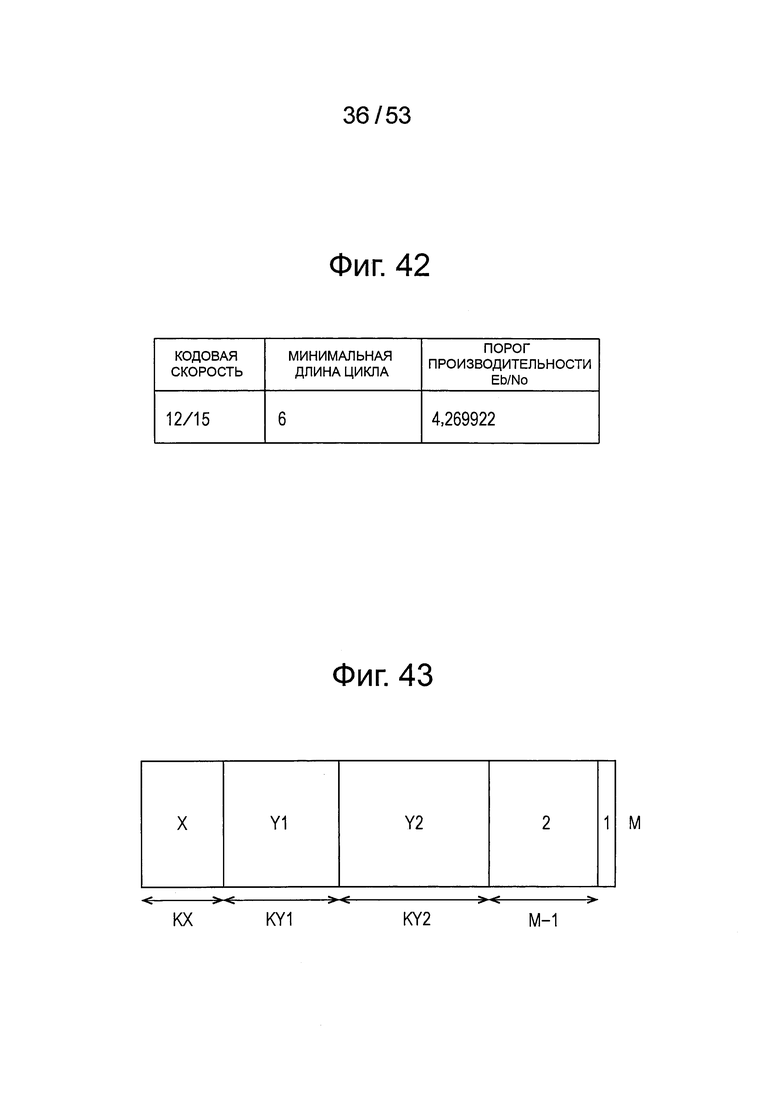

Фиг. 42 - схема, иллюстрирующая минимальную длину цикла и порог производительности матрицы контроля четности кода 16k с r=12/15.

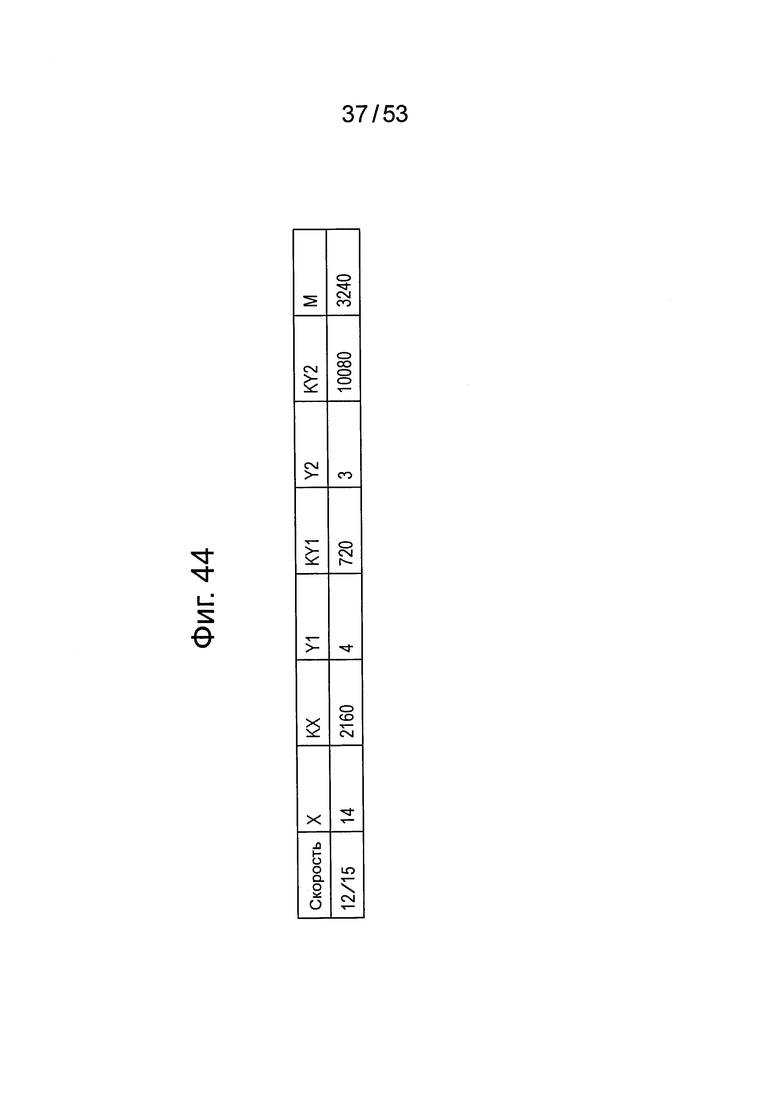

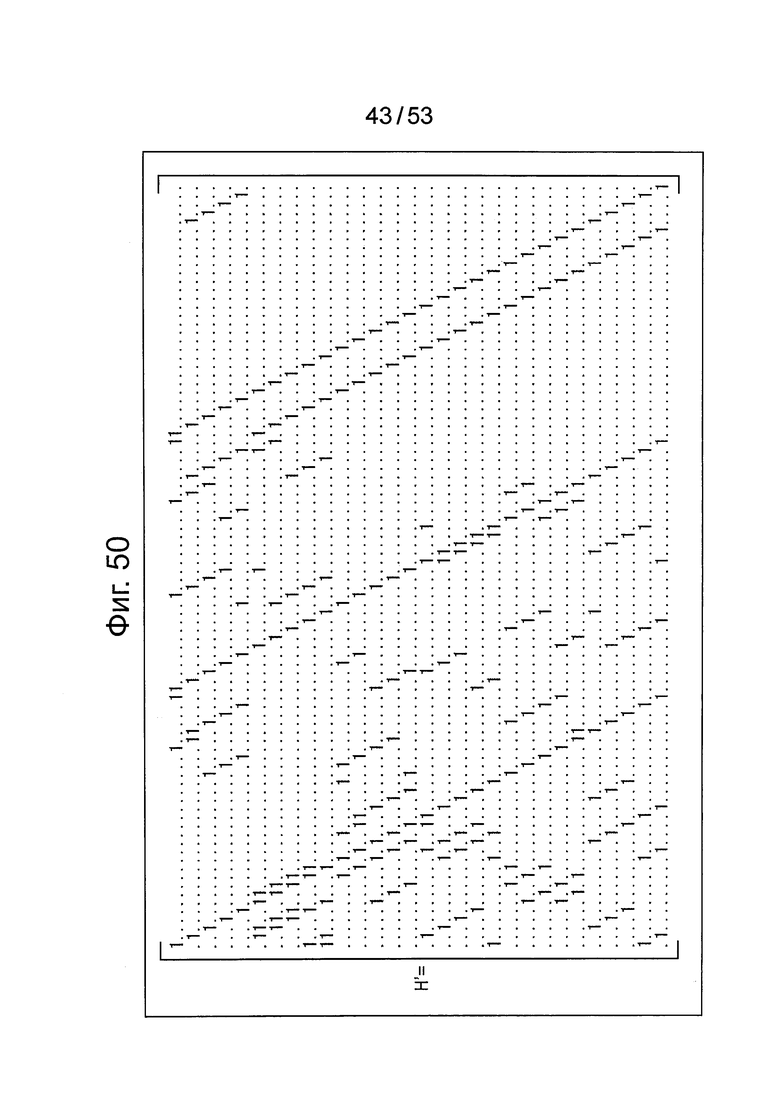

Фиг. 43 - схема, изображающая матрицу контроля четности кода 16k с r=12/15.

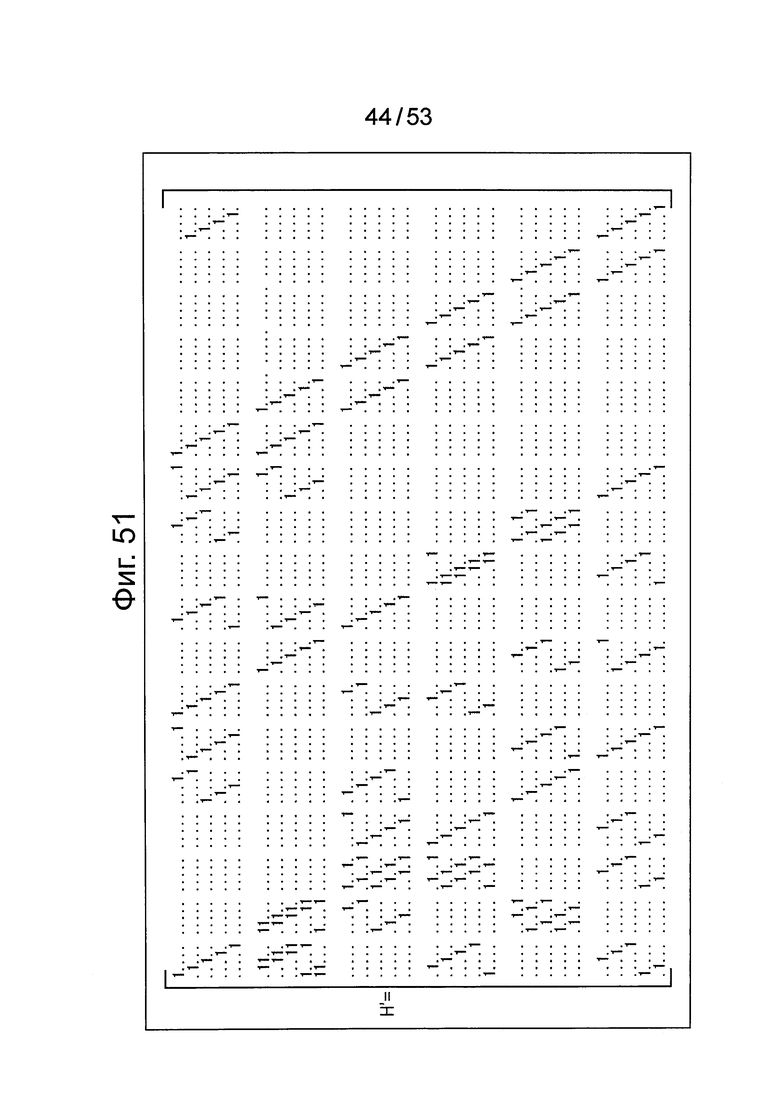

Фиг. 44 - схема, изображающая матрицу контроля четности кода 16k с r=12/15.

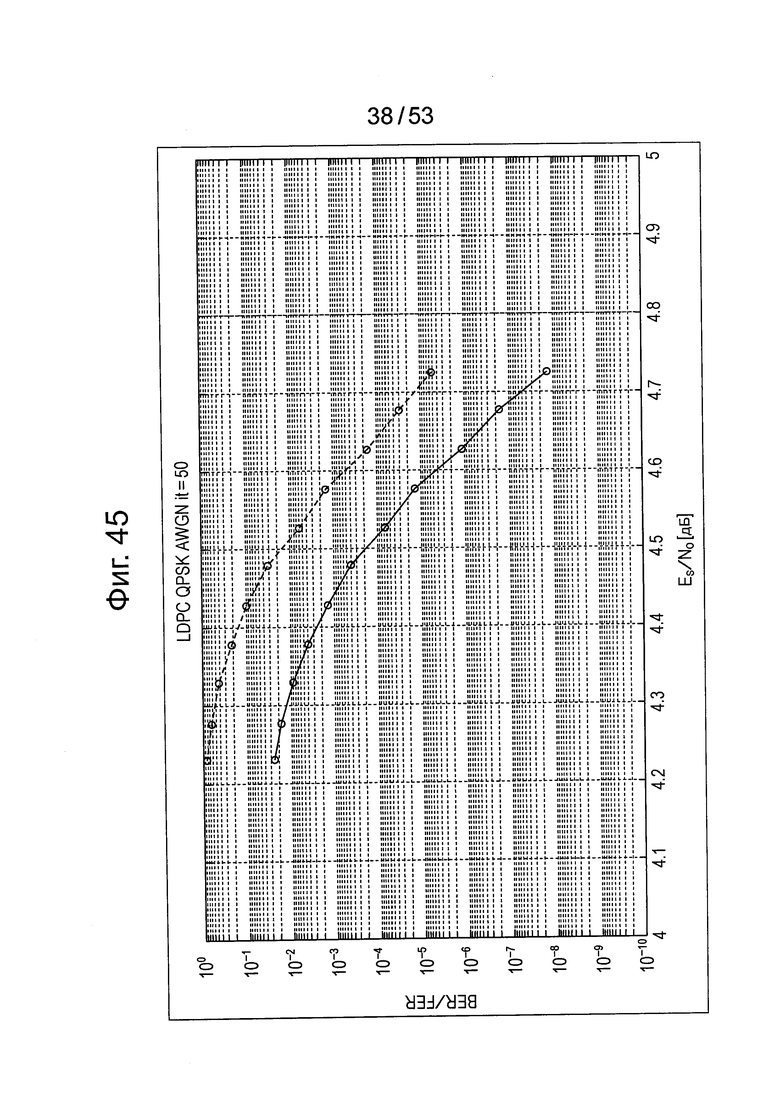

Фиг. 45 - схема, иллюстрирующая результат моделирования измерения BER/FER.

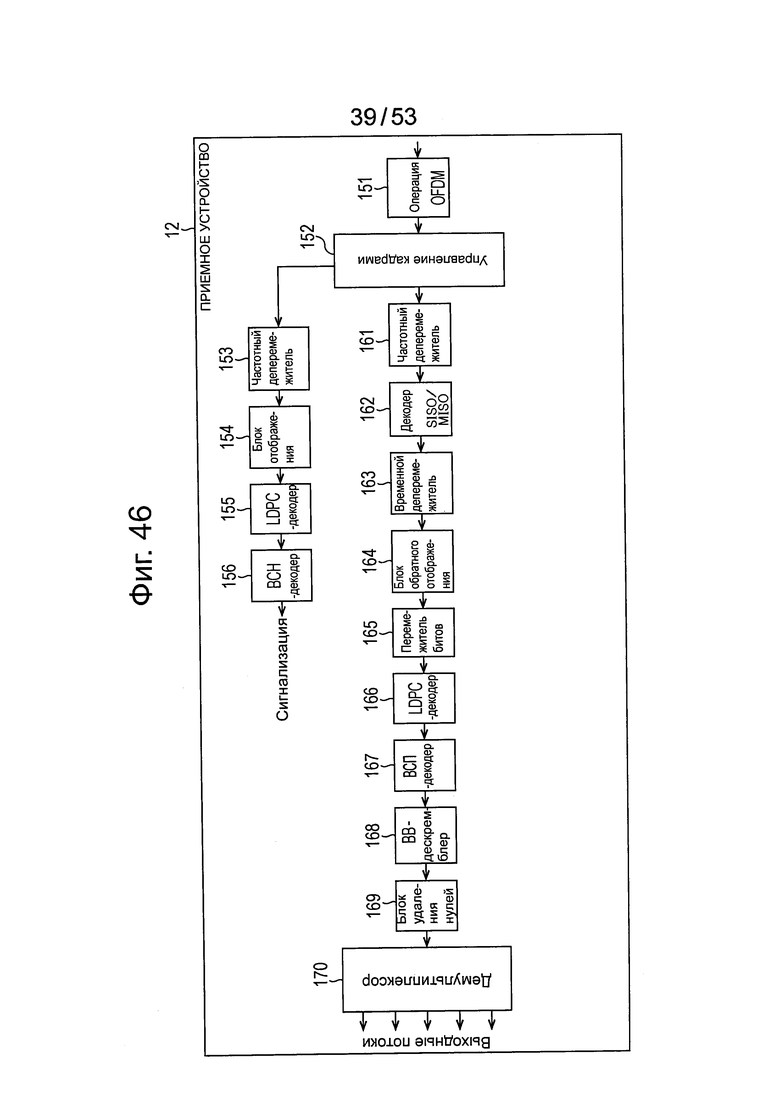

Фиг. 46 - блок-схема, иллюстрирующая пример конфигурации приемного устройства 12.

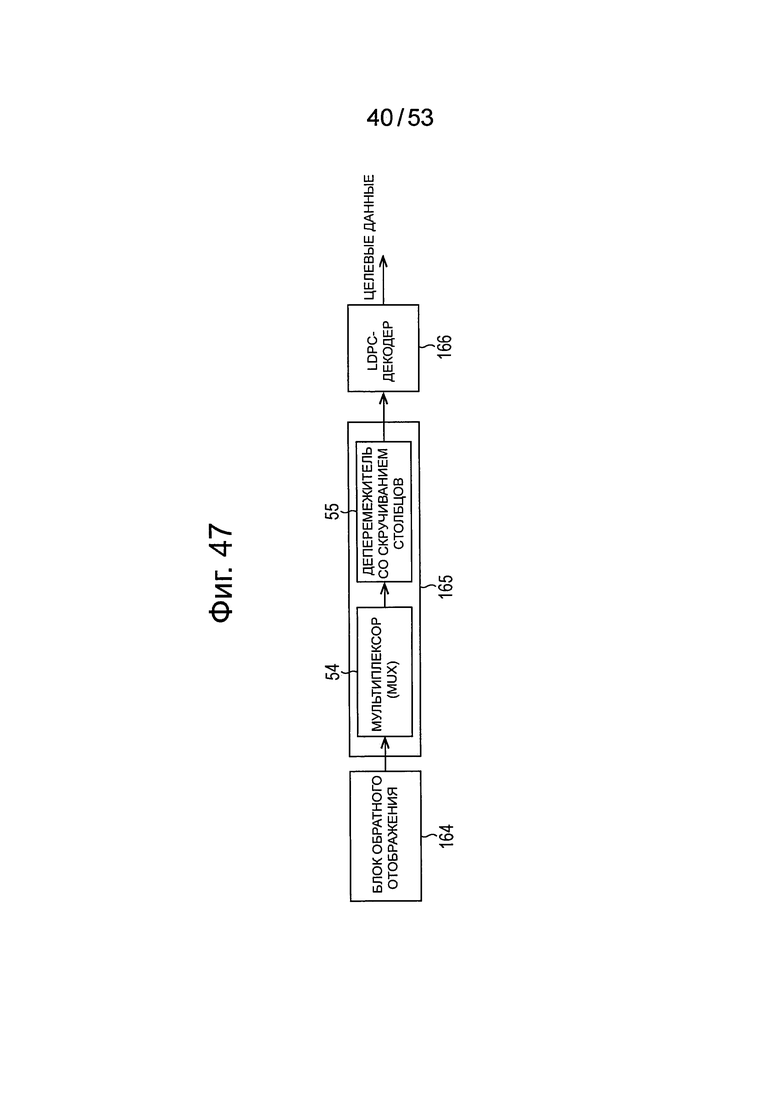

Фиг. 47 - блок-схема, иллюстрирующая пример конфигурации деперемежителя 165 битов.

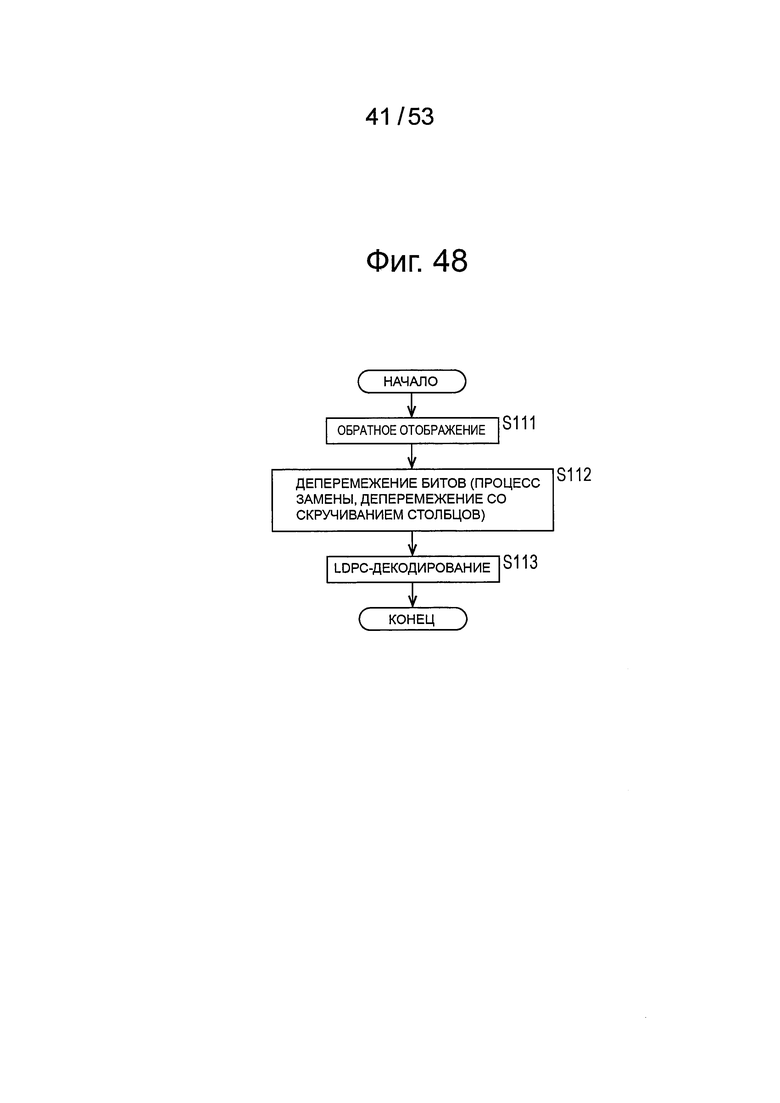

Фиг. 48 - блок-схема последовательности операций, иллюстрирующая процесс, выполняемый устройством 164 обратного отображения, деперемежителем 165 битов и LDPC-декодером 166.

Фиг. 49 - схема, иллюстрирующая пример матрицы контроля четности LDPC-кода.

Фиг. 50 - схема, иллюстрирующая матрица (матрицу контроля четности преобразования), полученную путем выполнения перестановки строк и перестановки столбцов в отношении матрицы контроля четности.

Фиг. 51 - схема, иллюстрирующая матрицу контроля четности преобразования, которая разделена на 5×5 блоков.

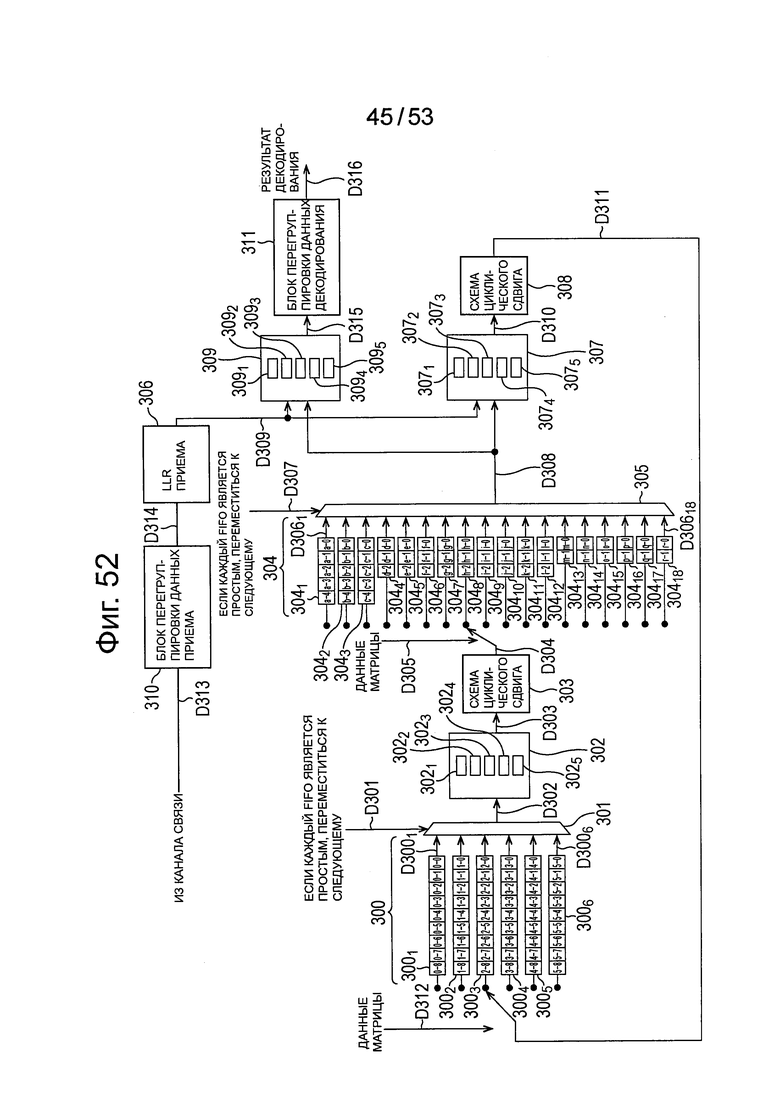

Фиг. 52 - блок-схема, иллюстрирующая пример конфигурации устройства декодирования, которое выполняет вычисление узла в группах P.

Фиг. 53 - блок-схема, иллюстрирующая пример конфигурации LDPC-декодера 166.

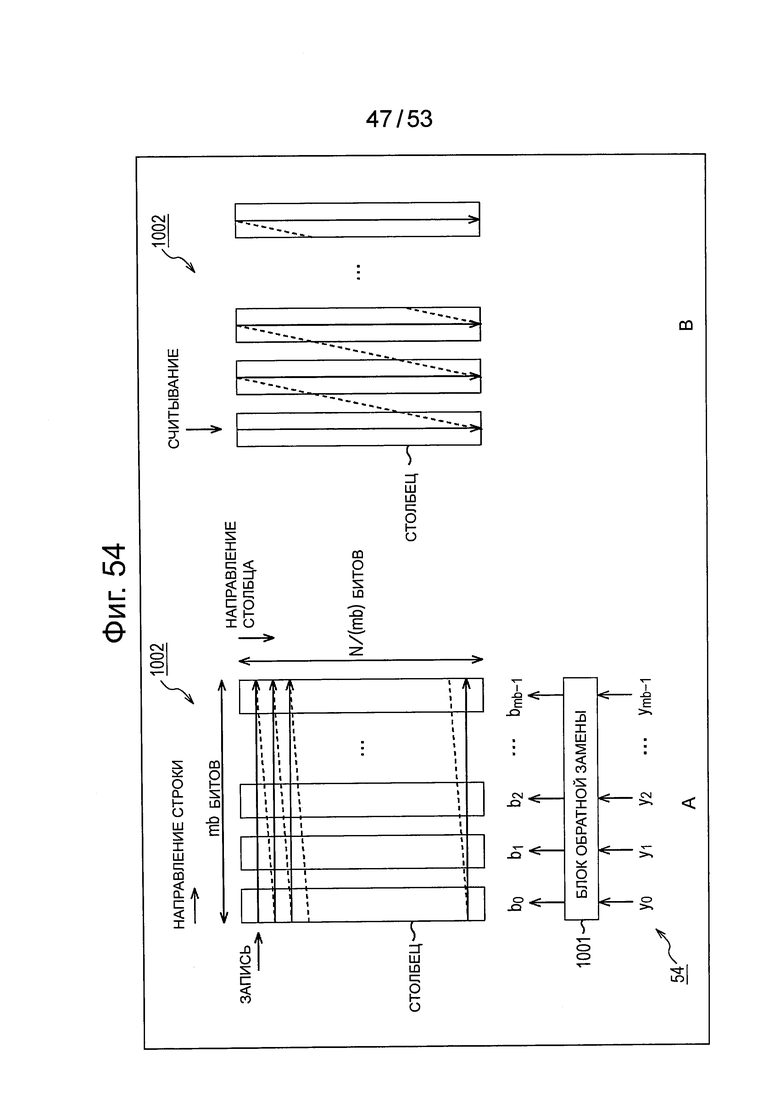

Фиг. 54 - схема, изображающая процесс, выполняемый мультиплексором 54, конфигурирующим деперемежитель 165 битов.

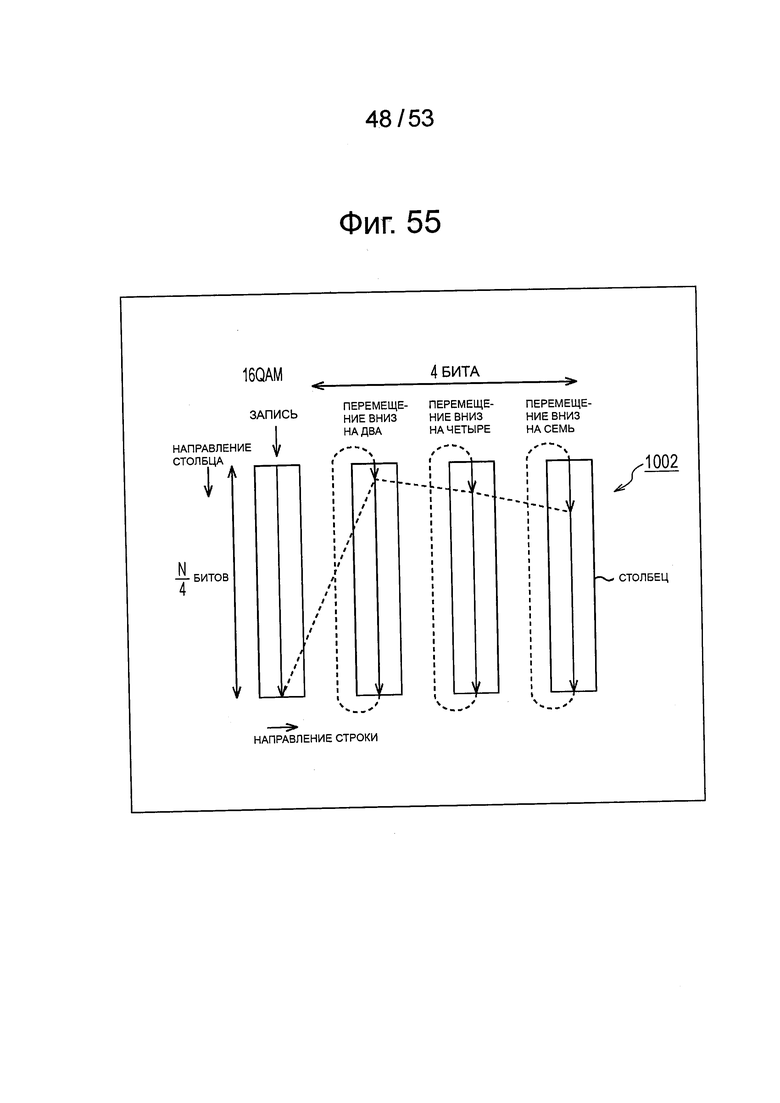

Фиг. 55 - схема, изображающая процесс, выполняемый деперемежителем 55 со скручиванием столбцов.

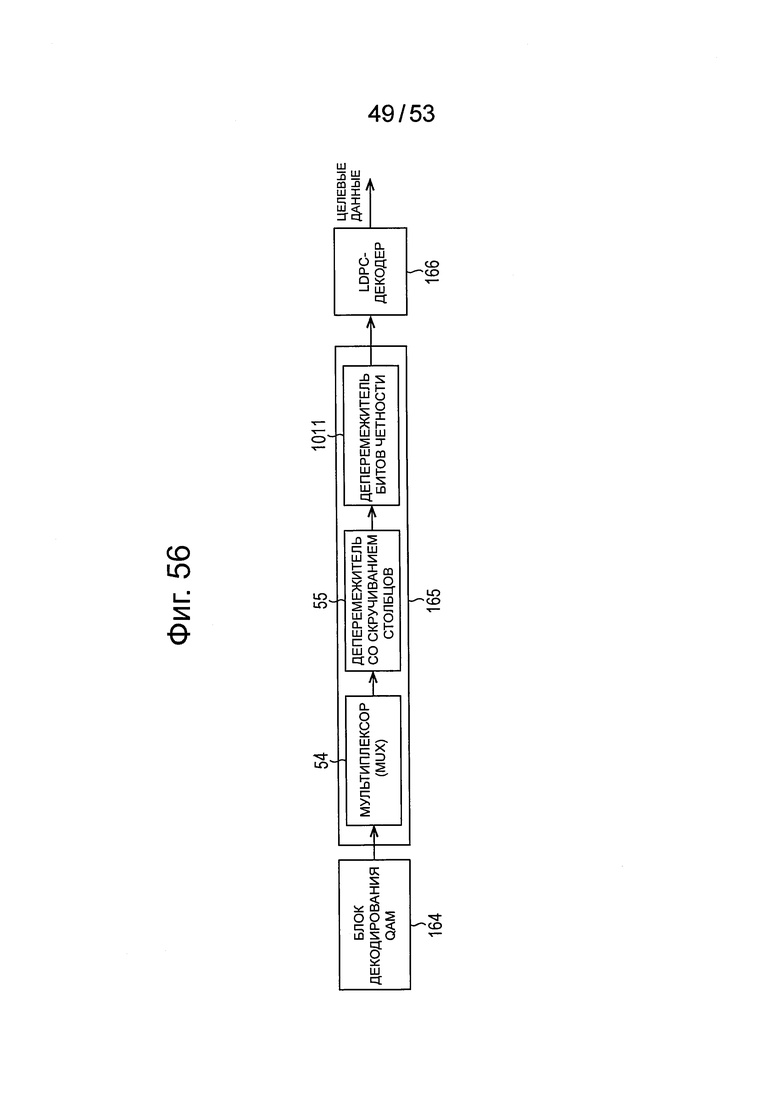

Фиг. 56 - блок-схема, иллюстрирующая другой пример конфигурации деперемежителя 165 битов.

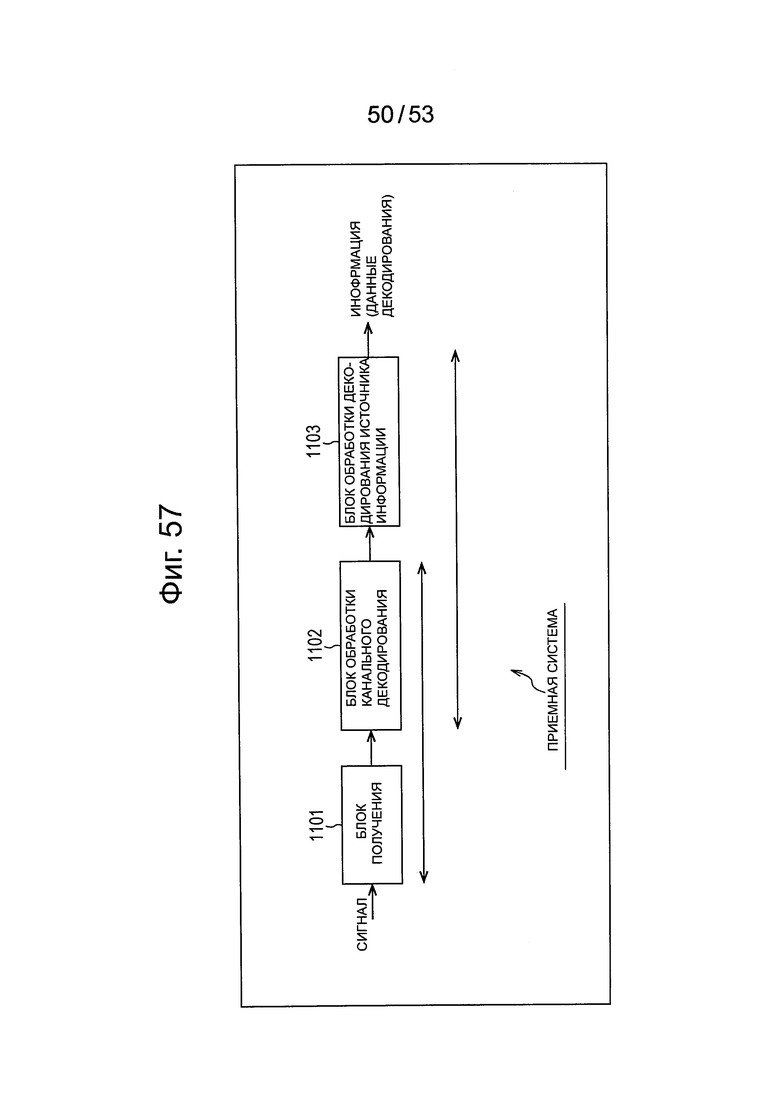

Фиг. 57 - блок-схема, иллюстрирующая первой пример конфигурации приемной системы, в которой может применяться приемное устройство 12.

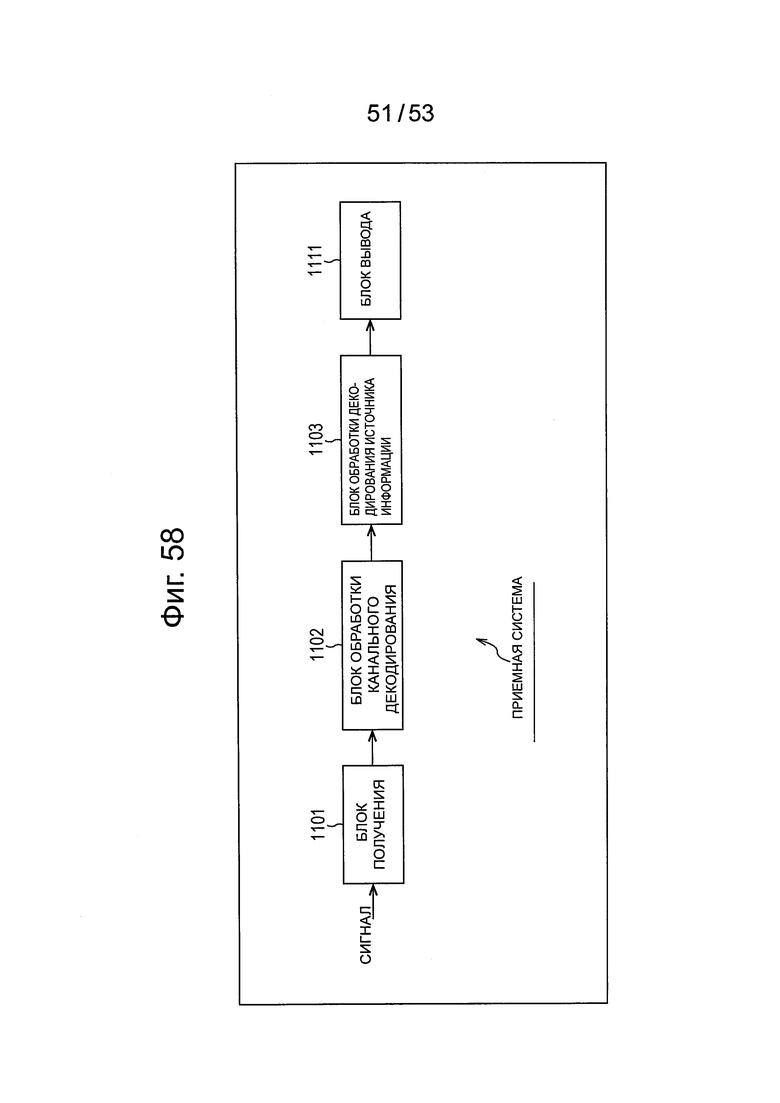

Фиг. 58 - блок-схема, иллюстрирующая второй пример конфигурации приемной системы, в которой может применяться приемное устройство 12.

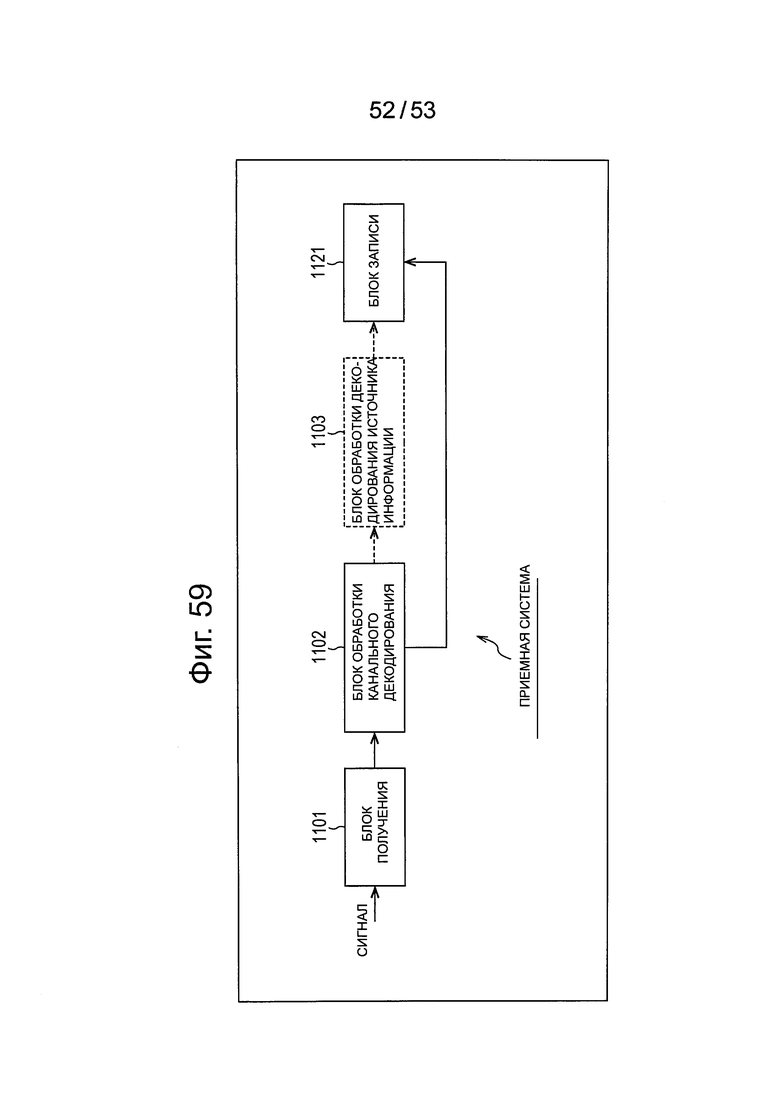

Фиг. 59 - блок-схема, иллюстрирующая третий пример конфигурации приемной системы, в которой может применяться приемное устройство 12.

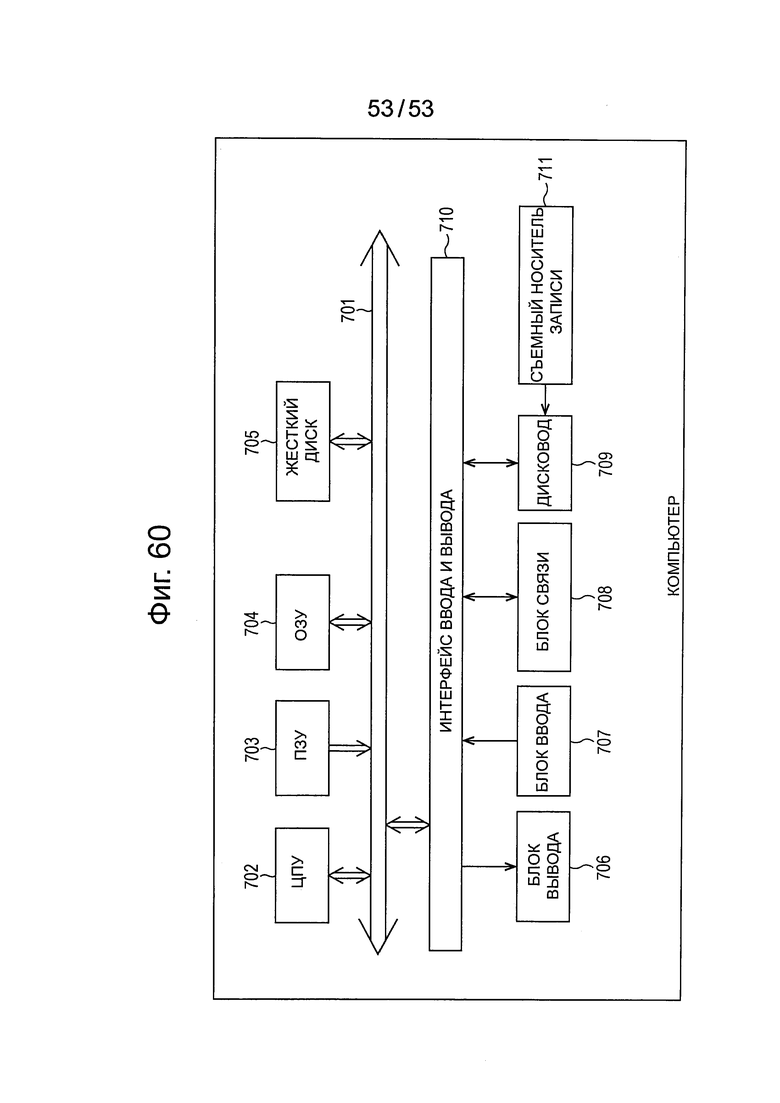

Фиг. 60 - блок-схема, иллюстрирующая пример конфигурации варианта осуществления компьютера, в котором применяется настоящая технология.

Подробное описание изобретения

Описание вариантов осуществления

Далее перед описанием вариантов осуществления данной технологии будет описан LDPC-код.

LDPC-код

Кроме того, LDPC-код представляет собой линейный код и не должен быть двоичным, но, в данном случае, описание будет приведено исходя из предположения того, что LDPC-код является двоичным.

Наиболее существенный признак LDPC-кода состоит в том, что матрица контроля четности, определяющая LDPC-код, является разреженной матрицей. В данном случае, разреженная матрица представляет собой матрицу, в которой число "1" элементов матрицы является очень маленьким (в основном элементы матрицы равны 0).

На фиг. 1 показана схема, иллюстрирующая матрицу H контроля четности LDPC-кода.

В матрице H контроля четности на фиг. 1, вес каждого столбца (вес столбца) (число "1") (вес) установлен на "3", и вес каждой строки (вес строки) установлен на "6".

При кодировании с использованием LDPC-кода (LDPC-кодирования), например, порождающая матрицы G, вырабатывается на основании матрицы H контроля четности, и кодовое слово (LDPC-код), вырабатывается путем умножения порождающей матрицы G на двоичный информационный бит.

В частности, устройство кодирования, которое выполняет LDPC-кодирование, сначала вычисляет порождающую матрицу G, в которой между матрицей H контроля четности и ее транспонированной матрицей HT устанавливается уравнение GHT=0. В данном случае, когда порождающая матрица G представляет собой матрицу размером K×N, устройство кодирования умножает битовую последовательность (вектор u) информационного бита, сформированного из K битов, с порождающей матрицей G для того, чтобы выработать кодовое слово c (=uG), сформированное из N битов. Кодовое слово (LDPC-код), выработанное с помощью устройства кодирования, принимается на приемной стороне через предварительно определенной канал связи.

Декодирование LDPC-кода представляет собой алгоритм, который предложен и упоминается как вероятностное кодирование Галлагера, и алгоритм можно выполнить с помощью алгоритма передачи сообщений путем распространения по так называемому графу Таннера, который выполнен с переменным узлом (который также упоминается как узел сообщения) и проверочным узлом. Здесь и далее переменный узел и контрольный узел упоминаются при необходимости просто как узел.

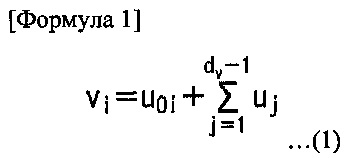

На фиг. 2 показана блок-схема последовательности операций, иллюстрирующая процедуру декодирования LDPC-кода.

Здесь и далее при необходимости действительное число (принятое LLR), которое получено путем правдоподобия "0" значения кодового бита LDPC-кода (кодовое слово 1), принятое на приемной стороне в качестве логарифмического отношения правдоподобия, упоминается как принятое значение u0i. Кроме того, предполагается, что сообщение, выходящее из проверочного узла, будет представлять собой uj, и предполагается, что сообщение, выходящее из переменного узла, будет представлять собой vi.

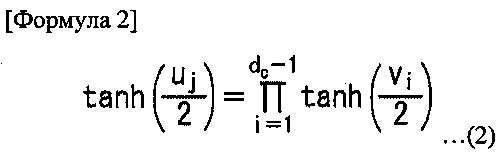

Сначала при декодировании LDPC-кода, как показано на фиг. 2, на этапе S11 принимается LDPC-код, сообщение uj (сообщение проверочного узла) устанавливается в "0", переменная k, которая представляет собой целое число в качестве счетчика итерационного процесса, устанавливается в "0", и процесс переходит на этапе S12. На этапе S12 сообщение vi (сообщение переменного узла) получается путем выполнения вычисления (вычисления переменного узла), показанного в уравнении (1), на основании принятого значения u0i, полученного путем приема LDPC-кода, и сообщение uj получается путем выполнения вычисления (вычисления проверочного узла), показанного в уравнении (2), на основании сообщения vi.

В данном случае, dv и dc в уравнении (1) и в уравнении (2) представляют собой, соответственно, параметры, показывающие число "1" в вертикальном направлении (в направлении столбца) и в горизонтальном направлении (в направлении строки) матрицы H контроля четности, которую можно выбрать произвольным образом. Например, в случае LDPC-кода, показанного на фиг. 1, в котором вес столбца равен 3, и вес строки равен 6 (LDPC-код (3, 6)), он устанавливается с параметрами dv=3 и dc=6.

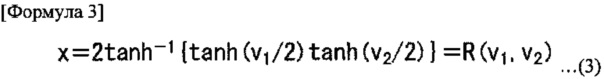

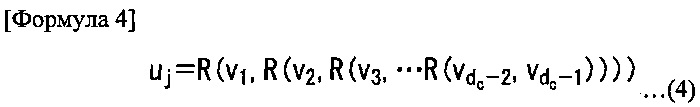

В дополнение к этому, при вычислении переменного узла из уравнения (1) и вычислении проверочного узла из уравнения (2) сообщение, которое вводится с края (линия, соединяющая переменный узел и проверочный узел), и из которого должно выводиться сообщение, не используется в качестве цели вычисления, и таким образом, диапазон вычисления равен 1 - Dv-1 или 1 - Dc-1. Кроме того, вычисление проверочного узла из уравнения (2) выполняется фактически путем предварительного создания таблицы из функции R(v1,v2), показанной в уравнении (3), которая определена в качестве одного выхода для двух входов v1 и v2 и непрерывно (рекурсивно) использует таблицу, как показано в уравнении (4).

На этапе S12 переменная k получает приращение на "1", и процесс переходит на этап S13. На этапе S13 определяется, больше или нет переменная k, чем предварительно определенное итерационное число C декодирования. На этапе S13, если определено, что переменная k не будет больше, чем C, процесс возвращается на этап S12, и повторяется тот же самый процесс.

Кроме того, на этапе S13, если определено, что переменная k больше, чем C, процесс переходит на этап S14, сообщение vi, в качестве результата декодирования, который будет окончательно выводиться, получается и выводится путем выполнения вычисления, показанного в уравнении (5), и процесс декодирования LDPC-кода заканчивается.

В данном случае, вычисление уравнения (5) отличается от вычисления переменного узла из уравнения (1) и выполняется с использованием сообщения uj со всех ребер, связанных с переменным узлом.

На фиг. 3 показана схема, иллюстрирующая пример матрицы H контроля четности с LDPC-кодом (3, 6) (кодовая скорость равна 1/2, длина кода равна 12).

В матрице H контроля четности, показанной на фиг. 3, вес столбца установлен на 3, и вес строки установлен на 6, аналогично фиг. 1.

На фиг. 4 показана схема, иллюстрирующая график Таннера матрицы H контроля четности (фиг. 3).

В данном случае, на фиг. 4, проверочные узлы показаны знаком плюс "+", и переменные узлы показаны знаком равно "=". Проверочные узлы и переменные узлы, соответственно, соответствуют строкам и столбцам матрицы H контроля четности. Соединительные линии между проверочными узлами и переменными узлами представляют собой ребро, и ребра соответствуют элементам "1" в матрице контроля четности.

Другими словами, если элемент в j-ой строке и i-ом столбце матрицы контроля четности равен 1 (фиг. 4), i-ый переменный узел (узел "=") сверху и j-ый проверочный узел (узел "+") сверху соединены с помощью ребра. Ребро представляет собой то, что кодовый бит, соответствующий переменному узлу, имеет ограничения, соответствующие проверочному узлу.

В алгоритме произведения суммы, который представляет собой способ декодирования LDPC-кода, вычисление переменного узла и вычисление проверочного узла выполняются повторно.

На фиг. 5 показана схема, иллюстрирующая вычисление переменного узла, которое выполняется в переменном узле.

В переменном узле сообщение vi, соответствующее ребру, подлежащему вычислению, получается путем вычисления переменного узла из уравнения (1) с использованием сообщений u1 и u2 из оставшихся ребер, которые соединены с переменным узлом, и принятого значения u0i. Сообщения, соответствующие другим ребрам, получаются таким же образом.

На фиг. 6 показана схема, иллюстрирующая вычисление проверочного узла, которая выполняется в проверочном узле.

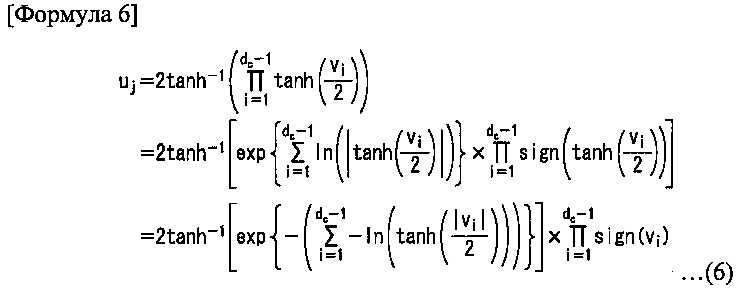

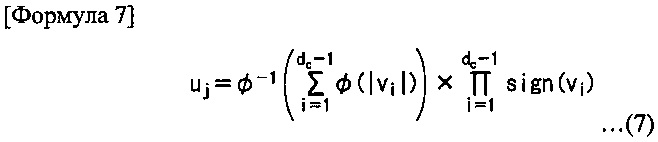

В данном случае, вычисление проверочного узла из уравнения (2) можно переписать в виде уравнения (6) с использованием функциональной зависимости уравнения a×b=exp{ln(|a|)+ln(|b|)}×sign(a)×sign(b). В данном случае, sign(x) равен 1 при x≥0, и sign(x) равен -1 при x<0.

Когда x≥0, если функция ϕ(x) определена в виде уравнения ϕ(x)=Ln(tanh(x/2)), устанавливается уравнение ϕ-1(x)=2tanh-1(e-x) таким образом, что уравнение (6) можно преобразовать в уравнение (7).

В проверочном узле вычисление проверочного узла из уравнения (2) выполняется в соответствии с уравнением (7).

Другими словами, в проверочном узле, как показано на фиг. 6, сообщение Uj, соответствующее ребру, которое будет вычисляться, получается с помощью вычисления проверочного узла из уравнения (7) с использованием сообщений v1, v2, v3, v4, и v5 из оставшихся ребер, которые соединены с проверочным узлом. Сообщения, соответствующие другим ребрам, получаются таким же образом.

В дополнение, функция ϕ(x) из уравнения (7) может быть представлена в виде уравнения ϕ(x)=ln((ex+1)/(ex-1)), когда x>0, ϕ(x)=ϕ-1(x). Когда функции ϕ(x) и ϕ-1(x) реализованы в виде обратных средств, в некоторых случаях функции можно реализовать с использованием таблиц поиска (LUT), но LUT являются одинаковыми.

Пример конфигурации передающей системы, в которой применяется настоящая технология

На фиг. 7 показана схема, иллюстрирующая пример конфигурации варианта осуществления передающей системы, в которой применяется настоящая технология (система относится к таким системам, в которых множество устройств ассемблируется логическим образом, и не имеет значение то, находится ли устройство, составляющее часть целого, в одном и том же корпусе).

На фиг. 7 передающая система включает в себя передающее устройство 11 и приемное устройство 12.

Передающее устройство 11 выполняет передачу (широковещание) (отправку), например, программ и т.п. телевизионного вещания. Другими словами, передающее устройство 11 кодирует, например, целевые данные, которые представляют собой цель передачи, такие как данные изображения и аудиоданные в виде программы в LDPC-код, и передает кодированные целевые данные через канал 13 связи, такой как, например, спутниковые линии, наземные волны, кабели (проводные линии).

Приемное устройство 12 принимает LDPC-код, который передается из передающего устройства 11 через канал 13 связи, декодирует LDPC-код в целевые данные и выводит данные.

В данном случае, известно, что LDPC-код, который используется в системе передачи, показанной на фиг. 7, проявляет в значительной степени высокую пропускную способность в канале связи с аддитивным белым гауссовым шумом (AWGN).

Между тем, канал 13 связи может вырабатывать пакетную ошибку или стирание пакета. Например, в частности, когда канал 13 связи представляет собой наземные волны, в системе ортогонального мультиплексирования с частотным разделением (OFDM) в многолучевой среде, в которой отношение желательного сигнала к нежелательному (D/U) равно 0 дБ (мощность нежелательного сигнала (эхо-сигнала) равна мощности желательного сигнала (сигнала, распространяющегося по основному пути)), мощность определенного символа становится равной 0 (стирание) в соответствии с задержкой эхо-сигнала (путь распространения отличается от основного пути распространения).

Кроме того, даже при фазовом дрожании (канал связи, в котором задержка равна 0, и добавляется эхо-сигнал из-за доплеровской частоты), если отношение D/U равно 0 дБ, мощность всех OFDM символов в специфический момент времени становится равной 0 (стирание) из-за Доплеровской частоты.

Кроме того, пакетная ошибка может возникать из-за статуса проводного соединения из приемного блока (не показан), такого как антенна, которая принимает сигналы из передающего устройства 11 на стороне приемного устройства 12 в приемное устройство 12, и нестабильности мощности приемного устройства 12.

Между тем, при декодировании LDPC-кода в столбце матрицы H контроля четности и переменного узла, соответствующего кодовому биту LDPC-кода, как показано на фиг. 5, поскольку выполняется вычисление переменного узла из уравнения (1) с добавлением кодового бита (его принятого значения u0i) LDPC-кода, если в кодовом бите, используемом при вычислении переменного узла, возникает ошибка, точность полученного сообщения уменьшается.

Затем при декодировании LDPC-кода, поскольку вычисление проверочного узла из уравнения (7) в проверочном узле выполняется с использованием сообщения, которое получено в переменном узле, который подсоединен к проверочному узлу, если увеличивается число проверочных узлов, в которых множество переменных узлов, соединенных с ним (кодовый бит LDPC-кода, соответствующий ему), одновременно становится ошибочным состоянием (включая стирание), производительность декодирования ухудшается.

Другими словами, например, если два или более переменных узлов, подсоединенных к проверочному узлу, стираются одновременно, проверочный узел возвращает сообщение, в котором вероятность наличия значения 0 и вероятность наличия значения 1 являются одинаковыми во всех переменных узлах. В этом случае, проверочный узел, которые возвращает сообщение с равной вероятностью, не вносит вклад ни в один процесс декодирования (один набор из вычисления переменного узла и вычисления проверочного узла), в результате требуется большое число итераций процесса декодирования, производительность декодирования ухудшается, и увеличивается потребляемая мощность приемного устройства 12, которая декодирует LDPC-код.

Таким образом, передающая система, показанная на фиг. 7, позволяет повысить стойкость к ошибке и стиранию пакета при сохранении производительности в канале связи AWGN (AWGN-канале).

Пример конфигурации передающего устройства 11

На фиг. 8 показана блок-схема, иллюстрирующая пример конфигурации передающего устройства 11 (фиг. 7).

В передающем устройстве 11 входные потоки из одного или более входных потоков в качестве целевых данных подаются в мультиплексор 111 с адаптацией режима.

Мультиплексор 111 с адаптацией режима выполняет процесс, такой как выбор режима и мультиплексирование одного или более входных потоков, подаваемых в него, при необходимости, и обеспечивают подачу результирующих данных в блок 112 набивки.

Блок 112 набивки выполняет необходимую набивку нулями (вставку нулей) в отношении данных, полученных из мультиплексора 111 с адаптацией режима, и обеспечивает подачу результирующих данных в BB-скремблер 113.

BB-скремблер 113 выполняет основополосное скремблирование (BB-скремблирование) в отношении данных, поступающих из блока 112 набивки, и подает результирующие данные в BCH-кодер 114.

BCH-кодер 114 выполняет BCH-кодирование-кодирование над данными, поступающими из BB-скремблера 113, и подает результирующие данные в виде целевых LDPC-данных, которые представляют собой цель LDPC-кодирования, в LDPC-кодер 115.

LDPC-кодер 115 выполняет LDPC-кодирование в соответствии с матрицей контроля четности, в которой матрица четности, которая представляет собой часть, соответствующую битам четности LDPC-кода, имеет ступенчатую структуру над целевыми LDPC-данными, поступающими из BCH-кодера 114, и выводит LDPC-код с целевыми LDPC-данными в виде информационного бита.

Другими словами, LDPC-кодер 115 выполняет LDPC-кодирование, которое кодирует целевые LDPC-данные в LDPC-код (соответствующий матрице контроля четности), который определен в предварительно определенной стандартах, таких как, например, DVB-S.2, DVB-T.2 и DVB-C.2, или в LDPC-код (соответствующий матрице контроля четности), который определяется заранее, и выводит результирующий LDPC-код.

В данном случае, LDPC-код, который определен в стандартах, таких как DVB-S.2, DVB-T.2 и DVB-C.2, представляет собой нерегулярный код повторения-накопления (IRA), и матрица четности в матрице контроля четности LDPC-кода имеет ступенчатую структуру. Матрица четности и ступенчатая структура будут описаны позже. Кроме того, код IRA описан, например, в "Irregular Repeat-accumulate Codes," Н. Jin, A. Khandekar, and RJ. McEliece, in Proceedings of 2nd International Symposium on Turbo codes and Related Topics, pp. 1-8, Sept. 2000.

LDPC-код, выводимый из кодера 115 LDPC, подается в перемежитель 116 битов.

Перемежитель 116 битов выполняет перемежение битов, которое будет описано позже, над LDPC-кодом, поступающим из LDPC-кодера 115, и подает LDPC-код после битового перемежения в блок 117 отображения.

Блок 117 отображения выполняет квадратурную модуляцию (многоуровневую модуляцию) путем отображения LDPC-кода, поступающего из перемежителя 116 битов, в сигнальную точку, представляющую один символ квадратурной модуляции, в блок кодового бита одного бита или более из LDPC-кода (символьного блока).

Другими словами, блок 117 отображения выполняет квадратурную модуляцию путем отображения LDPC-кода, поступающего из битового перемежителя 116, в сигнальные точки, которые определены в схеме модуляции, которая выполняет квадратурную модуляцию LDPC-кода, на плоскости IQ (созвездии IQ), которая определена в виде оси I, представляющей собой компоненту I, которая находится в фазе с несущей волной, и оси Q, представляющей собой компоненту Q, которая ортогональна несущей волне.

В данном случае, пример схема модуляции квадратурной модуляции, выполняемой в блоке 117 отображения, включает в себя, например, схему модуляции, которая определена в стандартах, таких как DVB-S.2, DVB-T.2 и DVB-C.2, и другие схемы модуляции, иными словами, например, двоичную фазовую манипуляцию (BPSK), квадратурную фазовую манипуляцию (QPSK), 8-позиционную фазовую манипуляцию (PSK), 16-позиционную амплитудно-фазовую манипуляцию (APSK), 32 APSK, 16-позиционную квадратурную амплитудную модуляцию (QAM), 64QAM, 256QAM, 1024QAM, 4096QAM и 4-позиционную импульсную амплитудную модуляцию (PAM). В блоке 117 отображения схема модуляции, с помощью которой выполняется квадратурная модуляция, устанавливается заранее, например, в соответствии с операцией оператора передающего устройства 11.

Данные, которые получаются с помощью процесса, выполняемого в блоке 117 отображения (результат отображения, полученные путем отображения символа в сигнальную точку), подаются во временной перемежитель 118.

Временной перемежитель 118 выполняет временное перемежение (перемежение в направлении времени) в блоке символа над данными, поступающими из блока 117 отображения, и подает результирующие данные в кодер 119 с одним входом и одним выходом/с множеством входов и одним выходом (SISO/MISO).

Кодер 119 SISO/MISO выполняет пространственно-временное кодирование над данными, поступающими из временного перемежителя 118, и подает результирующие данные в частотный перемежитель 120.

Частотный перемежитель 120 выполняет частотное перемежение (перемежение в частотном направлении) в блоке символа над данными, поступающими из кодера 119 SISO/MISO, и подает результирующие данные в блок 131 построителя кадров/выделения ресурсов.

Между тем, например, управляющие данные для управления передачей, такие как основополосная сигнализация (BB-сигнализация) (заголовок BB) подается в BCH-кодер 121.

BCH-кодер 121 аналогично BCH-кодеру 114 выполняет BCH-кодирование управляющих данных, подаваемых в него, и подает результирующие данные в LDPC-кодер 122.

LDPC-кодер 122, аналогично LDPC-кодеру 115, выполняет LDPC-кодирование над данными, поступающими из BCH-кодера 121 в качестве целевых LDPC-данных, и подает результирующий LDPC-код в блок 123 отображения.

Блок 123 отображения, аналогично блоку 117 отображения, выполняет квадратурную модуляцию путем отображения LDPC-кода, поступающего из LDPC-кодера 122, в сигнальную точку, представляющую один символ квадратурной модуляции, в блоке кодового бита из одного бита или более LDPC-кода (символьного блока), и подает результирующие данные в частотный перемежитель 124.

Частотный перемежитель 124, аналогично частотному перемежителю 120, выполняет частотное перемежение в символьном блоке над данными, поступающими из блока 123 отображения, и подает результирующие данные в блок 131 выделения ресурсов/построитель кадров.

Блок 131 выделения ресурсов/построитель кадров вставляет пилотный символ в необходимую позицию данных (символа), поступающих из частотных перемежителей 120 и 124, вырабатывает кадр, сформированный из символов с предварительно определенным числом (например, кадр физического уровня (PL), кадр T2, кадр C2 и т.п.), из результирующих данных (символа) и подает кадр в блок 132 выработки OFDM-сигнала.

Блок 132 выработки OFDM-сигнала вырабатывает OFDM-сигнал, соответствующий кадру, из кадра, поступающего из блока 131 выделения ресурсов/построения кадров, и передает OFDM-сигнал через канал 13 связи (фиг. 7).

В дополнение, передающее устройство 11 можно сконфигурировать без наличия некоторых блоков, показанных на фиг. 8, таких как, например, временной перемежитель 118, кодер 119 SISO/MISO, частотный перемежитель 120 и частотный перемежитель 124.

Фиг. 9 иллюстрирует пример конфигурации перемежителя 116 битов, показанного на фиг. 8.

Перемежитель 116 битов имеет функцию перемежения данных и выполнен с перемежителем 23 четности, перемежителем 24 со скручиванием столбцов и демультиплексором (DEMUX) 25. В дополнение, перемежитель 116 битов можно выполнить без наличия одного или двух из перемежителя 23 четности и перемежителя 24 со скручиванием столбцов.

Перемежитель 23 четности выполняет перемежение битов четности, которое обеспечивает перемежение бита четности LDPC-кода, поступающего из LDPC-кодера 115, в позиции другого бита четности и подает LDPC-код после перемежения четности в перемежитель 24 со скручиванием столбцов.

Перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов над LDPC-кодом, поступающим из перемежителя 23 четности, и подает LDPC-код после перемежения со скручиванием столбцов в демультиплексор 25.

Другими словами, LDPC-код передается тогда, когда кодовые биты одного бита или более LDPC-кода отображаются в сигнальную точку, представляющую один символ или квадратурную модуляцию с помощью блока 117 отображения (фиг. 8).

В перемежителе 24 со скручиванием столбцов, например, перемежение со скручиванием столбцов, которое будет описано позже, выполняется в качестве процесса перегруппировки, предназначенного для перегруппировки кодовых битов LDPC-кода, поступающего из перемежителя 23 четности, таким образом, что множество кодовых битов LDPC-кода, соответствующего любой 1 в любой одной строке матрицы контроля четности, которая используется в LDPC-кодере 115, не включены в один символ.

Демультиплексор 25 получают LDPC-код, имеющей повышенную устойчивость к AWGN и т.п., путем выполнения процесса замены для замены позиции двух или более кодовых битов LDPC-кода, который представляет собой символ, над LDPC-кодом, поступающим из перемежителя 24 со скручиванием столбцов. Затем демультиплексор 25 подает два или более кодовых битов LDPC-кода, который получается в процессе замены, в качестве символа, в блок 117 отображения (фиг. 8).

На фиг. 10 показана схема, иллюстрирующая матрицу H контроля четности, используемую при LDPC-кодировании в LDPC-кодере 115, показанном на фиг. 8.

Матрица Н контроля четности имеет структуру порождающей матрицы малой плотности (LDGM) и может быть представлена уравнением H=[HA|HT] (матрица, в которой элементы информационной матрицы HA представляют собой элементы, расположенные слева, элементы матрицы HT четности представляют собой элементы, расположенные справа) с помощью информационной матрицы HA частей, соответствующих информационному биту, и матрицы HT четности частей, соответствующих биту четности, из кодовых битов LDPC-кода.

В данном случае, число битов информационного бита и число битов бита четности из кодовых битов одного LDPC-кода (1 кодовое слово), соответственно, упоминаются как информационная длина K и длина M битов четности, и число кодовых битов одного LDPC-кода упоминается как длина N (=K+M) кода.

Информационная длина K и длина M битов четности для LDPC-кода с определенной длиной N кода определяются с помощью кодовой скорости. Кроме того, матрица H контроля четности представляет собой матрицу типа строка × столбец размером M×N. Затем информационная матрица HA представляет собой матрицу размером M×K, и матрица HT четности представляет собой матрицу размером M×M.

На фиг. 11 показана матрица HT четности матрицы H контроля четности LDPC-кода, которая определена в стандартах DVB-S.2, DVB-T.2 и DVB-C.2.

Как показано на фиг. 11, матрица HT четности матрицы H контроля четности LDPC-кода, который определен в стандарте, такой как DVB-T.2, представляет собой матрицу со ступенчатой структурой, в которой элементы 1 размещаются в ступенчатом виде (нижняя двухдиагональная матрица). Вес строки матрицы HT четности равен 1 в первой строке и равен 2 во всех оставшихся строках. Кроме того, вес столбца равен 1 в последнем столбце и равен 2 во всех оставшихся столбцах.

Кроме того, как описано выше, можно легко выработать LDPC-код матрицы H контроля четности, чья матрица HT четности имеет ступенчатую структуру, за счет использования матрицы H контроля четности.

Другими словами, LDPC-код (одно кодовое слово) представлен с помощью вектора-строки c, и вектор-столбец, полученный путем транспонирования вектора-строки, представлен cT. Кроме того, часть информационного бита представлена с помощью вектора-строки c, и часть бита четности представлена с помощью вектора-строки T, в котором вектор-строка представляет собой LDPC-код.

В этом случае вектор-строка с представлен с помощью уравнения c=[A|T] (вектор-строка, в котором элементы вектора-строки A представляют собой элементы, расположенные слева, и элементы вектора-строки T представляют собой элементы, расположенные справа) с использованием вектора-строки A в качестве информационного бита и вектора-строки T в качестве бита четности.

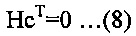

Необходимо, чтобы матрицы H контроля четности и вектор-строка c=[A|T] в качестве LDPC-кода удовлетворяли уравнению HcT=0, и если матрица HT четности матрицы H=[HA|HT] контроля четности имеет ступенчатую структуру, показанную на фиг. 11, вектор-строка T в качестве битов четности, конфигурирующих вектор-строку c=[A|T], удовлетворяющую уравнению HcT=0, можно получить последовательно (по порядку) путем выработки элемента каждой строки 0 из элемента первой строки вектора-столбца HcT по порядку в уравнении HcT=0.

На фиг. 12 показана схема, изображающая матрицу Н контроля четности LDPC-кода, которая определяется в стандарте DVB-T.2.

В матрице H контроля четности LDPC-кода, которая определяется в стандарте DVB-T.2, вес X столбца задается в первом столбце - KX-ом столбце, и вес столбца 3 задается в следующем K3 столбце, вес столбца 2 задается в следующем M-1 столбце, и вес столбца 1 задается в последнем столбце.

В данном случае, выражение KX+K3+M-1+1 равно длине N кода.

На фиг. 13 показана схема, иллюстрирующая число столбцов KX, K3 и M и вес X столбца для каждой скорости кодирования LDPC-кода, которая определена в стандартах DVB-T.2 и т.п.

В стандартах DVB-T.2 и т.п. определены LDPC-коды длиной N кода 64800 битов и 16200 битов.

Затем определяются 11 кодовых скоростей (номинальных скоростей) 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10 для LDPC-кода длиной N кода 64800 битов, и определяются 10 кодовых скоростей 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6 и 8/9 для LDPC-кода длиной N кода 16200 битов.

В данном случае, длина N кода 64800 битов упоминается как 64 кбит, и длина N кода 16200 битов упоминается как 16 кбит.

Для LDPC-кода кодовый бит, соответствующий столбцу, имеющему большой вес столбца матрицы H контроля четности, должен иметь, вероятно, низкую частоту появления ошибок.

В матрице H контроля четности, которая определена в стандарте DVB-T.2 и т.п., показанной на фиг. 12 и фиг. 13, чем ближе столбец находится к первой стороне (к левой стороне), тем, вероятно, будет больше вес столбца, поэтому для LDPC-кода, соответствующему матрице H контроля четности, кодовый бит на начальной стороне должен быть, вероятно, сильным по отношению к ошибке (то есть иметь устойчивость к ошибке), и кодовый бит на конечной стороне должен быть, вероятно, слабым по отношению к ошибке.

Фиг. 14 иллюстрирует пример размещения 16 символов (сигнальных точек, соответствующих им) на плоскости IQ, когда 16QAM выполняется блоком 117 отображения, показанным на фиг. 8.

Другими словами, поз. A на фиг. 14 показывает символы (сигнальные точки, соответствующие им) 16QAM стандарта DVB-T.2.

В 16QAM один символ представлен четырьмя битами, и существует 16 (=24) символов. Затем 16 символов размещаются таким образом, чтобы сформировать квадрат размером 4×4 square в направлении I × направлении Q, с началом координат плоскости IQ в качестве центра.

Теперь, если (i+1)-ый бит из старшего значащего бита в битовой последовательности, представленной с помощью одного символа, представлен в виде бита yi, четыре бита, которые представляют собой один бит 16QAM, можно представить в виде битов y0, y1, y2 и y3 из старшего значащего бита по порядку. Если схемой модуляции является 16QAM, четыре бита кодовых битов LDPC-кода становятся (принимают вид символа) в символ (значения символа) из четырех битов y0-y3.

Поз. B на фиг. 14 показывает битовые границы для четырех битов y0-y3 символьного бита yi (который в дальнейшем упоминается как символьный бит), представленных символами 16QAM.

В данном случае, битовая граница для символьного бита yi (на фиг. 14 i=0, 1, 2, и 3) означает границу между символом, чей символьный бит yi равен 0, и символом, чей символьный бит yi равен 1.

Как показано поз. B на фиг. 14, для верхнего символьного бита y0 из четырех символьных битов y0-y3, представленных символами 16QAM, одно место по Q-оси в плоскости IQ представляет собой битовую границу, и для второго места (второго из старшего значащего бита) символьного бита y1 только одно место по I-оси в плоскости IQ представляет собой битовую границу.

Кроме того, для третьего символьного бита y2, битовые границы расположены между первым столбцом и вторым столбцом и между третьим столбцом и четвертым столбцом слева в пределах 4×4 символов.

Кроме того, для четвертого символьного бита y3, битовые границы находятся между первой строкой и второй строка и между третьей строкой и четвертой строкой сверху в пределах 4×4 символов.

Что касается символьного бита yi, представленного символами, чем больше символов находится в стороне от битовой границы, тем меньше возникает ошибок (вероятность возникновения ошибок является низкой), и чем больше символов находится ближе к битовой границе символов, тем больше возникает ошибок (вероятность возникновения ошибок является высокой).

Теперь, если бит, в котором почти не возникает ошибка (сильный с точки зрения возникновения ошибок) упоминается как "сильный бит", и бит, в котором легко возникает ошибка (слабый с точки зрения возникновения ошибок), упоминается как "слабый бит", то для четырех символьных битов y0-y3 для символа 16QAM, верхний символьный бит y0 и второй символьный бит y1 являются сильными битами, а третий символьный бит y2 и четвертый символьный бит y3 являются слабыми битами.

Фиг. 15 - фиг. 17 иллюстрируют пример размещения 64 символов (сигнальных точек, соответствующих им), другими словами, символов 16QAM DVB-T.2 на плоскости IQ, когда 64QAM выполняется с помощью блока 117 отображения, показанного на фиг. 8.

В 64QAM один символ представлен шестью битами, и существует 64 (=26) символа. Затем 64 символа размещаются таким образом, чтобы сформировать квадрат размером 8×8 в направлении I × направлении Q, с началом координат плоскости IQ в качестве центра.

Символьные биты одного символа 64QAM можно представить в виде битов y0, y1, y2, y3, y4 и y5 из старшего значащего бита и здесь по порядку. Если схемой модуляции является 64QAM, то шесть битов кодовых битов LDPC-кода представляет собой символ из символьных битов y0-y5 шести битов.

В данном случае, фиг. 15 иллюстрирует битовую границу для каждого из верхнего символьного бита y0 и второго символьного бита y1, фиг. 16 иллюстрирует битовую границу для каждого из третьего символьного бита y2 и четвертого символьного бита y3, и фиг. 17 иллюстрирует битовую границу для каждого из пятого символьного бита y4 и шестого символьного бита y5 среди символьных битов y0-y5 символа 64QAM.

Как показано на фиг. 15, число битовых границ для каждого из верхнего символьного бита y0 и второго символьного бита y1 равно одному. Кроме того, как показано на фиг. 16, число битовых границ для каждого из третьего символьного бита y2 и четвертого символьного бита y3 равно двум, и как показано на фиг. 17, число битовых границ для каждого из пятого символьного бита y4 и шестого символьного бита y5 равно четырем.

Поэтому, для символьных битов y0-y5 символа 64QAM верхний символьный бит y0 и второй символьный бит y1 являются самыми сильными битами, и третий символьный бит y2 и четвертый символьный бит y3 являются вторыми самыми сильными битами. Затем пятый символьный бит y4 и шестой символьный бит y5 являются слабыми битами.

Из фиг. 14 и фиг. 15 - фиг. 17 видно, что верхний бит должен быть, вероятно, сильным битом, и нижний бит должен быть, вероятно, слабым битом для символьных битов символа квадратурной модуляции.

Фиг. 18 иллюстрирует пример размещения четырех символов (сигнальных точек, соответствующих им) на плоскости IQ, другими словами, например, размещение сигнальных точек QPSK DVB-S.2, когда спутниковая линия используется в качестве канала 13 связи (фиг. 7), и QPSK выполняется блоком 117 отображения, показанным на фиг. 8.

В QPSK стандарта DVB-S.2 символ отображается в одну из четырех сигнальных точек, расположенных по окружности круга, имеющего радиус ρ, равный 1 с началом координат плоскости IQ в качестве центра.

Фиг. 19 иллюстрирует пример размещения восьми символов на плоскости IQ, другими словами, например, размещения сигнальных точек 8PSK DVB-S.2, когда спутниковая линия используется в качестве канала 13 связи (фиг. 7) и 8PSK выполняется блоком 117 отображения, показанным на фиг. 8.

В 8PSK стандарта DVB-S.2, символ отображается в один из восьми сигнальных точек, расположенных по окружности круга, имеющего радиус ρ, равный 1, с началом координат плоскости IQ в качестве центра.

Фиг. 20 иллюстрирует пример размещения 16 символов на плоскости IQ, другими словами, например, размещение сигнальных точек 16APSK стандарта DVB-S.2, когда спутниковая линия используется в качестве канала 13 связи (фиг. 7) и 16APSK выполняется блоком 117 отображения, показанным на фиг. 8.

Поз. А на фиг. 20 показывает созвездие 16APSK стандарта DVB-S.2.

В 16APSK стандарта DVB-S.2, символ отображается в одну из всех 16 сигнальных точек, включающих в себя четыре сигнальных точек, расположенных по окружности круга, имеющего радиус R1, и 12 сигнальных точек, расположенных по окружности круга, имеющего радиус R2 (>R1), с началом координат плоскости IQ в качестве центра.

Поз. В на фиг. 20 показывает отношение γ=R2/R1 радиуса R2 к радиусу R1 в созвездии 16APSK стандарта DVB-S.2.

Отношение γ радиуса R2 к радиусу R1 изменяется в зависимости от кодовой скорости в созвездии 16APSK стандарта DVB-S.2.

Фиг. 21 иллюстрирует пример размещения 32 символов на плоскости IQ, другими словами, например, размещение сигнальных точек 32APSK стандарта DVB-S.2, когда спутниковая линия используется в качестве канала 13 связи (фиг. 7), и 32APSK выполняется блоком 117 отображения, показанным на фиг. 8.

Поз. А на фиг. 21 показывает созвездие 32APSK стандарта DVB-S.2.

В 32APSK стандарта DVB-S.2, символ отображается в одну из всех 32 сигнальных точек, включающих в себя четыре сигнальных точки, расположенных по окружности круга, имеющего радиус R1, 12 сигнальных точек, расположенных по окружности круга, имеющего радиус R2 (>R1), и 16 сигнальных точек расположенных по окружности круга, имеющего радиус R3 (>R2), с началом координат плоскости IQ в качестве центра.

Поз. В на фиг. 21 показывает отношение γ1=R2/R1 радиуса R2 к радиусу R1 и отношение γ2=R3/R1 радиуса R3 к радиусу R1 в созвездии 32APSK стандарта DVB-S.2.

Отношение γ1 радиуса R2 к радиусу R1 и отношение γ2 радиуса R3 к радиусу R1 изменяются в зависимости от кодовой скорости в созвездии 32APSK стандарта DVB-S.2.

Существуют сильные биты и слабые биты даже для символьных битов для символов соответствующих типов квадратурных модуляций (QPSK, 8PSK, 16APSK и 32APSK) стандарта DVB-S.2, чьи созвездия показаны на фиг. 18 - фиг. 21, аналогично случаю, показанному на фиг. 14 - фиг. 17.

В данном случае, как показано на фиг. 12 и фиг. 13, существуют кодовые биты, которые являются слабыми с точки зрения возникновения ошибок, и кодовые биты, которые являются сильными с точки зрения возникновения ошибок, для LDPC-кода, который выводит LDPC-кодер 115 (фиг. 8).

Кроме того, как показано на фиг. 14 - фиг. 21, существуют сильные биты и слабые биты для символьных битов символа квадратурной модуляции, выполняемой блоком 117 отображения.

Поэтому, если кодовый бит, который является слабым с точки зрения возникновения ошибок, LDPC-кода выделяется слабому символьному биту символа квадратурной модуляции, то, в целом, устойчивость к ошибке уменьшается.

Таким образом, в качестве тенденции выделения кодового бита, который является слабым к ошибке, LDPC-кода сильному биту (символьному биту) символа квадратурной модуляции предложен перемежитель для перемежения кодового бита LDPC-кода.

Демультиплексор 25, показанный на фиг. 9, может выполнять процесс, выполняемый перемежителем.

На фиг. 22 показана схема, изображающая процесс, выполняемый демультиплексором 25 (фиг. 9).

Другими словами, поз. А на фиг. 22 показывает пример функциональной конфигурации демультиплексора 25.

Демультиплексор 25 выполнен с памятью 31 и блоком 32 замены.

LDPC-код из LDPC-кодера 115 подается в память 31.

Память 31 имеет объем памяти для хранения mb битов в направлении строки (по горизонтали) и N/(mb) битов в направлении столбца (по вертикали) и обеспечивает блок 32 замены кодовым битом LDPC-кода, который подается в нее, путем записи кодового бита в направлении столбца и считывания кодового бита в направлении строки.

В данном случае, N (= информационная длина K + длина M битов четности) представляет собой длину кода LDPC-кода, как описано выше.

Кроме того, m представляет собой число битов кодового бита LDPC-кода в качестве одного символа, b представляет собой предварительно определенное положительное целое число, и m представляет собой множитель, который используется для целочисленного умножения. Демультиплексор 25 формирует (символизирует) кодовый бит LDPC-кода в символ в блоке с предварительно определенным числом битов m, и множитель b представляет собой число символов, полученных с помощью однократной символизации с помощью демультиплексора 25.

Поз. А на фиг. 22 иллюстрирует пример конфигурации демультиплексора 25, в котором схемой модуляции является 64QAM, которая отображает символ в любой из 64 сигнальных точек, и поэтому, числом m битов кодового бита LDPC-кода, которое равно одному символу, равно шести битам.

Кроме того, как показано поз. А на фиг. 22, множитель b равен 1, и поэтому память 31 имеет объем памяти N/(6×1)×(6×1) битов в направлении столбца х направлении строки.

В данном, случае, область хранения памяти 31, которая имеет один бит в направлении строки и продолжается в направлении столбца, в дальнейшем, при необходимости, упоминается как столбец. Как показано поз. А на фиг. 22, память 31 выполнена с 6 (=6×1) столбцами.

В демультиплексоре 25 запись кодового бита LDPC-кода в направлении сверху вниз столбцов (в направлении столбца), конфигурирующих память 31, выполняется в направлении столбца слева направо.

Затем, если запись кодового бита закончилась внизу крайнего правого столбца, кодовые биты считываются из первого столбца всех столбцов, конфигурирующих память 31, в направлении строки в блок из шести битов (mb битов) и подаются в блок 32 замены.

Блок 32 замены выполняет процесс замены, предназначенный для замены позиций кодовых битов из шести битов из памяти 31, и выводит шесть результирующий битов в качестве шести символьных битов y0, y1, y2, y3, y4 и y5, которые представляют собой один символ 64QAM.

Другими словами, кодовые биты mb битов (в данном случае, шесть битов) считываются из памяти 31 в направлении строки, но если i-ый бит (i=0, 1, …, mb-1) из старшего значащего бита кодовых битов mb битов, которые считываются из памяти 31, представлен в качестве бита bi, кодовые биты из шести битов, которые считываются из памяти 31 в направлении строки, можно представить в порядке в виде битов b0, b1, b2, b3, b4 и b5 от старшего значащего бита.

Из зависимости весов столбцов, показанной на фиг. 12 и фиг. 13, кодовый бит, расположенный в направлении бита b0, представляет собой кодовый бит, который является "сильным" по отношению к ошибке, и кодовый бит, расположенный в направлении бита b5 представляет собой кодовый бит, который является "слабым" по отношению к ошибке.

Блок 32 замены может выполнять процесс замены, предназначенный для замены позиций кодовых битов b0-b5 количеством шесть битов из памяти 31 таким образом, что кодовый бит, который является "слабым" по отношению к ошибке среди кодовых битов b0-b5 количеством шесть битов из памяти 31 выделяется сильным битам среди символьных битов y0-y5 одного символа 64QAM.

В данном случае, различные способы замены, которые позволяют заменять кодовые биты b0-b5 количеством шесть битов из памяти 31 и выделять их каждому из шести символьных битов y0-y5, представляющих один символ 64QAM, были предложены многими компаниями.

Поз. B на фиг. 22, поз. C на фиг. 22 и поз. D на фиг. 22 соответственно показывают первый способ замены, второй способ замены и третий способ замены.

В поз. B на фиг. 22 - поз. D на фиг. 22 (аналогичным образом даже на фиг. 23, который будет описан позже), линия, соединяющая бит bi и yi означает выделение кодового бита bi символьному биту yi символа (заменяя его в позиции символьного бита yi).

В качестве первого способа замены (поз. B на фиг. 22) предлагается выбрать любой из трех типов способов замены, и в качестве второго способа замены (поз. C на фиг. 22) предлагается выбрать любой из двух типов способов замены.

В качестве третьего способа замены (поз. D на фиг. 22) предлагается выбрать и использовать надлежащим образом шесть типов способов замены.

Фиг. 23 иллюстрирует пример конфигурации демультиплексора 25, в котором схемой модуляции является 64QAM, которая отображает символ в любую из 64 сигнальных точек (поэтому число m битов кодового бита LDPC-кода, который отображается в один символ, равно шести битам также, как и на фиг. 22), и множитель b равен 2, и четвертый способ замены.

Когда множитель b равен 2, память 31 включает в себя объем памяти N/(6×2)×(6×2) битов в направлении столбца × направлении строки, и выполнена с 12 (=6×2) столбцами.

Поз. А на фиг. 23 иллюстрирует порядок записи LDPC-кода в память 31.

В демультиплексоре 25, как показано на фиг. 22, запись кодового бита LDPC-кода в направлении сверху вниз столбцов (в направлении столбца), конфигурирующих память 31, выполняется в направлении столбца слева направо.

Затем, если запись кодового бита закончилась внизу крайнего правого столбца (при окончании записи одного кодового слова), кодовые биты считываются из первого столбца всех столбцов, конфигурирующих память 31, в направлении строки в блоке из 12 битов (mb битов) и подаются в блок 32 замены.

Блок 32 замены выполняет процесс замены, предназначенный для замены позиций кодовых битов из 12 битов из памяти 31 с использованием четвертого способа замены, и выводит 12 результирующих битов в виде 12 битов представляющих собой два символа (b символов) 64QAM, другими словами, шесть символьных битов y0, y1, y2, y3, y4 и y5, которые представляют один символ 64QAM, и шесть символьных битов y0, y1, y2, y3, y4 и y5, которые представляют собой один следующий символ.

В данном случае, поз. B на фиг. 23 иллюстрирует четвертый способ замены процесса замены, выполняемого блоком 32 замены (поз. A на фиг. 23).

В дополнение к этому, когда множитель b равен 2 (то же самое относится к случаю, когда он равен 3 или более), в процессе замены кодовые биты mb битов выделяются символьным битам mb битов последующих символов b. В дальнейшем для удобства объяснения, в том числе как показано на фиг. 23, (i+1)-ый бит из старшего значащего бита символьного бита mb битов последующих символов b будет представлен в виде бита (символьного бита) yi.

То, что способ замены кодовых битов является подходящим, другими словами, то, что дополнительно повышает частоту появления ошибок в канале связи AWGN и т.п., варьируется в зависимости от кодовой скорости и длины кода LDPC-кода, схемы модуляции и т.п.

Перемежение битов четности

Далее, со ссылкой на фиг. 24 - фиг. 26, будет описано перемежение битов четности, выполняемое перемежителем 23 битов четности на фиг. 9.

Фиг. 24 иллюстрирует график Таннера (часть его) матрицы контроля четности LDPC-кода.

Как показано на фиг. 24, если множество (2 или т.п.) переменных узлов (кодовых битов, соответствующих им), соединенных с проверочным узлом, одновременно становятся ошибочными узлами, такими как блок стирания, проверочный узел возвращает сообщение, в котором вероятность наличия значения 0 и вероятность наличия значения 1 равны, во все переменные узлы, соединенные с проверочным узлом. Поэтому, если множество переменных узлов, соединенных с одним и тем же проверочным узлом, одновременно становятся устройством стираня, производительность декодирования ухудшается.

В данном случае, LDPC-код, который определен в стандарте DVB-S.2 и выводится с помощью LDPC-кодера 115 (фиг. 8), представляет собой IRA код, и матрица HT четности матрицы H контроля четности имеет ступенчатую структуру, как показано на фиг. 11.

На фиг. 25 показана схема, иллюстрирующая матрицу HT четности, имеющая ступенчатую структуру, и график Таннера, соответствующий матрице HT четности.

Другими словами, поз. A на фиг. 25 показывает матрицу HT четности, имеющую ступенчатую структуру, и поз. B на фиг. 25 показывает график Таннера, соответствующий матрице HT четности (поз. A на фиг. 25).

В матрице HT четности, имеющей ступенчатую структуру, элементы 1 находятся рядом в каждой строке (за исключением первой строки). Поэтому, на графике Таннера матрицы HT четности два соседних переменных узла, соответствующих столбцам двух соседних элементов, значения которых в матрице HT четности равны 1, соединены с тем же самым проверочным узлом.

Поэтому, если биты четности, соответствующие двум соседним переменным узлам, описанным выше, одновременно становятся ошибочными битами из-за пакетной ошибки или стирания, проверочный узел, соединенный с двумя переменными узлами (с переменными узлами для получения сообщения с использованием бита четности), соответствующими двум битам четности, которые становятся ошибочными битами, возвращает сообщение, в котором вероятность наличия значения 0 и вероятность наличия значения 1 равны, в переменный узел, соединенный с проверочным узлом таким образом, что производительность декодирования ухудшается. Затем, если длина пакета (число битов из битов четности, которые становятся ошибочными битами один за другим) увеличивается, то число проверочных узлов, возвращающих сообщение, показывающее равные вероятности, увеличивается, и производительность декодирования дополнительно ухудшается.

Таким образом, для того чтобы предотвратить снижение производительности декодирования, описанной выше, перемежитель 23 битов четности (фиг. 9) выполняет перемежение битов четности LDPC-кода, подаваемого из LDPC-кодера 115 в позицию другого бита четности.

На фиг. 26 показана схема, иллюстрирующая матрицу HT четности матрицы H контроля четности, соответствующую LDPC-коду, после перемежения битов четности, выполняемого перемежителем 23 битов четности (фиг. 9).

В данном случае, информационная матрица На матрицы H контроля четности, соответствующая LDPC-коду, которая выводится кодером 115 LDPC и определена в стандарте DVB-S.2, имеет циклическую структуру.

Циклическая структура относится к структуре, в которой определенный столбец получается путем циклического сдвига другого столбца, и включает в себя, например, структуру, в которой для каждых P столбцов позиция 1 в каждой строке P столбца представляет собой позицию, полученную в результате циклического сдвига первого столбца P столбца на значение, пропорциональное значению q, полученному путем деления длины M битов четности в направлении столбца. В дальнейшем, в случае необходимости, P столбец в циклической структуре упоминается как число столбцов блока циклической структуры.

Пример LDPC-кода, который определен в стандарте DVB-S.2, включает в себя два типа LDPC-кодов, в которых длина N кода равна 64800 битам и 16200 битам, как описано на фиг. 12 и фиг. 13, для обоих двух типов LDPC-кодов число P столбцов блока циклической структуры определено как 360, которое является одним из делителей за исключением 1 и M среди делителей, имеющих длину M битов четности.

Кроме того, длина M четности равна значению, отличному от простого числа, представленного с помощью уравнения M=q×P=q×360, при использовании значения q, которое изменяется в зависимости от кодовой скорости. Поэтому, значение q, аналогичное числу P столбцов блока циклической структуры, представляет собой также другой один из делителей, за исключением 1 и M среди делителей с длиной M четности, и получается путем деления длины M четности на число P столбцов блока циклической структуры (произведение P и q, которые являются делителями длины M четности, представляют собой длину M битов четности).

Как описано выше, когда информационная длина равна K, и x представляет собой целое число, равное 0, или больше или меньше, чем P, если у представляет собой целое число, равное 0, или больше или меньше, чем q, перемежитель 23 битов четности выполняет перемежение (K+qx+y+1)-го кодового бита среди кодовых битов LDPC-кода N битов в позиции (K+Py+x+1)-го кодового бита, в качестве перемежения битов четности.

Поскольку как (K+qx+y+1)-ый кодовый бит, так и (K+Py+x+1)-ый кодовый бит представляют собой (K+1)-ый и последующие кодовые биты в соответствии с перемежением битов четности, позиция бита четности LDPC-кода смещается.

Согласно такому перемежению битов четности переменные узлы (бит четности, соответствующий им), соединенные с одним и тем же проверочным узлом, разделяются на число P столбцов блока циклической структуры, другими словами, в данном случае, 360 бит, поэтому, когда длина пакета составляет менее чем 360 битов, можно избежать состояния, в котором множество переменных узлов, соединенных с одним и тем же проверочным узлом, одновременно становятся ошибочными узлами, и тем самым повышая устойчивость к пакетной ошибке.

В дополнение к этому, LDPC-код после перемежения битов четности, предназначенного для перемежения (K+qx+y+1)-го кодового бита позиции (K+Py+x+1)-го кодового бита, совпадает с LDPC-кодом матрицы контроля четности (которая в дальнейшем упоминается как матрица контроля четности преобразования), полученной с помощью перестановки столбцов, предназначенной для замены (K+qx+y+1)-ого столбца исходной матрицы H контроля четности на (K+Py+x+1)-ый столбец.

Кроме того, квазициклическая структура с P столбцами (на фиг. 26 360 столбцов) показана в виде блока в матрице четности матрицы контроля четности преобразования, как показано на фиг. 26.

В данном случае квазициклическая структура означает, что структура, в которой некоторые части, за исключением других частей, имеет циклическую структуру. В матрице контроля четности преобразования, полученной путем выполнения перестановки столбцов, соответствующей перемежению битов четности, в матрице контроля четности LDPC-кода, который определен в стандарте DVB-S.2, отсутствует элемент 1 (становится элементом 0) на участке 360 строк × 360 столбцов на участке правого угла (сдвиговая матрица, которая будет описана позже), и с этого момента матрица контроля четности не имеет (законченную) циклическую структуру, а имеет так называемую квазициклическую структуру.

В дополнение к этому, матрица контроля четности преобразования, показанная на фиг. 26, представляет собой матрицу, полученную путем выполнения перестановки строк таким образом, чтобы сконфигурировать конфигурирующую матрицу, которая будет описана позже, а также перестановки столбцов, соответствующей перемежению битов четности, исходной матрицы H контроля четности.

Перемежение со скручиванием столбцов

Далее, со ссылкой на фиг. 27 - фиг. 30, будет описано перемежение со скручиванием столбцов в качестве процесса перегруппировки, выполняемого перемежителем 24 со скручиванием столбцов (фиг. 9).

Передающее устройство 11 (фиг. 8) передает один бит или более кодовых битов LDPC-кода в качестве одного символа. Другими словами, например, когда два бита кодового бита представляют собой один символ, например, QPSK используется в качестве схемы модуляции, и когда четыре бита кодового бита представляют собой один символ, например, 16APSK или 16QAM используется в качестве схемы модуляции.

Когда два или более битов кодового бита передаются в виде одного символа, если в любом символе имеет место стирание или т.п., все кодовые биты символа стираются.

Поэтому, необходимо избежать соединений переменного узла, соответствующего кодовым битам одного символа, с тем же самым проверочным узлом, чтобы уменьшить вероятность того, что множество переменных узлов, соединенных с одним и тем же проверочным узлом (кодовый бит, соответствующий ему), стираются в одно и то же время для того, чтобы повысить производительность декодирования.

Между тем, как описано выше, в матрице H контроля четности LDPC-кода, которая выводится LDPC-кодером 115 и определена в стандарте DVB-S.2, информационная матрица HA имеет циклическую структуру, и матрица HT четности имеет ступенчатую структуру. Затем, как показано на фиг. 26, в матрице контроля четности преобразования, которая представляет собой матрицу контроля четности LDPC-кода после перемежения битов четности, циклическая структура (а именно, как описано выше, квазициклическая структура) показана в матрице четности.

Фиг. 27 иллюстрирует матрицу контроля четности преобразования.

Другими словами, фиг. 27 иллюстрирует матрицу контроля четности преобразования матрицы H контроля четности LDPC-кода, в которой длина N кода равна 64800 битам, и кодовая скорость (r) равна 3/4.

В поз. A на фиг. 27, в матрице контроля четности преобразования, позиции элементов, значения которых установлены на 1, представлены точками (⋅).

Поз. B на фиг. 27 иллюстрирует процесс, выполняемый демультиплексором 25 (фиг. 9) в отношении LDPC-кода матрицы контроля четности преобразования (поз. A фиг. 27), другими словами, LDPC-кода после перемежения битов четности в качестве цели.

В поз. B на фиг. 27 в случае схемы модуляции, такой как схема отображения символа в 16 сигнальных точек, например 16APSK или 16QAM, кодовые биты LDPC-кода после перемежения битов четности записываются в четыре столбца, конфигурирующие память 31 демультиплексора 25 в направлении столбца.

Кодовые биты, которые записаны в четырех столбцах, конфигурирующих память 31 в направлении столбца, считываются в четырех битовых блоках в направлении строки с тем, чтобы представлять собой один символ.

В этом случае, кодовые биты B0, B1, B2 и B3 четырех битов в качестве одного символа могут представлять собой кодовые биты, соответствующие 1 в любой одной строке матрицы контроля четности преобразования (поз. A на фиг. 27), и в этом случае переменные узлы, соответственно, соответствующие кодовым битам B0, B1, B2 и B3, соединены с одним и тем же проверочным узлом.

Поэтому, когда кодовые биты B0, B1, B2 и B3 четырех битов одного символа представляют собой кодовые биты, соответствующие 1 в любой одной строке матрицы контроля четности преобразования, если в символе происходит стирание, нельзя получить подходящее сообщение из одного и того же проверочного узла, соединенного с переменными узлами, соответственно, соответствующих кодовым битам B0, B1, B2 и B3, и, таким образом производительность декодирования ухудшается.

Даже при кодовой скорости, отличной от кодовой скорости 3/4, аналогичным образом, множество кодовых битов, соответствующих множеству переменных узлов, соединенных с одним и тем же узлом, может представлять собой один символ 16APSK или 16QAM.

Таким образом, перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов, предназначенное для перемежения кодового бита LDPC-кода после перемежения битов четности из перемежителя 23 битов четности таким образом, что множество кодовых битов, соответствующих 1 в любой одной строке матрицы контроля четности преобразования, не включено в один символ.

На фиг. 28 показана схема, изображающая перемежение со скручиванием столбцов.

Другими словами, фиг. 28 иллюстрирует память 31 (фиг. 22 и фиг. 23) демультиплексора 25.

Как показано на фиг. 22, память 31 имеет объем памяти для хранения mb битов в направлении столбца (по вертикали) и N/(mb) битов в направлении строки (по горизонтали) и выполнена с mb столбцами. Затем перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов путем управления позиции начала записи для памяти 31 при записи кодового бита LDPC-кода в направлении столбца и при считывании кодового бита в направлении строки.

Другими словами, перемежитель 24 со скручиванием столбцов подходящим образом изменяет позицию начала записи, в которой начинается запись кодового бита, для каждого из множества столбцов, таким образом, что множество кодовых битов, конфигурирующих один символ, которые считываются в направлении строки, не становятся кодовыми битами, соответствующими 1, расположенными в определенной одной строке матрицы контроля четности преобразования (кодовые биты LDPC-кода перегруппировываются таким образом, что множество кодовых битов, соответствующих 1, расположенных в определенной одной строке матрицы контроля четности, не включаются в один и тот же символ).

В данном случае, фиг. 28 иллюстрирует пример конфигурации памяти 31, когда схемой модуляции является 16APSK или 16QAM, и множитель b, описанный на фиг. 22, равен 1. Поэтому, числом m битов кодового бита LDPC-кода, сконфигурированного в виде одного символа, равно четырем битам, и память 31 сконфигурирована с четырьмя (=mb) столбцами.

Перемежитель 24 со скручиванием столбцов (то есть демультиплексор 25 на фиг. 22) выполняет запись кодового бита LDPC-кода в направлении сверху вниз четырех столбцов (в направлении столбца), конфигурирующего память 31 в направлении столбца в направлении слева направо.

Затем, если запись кодового бита заканчивается в крайнем правом столбце, перемежитель 24 со скручиванием столбцов считывает кодовый бит из первой строки всех столбцов, конфигурирующих память 31, в направлении строки, в блоке из четырех битов (mb битов), и выводит кодовый бит в качестве LDPC-кода после перемежения со скручиванием столбцов в блок 32 замены (фиг. 22 и фиг. 23) демультиплексора 25.

Однако, если предполагается, что адрес первой (верхней) позиции каждого столбца равен 0, и адрес каждой позиции в направлении столбца представлен целыми числами в возрастающем порядке, в перемежителе 24 со скручиванием столбцов, предполагается, что позиция начала записи крайнего левого столбца представляет собой позицию адреса 0, позиция начала записи второго (слева) столбца представляет собой позицию адреса 2, позиция начала записи третьего столбца представляет собой позицию адреса 4, и позиция начала записи четвертого столбца представляет собой позицию адреса 7.

В дополнение к этому, что касается столбцов, чьи позиции начала записи отличаются от позиции адреса 0, то после того, как кодовые биты записались в крайней нижней позиции, кодовые биты перемещаются в верхнюю позицию (в позицию адреса 0) и записываются вплоть до позиции, расположенной непосредственно перед позицией начала записи. После этого выполняется запись в следующем (в правом) столбце.

Путем выполнения перемежения со скручиванием столбцов, описанным выше, можно избежать формирования множества кодовых битов, соответствующих множеству переменных узлов, соединенных с одним и тем же проверочным узлом, в виде одного символа 16APSK или 16QAM (включения в один символ), для LDPC-кода, который определен в стандарте DVB-T.2, в результате можно повысить производительность декодирования в канале связи со стиранием.

Фиг. 29 иллюстрирует требуемое число столбцов памяти 31 для перемежения со скручиванием столбцов и адрес позиции начала записи для каждой схемы модуляции для соответствующих LDPC-кодов с длиной N кодов, равной 64800, и 11 кодовыми скоростями, которые определены в стандарте DVB-T.2.

Если множитель b равен 1, и число m битов одного символа равно двум битам при использовании, например, QPSK в качестве схемы модуляции согласно фиг. 29, память 31 имеет два столбца, хранящих 2×1 (=mb) битов в направлении строки, и хранит 64800/(2×1) битов в направлении столбца.

Затем среди двух столбцов памяти 31 предполагается, что позиция начала записи первого столбца представляет собой позицию адреса 0, и позиция начала записи второго столбца представляет собой позицию адреса 2.

В дополнение к этому, например, когда любой один из первого-третьего способа замены (фиг. 22) приняты в качестве способа замены для процесса замены демультиплексора 25 (фиг. 9), множитель b равен 1.

Если множитель b равен 2, и число m битов одного символа равно двум битам при использовании, например, QPSK в качестве схемы модуляции согласно фиг. 29, память 31 имеет четыре столбца, хранящих 2×2 битов в направлении строки, и хранит 64800/(2×2) битов в направлении столбца.

Затем среди четырех столбцов памяти 31 предполагается, что позиция начала записи первого столбца представляет собой позицию адреса 0, позиция начала записи второго столбца представляет собой позицию адреса 2, позиция начала записи третьего столбца представляет собой позицию адреса 4 и позиция начала записи четвертого столбца представляет собой позицию адреса 7.

В дополнение к этому, например, когда четвертый способ замены (фиг. 23) принят в качестве способа замены для процесса замены демультиплексора 25 (фиг. 9), множитель b равен 2.

Если множитель b равен 1, и число m бита одного символа равно четырем битам при использовании, например, 16QAM в качестве схемы модуляции согласно фиг. 29, память 31 имеет четыре столбца, хранящих 4×1 битов в направлении строки, и хранит 64800/(4×1) битов в направлении столбца.

Затем среди четырех столбцов памяти 31 предполагается, что позиция начала записи первого столбца представляет собой позицию адреса 0, позиция начала записи второго столбца представляет собой позицию адреса 2, позиция начала записи третьего столбца представляет собой позицию адреса 4 и позиция начала записи четвертого столбца представляет собой позицию адреса 7.

Если множитель b равен 2, и число m битов одного символа равно четырем битам при использовании, например, 16QAM в качестве схемы модуляции согласно фиг. 29, память 31 имеет восемь столбцов, хранящих 4×2 битов в направлении строки, и хранит 64800/(4×2) битов в направлении столбца.

Затем среди восьми столбцов памяти 31 предполагается, что позиция начала записи первого столбца представляет собой позицию адреса 0, позиция начала записи второго столбца представляет собой позицию адреса 0, позиция начала записи третьего столбца представляет собой позицию адреса 2, позиция начала записи четвертого столбца представляет собой позицию адреса 4, позиция начала записи пятого столбца представляет собой позицию адреса 4, позиция начала записи шестого столбца представляет собой позицию адреса 5, позиция начала записи седьмого столбца представляет собой позицию адреса 7, и позиция начала записи восьмого столбца представляет собой позицию адреса 7.

Если множитель b равен 1, и число m битов одного символа равно шести битам при использовании, например, 64QAM в качестве схемы модуляции согласно фиг. 29, память 31 имеет шесть столбцов, хранящих 6×1 битов в направлении строки, и хранит 64800/(6×1) битов в направлении столбца.

Затем среди шести столбцов памяти 31 предполагается, что позиция начала записи первого столбца представляет собой позицию адреса 0, позиция начала записи второго столбца представляет собой позицию адреса 2, позиция начала записи третьего столбца представляет собой позицию адреса 5, позиция начала записи четвертого столбца представляет собой позицию адреса 9, позиция начала записи пятого столбца представляет собой позицию адреса 10 и позиция начала записи шестого столбца представляет собой позицию адреса 13.

Если множитель b равен 2, и число m битов одного символа равно шести битам при использовании, например, 64QAM в качестве схемы модуляции в соответствии с фиг. 29, память 31 имеет 12 столбцов, хранящих 6×2 битов в направлении строки, и хранит 64800/(6×2) битов в направлении столбца.