Предлагаемое устройство относится к области радиотехники и может найти широкое применение при построении систем радиосвязи.

Известно устройство декодирования турбокодов, описанное в [1], в котором для обнаружения ошибок совместно с турбокодами используются блоковые коды.

Известно также устройство декодирования турбокодов, описанное в [2], в котором сформированные пакеты кодируются циклическим кодом (CRC кодом), затем кодируются турбокодом и передаются получателю через канал радиосвязи.

Недостатком данных устройств декодирования является то, что блоковые и циклические коды, используемые совместно с турбокодами, вносят избыточность, чем снижают пропускную способность канала радиосвязи.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство, представленное на рис.12 в [3].

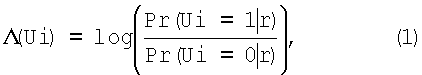

Функциональная схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

1 - турбодекодер;

1.1 - первый декодер;

1.2 - второй декодер;

1.3 - первый деперемежитель;

1.4 - второй деперемежитель;

1.5 - перемежитель;

1.6 - формирователь жестких решений.

Устройство-прототип представляет собой турбодекодер 1, содержащий последовательно соединенные первый декодер 1.1, перемежитель 1.5, второй декодер 1.2, второй деперемежитель 1.4 и формирователь жестких решений 1.6, выход которого является выходом устройства. Второй выход второго декодера 1.2 через первый деперемежитель 1.3 соединен со вторым входом первого декодера 1.1, первый вход которого, являющийся входом устройства, соединен со вторым входом второго декодера 1.2.

Устройство-прототип работает следующим образом.

Вначале на первый декодер 1.1 поступает кодированный пакет данных (от демодулятора), содержащий информационные и проверочные символы.

Первый декодер 1.1, используя полученные искаженные в канале информационные и проверочные символы, выдает мягкое решение для информационных символов пакета данных (см. стр.3-15 в [3]).

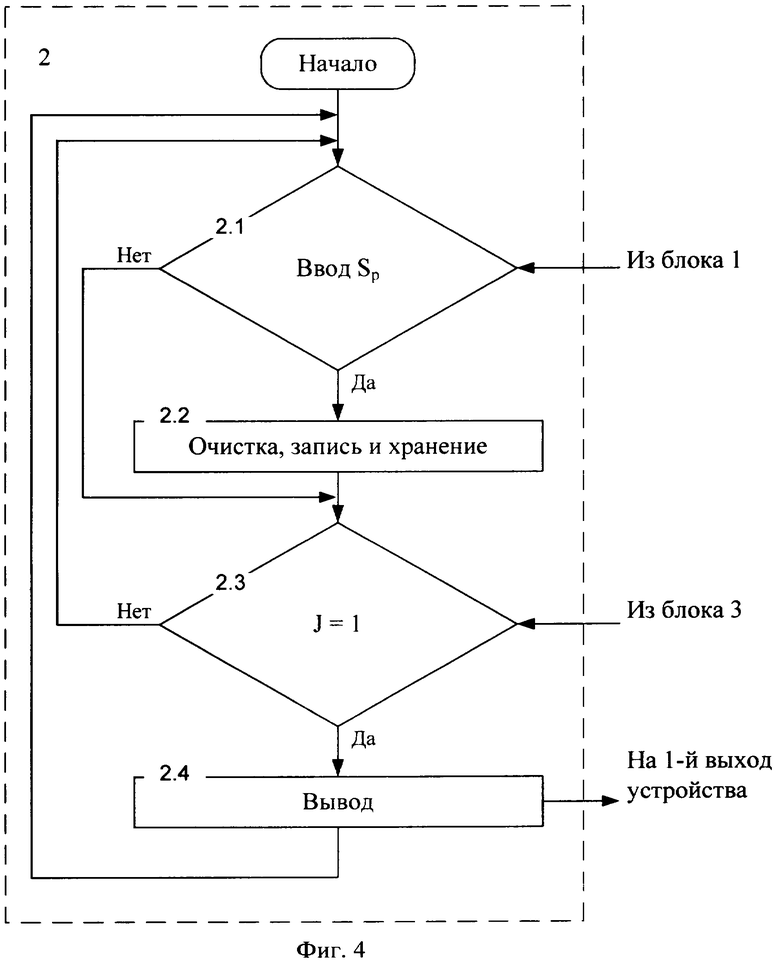

Мягкое решение представляет собой оценку логарифмического отношения правдоподобия (Log likehood ratio) (см. стр.201-230 в [6]):

где Λ(Ui) - логарифмическое отношение правдоподобия;

Ui - значение передаваемого символа исходного пакета;

r - принятая последовательность.

Полученное решение поступает на перемежитель 1.5 и после перемежения подается в качестве априорной информации на первый вход второго декодера 1.2.

Второй декодер 1.2, используя полученную априорную информацию, декодирует принятый пакет данных, по результатам декодирования выдает улучшенное мягкое решение для информационных символов, которое затем поступает на первый деперемежитель 1.3 и на второй деперемежитель 1.4, с выхода которого подается на формирователь жестких решений 1.6.

С выхода первого деперемежителя 1.3 мягкие решения поступают на второй вход первого декодера 1.1, замыкая тем самым итеративную обратную связь.

Подобную итерацию можно повторять многократно с целью улучшения результатов декодирования на каждой итерации.

Выходные биты Ui согласно формуле (1) формируются по правилу: если Λ(Ui)>0, то Ui=1, в противном случае Ui=0.

Компоненты элементарных первого 1.1 и второго 1.2 декодеров обычно работают по алгоритму максимальной апостериорной вероятности MAP (maximum aposteriory probability) или алгоритму Витерби с мягким выходом SOVA (Soft Output Viterbi Algorithm). Также могут использоваться любые декодеры сверточного кода типа SISO (soft input - soft output), т.е. мягкий вход - мягкий выход (см. стр.201-230 в [6]).

Формирователь жестких решений 1.6 осуществляет преобразование декодированного пакета, представленного в виде мягких решений, к виду жестких решений. Таким образом, с выхода блока 1.6 декодированный пакет данных подается на выход устройства.

Однако устройство-прототип имеет существенный недостаток, заключающийся в том, что в нем отсутствует контроль правильности принятия пакета данных. Это приводит к тому, что итеративное декодирование будет происходить сколь угодно долго, при этом отсутствует возможность контроля правильности принятия сообщения.

Для устранения указанного недостатка в устройство декодирования турбокодов, содержащее турбодекодер, вход которого является входом устройства, согласно изобретению введены программируемый логический блок, буфер, первый и второй запоминающие блоки, при этом выход турбодекодера соединен с первым, информационным входом буфера и первым входом программируемого логического блока, второй и третий входы которого соединены с выходами первого и второго запоминающих блоков соответственно, первый выход программируемого логического блока соединен со вторым, управляющим входом буфера, выход которого является первым выходом устройства, второй и третий выходы программируемого логического блока являются соответственно вторым и третьим выходами устройства.

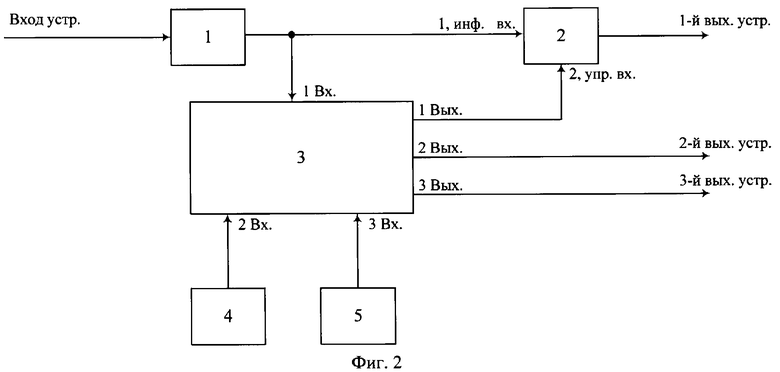

Функциональная схема предлагаемого устройства приведена на фиг.2, где введены следующие обозначения:

1 - турбодекодер;

2 - буфер;

3 - программируемый логический блок;

4 - первый запоминающий блок;

5 - второй запоминающий блок.

Предлагаемое устройство содержит турбодекодер 1, вход которого является входом устройства, а выход турбодекодера 1 соединен с первым, информационным входом буфера 2 и первым входом программируемого логического блока 2, второй и третий входы которого соединены с выходами первого 4 и второго 5 запоминающих блоков соответственно, первый выход программируемого логического блока 3 соединен со вторым, управляющим входом буфера 2, выход которого является первым выходом устройства, второй и третий выходы программируемого логического блока 3 являются соответственно вторым и третьим выходами устройства.

Со входа устройства закодированный пакет данных поступает на турбодекодер 1, где выполняется итеративное декодирование. После каждой итерации декодирования полученный пакет данных с выхода турбодекодера 1 подается на первый, информационный вход буфера 2, где он хранится до тех пор, пока не поступит новый пакет, а также на первый вход программируемого логического блока 3, где принимается решение о правильности принятия этого пакета.

В предлагаемом устройстве для определения правильности принятия пакета данных используется оценка правильности принятия (декодирования) служебной информации, которая входит в состав пакета. Эта служебная информация представляет собой проверяемую последовательность символов  , обозначающих например: адрес отправителя, адрес получателя, длину заголовка, версию протокола и другие заранее известные символы, которые не зависят от пользовательской информации. Значение требуемых для проверки символов служебной информации определяется заранее и сохраняется в первом запоминающем блоке 4 как контрольная последовательность символов

, обозначающих например: адрес отправителя, адрес получателя, длину заголовка, версию протокола и другие заранее известные символы, которые не зависят от пользовательской информации. Значение требуемых для проверки символов служебной информации определяется заранее и сохраняется в первом запоминающем блоке 4 как контрольная последовательность символов  .

.

Поступивший из турбодекодера 1 в программируемый логический блок 3 декодированный пакет данных запоминается в нем в виде последовательности символов Sp. При этом в программируемый логический блок 3 через второй вход из первого запоминающего блока 4 поступает и запоминается контрольная последовательность символов  , а через третий вход из второго запоминающего блока 5 в программируемый логический блок 3 поступает и запоминается максимально допустимое число итераций Imax. Выбор максимально допустимого числа итераций определяется качеством канала, мощностью передатчика и т.п. В результате исследований, приведенных в [3], установлено, что после двенадцати итераций увеличение надежности декодированных битов становится достаточно малым, поэтому более двенадцати итераций декодирования проводить нецелесообразно.

, а через третий вход из второго запоминающего блока 5 в программируемый логический блок 3 поступает и запоминается максимально допустимое число итераций Imax. Выбор максимально допустимого числа итераций определяется качеством канала, мощностью передатчика и т.п. В результате исследований, приведенных в [3], установлено, что после двенадцати итераций увеличение надежности декодированных битов становится достаточно малым, поэтому более двенадцати итераций декодирования проводить нецелесообразно.

В блоке 3 из последовательности символов Sp выделяется проверяемая последовательность символов  и сравнивается с контрольной последовательностью символов

и сравнивается с контрольной последовательностью символов  , подаваемой с блока 4.

, подаваемой с блока 4.

Если проверяемая последовательность символов  совпадает с контрольной последовательностью символов

совпадает с контрольной последовательностью символов  , то принимается решение о том, что пакет данных принят правильно, и на втором выходе программируемого логического блока 3 формируется квитанция «Пакет принят», а на первом выходе формируется управляющий сигнал для буфера 2. По сигналу, выдаваемому с первого выхода программируемого логического блока 3 на второй, управляющий вход буфера 2, производится выдача декодированного пакета данных из буфера 2 на первый выход устройства.

, то принимается решение о том, что пакет данных принят правильно, и на втором выходе программируемого логического блока 3 формируется квитанция «Пакет принят», а на первом выходе формируется управляющий сигнал для буфера 2. По сигналу, выдаваемому с первого выхода программируемого логического блока 3 на второй, управляющий вход буфера 2, производится выдача декодированного пакета данных из буфера 2 на первый выход устройства.

Если проверяемая последовательность символов  не совпадает с контрольной последовательностью символов

не совпадает с контрольной последовательностью символов  , то принимается решение о том, что пакет данных принят с ошибками, и со второго выхода программируемого логического блока 3 на третий выход устройства выдается квитанция «Пакет не принят», после чего производится повторная передача кодированного пакета на вход устройства.

, то принимается решение о том, что пакет данных принят с ошибками, и со второго выхода программируемого логического блока 3 на третий выход устройства выдается квитанция «Пакет не принят», после чего производится повторная передача кодированного пакета на вход устройства.

При поступлении на первый, информационный вход буфера 2 нового пакета новый пакет записывается в буфер 2, при этом буфер 2 очищается от информации предыдущего пакета.

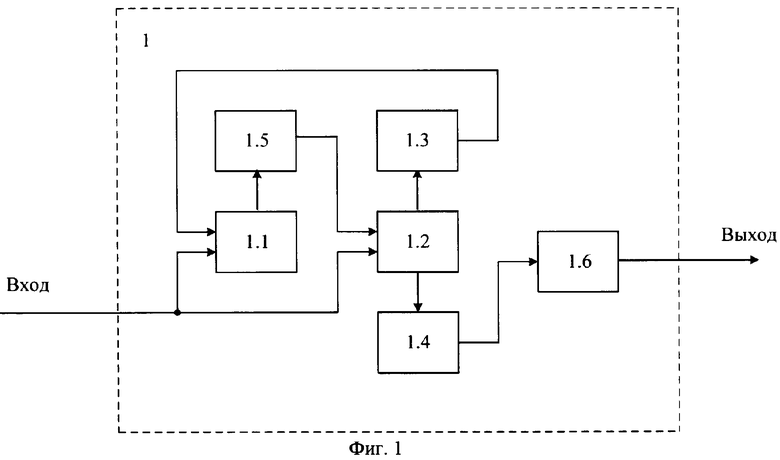

Программируемый логический блок 3 может быть реализован в форме ПЛИС [4], алгоритм функционирования которой представлен на фиг.3.

Работа программируемого логического блока 3 начинается с блока 3.1, где осуществляется обнуление счетчика числа итераций (I=0). В блоке 3.2 происходит ввод и запоминание максимально допустимого числа итераций Imax из блока 5.

В блоке 3.3 происходит ввод и запоминание контрольной последовательности символов  из блока 4, состоящей из требуемых служебных символов.

из блока 4, состоящей из требуемых служебных символов.

В блоке 3.4 происходит ввод и запоминание декодированного пакета данных в виде последовательности символов Sp. В блоке 3.5 происходит выделение из последовательности символов Sp проверяемой последовательности символов  путем выкалывания служебных символов с тех мест, где они должны находиться.

путем выкалывания служебных символов с тех мест, где они должны находиться.

В блоке 3.6 происходит посимвольное сравнение последовательностей  и

и  . Если эти последовательности совпадают, то по линии «Да» происходит переход к блоку 3.10, в котором формируется управляющий сигнал для буфера 2 «Выдать пакет», и далее в блоке 3.11 формируется квитанция «Пакет принят», которая выдается на второй выход устройства, после чего происходит переход в начало алгоритма, к блоку 3.1 и далее по алгоритму.

. Если эти последовательности совпадают, то по линии «Да» происходит переход к блоку 3.10, в котором формируется управляющий сигнал для буфера 2 «Выдать пакет», и далее в блоке 3.11 формируется квитанция «Пакет принят», которая выдается на второй выход устройства, после чего происходит переход в начало алгоритма, к блоку 3.1 и далее по алгоритму.

Если в блоке 3.6 в результате посимвольного сравнения последовательностей  и

и  обнаружилось несовпадение, то происходит переход по линии «Нет» к блоку 3.7, в котором счетчик итераций I увеличивается на единицу. После чего происходит переход блоку 3.8, где производится сравнение выполненного числа итераций I с максимально допустимым Iмах.

обнаружилось несовпадение, то происходит переход по линии «Нет» к блоку 3.7, в котором счетчик итераций I увеличивается на единицу. После чего происходит переход блоку 3.8, где производится сравнение выполненного числа итераций I с максимально допустимым Iмах.

Если число выполненных итераций меньше максимально допустимого, то по линии «Нет» происходит переход к блоку 3.4. Если число выполненных итераций равно максимально допустимому (I=Iмах), то происходит переход по линии «Да» к блоку 3.9, где формируется и выдается квитанция «Пакет не принят», после чего происходит переход в начало алгоритма к блоку 3.1.

Таким образом, итеративное декодирование полученного пакета данных выполняется до тех пор, пока пакет данных не будет принят или пока не будут проделаны все итерации.

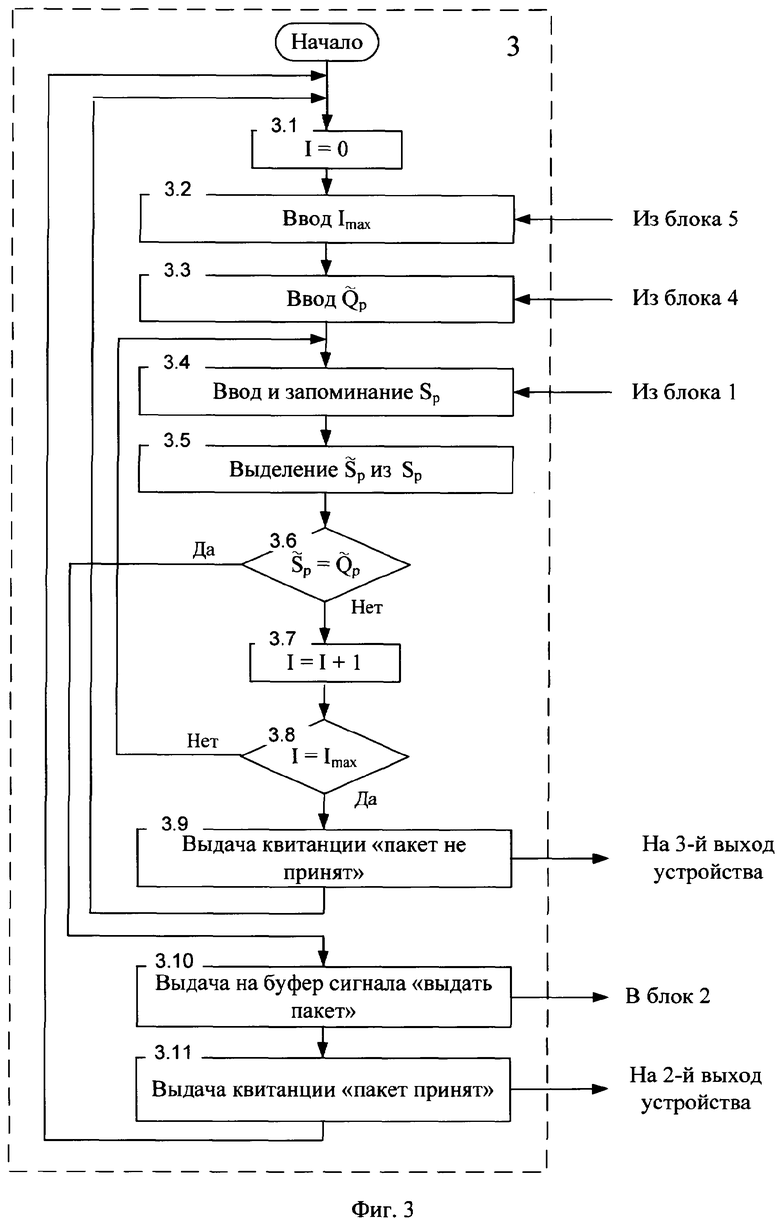

Буфер 2 может быть реализован в форме ПЛИС [4], алгоритм функционирования которой представлен на фиг.4.

Работа буфера 2 начинается с блока 2.1, в котором происходит проверка, приходит ли декодированный пакет из турбодекодера 1 на первый, информационный вход буфера 2 в виде последовательности символов Sp. Если пакет приходит - «Ввод Sp=1», то происходит переход по линии «Да» к блоку 2.2, в котором осуществляется очистка буфера от предыдущего пакета, а затем запись в буфер и сохранение в буфере нового декодированного пакета. Затем происходит переход к блоку 2.3.

Если в буфер 2 не поступает декодированный пакет, то условие «Ввод Sp=1» не выполняется и происходит переход по линии «Нет» к блоку 2.3.

В блоке 2.3 производится проверка наличия управляющего сигнала J на втором, управляющем входе буфера 2. Если выполняется условие «J=1», то управляющий сигнал поступил и происходит переход по линии «Да» к блоку 2.4, а если не выполняется условие «J=1», то сигнал отсутствует и происходит переход по линии «Нет» к блоку 2.1.

Блок 2.4 осуществляет «вывод», то есть выдачу на первый выход устройства хранящегося в буфере декодированного пакета данных.

Первый 4 и второй 5 запоминающие блоки, в которых хранятся заранее определенные соответственно контрольная последовательность символов  и допустимое число итераций Imax, могут быть реализованы на постоянных запоминающих устройствах (ПЗУ) (см. стр.710-719 в [5]).

и допустимое число итераций Imax, могут быть реализованы на постоянных запоминающих устройствах (ПЗУ) (см. стр.710-719 в [5]).

Таким образом, введение в предлагаемом устройстве новых блоков для определения правильности принятия пакета данных позволяет использовать оценку правильности принятия (декодирования) служебной информации, входящей в состав пакета, в результате чего значительно сокращается время декодирования пакетов данных, передаваемых с использованием турбокодов.

Источники информации

1. Патент USA №1003372, H04L 7/02, 1981 г.

2. Патент USA №5983984, H03M 13/00. "Turbo-coding with staged data transmission and processing" Турбокодирование с каскадной передачей и обработкой данных, 1999 г.

3. Панько С.П., Югай В.В. Турбокодирование // Успехи современной радиоэлектроники. - М.: Радиотехника, 2004. - №2. - С.3-15.

4. А.П.Антонов. Язык описания цифровых устройств ALteraHDL. Практический курс. 2-е изд., стереотип. М.: ИП Радиософт, 2002. - 224 с.: ил.

5. Аналоговая и цифровая электроника (Полный курс): Учебник для вузов / Ю.Ф.Опадчий, О.П.Глудкин, А.И.Гуров; Под ред. О.П.Глудкина. - М.: Горячая Линия - Телеком, 2000. 768 с.: ил., с.710-719.

6. Р.Морелос-Сарагоса / Искусство помехоустойчивого кодирования. Методы, алгоритмы, применение. М.: Техносфера, 2005. - 320 с., с.201-230.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТУРБОКОДОВ | 2009 |

|

RU2393633C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА УСЛУГ НА КАНАЛАХ ПЕРЕДАЧИ В ЦИФРОВОЙ СИСТЕМЕ ПЕРЕДАЧИ | 1998 |

|

RU2202153C2 |

| УСТРОЙСТВО И СПОСОБ ГЕНЕРИРОВАНИЯ И ДЕКОДИРОВАНИЯ КОДОВ В СИСТЕМЕ СВЯЗИ | 2002 |

|

RU2236756C2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| УСТРОЙСТВО И СПОСОБ ТУРБОКОДИРОВАНИЯ/ДЕКОДИРОВАНИЯ ДЛЯ ОБРАБОТКИ ДАННЫХ КАДРА В СООТВЕТСТВИИ С КАЧЕСТВОМ ОБСЛУЖИВАНИЯ | 1999 |

|

RU2210185C2 |

| АРХИТЕКТУРА ТУРБОДЕКОДЕРА ДЛЯ ИСПОЛЬЗОВАНИЯ В ПРОГРАММНО-ОПРЕДЕЛЯЕМЫХ РАДИОСИСТЕМАХ | 2006 |

|

RU2383992C2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ | 2007 |

|

RU2343629C1 |

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ ЛИНИЙ СВЯЗИ ПО МОДЕЛИ СИГНАЛА И ПЕРЕПРОГРАММИРУЕМЫМ ЭЛЕКТРИЧЕСКИМ СХЕМАМ | 2005 |

|

RU2317641C2 |

| Способ передачи данных в системе цифровой радиосвязи на основе кодов с низкой плотностью проверок на четность и способ перемежения кодовых символов | 2018 |

|

RU2700398C1 |

| ВЫБОР КОДА ПРЯМОЙ КОРРЕКЦИИ ОШИБОК И КОДОВОЙ СКОРОСТИ НА ОСНОВАНИИ РАЗМЕРА ПАКЕТА | 2008 |

|

RU2427086C2 |

Изобретение относится к области радиотехники и может найти широкое применение при построении систем радиосвязи. Устройство декодирования турбокодов содержит турбодекодер, а также запоминающий блок контрольной последовательности символов (КПС), запоминающий блок допустимого числа итераций (ДЧИ), блок оценки принятой служебной информации (ПСИ) и буфер, выход которого является выходом устройства, при этом выход турбодекодера соединен с информационным входом буфера и первым входом блока оценки ПСИ, а выходы запоминающего блока КПС и запоминающего блока ДЧИ соединены соответственно с соответствующими входами блока оценки ПСИ, выход управляющего сигнала которого соединен с управляющим входом буфера, а два других выхода блока оценки ПСИ являются соответственно выходом сигнала «квитанция пакет принят» и выходом сигнала «квитанция пакет не принят» устройства. Технический результат заключается в сокращении времени декодирования турбокодов за счет контроля правильности принятия пакета данных после каждой итерации декодирования, основанного на оценке правильности декодирования служебной информации, которая входит в состав пакета. 4 ил.

Устройство декодирования турбокодов, содержащее турбодекодер, вход которого является входом устройства, отличающееся тем, что введены запоминающий блок контрольной последовательности символов (КПС), запоминающий блок допустимого числа итераций (ДЧИ), блок оценки принятой служебной информации (ПСИ) и буфер, выход которого является выходом устройства, при этом выход турбодекодера соединен с информационным входом буфера и первым входом блока оценки ПСИ, а выходы запоминающего блока КПС и запоминающего блока ДЧИ соединены соответственно с соответствующими входами блока оценки ПСИ, выход управляющего сигнала которого соединен с управляющим входом буфера, а два других выхода блока оценки ПСИ является соответственно выходом сигнала «квитанция пакет принят» и выходом сигнала «квитанция пакет не принят» устройства.

| АРХИТЕКТУРА ПАМЯТИ ДЛЯ ДЕКОДЕРА МАКСИМАЛЬНОЙ АПОСТЕРИОРНОЙ ВЕРОЯТНОСТИ | 1999 |

|

RU2236085C2 |

| УСТРОЙСТВО И СПОСОБ ГЕНЕРИРОВАНИЯ И ДЕКОДИРОВАНИЯ КОДОВ В СИСТЕМЕ СВЯЗИ | 2002 |

|

RU2236756C2 |

| US 5983384 A, 1999.11.09 | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

2009-10-10—Публикация

2007-05-28—Подача