Изобретение относится к радиотехнике и может найти применение в средствах радиосвязи.

Известны устройства связи с частотным разделением каналов, описанные в учебном пособии «Системы, сети и устройства телекоммуникаций». Учебное пособие. // В.И.Николаев, Ю.Б.Нечаев, В.В.Прилепский, С.С.Гремяченский. Воронежский научно-исследовательский институт связи, 2004, стр.81, 82, недостатком которых является низкая скорость передачи данных, ограниченная временными характеристиками узкополосных фильтров, за счет которых осуществляется формирование и разделение сигналов.

Известны устройства связи с временным разделением каналов, описанные в учебном пособии «Системы, сети и устройства телекоммуникаций». Учебное пособие. // В.И.Николаев, Ю.Б.Нечаев, В.В.Прилепский, С.С.Гремяченский. Воронежский научно-исследовательский институт связи, 2004, стр.82, 83, недостатком которых является невысокая скорость передачи информации, ограниченная полосой пропускания одного информационного канала.

Известны устройства, в которых используются сигналы с расширением спектра за счет применения фазовой манипуляции, описанные в учебном пособии «Основы теории радиотехнических систем». Учебное пособие. // В.И.Борисов, В.М.Зинчук, А.Е.Лимарев, Н.П.Мухин. Под ред. В.И.Борисова. Воронежский научно-исследовательский институт связи, 2004, стр.251-254», недостатком которых является невысокая скорость передачи информации, ограниченная полосой сигнала, которая после соответствующей обработки сужается в коэффициент сжатия раз.

Наиболее близким по технической сущности к предлагаемому устройству является оптимальный максимума правдоподобия детектор, описанный в книге Прокис Джон «Цифровая связь». Пер. с англ. / Под ред. Д.Д.Кловского. - М.: Радио и связь. 2000, стр.141, 208, 219-221, 593-596, принятый за прототип.

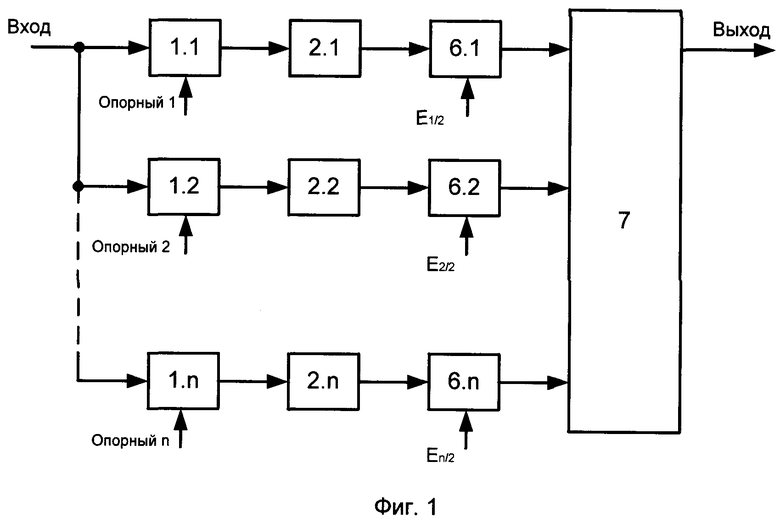

Структурная схема устройства-прототипа приведена на фиг.1, где обозначено:

1.1-1.n - блоки умножения;

2.1-2.n - интеграторы;

6.1-6.n - сумматоры;

7 - блок выбора по максимуму.

Устройство-прототип содержит n линеек, состоящих из соответствующих последовательно соединенных блока умножения 1, интегратора 2 и сумматора 6, причем выход каждого сумматора 6.1-6.n соединен с соответствующим входом блока выбора по максимуму 7, выход которого является выходом устройства. Кроме того, первые входы блоков умножения 1.1-1n объединены и являются входом устройства, вторые входы этих блоков являются входами для соответствующих опорных напряжений Sоп.1-Sоп.n. Вторые входы сумматоров 6.1-6.n являются входами для соответствующих отрицательных пороговых напряжений Е1/2-Е1/n.

Устройство-прототип работает следующим образом.

На вход устройства поступает аддитивная смесь сигнала и помехи

где Us - сигнал,

Up - помеха.

После умножения на соответствующие опорные сигналы Sоп.i в блоках умножения 1.1-1.n и интегрирования интеграторами 2.1-2.n на выходах интеграторов 2.1-2.n образуется соответствующая аддитивная смесь сигнала и помехи - результат преобразования сигнала и помехи, т.е. умножения на опорный сигнал и интегрирования (корреляционные метрики):

где Kis, Кip - коэффициенты преобразования сигнала и помехи соответственно, зависящие от вида используемой системы ортогональных функций.

В блоке выбора по максимуму 7 выбирается сигнал, соответствующий наибольшей корреляционной метрике.

Недостатком прототипа является низкая эффективность приема многочастотного сигнала.

Для устранения указанного недостатка в приемное устройство, содержащее n параллельных линеек, каждая из которых состоит из соответствующих последовательно соединенных блока умножения и интегратора, при этом первые входы n блоков умножения объединены и являются входом устройства, вторые входы блоков умножения являются входами для соответствующих опорных напряжений, согласно изобретению введены первый и второй вычислители, а также n блоков сравнения с порогом, выход каждого из которых является соответствующим выходом устройства, при этом n выходов первого вычислителя соединены с соответствующими входами второго вычислителя и вторыми входами соответствующих блоков сравнения с порогом, а первые входы каждого из них подсоединены к выходу второго вычислителя, кроме того, выход каждого из n интеграторов соединен с соответствующим входом первого вычислителя.

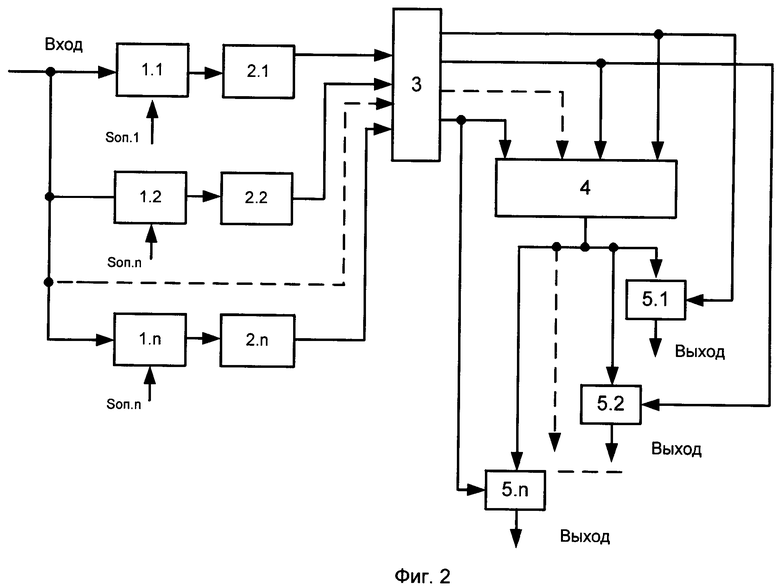

Структурная схема заявляемого устройства приведена на фиг.2, где обозначено:

1.1-1.n - блоки умножения;

2.1-2.n - интеграторы;

3, 4 - первый и второй вычислители;

5.1-5.n - блоки сравнения с порогом.

Предлагаемое устройство содержит n параллельных линеек (каналов), каждая из которых состоит из соответствующих последовательно соединенных блока умножения 1 и интегратора 2, причем выход каждого интегратора 2.1-2.n соединен с соответствующим входом первого вычислителя 3, n выходов которого соединены с соответствующими n входами второго вычислителя 4 и вторыми входами соответствующих блоков сравнения с порогом 5.1-5.n, первые входы которых подсоединены к выходу второго вычислителя 4.

Выходы блоков сравнения с порогом 5.1-5.n являются выходами устройства. При этом первые входы блоков умножения 1.1-1.n объединены и являются входом устройства, вторые входы этих блоков являются входами для соответствующих опорных напряжений Sоп.1-Sоп.n.

В качестве первого 3 и второго 4 вычислителей может быть использован процессор или программируемая логическая интегральная схема ПЛИС. Количество соединений между первым 3 и вторым 4 вычислителями определяется типами используемых процессоров или ПЛИС.

Предлагаемое устройство работает следующим образом.

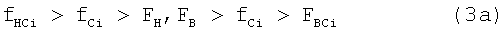

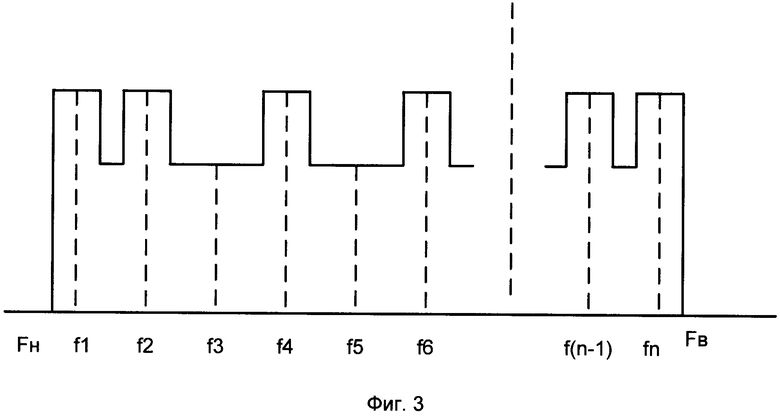

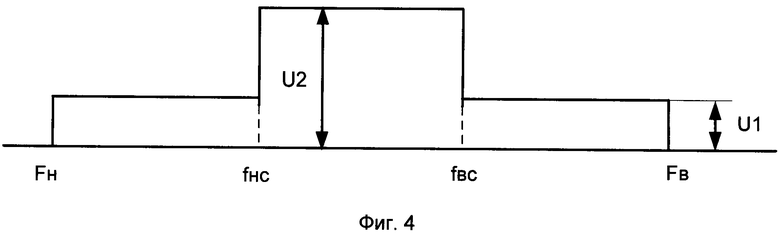

В передатчике радиостанции многочастотный сигнал (с неравномерной амплитудно-частотной характеристикой (АЧХ)) формируется в виде суммы п сигналов следующего вида (фиг.3, 4)

при

при

при

при

если сигнал передается и

при

при

если сигнал не передается,

где Fв, Fн - верхняя и нижняя частоты многочастотного сигнала соответственно,

fсi - частота спектра сигнала,

fвсi, fнсi - верхняя и нижняя частоты части любого сигнала, за счет использования которой передается информация,

i - номер сигнала с центральной частотой части спектра сигнала fцi, за счет использования которой передается информация.

Значение центральной частоты части спектра, в которой передается информация, определяется следующим образом:

где fс, F3 - ширина полосы сигнала и ширина полосы защитного частотного интервала соответственно.

Защитный частотный интервал используется, поскольку на практике форма спектра сигнала отличается от прямоугольной.

Значения центральной частоты спектров сигналов могут быть записаны также в следующем виде:

Коэффициент преобразования (к) записывается в виде:

В данном случае в качестве метода модуляции используется частотная манипуляция, т.е.

наличие сигнала на f1 (Uсi=U2) - передается 1,

наличие сигнала на f2 (Uсi=U1) - передается 0.

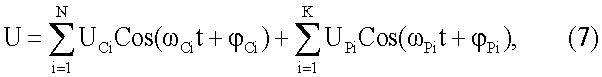

На вход устройства поступает аддитивная смесь сигнала и помехи:

где Uci, Upi, ωci, ωpi, φci, φp - амплитуда, частота и фаза частотных составляющих сигнала и помехи соответственно;

N - число несущих (центральных) частот;

K - число частотных составляющих помехи.

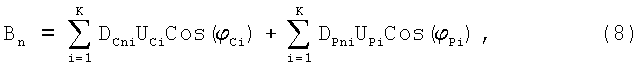

После умножения на соответствующие опорные сигналы и интегрирования на выходе n-го канала аддитивная смесь сигнала и помехи может быть записана следующим образом:

где Dcni, Dpni - коэффициенты преобразования i-й составляющей сигнала и помехи в n-ом канале (линейке) соответственно.

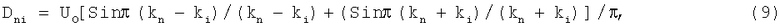

Произведя вычисления получим, что для i≠k

где Uо - амплитуда опорного напряжения.

Для i=n

Причем коэффициенты Dni одинаковы для частотной составляющей сигнала и составляющей помехи на той же частоте.

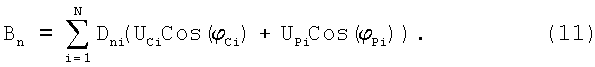

Поскольку коэффициенты Dni одинаковы для частотной составляющей сигнала и составляющей помехи на той же частоте, система линейных уравнений (8) может быть записана следующим образом

Система уравнений (11) является системой n линейных уравнений с n неизвестными. Неизвестными здесь являются сумма произведения амплитуды сигнала на косинус φci и помехи - на косинус φpi составляющих сигнала и составляющих помехи одной и той же частоты

Значения неизвестных рассчитываются в первом вычислителе 3. Расчет значений неизвестных осуществляется любым известным методом решения систем линейных уравнений.

Во второй вычислитель 4 поступают рассчитанные в первом вычислителе 3 суммы произведения амплитуды сигнала на косинус φci и помехи - на косинус φpi составляющих сигнала и составляющих помехи одной и той же частоты.

Во втором вычислителе 4 рассчитываются значения пороговых напряжений для сигналов.

Расчет значения порогового напряжения осуществляется следующим образом.

Среди рассчитанных значений суммы произведения амплитуды сигнала на косинус φci и помехи - на косинус φpi отыскиваются максимальное и минимальное значения этих суммарных сигналов

В качестве порогового напряжения используется среднее значение максимальной и минимальной амплитуд суммарных сигналов

На первые входы блоков сравнения с порогом 5.1-5.n подаются одинаковые постоянные напряжения с амплитудой Ucp.

Сигнал с неравномерной АЧХ может формироваться за счет применения метода обратного преобразования Фурье (ОбПФ), за счет использования специальных фильтров, имеющих АЧХ необходимой формы.

Заявленное устройство направлено на решение задачи восстановления в цифровом виде значений сумм произведений амплитуд составляющих сигнала на косинус φci и помехи на косинус φpi, для каждой частоты, которые используются при формировании сигнала, причем сигналы в данном случае могут формироваться с использованием произвольной сетки частот, а не только с использованием сетки кратных частот (например, ω, 2ω, 3ω и т.д.), как в случае использования сигналов с ортогональным частотным уплотнением (OFDM).

Повышение эффективности приема многочастотного сигнала в данном случае обеспечивается за счет того, что в цифровом виде восстанавливаются значения сумм произведений амплитуд составляющих сигнала на косинус φci и помехи на косинус φpi для каждой частоты, которые используются при формировании сигнала, которые затем сравнивается с порогом, в отличие от прототипа, в котором с порогом сравнивается сумма корреляционных откликов сигналов, сформированных на всех поднесущих (т.е. умножения на опорный сигнал и интегрирования).

Изобретение относится к радиотехнике и может найти применение в средствах радиосвязи. Технический результат - повышение эффективности приема многочастотного сигнала. Это достигается тем, что в устройство введены первый (3) и второй (4) вычислители, а также n блоков сравнения с порогом (5.1-5.n), выход каждого из которых является соответствующим выходом устройства, при этом n выходов первого вычислителя (3) соединены с соответствующими входами второго вычислителя (4) и вторыми входами соответствующих блоков сравнения с порогом (5.1-5.n), а первые входы каждого из них подсоединены к выходу второго вычислителя (4), кроме того, выход каждого из n интеграторов (2.1-2.n) соединен с соответствующим входом первого вычислителя (3). 4 з.п. ф-лы, 4 ил.

1. Приемное устройство многочастотного сигнала, содержащее n параллельных линеек, каждая из которых состоит из соответствующих последовательно соединенных блока умножения и интегратора, при этом первые входы n блоков умножения объединены и являются входом устройства, вторые входы блоков умножения являются входами для соответствующих опорных напряжений, отличающееся тем, что введены первый вычислитель - вычислитель значений амплитуд суммы сигнала и помехи, и второй вычислитель - вычислитель значений пороговых напряжений, а также n блоков сравнения с порогом, выход каждого из которых является соответствующим выходом устройства, при этом n выходов первого вычислителя соединены с соответствующими входами второго вычислителя и вторыми входами соответствующих блоков сравнения с порогом, а первые входы каждого из них подсоединены к выходу второго вычислителя, кроме того, выход каждого из n интеграторов соединен с соответствующим входом первого вычислителя.

2. Приемное устройство по п.1, отличающееся тем, что в качестве первого и второго вычислителей использован процессор.

3. Приемное устройство по п.1, отличающееся тем, что в качестве первого и второго вычислителей использована программируемая логическая интегральная схема (ПЛИС).

4. Приемное устройство по п.1, отличающееся тем, что в качестве первого вычислителя использована ПЛИС, а в качестве второго вычислителя - процессор.

5. Приемное устройство по п.1, отличающееся тем, что в качестве первого вычислителя использован процессор, а в качестве второго - ПЛИС.

| ПРИЕМНИК ЧАСТОТНО-МАНИПУЛИРУЕМЫХ СИГНАЛОВ | 2001 |

|

RU2211542C2 |

| СПОСОБ КВАДРАТУРНОГО ПРИЕМА ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С МИНИМАЛЬНЫМ СДВИГОМ | 1999 |

|

RU2192101C2 |

| Устройство для передачи частотно-манипулированных сигналов | 1991 |

|

SU1811022A1 |

| Устройство для формирования частотно-манипулированного сигнала | 1987 |

|

SU1467783A1 |

| Устройство для приема частотно-манипулированных сигналов | 1984 |

|

SU1264369A1 |

| JP 2008177914 A, 31.07.2008. | |||

Авторы

Даты

2009-11-10—Публикация

2008-10-01—Подача