Изобретение относится к аппаратным средствам персонального компьютера /ПК/ и телевизионных приемников, может быть использовано цифровым дисплеем в ПК, ноутбуках и телевизорах.

Аналогом является «Цифровой плоскопанельный дисплей» [1], прототипом принят «Светодиодный дисплей» [2], содержащий три идентичных канала сигналов R, G, B, каждый из которых включает последовательно соединенные накопитель кодов кадра и блок формирования управляющих сигналов, выходы каналов подключены к входам плоскопанельного экрана. Накопители кодов кадра идентичны, каждый включает блоки регистров по числу строк в кадре. Блоки формирования управляющих сигналов идентичны и осуществляют преобразование кодов в соответствующие их величинам длительности излучения светодиода «код - длительность излучения». Плоскопанельный экран представлен совокупностью 2304000 элементов в матрице /1920×1200/, размещаемой в экранном стекле. Каждый элемент матрицы из трех светодиодных ячеек, каждая из которых излучает один из основных цветов R, G, В. Каждая ячейка содержит последовательно расположенные светодиод белого свечения и соответствующий цветной светофильтр R, G, В. Управляющий вход каждого светодиода подключен к своему выходу в блоке формирования управляющих сигналов. Длительность излучения каждой ячейки прямо пропорциональна величине кода цветового сигнала. Суммарное излучение трех цветов светодиодами ячейки формирует цветовой тон и яркость пиксела. Каждый блок формирования управляющих сигналов включает генератор импульсов и 2304000 идентичных преобразователей «код - длительность излучения», каждый из которых включает последовательно соединенные первый ключ, вычитающий счетчик импульсов, дешифратор и второй ключ, и источник питания, выход которого подключен к сигнальному входу второго ключа. Скважность излучения светодиодов формируют цветовые тона и яркости всех пикселов экрана. Строчная и кадровая развертки отсутствуют. Дисплей воспроизводит четыре режима разрешения: 1024×768, 1280×1024, 1920×1080, 1600×1200.

Недостатки прототипа: первый - снижение достоверности цветопередачи при малых значениях кодов, ведущее к искажению гаммы цветов, так как излучение начинается с началом периода кадра при малых значениях кодов, вычитание в счетчике заканчивается также в начале периода кадра, глаз утрачивает часть яркости излучения в конце периода, что и снижает достоверность цветопередачи; второй - дисплей не воспроизводит стереоизображения.

Цель изобретения - получить одинаково достоверную цветопередачу при всех значениях кодов сигналов и осуществить дисплеем воспроизведение стереоизображения при подключении его к источникам выдачи кодов стереопар.

Техническим результатом являются достоверная цветопередача всех кодов цветовых сигналов и воспроизведение стереоизображения, достигаемые преобразованием кодов в соответствующую последовательность импульсов излучений преобразованием «код - число импульсов излучений» и введением в состав дисплея аппаратных средств для восприятия зрителем объемного изображения. Сущность изобретения в том, что в универсальный цифровой дисплей /УЦД/, содержащий три канала цветовых сигналов, каждый из которых включает накопитель кодов кадра и блок формирования управляющих сигналов, и плоскопанельный экран, содержащий стекло с матрицей в нем из элементов по числу разрешения кадра, введены ключ, триггер, переключатель, ИК-передатчик, ЗД-очки с ИК-приемником, а блок формирования управляющих сигналов выполнен из преобразователей «код - число импульсов излучений», которых по числу максимального разрешения кадра, и двух блоков схем формирования импульса. Универсальный цифровой дисплей на фиг.1, накопитель кодов кадра на фиг.2, блок регистров на фиг.3-6, блок формирования управляющих сигналов на фиг.7. Универсальный цифровой дисплей /УЦД/ воспроизводит пять видеорежимов с разрешением: 1024×768, 1280×1024, третий 1920×1080, четвертый 1600×1200 и пятый 1920×1200. Частота кадров при любом режиме разрешения может быть в диапазоне 50-120 Гц. В формате режима наибольшего разрешения и при частоте кадров 100 Гц частота дискретизации составляет:

fд=1920×1200×100 Гц=230,4 МГц,

где 1920 - число отсчетов в строке, 1200 - число строк в кадре, 100 Гц - частота кадров. Частота строк fс - 1200×100=120 кГц. Параметры видеорежимов в таблице 1.

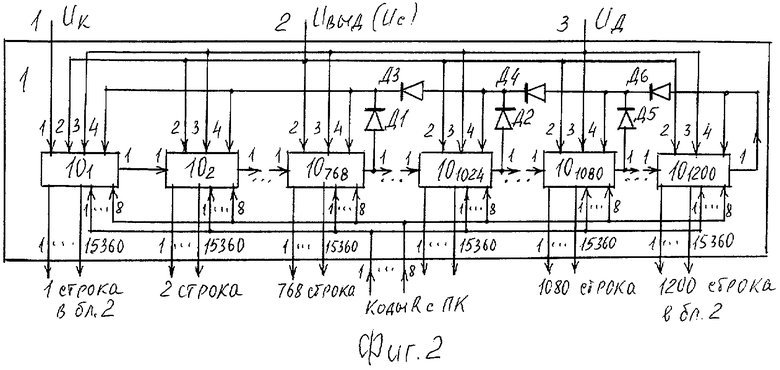

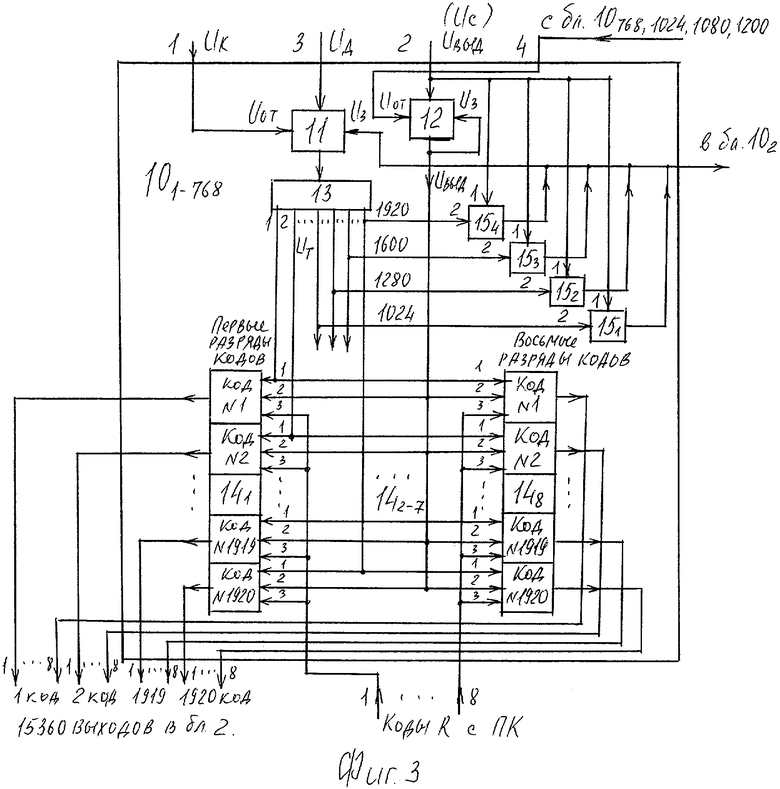

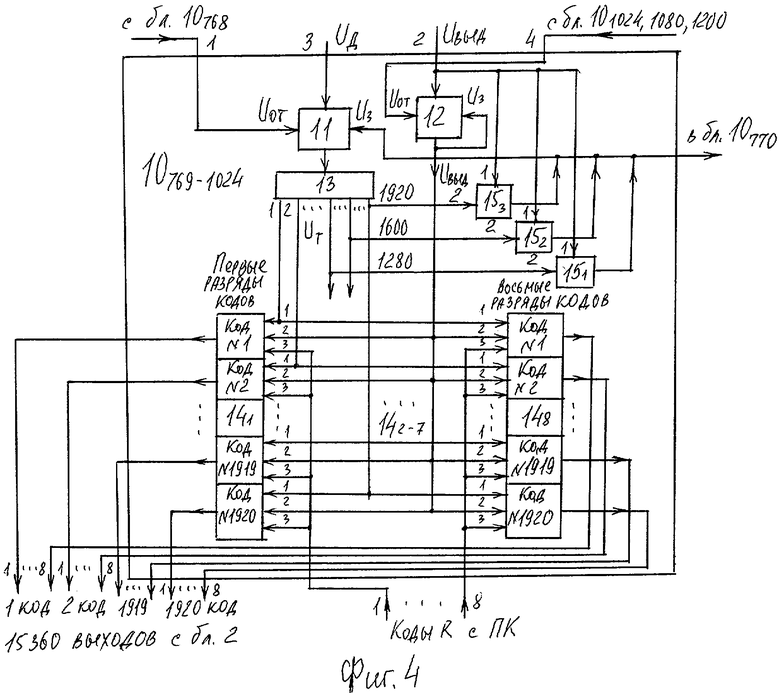

Универсальный цифровой дисплей включает /фиг.1/ первый диод Д1, второй диод Д2, три идентичных канала цветовых сигналов /R, G, В/, каждый из которых включает последовательно соединенные накопитель 1 кодов кадра и блок 2 формирования управляющих сигналов, выходы которого подключены к соответствующим входам плоскопанельного экрана 3, включает третий диод Д3, четвертый диод Д4, последовательно соединенные ключ 4, триггер 5 и переключатель 6, ИК-передатчик 7 на корпусе экрана 3, ЗД-очки 8 и ИК-приемник 9 на их оправе, который подключается переключателем 6 к второму выходу триггера 5. Переключатель 6 имеет фиксированные первый и второй крайние положения и нейтральное третье положение. Накопители 1 кодов кадра идентичны /фиг.2/, каждый включает блоки 10 регистров по наибольшему числу строк в кадре 1200. Информационным входом накопителя 1 кодов кадра являются поразрядно объединенные 1-8 входы блоков 10 регистров. Управляющими входами являются: первым - первый управляющий вход Uк первого блока 101 регистров, вторым - объединенные вторые управляющие входы Uвыд блоков 10 регистров, третьим - объединенные третьи управляющие входы Uд блоков 10 регистров. Управляющий выход каждого предыдущего блока 10 регистров является первым управляющим входом каждого последующего блока 10 регистров. Управляющий выход последнего блока регистров каждого режима разрешения 10768, 101024, 101080, 101200 через соответствующие диоды Д1, Д2 и Д3, Д5, Д4 и Д3, Д6, Д4 и Д3 подключены параллельно к четвертым управляющим входам всех блоков 10 регистров, предшествующих блоку 10, представляющего последнюю строку режима разрешения. Первым, вторым и третьим информационными входами УЦД являются информационные 1-8 входы накопителей кодов кадра первого - третьего каналов цветовых сигналов. Первым и четвертым управляющими входами УЦД являются входы первого диода Д1 и второго диода Д2, выходы которых объединены и подключены к объединенным первым управляющим входам накопителей 1 кодов кадра. Вторым и третьим управляющими входами УВД являются объединенные соответственно вторые и третьи управляющие входы накопителей 1 кодов кадра. Блоки 10 регистров идентичны /фиг.3-6/, каждый включает первый 11 и второй 12 ключи, распределитель 13 импульсов, восемь регистров 141-8 и элементы И 15. В первом режиме разрешения 1024×768 блоки регистров 101-768 имеют по четыре элемента И 151-4, блоки 10769-1024 второго режима разрешения 1280×1024 имеют по три элемента И 151-3 /фиг.4/, блоки 101025-1080 /фиг.5/ третьего режима разрешения 1920×1080 имеют по два элемента И1-2, блоки 101081-1200 четвертого и пятого режимов разрешения 1600×1200, 1920×1200 имеют также по два элемента И 151-2. Информационным входом каждого блока 10 являются поразрядно объединенные третьи /информационные/ входы разрядов регистров 14, выходами блока 10 регистров являются параллельные выходы всех разрядов восьми регистров, которых 15360. Управляющими входами блока 10 являются: первым - первый управляющий вход Uк первого ключа 11, вторым - сигнальный вход Uвыд /Uс/ второго ключа 12, третьим - сигнальный вход Uд первого ключа 11, четвертым - первый управляющий вход второго ключа 12, подключенный через соответствующие диоды к управляющим выходам блоков 10768, 101024, 101080, 101200. Первые входы элементов И 151-4 /фиг.3/ объединены и подключены к сигнальному входу ключа 12, вторые их входы подключены к выходам соответственно 1024, 1280, 1600 и 1920 блока 13, а выходы этих элементов И объединены и подключены к второму управляющему входу ключа 11 и являются управляющим выходом в блоки 102-768. Первые входы элементов И1-3 /фиг.4/ в блоках 10769-1024 объединены, подключены к сигнальному входу ключа 12, вторые их входы подключены к выходам 1280, 1600, 1920 блока 13, выходы этих элементов И объединены и подключены к второму управляющему входу ключа 11 и являются управляющим выходом в блоки 10770-1024. Первые входы элементов И 151-2 /фиг.5/ в блоках 101025-l080 объединены, подключены к сигнальному входу ключа 12, вторые их входы подключены к выходам 1600, 1920 блока 13, выходы их объединены, подключены к второму управляющему входу ключа 11 и являются управляющим выходом в блоки 101025-I080. Первые входы элементов И 151-2 /фиг.6/ в блоках 101081-1200 подключены к сигнальному входу ключа 12, вторые их входы подключены к выходам 1600 и 1920 блока 13, выходы этих элементов И объединены подключены к второму управляющему входу первого ключа 11 и являются управляющим выходом в блоки 101081-1200. Выход первого ключа 11 подключен к входу распределителя 13 импульсов, выходы которого последовательно подключены к первым /тактовым/ управляющим входам разрядов параллельно восьми регистров 14. Выход второго ключа 12 подключен параллельно к вторым управляющим входам разрядов восьми регистров 14 и к второму управляющему входу ключа 12. Блоки формирования 2 управляющих сигналов предназначены для преобразования значений кодов цветовых сигналов в соответствующую последовательность соответствующего числа импульсов излучений элементами матрицы экрана 3, размещаемых в экранном материале. Экранным материалом является стекло или эластичный пластик, в котором методом микроэлектронной технологии размещаются 2304000 излучающие элементы матрицы 1920×1200 экрана 3. Каждый из элементов матрицы содержит три излучающих ячейки, каждая из которых излучает один из основных цветов R, G, В. Излучающими ячейками являются ячейки OLED - органические светоизлучающие диоды [3 с.7-9, 4 с.42, 43], из которых компании Европы, Азии в 2008 году приступили к серийному производству OLED-телевизоров [3 с.8]. В США с экраном из OLED-диодов выпускают телевизор XEL-I. Толщина OLED-диодов 500 нанометров, напряжение анод-катод 3…16 В, время наработки 30000 часов [3 с.7]. В сравнении с LCD диоды OLED имеют большую яркость, контрастность 106:1 и экономичность в энергопотреблении [3 с.9]. Применяемые сейчас OLED-дисплеи управляются активными TFT-матрицами [3 с.8 рис.6б]. Такие ячейки занимают часть площади экрана и имеют много проводников. Для исключения с площади экрана миллионов TFT и освобождения его от проводников в универсальном цифровом дисплее применены блоки 2 формирования управляющих сигналов, которые размещаются вне экрана на тыльной его стороне. Каждый блок 2 содержит преобразователи «код - число импульсов излучений» по числу разрешения 2304000 /1920×1200/, первый 16, второй 17 блоки схем формирования импульса /Uп/ пуска по амплитуде и длительности. Каждый из блоков 16, 17 включает по 2304000 схем. Каждый преобразователь включает /фиг.7/ последовательно соединенные дешифратор 18, входы которого являются 1-8 информационными входами преобразователя, блок 19 ключей из 255 ключей и выходной ключ 20, включает первый 21 и второй 22 самоходные распределители импульсов /СРИ/ и источник питания 23, запитывающий OLED-диод в излучающей ячейке экрана 3. Выходы дешифратора 18 подключены к управляющим входам соответствующих 255 ключей в блоке 19 ключей, к сигнальным входам которых подключены выходы соответствующих 255 разрядов СРИ 21, 22. Выходы 255 ключей блока 19 через диоды объединены и подключены к управляющему входу своего выходного ключа 20, сигнальный вход которого подключен к выходу источника 23 питания. Входы первых СРИ 21 подключены к выходам схем формирования импульса Uп пуска в блоке 16, входы вторых СРИ 22 подключены к выходам схем формирования в блоке 17. Каждый СРИ 21, 22 имеет по 255 разрядов, выходы которых поразрядно объединены и подключены к сигнальным входам соответствующих ключей в блоке 19. СРИ 21 работают при поступлении на вход блока 16 импульса Uк частотой 50 Гц или 60 Гц, СРИ 22 работают при поступлении на вход блока 17 импульса Uк частотой 80 Гц, 100 Гц, 120 Гц. Входы блоков 16 и 17 являются первым и вторым управляющими входами блока 2. Информационными входами блока 2 являются информационные входы 2304000 всех дешифраторов 18. Выходами блока 2 являются выходы 2304000 всех выходных ключей 20, которые подключены к входам своих излучающих ячеек OLED-диодов в экране 3. Исходное состояние ключей в блоках 19 и выходных ключей 20 закрытое. С поступлением на первый /второй/ управляющий вход блока 2 сигнала Uк все схемы формирования импульсов блока 16 /17/ выдают параллельно на входы СРИ 21 /СРИ 22/ импульсы Uп пуска, запускающие СРИ 21 /22/ в работу. Длительность работы СРИ определяется прохождением импульса Uп пуска от первого разряда до 255 и равно длительности периода кадра подключенного режима. Коды с накопителей 1 кодов кадра /фиг.1/ в параллельном виде и синхронно выдаются в дешифраторы 18 блоков 2 /фиг.7/. Выходные сигналы с дешифраторов 18 поступают на первые управляющие входы ключей и открывают соответствующие ключи в блоке 19 соответственно величине кода. С выходов разрядов СРИ 21 /22/ импульсы соответствующей длительности последовательно поступают на сигнальные входы ключей блока 19 и через открытые ключи поступают на управляющий вход выходного ключа 20, открывая его на время своей длительности 65 мкс при периоде 16,67 мс и на 39 мкс при периоде кадра 10 мс /80 Гц, 100 Гц, 120 Гц/. Источник питания 23 при открытом ключе 20 запитывает излучающую ячейку OLED в экране 3, которая в течение запитывающего импульса излучает световой импульс соответствующего цвета. Импульс с выхода ключа в блоке 19 задним фонтом закрывает ключ. При частоте 60 Гц каждый импульс Uот с блока 19 открывает ключ 20 на длительность: 16,67 мс : 255=65 мкс, где: 16,67 мс длительность кадра при 60 Гц, 255 - разрешение 8-разрядного кода или число 255 разрядов в СРИ. Длительность кадра при 60 Гц составляет 83% от длительности кадра при 50 Гц, следовательно, длительность импульса 65 мкс южно применять и при частоте 50 Гц и при частоте 60 Гц. Длительность кадра при 100 Гц составляет 10 мс, что составляет 75% от длительности кадра 80 Гц и 83% от длительности кадра при частоте 120 Гц  , т.е. при частотах 80 Гц, 100 Гц, 120 Гц можно пользоваться одним и те же импульсом 39 мкс

, т.е. при частотах 80 Гц, 100 Гц, 120 Гц можно пользоваться одним и те же импульсом 39 мкс  . Излучающая ячейка соответственно величине кода за период кадра запитывается столько раз по 65 мкс или 39 мкс, сколько было открыто ключей в блоке 19. Чем больше код, тем больше импульсов излучений за период кадра выполнит излучающая ячейка OLED-диод. Распределение импульсов излучений в периоде кадра соответственно величинам кодов приводится в таблице 2.

. Излучающая ячейка соответственно величине кода за период кадра запитывается столько раз по 65 мкс или 39 мкс, сколько было открыто ключей в блоке 19. Чем больше код, тем больше импульсов излучений за период кадра выполнит излучающая ячейка OLED-диод. Распределение импульсов излучений в периоде кадра соответственно величинам кодов приводится в таблице 2.

Следование импульсов излучений в периоде кадра через равные интервалы времени соответствует природному восприятию изображения зрением человека, следовательно, восприятие яркости и цветопередачи будет максимально достоверно, воспроизводимая гамма цветов будет соответствовать существующим в природе. Инерционность срабатывания излучателей OLED-диодов составляет до 1 мкс. При разрешении 1920×1200 матрица экрана 3 содержит 2304000 излучающих элементов или 6912000 излучающих ячеек /2304000×3/ OLED. Процесс получения изображения на экране упрощается и состоит в параллельном и синхронном запитывании излучающих ячеек экрана 3 с блоков 2 соответственно значениям кодов кадра, необходимость в строчной и кадровой развертках отпадает. Смена изображений кадров на экране подобно проекции с кинопленки на экран. Современные технологии изготовления микросхем позволяют выполнить каждый из блоков 1 и 2 в одной микросхеме.

Работа блоков регистров /фиг.3-6/.

Сигналы разрядов кодов поступают на третьи входы разрядов регистров 14. Заполнение регистров кодами строки начинается с открытием импульсом Uк первого ключа 11, который пропускает импульсы Uд на вход распределителя 13 импульсов. Тактовые импульсы с выходов блока 13 последовательно поступают параллельно на первые /тактовые/ управляющие входы разрядов регистров 141-8. Сигналы первых разрядов поступают в разряды первого регистра 141, вторых разрядов кодов в разряды второго регистра 142 и т.д., восьмых разрядов кодов в разряды регистра 148. По заполнении регистров сигнал с соответствующего выхода блока 13 соответственно режима разрешения поступает на второй вход элемента И 15, на первый вход которого поступает импульс частота строк /он же сигнал Uвыд по таблице 1/. При совпадении импульсов в элементе И 15 сигнал с его выхода закрывает ключ 11 и как выходной управляющий сигнал открывает ключ 11 в следующем блоке 102 регистров, регистры 14 которого заполняются кодами второй строки. Такой процесс идет до последнего блока 10 регистров соответственно режиму разрешения, выходной сигнал с которого открывает все вторые ключи 12 в блоках 10 регистров, которые пропускают по одному импульсу Uвыд, частота следования которых соответствует частоте строк принимаемого режима разрешения. Сигнал Uвыд синхронно выдает из всех блоков 10 коды кадра в блоки 2 и обнуляет разряды регистров блоков 10 для приема ими кодов следующего кадра.

Работа устройства.

С информационных пиковых выходов видеоадаптера ПК /или с соответствующего блока телевизора, проигрывателя DVD/ на информационные входы накопителей 1 кодов кадра /фиг.1/ в параллельном виде поступают 8-разрядные коды сигналов R, G, В и на управляющие входы 1-5 соответственно управляющие сигналы синхроимпульсы частоты кадров Uк, строк Uвыд, импульсы частоты дискретизации Uд, импульсы частоты стереопар Uсп. За время первого кадра регистры блоков 10 последовательно заполняются кодами первого кадра. Каждый блок 10 сосредотачивает коды одной строки. При первом режиме разрешения 1024×768 заполняются блоки 10 регистров с первого по 768 /фиг.2/, при втором 1280×1024 заполняются блоки с первого по 1024, при третьем - 1920×1080 заполняются блоки с первого по 1080, при четвертом 1600×1200 - блоки с 1-го по 1200, при пятом 1920×1200 заполняются блоки 10 регистров с 1-го по 1200. За первый период кадра в накопителях 1 кодов кадра сосредотачиваются все коды кадра. С окончанием периода кадра управляющий сигнал с соответствующего блока 10 поступает на четвертые управляющие входы блоков 10 и выдает из них синхронно и в параллельном виде все коды кадра в блоки 2, в которых коды преобразуются в последовательность импульсов, запитывающих излучающие ячейки OLED, на экране 3 в течение длительности периода кадра высвечивается изображение кадра. После заполнения кодами второго кадра накопителей 1 процесс повторяется. Вся площадь экрана 3 занимается изображением только при пятом режиме разрешения 1920×1200. Универсальный цифровой дисплей работает в трех режимах. При первом - переключатель 6 в нейтральном положений 3 /фиг.1/ - идет воспроизведение плоского пространства. Второй режим - переключатель 6 в положении 1 - идет воспроизведение стереоизображений с использованием ИК-передатчика 7 и восприятие зрителем объемного изображения через ЗД-очки 8 с ИК-приемником 9, третий режим - переключатель 6 в положении 2, идет воспроизведение стереоизображений без ИК-передатчика 7, восприятие объемного изображения выполняется с использованием ИК-приемника 9 и ЗД-очков. В режиме стереоизображения на пятый управляющий вход /фиг.1/ подаются импульсы стереопар Uсп 25 Гц или 30 Гц, 40 Гц, 50 Гц, 60 Гц. В каждой стереопаре правый и левый кадры следуют друг за другом. При этом импульсы Uк правого и левого кадров частотой 50 Гц /25 Гц+25 Гц/, 60 Гц /30 Гц+30 Гц/ поступают на первый управляющий вход УЦД, импульсы кадров Uк частотой 80 Гц /40 Гц+40 Гц/, 100 Гц /50 Гц+50 Гц/, 120 Гц /60 Гц+60 Гц/ поступают на четвертый управляющий вход УПД. Зритель воспринимает изображение объемным через ЗД-очки, выполненные по технологии ЖК-ячеек просветного типа и используются как электронно-управляемые светофильтры /затворы/ [5 с.558, 564]. 1 и 4 управляющие входы через диоды Д3, Д4 объединяются и подключены к сигнальному входу ключа 4, который для выделения первым в стереопаре правого кадра открывается импульсом каждой стереопары Uсп, поступающим на управляющий вход Uот ключа 4 с пятого управляющего входа УЦД. С выхода ключа 4 импульсы кадров поступают на вход триггера 5, второй выход которого подключен к переключателю 6. При использовании ИК-передатчика 7 переключатель 6 ставится в первое фиксированное положение. При открытии ключа 4 сигнал со второго выхода триггера 5 соответствует левому кадру стереопары, ИК-передатчик излучает ИК-импульс, который принимается ИК-приемником 9, выдающим сигнал соответствующей длительности в ЖК-ячейки правого стекла, при срабатывании ЖК-ячеек правое стекло очков затемняется, и левый глаз видит левый кадр экрана 3. Затем схема ИК-приемника 9 сама выдает такой же длительности импульс в ЖК-ячейки левого стекла, которое затемняется, правый глаз видит изображение правого кадра на экране. Каждый глаз видит свой кадр, что и дает стереоэффект. При третьем режиме переключатель 6 ставится в положение 2. При этом выход триггера 5 подключается через кабель ко входу ИК-приемника 9. Идет тот же процесс управления затемнением стекол ЗД-очков без участия ИК-передатчика 7. В связи с большим числом соединений от микросхем блоков 1 к микросхемам блока 2 и от них к OLED-ячейкам в экране 3 блоки 1 и 2 следует выполнить на тыльной стороне экрана 3. Предлагаемый дисплей воспроизводит пять режимов разрешения при изображении плоского пространства и пять режимов разрешения в стереоизображении, что позволяет признать его универсальным цифровым дисплеем и применить в качестве универсального исполнительного устройства: монитором во всех ПК и ноутбуках и плоскопанельным экраном в телевизорах.

Использованные источники

1. Патент №2316138 С1, кл. Н04N 9/12, бюл. №3 от 27.01.08, аналог.

2. Патент №2316139 С1, кл. Н04N 9/12, бюл. №3 от 27.01.08, прототип.

3. Радио №6, 2008, с.7-9, рис.6а, б.

4. «Домашний компьютер» №12, 2096, с.42-43.

5. Колиниченко О.В., Шишигин И.В. Аппаратные средства РС, 5-е изд-е, СПб, 2004, с.558, 564.

| название | год | авторы | номер документа |

|---|---|---|---|

| СВЕТОДИОДНЫЙ ДИСПЛЕЙ | 2006 |

|

RU2316139C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ ОБЪЕМНОЙ ВИДЕОИНФОРМАЦИИ | 2009 |

|

RU2413388C1 |

| ШИРОКОФОРМАТНЫЙ ЭКРАН | 2006 |

|

RU2316141C1 |

| УСТРОЙСТВО ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ СТЕРЕОВИДЕОИНФОРМАЦИИ | 2009 |

|

RU2421935C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2010 |

|

RU2420025C1 |

| ВИДЕОКАМЕРА | 2007 |

|

RU2358412C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2375841C1 |

| ЦИФРОВОЙ МОНИТОР | 2006 |

|

RU2306677C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2369041C1 |

| ЦИФРОВОЙ МОНИТОР | 2006 |

|

RU2306676C1 |

Изобретение относится к аппаратным средствам персонального компьютера /ПК/ и телевизионных приемников, может быть использовано в качестве цифрового дисплея в ПК, ноутбуках и телевизорах. Техническим результатом являются достоверная цветопередача кодов цветовых сигналов и воспроизведение стереоизображения. Результат достигается тем, что в универсальный цифровой дисплей, содержащий три канала цветовых сигналов и плоскопанельный экран, введены ключ, триггер, переключатель, ИК-передатчик, ЗД-очки с ИК-приемником, а блок формирования управляющих сигналов выполнен из преобразователей "код - число импульсов излучений" по числу максимального разрешения кадра и двух блоков схем формирования импульса. 7 ил., 2 табл.

Универсальный цифровой дисплей (УЦД), содержащий три канала цветовых сигналов R, G, В, каждый из которых включает последовательно соединенные накопитель кодов кадра и блок формирования управляющих сигналов, и плоскопанельный экран, содержащий экранное стекло с матрицей в нем из элементов по числу максимального разрешения кадра, каждый элемент матрицы включает три излучающих ячейки основных цветов R, G, В, первым, вторым и третьим информационными входами УЦД являются информационные входы накопителя кодов кадра каждого канала цветового сигнала, подключенные к соответствующим информационным выходам видеоадаптера персонального компьютера (ПК), первым, вторым и третьим управляющими входами являются объединенные соответственно первые, вторые и третьи управляющие входы накопителей кодов кадра, подключенные к соответствующим управляющим выходам видеоадаптера ПК, накопители кодов кадра идентичны, каждый включает блоки регистров по числу строк максимального разрешения, информационным входом накопителя кодов кадра являются поразрядно объединенные информационные входы блоков регистров, первым управляющим входом является первый управляющий вход первого блока регистров, вторым - объединенные вторые управляющие входы блоков регистров, третьим - объединенные третьи управляющие входы блоков регистров, каждый управляющий выход предыдущего блока регистров является первым управляющим входом последующего блока регистров, управляющий выход блока регистров, представляющий 768-ю строку первого режима разрешения, подключен через первый диод параллельно к четвертым управляющим входам блоков регистров с первого по 768-й, управляющий вход блока регистров, представляющий последнюю 1024-ю строку второго режима разрешения, через второй и третий диоды подключен параллельно к четверым управляющим входам блоков регистров с первого по 1024-й, управляющий выход блока регистров, представляющий последнюю 1080-ю строку третьего режима разрешения последовательно через пятый, четвертый и третий диоды подключен параллельно к четвертым управляющим входам блоков регистров с первого по 1080-й, управляющий выход блока регистров, представляющий последнюю 1200-ю строку четвертого режима разрешения последовательно через шестой, четвертый и третий диоды подключен к четвертым управляющим входам блоков регистров с первой по 1200-ю, выходами накопителя кодов кадра являются параллельные выходы всех блоков регистров, блоки регистров идентичны, каждый включает первый и второй ключи, распределитель импульсов и восемь регистров, каждый из которых включает по 1920 разрядов, информационными 1-8 входами блока регистров являются поразрядно объединенные третьи (информационные) входы восьми регистров, параллельные выходы всех разрядов регистров являются выходами блока регистров, первым управляющим входом блока регистров является первый управляющий вход первого ключа, вторым - сигнальный вход второго ключа, третьим - сигнальный вход первого ключа, четвертым - первый управляющий вход второго ключа, подключенный к управляющему выходу блока регистров, представляющего последнюю строку своего режима разрешения (768, 1024, 1080, 1200), выход первого ключа подключен к входу распределителя импульсов, выходы которого последовательно подключены к первым (тактовым) управляющим входам параллельно восьми регистров, выход второго ключа подключен параллельно к вторым управляющим входам всех разрядов восьми регистров и к второму управляющему входу второго ключа, блоки регистров с первого по 768-й содержат по четыре элемента И, первые входы которых подключены к сигнальному входу второго ключа, вторые их входы подключены: первого элемента И к 1024-у выходу распределителя импульсов, второго элемента И к 1280-у выходу распределителя импульсов, третьего элемента И к 1600-у выходу распределителя импульсов, четвертого элемента И к 1920-у выходу распределителя импульсов, выходы этих элементов И объединены, подключены к второму управляющему входу первого ключа и являются управляющим выходом в блоках регистров с первого по 768-й, блоки регистров с 769-й по 1024-й содержат по три элемента И, первые входы которых объединены и подключен к сигнальному входу второго ключа, вторые их входы подключены соответственно: первого элемента И к 1280-у выходу, второго элемента И к 1600-у выходу и третьего элемента И к 1920-у выходу распределителя импульсов; выходы этих элементов И объединены и подключены к второму управляющему входу первого ключа и являются управляющим выходом в блоках регистров с 769-го по 1024-й, блоки регистров с 1025-го по 1080-й содержат по два элемента И, первые входы которых подключены к сигнальному входу второго ключа, вторые их входы подключены: первого элемента И к 1600-у выходу распределителя импульсов, второго элемента И к 1920-у выходу распределителя импульсов, выходы этих элементов И объединены и подключены к второму управляющему входу первого ключа и являются управляющим выходом в блоках регистров с 1025-го по 1080-й, блоки регистров с 1081-го по 1200-й содержат по одному элементу И, первый вход которого подключен к сигнальному входу второго ключа, второй вход подключен к 1920-у выходу распределителя импульсов, выход этого элемента И подключен к второму управляющему входу первого ключа и является управляющим выходом в блоках регистров с 1081-й по 1200-й, отличающийся тем, что в первый управляющий вход УЦД введен первый диод, вход которого является первым управляющим входом УЦД, введен второй диод, вход которого является четвертым управляющим входом УЦД, выходы первого и второго диодов объединены и подключены к объединенным первым управляющим входам накопителей кодов кадра, введены третий и четвертый диоды, вход третьего диода подключен к входу первого диода, вход четвертого диода подключен к входу второго диода, а выходы третьего и четвертого диодов объединены, в УЦД введены последовательно соединенные ключ, вход которого подключен к объединенным выходам третьего и четвертого диодов и управляющий вход его является пятым управляющим входом УЦД, триггер и переключатель, имеющий три фиксированных положения, вход которого подключен к второму выходу триггера, ИК-передатчик, расположенный на корпусе экрана, подключенный к второму выходу триггера при первом фиксированном положении переключателя, ЗД-очки с ИК-приемником на их оправе, который подключается к второму выходу триггера при втором фиксированном положении переключателя, третье фиксированное положение которого является нейтральным, блоки формирования управляющих сигналов идентичны, каждый содержит преобразователи "код - число импульсов излучений" по числу максимального разрешения (1920×1200), первый и второй блоки схем формирования импульса, каждый из которых включает схемы формирования импульса Uп по числу преобразователей 2304000 (1920×1200), входы первого и второго блоков схем формирования импульса являются соответственно первым и вторым управляющими входами блока формирования управляющих сигналов и подключены соответственно к входам третьего и четвертого диодов УЦД, каждый преобразователь "код - число импульсов излучений" содержит последовательно соединенные дешифратор, блок ключей из 255 ключей, первые управляющие входы которых подключены к соответствующим выходам дешифратора, и выходной ключ, выход которого является выходом преобразователя, первый и второй самоходные распределители импульсов (CPU), входы первых СРИ подключены к выходам соответствующих схем формирователя импульса Uп в первом блоке схем формирования импульса, входы вторых СРИ подключены к выходам соответствующих схем формирования импульса Uп во втором блоке схем формирования импульса, каждый из СРИ включает по 255 разрядов, выходы которых попарно и поразрядно объединены и подключены к сигнальным входам соответствующих ключей в блоке ключей, выходы которых через диоды объединены и подключены к управляющему входу выходного ключа, преобразователь "код - число импульсов излучений" включает источник питания, выход которого подключен к сигнальному входу выходного ключа, выходами блока формирования управляющих сигналов являются выходы всех преобразователей "код - число импульсов излучений", которые подключены к соответствующим входам плоскопанельного экрана, в элементах матрицы которого каждая излучающая ячейка является OLED-диодом (органическим светоизлучающим диодом), и в блоки регистров с 1081-й по 1200-й введен второй элемент И, первый вход которого подключен к сигнальному входу второго ключа блока регистров, второй его вход подключен к 1920-у выходу распределителя импульсов блока регистров, выход второго элемента И объединен с выходом первого элемента и в этих блоках регистров.

| СВЕТОДИОДНЫЙ ДИСПЛЕЙ | 2006 |

|

RU2316139C1 |

| US 2008150847 A1, 26.06.2008 | |||

| CN 101211533 А, 02.07.2008 | |||

| RU 2006146956 A, 10.07.2008. | |||

Авторы

Даты

2010-01-27—Публикация

2008-07-21—Подача