Изобретение относится к аппаратным средствам персонального компьютера и может быть использовано как монитор в персональном компьютере /ПК/.

Прототипом принят цифровой монитор [1], содержащий элемент И, с первого по десятый ключи, делитель частоты, триггер, с первого по шестой накопители кодов строки сигналов R, G, В, три блока импульсных усилителя, блок модуляции излучений, первый усилитель и первый пьезодефлектор с отражателем на торце, второй усилитель и второй пьезодефлектор с отражателем на торце, четыре источника опорных напряжений, проекционный объектив, матовый экран, блоки строчной и кадровой разверток. Недостатком прототипа является развертка кадра одной строкой, а так как излучение луча безинерционно и матовый экран не имеет излучающего покрытия, то яркость изображения на экране для восприятия зрителя будет недостаточна.

Цель изобретения - увеличить яркость воспроизводимого изображения для визуального восприятия зрителем.

Техническим результатом является повышение усредненной яркости изображения, воспринимаемой зрителем, в 99840 раз.

Результат достигается разверткой кадра одновременно всеми активными строками растра /768/ и повтором их за кадр 130 раз /768×130/. Воспроизведение цветного изображения выполняется на экране монитора одновременно 768 активными строками при 60 кадрах в секунду. С соответствующих выходов видеоадаптера ПК рабочая частота, строчные и кадровые синхроимпульсы и последовательные коды сигналов R, G, В поступают соответственно на 1-3 управляющие входы и с первого по третий информационные входы цифрового монитора. Изображение на экране воспроизводится электронно-оптической разверткой промодулированными по яркости излучениями 768 излучателей трех основных цветов R, G, В.

Сущность заявляемого изобретения в том, что в цифровой монитор, содержащий элемент И, соответствующее число ключей, делитель частоты, три блока импульсных усилителей, блок модуляции излучений, блок строчной развертки, усилитель и пьезодефлектор с отражателем на торце, проекционный объектив и матовый экран, введены второй триггер, три накопителя кодов нечетного кадра и три накопителя кодов четного кадра, блок модуляции излучений выполняется из соответствующего числа каналов, каждый из которых содержит фокусирующий конус световода /фокон/ с выполненным в его входном окне излучателем трех основных цветов, и содержит лампу подсветки.

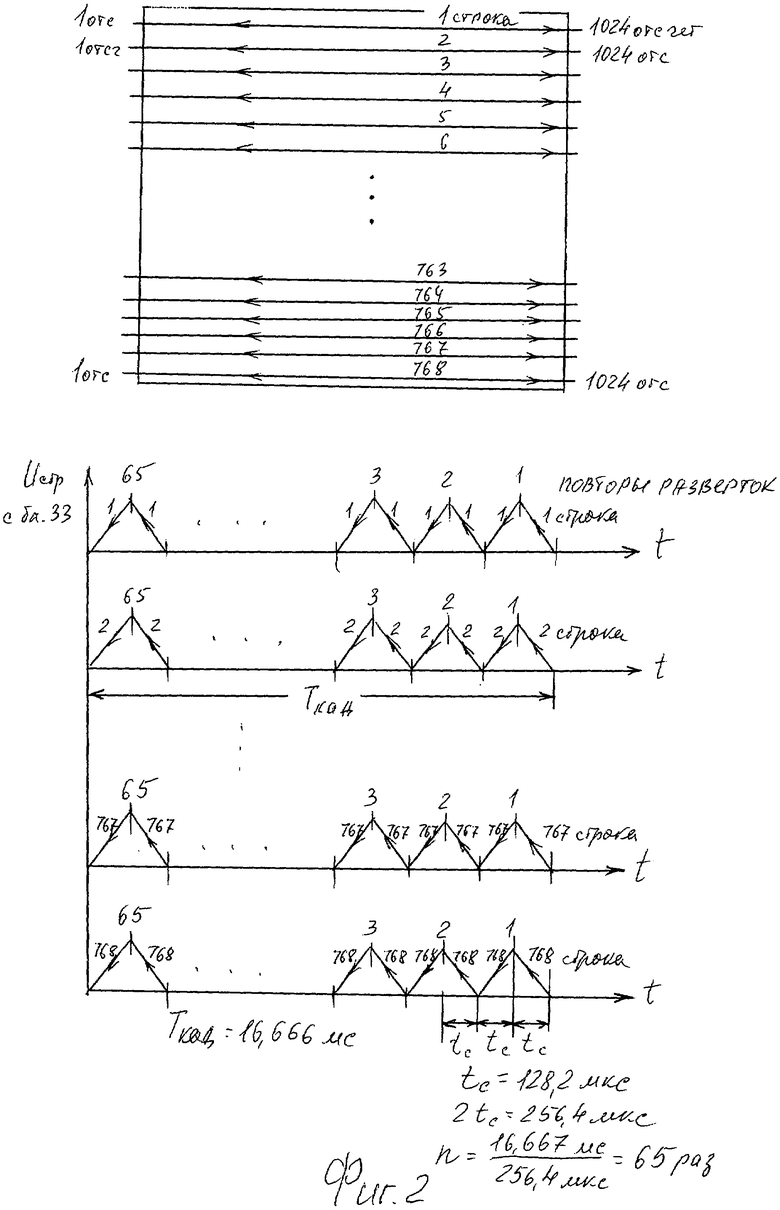

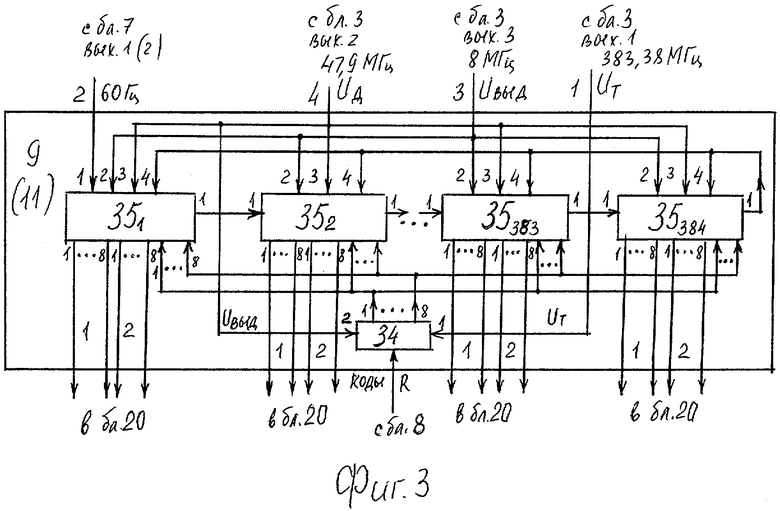

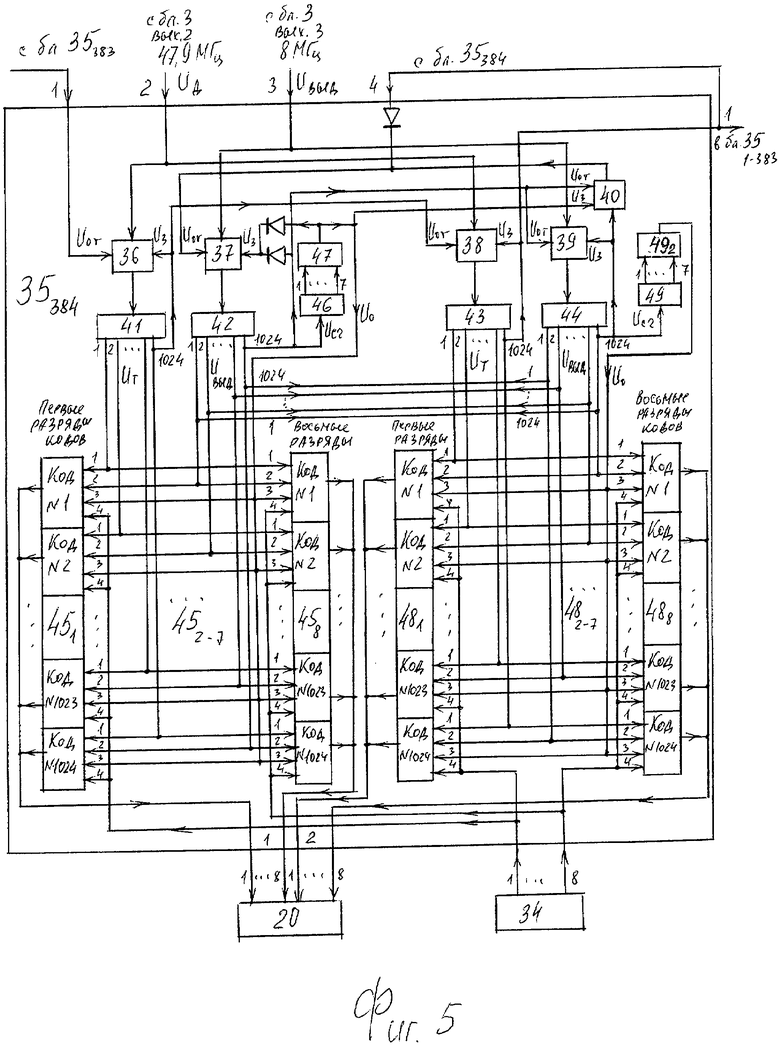

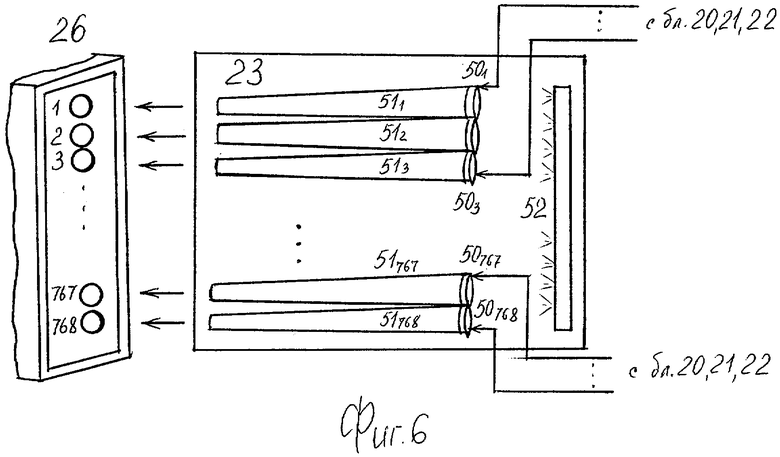

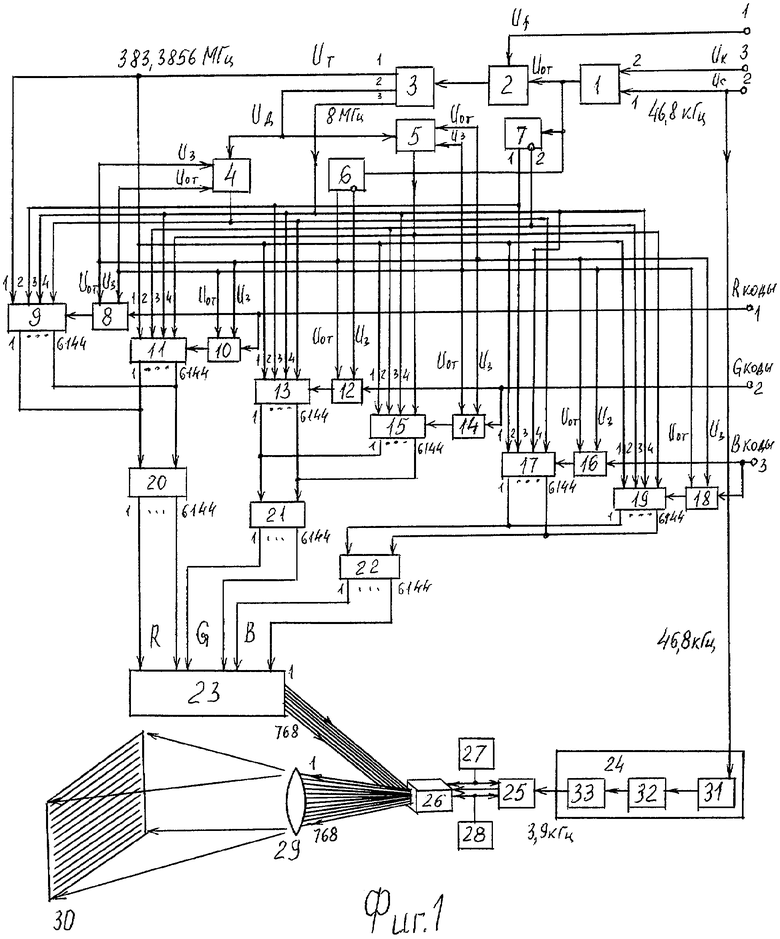

Функциональная схема цифрового монитора представлена на фиг.1, развертка кадра на экране и формы управляющих напряжений - на фиг.2, накопитель кодов нечетного /четного/ кадра - на фиг.3, блок регистров - на фиг.4 и 5, блок модуляции излучений - на фиг.6, конструкция пьезодефлектора - на фиг.7.

Цифровой монитор включает /фиг.1/ последовательно соединенные элемент И, первый ключ 2, делитель 3 частоты и второй ключ 4, третий ключ 5, первый триггер 6, второй триггер 7, последовательно соединенные соответственно четвертый ключ 8 и первый накопитель 9 кодов нечетного кадра /R/, пятый ключ 10 и первый накопитель 11 кодов четного кадра /R/, шестой ключ 12 и второй накопитель 13 кодов нечетного кадра /G/, седьмой ключ 14 и второй накопитель 15 кодов четного кадра /G/, восьмой ключ 16 и третий накопитель 17 кодов нечетного кадра /В/, девятый ключ 18 и третий накопитель 19 кодов четного кадра /В/, первый 20, второй 21, третий 22 блоки импульсных усилителей, блок 23 модуляции излучений, последовательно соединенные блок 24 строчной развертки, усилитель 25 и пьезодефлектор 26 с отражателем на торце, источник 27 положительного опорного напряжения, источник 28 отрицательного опорного напряжения, проекционный объектив 29, во внешней фокальной плоскости которого расположен матовый экран 30. Блок 24 строчной развертки включает последовательно соединенные делитель 31 частоты /12:1/, задающий генератор 32 и выходной каскад 33, подключенный к первому входу усилителя 25. Вход делителя 31 частоты подключен к первому входу элемента И 1. Входы четвертого 8 и пятого 10 ключей объединены и являются первым информационным входом цифрового монитора /R коды/, входы шестого 12 и седьмого 14 ключей объединены и являются вторым информационным входом цифрового монитора /G коды/, входы восьмого 16 и девятого 18 ключей объединены и являются третьим информационным входом цифрового монитора /В коды/. Первый-третий информационные входы монитора подключены к соответствующим выходам видеоадаптера в системном блоке ПК, первым, вторым, третьим управляющими входами монитора являются соответственно сигнальный вход первого ключа 2, первый и второй входы элемента И 1, также подключенные к соответствующим выходам видеоадаптера ПК. Накопители 9, 13, 17 кодов нечетного кадра и накопители 11, 15, 19 кодов четного кадра идентичны /фиг.3/, каждый включает входной регистр 34 и по числу половины активных строк /768:2/ блоки 351-384 регистров. Первым управляющим входом во всех накопителях кодов является первый /тактовый/ управляющий вход входного регистра 34, подключенный к первому выходу делителя 3 частоты /383,3856 МГц/, третьим и четвертым управляющими входами накопителей 9, 13, 17 и 11, 15, 19 кодов являются объединенные вторые и третьи управляющие входы блоков 351-384 регистров, подключенные соответственно к третьему и второму выходам делителя 3 частоты. Вторыми управляющими входами накопителей 9, 13, 17 кодов нечетного кадра являются первые управляющие входы первого блока 351 регистров, подключенные к первому выходу второго триггера 7, вторыми управляющими входами накопителей 11, 15, 19 кодов четного кадра являются первые управляющие входы первого блока 351 регистров, подключенные к второму выходу второго триггера 7. Выходами накопителей 9, 11, кодов кадра сигнала R являются 1-8 выходы первых восьми регистров /коды нечетной строки/ и 1-8 выходы вторых восьми регистров /коды четной строки/ блоков 351-384 регистров, объединенные соответствующим образом и подключенные к соответствующим входам первого блока 20 импульсных усилителей, содержащего 6144 импульсных усилителя /по числу строк и разрядов в коде/ 768×8=6144. Аналогично выходы вторых накопителей 13, 15 кодов кадра сигнала G подключены к соответствующим входам второго блока 21 импульсных усилителей, содержащего 6144 импульсных усилителя, и выходы третьих накопителей 17, 19 кодов кадра, сигнала В подключены к соответствующим входам третьего блока 22 импульсных усилителей, содержащего 6144 импульсных усилителя.

Блоки 351-384 регистров идентичны /фиг.4 и 5/, каждый включает с первого 36 по пятый 40 ключи, с первого 41 по четвертый 44 распределители импульсов, первые восемь регистров 451-8, последовательно соединенные первый счетчик 46 импульсов и первый дешифратор 47, вторые восемь регистров 481-8, последовательно соединенные второй счетчик 49 импульсов и второй дешифратор 492. Информационными с первого по восьмой входами блока 35 регистров являются поразрядно объединенные информационные /четвертые/ входы разрядов первых восьми 45 и вторых восьми 48 регистров, подключенные к 1-8 выходам выходного регистра 34. Выходы разрядов в каждом из первых восьми регистров 451-8 объединены и являются первыми с первого по восьмой выходами блока 35 регистров, выходы разрядов в каждом из вторых восьми регистров 481-8 объединены и являются вторыми с первого по восьмой выходами блока 35 регистров.

Управляющих входов четыре: первым является первый управляющий вход первого ключа 36 в блоке 351 регистров, подключенный к первому выходу триггера 7 /фиг.1/, в блоках 352-384 регистров первый управляющий вход первого ключа 36, подключенный к первому управляющему выходу в каждом предыдущем блоке 351-383 регистров, вторым - являются объединенные сигнальные входы первого 36 и третьего 38 ключей, он подключен к второму выходу /47,9232 МГц/ делителя 3 частоты, третьим - являются объединенные сигнальные входы второго 37 и четвертого 39 ключей, он подключен к третьему выходу /8 МГц/ делителя 3 частоты, четвертым управляющим входом является первый управляющий вход второго ключа 37, подключенный через диод к первому управляющему выходу в последнем блоке 35384 регистров. Блок 23 модуляции излучений /фиг.6/ выполнен из 768 каналов /по числу активных строк/, каждый из которых содержит фокусирующий конус 51 световода /фокон/ [2 с.77], с расположенным в его входном окне излучателем 50 трех основных цветов, и лампу 52 подсветки белого цвета. Излучение каждого излучателя 50 в отдельности определяет пиксел /точку/ в строке, которых в строке 1024. Излучатель 50 представляет матрицу из восьми триад ЖК-ячеек, выполненную методом микроэлектронной технологии непосредственно во входном окне каждого фокона 511-768. Входной диаметр фокона 50 при размере одной ячейки ЖК 0,25 мм [3, с.490] составляет не более 3 мм /0,25 мм ×3 ячейки ×3 ряда триад/, 7 мм2 - занимаемая площадь. Выходной диаметр фокона принимается 0,02 мм. Контроллер для управления ЖК-ячейками излучателя [4, с.473, 477, 483] не нужен, каждая ЖК-ячейка автономно подключается к запитывающему ее импульсному усилителю в блоках 20, 21, 22. Получение соответствующего тона цвета формируется смешиванием основных цветов R, G, В ЖК-ячеек восьми триад, излучения которых модулируются по яркости соответственно величине кода. Модуляция ячеек по яркости осуществляется применением нейтральных светофильтров соответствующей плотности, которые ослабляют излучение ЖК-ячеек по принадлежности их к разряду кода. В каждой триаде три ЖК-ячейки: красного, зеленого и синего излучения [3, с.488-490], получаемые за счет белого цвета /от лампы подсветки/, проходящего через цветные фильтры в ячейке. Для модуляции излучения ячейки на ее поверхности после цветного фильтра наносится тончайший слой нейтрального светофильтра по плотности, соответствующей коэффициентам двоичного кода, который определяет разрядную иерархию каждой ячейки в излучателе 50. Первая триада имеет три ЖК-ячейки R, G, В без нейтральных светофильтров, их излучение соответствует первому /старшему/ разряду в коде. Вторая триада имеет три ЖК-ячейки R, G, В с нейтральными светофильтрами кратности 2х, их излучение соответствует второму разряду в коде. Третья триада имеет ЖК-ячейки с нейтральными светофильтрами 4х, их излучение соответствует третьему разряду в коде и т.д, в восьмой триаде ЖК-ячейки имеют нейтральные светофильтры 128х, их излучение соответствует восьмому разряду в коде /младшему/. Распределение двоичных коэффициентов по разрядам кода, соответствующая им плотность нейтральных светофильтров и вес разряда в коде приведены в таблице 1.

Формирование смешанного излучения в каждом излучателе осуществляется использованием излучений восьми триад ЖК-ячеек, по числу разрядов в коде. При отсутствии сигнала с импульсного усилителя /блоков 20, 21, 22/ световой поток от лампы подсветки [3, C.487, 489] ячейку не проходит /поглощается/, при наличии сигнала с импульсного усилителя световой луч от лампы подсветки уже соответствующего цвета [3, с.489] проходит ЖК-ячейку, ее цветной фильтр, после которого ослабляется нейтральным светофильтром соответственно таблице 1. Излучения ЖК-ячеек в восьми триадах после прохода своих нейтральных светофильтров смешиваются в фоконе, на выходе с которого яркость, насыщенность и цветовой тон результирующего излучения определяются взаимным соотношением составляющих трех цветов и их яркости соответственно кодов каждого цветового сигнала R, G, В. В излучателях 501-768 применяются 18432 ЖК-ячеек /768×8×3/, в панели ЖК-монитора [3, с.488, 490] при разрешении 1024×768 используются 786432 триады, т.е. 2359296 ЖК-ячеек, в 128 раз больше.

Входами блока 23 являются входы излучателей 501-768, подключенные к соответствующим выходам блоков 20, 21, 22 импульсных усилителей. Выходные окна фоконов 51 проецируют излучение излучателей 50 на отражатель пьезодефлектора 26, а выходные торцы фоконов образуют вертикальную линейку. Диаметр цветового круга на отражателе составляет 0,02 мм, длина отражателя составляет 15,36 мм /768×0,02/.

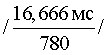

Излучатели 501-768 через фоконы 51 и отражатель пьезодефлектора 26, расположенный в задней фокальной плоскости проекционного объектива 29, оптически соединены с матовым экраном 30, расположенным во внешней фокальной плоскости проекционного объектива 29. Свободный торец пьезодефлектора 26 с отражателем совершает колебания с частотой 3,9 кГц и выполняет строчную развертку всех 768 строк кадра с повтором их за кадр 130:65 раз слева направо и 65 раз справа налево. Частоту колебаний пьезодефлектора задает делитель 31 частоты, выполняющий деление частоты 46,8 кГц, поступающей на второй управляющий вход монитора, 12:1, 46,8 кГц:12=3,9 кГц. Делитель 3 частоты выдает с первого выхода тактовые импульсы 383,3856 МГц для заполнения входных регистров 34 /фиг.3/ последовательными кодами с информационных входов монитора:

fT=730×60 Гц ×1024 ×8раз =383,3856 МГц,

где 780 - число строк в кадре, 60 Гц - частота кадров,

1024 - число отсчетов в строке, 8 - число разрядов в коде.

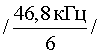

С второго выхода делитель 3 частоты выдает импульсы дискретизации видеосигналов: fД=780×60 Гц ×1024=47,9232 МГц. С третьего выхода блока 3 идут сигналы UВЫД 8 МГц, являющиеся сигналами выдачи кодов из регистров 45, 48 /фиг.4, 5/ блоков 35 регистров. Частота строчной развертки с видеоадаптера ПК, поступающая на второй управляющий вход монитора, 46,8 кГц, длительность поступающего с видеоадаптера кадра составляет

,

,

длительность строки 21,367 мкс

.

.

Длительность воспроизводимого кадра также 16,666 мс, частота строк воспроизводимого кадра 7,8 кГц

,

,

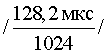

длительность строки на экране в кадре 128,2 мкс

.

.

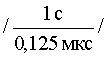

Период следования кодов с выходов блоков регистров 35125 нс

.

.

Частота сигналов выдачи UВЫД с блока 3 составляет: 8 МГц

.

.

Число повторов разверток строк за кадр 16,666 мс составляет: 130 раз

,

,

65 раз 768 строк развертываются слева направо и 65 раз справа налево /фиг.2/.

Делитель 31 частоты /фиг.1/ выполняет деление частоты 46,8 кГц на 12. Импульсы частотой 3,9 кГц идут на вход задающего генератора 32, из которых генератор 32 формирует прямоугольные импульсы с периодом следования двух строк 256,4 мкс /128,2×2/, поступающие в выходной каскад 33, формирующий управляющее напряжение треугольной формы /фиг.2/ с периодом 256,4 мкс, поступающие на вход усилителя 25. Усилитель 25 усиливает управляющее напряжение, поступающее на внутренний электрод 55 пьезодефлектора 26. На внешние электроды 56, 57 поступают соответствующие напряжения с источников 27, 28 опорных напряжений /фиг.7/. Торец пьезодефлектора 26 с отражателем приходит в колебательное движение [5, с.122] с частотой 3,9 кГц и производит развертку одновременно всех строк кадра, за период кадра развертка строк повторяется 130 раз. С приходом на входы элемента И 1 строчного и кадрового синхроимпульсов сигнал с элемента И открывает первый ключ 2, остающийся открытым все время работы цифрового монитора. Через ключ 2 рабочая частота fр поступает на вход делителя 3 частоты, импульсы 60 Гц с выхода элемента И 1 поступают в триггеры 7 и 6. Сигнал с первого выхода триггера 6 открывает четвертый 8, шестой 12 и восьмой 16 ключи, через которые последовательные коды R, G, В с 1-3 информационных входов монитора поступают во входные регистры 34 /фиг.3/ накопителей 9, 13, 17 кодов нечетного кадра, в которых за период первого кадра первые 45 и вторые 48 регистры блоков 351-384 регистров заполняются кодами первого кадра /786432 кода/. С приходом второго кадрового синхроимпульса в триггер 6, сигнал с второго его выхода закрывает ключи 8, 12, 16 и открывает ключи 10, 14, 18, через которые коды сигналов R, G, В поступают в входные регистры 34 накопителей 11, 15, 19 кодов четного кадра, заполняя в них регистры блоков 351-384 кодами второго кадра. Одновременно в период второго кадра коды первого кадра всех 768 строк параллельно выдаются с накопителей 9, 13, 17 в блоки 20, 21, 22 импульсных усилителей. Сигналы разрядов кодов, усиленные импульсными усилителями, поступают в соответствующие излучатели 501-768, в них запитывают свои ЖК-ячейки в триадах излучателя 50. Фоконы 511-768 проецируют излучения на отражатель пьезодефлектора 26, выполняющего строчную развертку всех строк кадра одновременно. Частота строк 7,8 кГц, длительность строки 128,2 мкс. За период кадра развертка строк повторяется 130 раз, выполняя увеличение яркости воспринимаемого зрителем изображения в 99840 раз //768×130/ против прототипа. Кадровая развертка отсутствует. С приходом третьего кадрового синхроимпульса 60 Гц в триггер 6 сигнал с его первого выхода закрывает ключи 10, 14, 18 и открывает ключи 8, 12, 16, и процессы повторяются. Каждый из блоков импульсных усилителей 20, 21, 22 содержит импульсные усилители по числу строк в кадре и числу разрядов в коде 6144 /768×8/. В трех блоках их 18432 штук. Период следования кодов на входы блоков 20, 21, 22 составляет 125 нс

.

.

Применяемые импульсные усилители должны иметь время срабатывания менее 125 нс, например в микросхемах усилителей-формирователей 533АД6 время срабатывания 18 нс [6, с.128]. Микроэлектронные технологии позволяют выполнить 6144 импульсных усилителя в одной микросхеме. Разрешающий элемент на отражателе пьезодефлектора 0,02 мм, кратность увеличения проекционным объективом 29 принимается 20 крат, тогда размеры экрана 30 составят:

по горизонтали 20×/0,02 мм×1024/=409,6 мм,

по вертикали 20×/0,02 мм×768/=307,2 мм,

по диагонали 512 мм или 21 дюйм.

Проекционный объектив 29, кроме того, позволяет уменьшать или увеличивать размеры изображения на экране.

Работа накопителей 9, 11, 13 и 15, 17, 19 кодов /фиг.4, 5/. С второго выхода делителя 3 частоты первый импульс UД /47,9232 МГц/ обнуляет разряды входного регистра 34 в накопителях 9, 13, 17. Входные регистры 34 в блоках 9, 13, 17 заполняются первым кодом первой строки первого кадра. Следующий импульс UД выдает код из входного регистра 34 в параллельном виде на входы блоков 351-384 регистров, а в них на информационные /четвертые/ входы разрядов регистров 451-8. Импульс с первого выхода триггера 7 открывает первый ключ 36, который пропускает импульсы UД в распределитель 41 импульсов, с 1024-х выходов которого эти импульсы в качестве тактовых последовательно с первого по 1024-й поступают на первые управляющие входы разрядов первых восьми регистров 45, и коды первой строки сигнала R /G, В/ заполняют регистры 451-8, причем сигналы первых разрядов кодов поступают в регистр 451, сигналы вторых разрядов кодов поступают в разряды регистра 452 и т.д., сигналы восьмых разрядов кода поступают в разряды 458. Сигнал с последнего выхода /1024/ распределителя 41 импульсов закрывает ключ 36 и открывает ключ 38, пропускающий импульсы UД на вход третьего распределителя 43 импульсов, выходы которого последовательно с первого по 1024-й подключены к первым управляющим входам разрядов вторых восьми регистров 481-8. Регистры 48 заполняются кодами сигналов R второй строки первого кадра. По заполнении регистров 48 сигнал с последнего выхода /1024/ распределителя 43 импульсов закрывает ключ 38 и является первым управляющим выходом во второй блок 352 регистров. В блоке 352 этот сигнал открывает первый ключ 36, и идет процесс заполнения кодами сигнала R третьей строки первого кадра регистров 45, затем кодами четвертой строки регистров 48. Аналогичные процессы заполнения кодами 5 и 6, 7 и 8... 767 и 768 строк идут в блоках 353-384. Параллельно эти же процессы идут в накопителях 13 и 17 кодов нечетного кадра кодами G, В. По заполнении кодами первого кадра накопителей 9, 13, 17 кодов нечетного кадра следует заполнение кодами накопителей 11, 15, 19 кодов четного кадра. А коды с накопителей 9, 13, 17 со всех блоков 351-384 и параллельно всех 768 строк выдаются в блоки 20, 21, 22 импульсных усилителей. Для этого сигнал с первого управляющего выхода блока 35384 поступает параллельно на четвертые управляющие входы всех 384-х блоков 35 регистров, открывает второй ключ 37, пропускающий импульсы UВЫД 8 МГц во второй распределитель 42 импульсов, с первого по 1024-й выходов которого они последовательно выдают коды первой и второй строк с регистров 451-8 и 481-8 в последовательности с первого по 1024-й разряды регистров. Параллельно идут выдачи кодов 3-768-й строк с блоков 352-384. По окончании выдачи кодов строк /развертка идет слева направо/ сигнал с 1024-го выхода распределителя 42 импульсов через диод закрывает ключ 37, поступает в счетчик 46 импульсов и открывает четвертый ключ 39 и пятый ключ 40. Ключ 39 пропускает сигналы UВЫД 8 МГц в четвертый распределитель 44 импульсов, который выдает коды первой и второй строк из регистров 451-8 и 481-8, начиная не с первых разрядов регистров, а с последних /1024-х/. Необходимость в этом определяется тем, что при развертке строк справа налево /фиг.2/ отсчеты строк начинаются с последнего /1024/ разряда регистра и идут к первому разряду регистров. Такой порядок выдачи кодов выполняется подключением выходов распределителя 44 импульсов к входам разрядов регистров в обратном порядке: первый выход подключается к вторым управляющим входам последних /1024-х/ разрядов в регистрах 45 и 48, а последний выход подключается к вторым управляющим входам первых разрядов в регистрах 45 и 48. Причем импульсы выдачи с 2-го 42 и четвертого 44 распределителей импульсов выдают коды с регистров 45 и 48, что осуществляется соответствующим подключением выходов распределителей 42, 44 к входам разрядов регистров 45 и 48. Таким образом выдаются параллельно коды 768 строк со всех блоков 351-384 при развертке справа налево. По окончании выдачи кодов всех строк сигнал с 1024-го выхода распределителя 44 поступает в второй счетчик 49 импульсов, закрывает ключ 39 и через открытый ключ 40 опять открывает второй ключ 37, следует выдача кодов строк с блоков 351-384, идет развертка всех строк кадра второй раз слева направо, т.е. с первого отсчета строки к 1024-му. Этот процесс повторяется 65 раз. При 65-й развертке слева направо счетчик 46 импульсов формирует двоичный код числа 65 /1000001/, дешифратор 47 выдает сигнал, закрывающий второй ключ 37, пятый ключ 40 и обнуляет разряды регистров 451-8. При развертке 65-й справа налево импульс с 1024-го выхода распределителя 44 импульсов закрывает ключ 39, счетчик 49 формирует двоичный код числа 65, дешифратор 492 выдает сигнал, обнуляющий разряды регистров 481-8. Следует новый процесс накопления кодов накопителями 9, 13, 17 кодов нечетного кадра /третьего/, параллельно идет выдача кодов второго кадра из накопителей 11, 15, 19 кодов четного кадра в блоки 20, 21, 22, и развертка его на экране 30. Чередуясь, процессы накопления и выдачи кодов кадров идут до выключения монитора.

Работа цифрового монитора.

В исходном состоянии ключи в закрытом состоянии. С приходом на вход элемента И 1 кадрового и строчного синхроимпульсов сигнал с элемента И открывает ключ 2 и поступает на входы триггеров 6, 7. Импульс с первого выхода триггера 6 открывает ключи 8, 12, 16. Накопители 9, 13, 17 кодов заполняются кодами первого кадра сигналов R, G, В. С приходом второго сигнала 60 Гц в триггер 6 импульс с второго его выхода закрывает ключи 8, 12, 16 и открывает ключи 10, 14, 18. Следует выдача кодов первого кадра, из накопителей 9, 13, 17 в блоки 20, 21, 22 импульсных усилителей и накопление кодов второго кадра в накопителях 11, 15, 19. При третьем кадре идет накопление кодов накопителями 9, 13, 17 и выдача кодов второго кадра из накопителей 11, 15, 19. Чередуясь, процессы повторяются. Усиленные сигналы разрядов кодов запитывают соответствующие ЖК-ячейки в триадах излучателей 501-768, излучения которых проецируются фоконами 51 на отражатель пьезодефлектора 26, выполняющего развертку параллельно всех строк кадра с повтором их за кадр 130 раз. Так как развертка идет всех строк одновременно, то отпадает необходимость в кадровой развертке. Проекционный объектив 29 проецирует цветное изображение на матовый экран 30 с увеличением его в 20 раз /вариант/. Технические характеристики заявляемого цифрового монитора представлены в таблице 2.

Использованные источники

1. Патент №2265286 кл. Н04N 9/18, бюл.33 от 27.11.05, прототип.

2. Л.М.Кучекян. Световоды. М., 1973, с.77.

3. Мураховский В.И. Устройство компьютера. «АСТ-ПРЕСС книга», 2003, с.486-490.

4. Колесниченко О.В, Шишигин И.В. Аппаратные средства PC. 5-е изд-е, СПб, 2004, с.473, 477, 483.

5. Фридлянд И.В, Сошников В.Г. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118 рис.5.5, с.122 рис.5.10.

6. Цифровые интегральные микросхемы. М.И.Богданович и др. Справочник, Минск, 1991, с.128.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ МОНИТОР | 2006 |

|

RU2306676C1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2006 |

|

RU2310287C1 |

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2006 |

|

RU2303334C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

| ЦИФРОВОЙ МОНИТОР | 2005 |

|

RU2292664C1 |

| ЦИФРОВОЙ ПРОЕКТОР | 2005 |

|

RU2292663C1 |

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2005 |

|

RU2304362C2 |

| ЦИФРОВОЙ МОНИТОР | 2004 |

|

RU2265286C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2298297C1 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2292127C1 |

Изобретение относится к аппаратным средствам персонального компьютера и может быть использовано как монитор в персональном компьютере (ПК). Технический результат - увеличение усредненной яркости изображения на экране, воспринимаемой зрителем, в 99840 раз достигается тем, что осуществляется развертка кадра всеми активными строками одновременно и повтором их развертки за кадр 130 раз. При этом в цифровой монитор вводятся второй триггер, три накопителя кодов нечетного кадра, три накопителя кодов четного кадра, блок модуляции излучений выполнен из каналов по числу активных строк в кадре, каждый из которых содержит фокусирующий конус световода (фокон), излучатель трех основных цветов и лампу подсветки. 7 ил., 2 табл.

Цифровой монитор, содержащий последовательно соединенные элемент И, первый ключ, делитель частоты и второй ключ, третий ключ, вход которого подключен к входу второго ключа, первый триггер, первым, вторым, третьим управляющими входами цифрового монитора являются соответственно сигнальный вход первого ключа, первый и второй входы элемента И, первым, вторым, третьим информационными входами цифрового монитора являются соответственно объединенные входы четвертого и пятого ключей, шестого и седьмого ключей, восьмого и девятого ключей, первый выход первого триггера подключен к первым управляющим входам третьего, четвертого, шестого и восьмого ключей, к вторым управляющим входам второго, пятого, седьмого и девятого ключей, второй выход первого триггера подключен к вторым управляющим входам третьего, четвертого, шестого и восьмого ключей и к первым управляющим входам второго, пятого, седьмого и девятого ключей, содержащий первый, второй, третий блоки импульсных усилителей, последовательно соединенные блок строчной развертки, вход которого подключен к первому входу элемента И, усилитель и пьезодефлектор с отражателем на торце, источник положительного опорного напряжения, выход которого подключен к вторым входам усилителя и пьезодефлектора, источник отрицательного опорного напряжения, выход которого подключен к третьим входам усилителя и пьезодефлектора, блок строчной развертки содержит последовательно соединенные делитель частоты, задающий генератор и выходной каскад, проекционный объектив, в задней фокальной плоскости которого расположен отражатель пьезодефлектора, во внешней фокальной плоскости проекционного объектива расположен матовый экран, отличающийся тем, что в него введены второй триггер, вход которого подключен к выходу элемента И, первый, второй, третий накопители кодов нечетного кадра, первый, второй, третий накопители кодов четного кадра, первый выход делителя частоты подключен параллельно к первым /тактовым/ входам первого, второго, третьего накопителей кодов нечетного кадра и первого, второго, третьего накопителей кодов четного кадра, первый выход второго триггера подключен параллельно к вторым управляющим входам с первого по третий накопителей кодов нечетного кадра, второй выход второго триггера подключен параллельно к вторым управляющим входам с первого по третий накопителей кодов четного кадра, третьи управляющие входы накопителей кодов нечетного кадра и накопителей кодов четного кадра объединены и подключены к третьему выходу делителя частоты, четвертые управляющие входы первого, второго, третьего накопителей кодов нечетного кадра объединены и подключены к выходу второго ключа, четвертые управляющие входы первого, второго, третьего накопителей кодов четного кадра объединены и подключены к выходу третьего ключа, информационный вход первого накопителя кодов нечетного кадра подключен к выходу четвертого ключа, информационный вход первого накопителя кодов четного кадра подключен к выходу пятого ключа, выходы первого накопителя кодов нечетного кадра и выходы первого накопителя кодов четного кадра соответствующим образом объединены и подключены к входам первого блока импульсных усилителей, информационный вход второго накопителя кодов нечетного кадра подключен к выходу шестого ключа, информационный вход второго накопителя кодов четного кадра подключен к выходу седьмого ключа, выходы второго накопителя кодов нечетного кадра и выходы второго накопителя кодов четного кадра соответствующим образом объединены и подключены к входам второго блока импульсных усилителей, информационный вход третьего накопителя кодов нечетного кадра подключен к выходу восьмого ключа, информационный вход третьего накопителя кодов четного кадра подключен к выходу девятого ключа, выходы третьего накопителя кодов нечетного кадра и выходы третьего накопителя кодов четного кадра соответствующим образом объединены и подключены к входам третьего блока импульсных усилителей, блок модуляции излучений выполнен из числа каналов по числу активных строк в кадре, каждый из которых содержит фокусирующий конус световода /фокон/, излучатель трех основных цветов, включающий восемь триад ЖК-ячеек и размещенный во входном окне фокона, и лампу подсветки, расположенную излучающей стороной в сторону входных окон фоконов, входами блока модуляции излучений являются входы излучателей, подключенные к соответствующим выходам с первого по третий блоков импульсных усилителей, излучающие стороны излучателей через выходные окна фоконов, отражатель пьезодефлектора и проекционный объектив оптически соединены с матовым экраном, первый, второй, третий накопители кодов нечетного кадра и первый, второй, третий накопители кодов четного кадра идентичны, каждый содержит входной регистр, вход которого является информационным входом в накопителе кодов нечетного кадра и в накопителе кодов четного кадра, и блоки регистров по числу половины активных строк кадра, первым управляющим /тактовым/ входом накопителя кодов нечетного /четного/ кадра является первый управляющий вход входного регистра, вторым управляющим входом является первый управляющий вход первого блока регистров, третьим являются объединенные вторые управляющие входы всех блоков регистров, четвертым - объединенные третьи управляющие входы всех блоков регистров и второго управляющего входа входного регистра, выходами каждого накопителя кодов нечетного кадра и накопителя кодов четного кадра являются первые с первого по восьмой и вторые с первого по восьмой выходы всех блоков регистров, блоки регистров идентичны, каждый включает с первого по пятый ключи, с первого по четвертый распределители импульсов, первые восемь регистров, последовательно соединенные первый счетчик импульсов и первый дешифратор, вторые восемь регистров, последовательно соединенные второй счетчик импульсов и второй дешифратор, информационным входом блока регистров являются поразрядно объединенные четвертые /информационные/ входы разрядов первых и вторых восьми регистров, подключенные к выходам с первого по восьмой входных регистров, выходы разрядов в каждом регистре объединены, выходы первых восьми регистров являются первым с первого по восьмой выходами блока регистров, выходы вторых восьми регистров являются вторым с первого по восьмой выходами блока регистров, подключенные к соответствующим входам соответствующего блока импульсных усилителей, управляющих входов четыре: первым является первый управляющий вход первого ключа в первом блоке регистров, подключенный к первому выходу второго триггера, в остальных блоках регистров первый управляющий вход первого ключа каждого последующего блока регистров подключен к первому управляющему выходу каждого предыдущего блока регистров, в последнем блоке регистров первый управляющий выход подключен параллельно к четвертым управляющим входам всех блоков регистров, вторым управляющим входом являются объединенные сигнальные входы первого и третьего ключей, подключенные к второму выходу делителя частоты цифрового монитора, третьим управляющим входом являются объединенные сигнальные входы второго и четвертого ключей, подключенные к третьему выходу делителя частоты, четвертым управляющим входом является первый управляющий вход второго ключа, через диод подключенный к первому управляющему выходу последнего блока регистров, выход первого ключа подключен к входу первого распределителя импульсов, выходы которого последовательно с первого по последний /1024/ подключены к первым управляющим входам разрядов первых восьми регистров, последний его выход /1024/ подключен к второму управляющему входу первого ключа и к первому управляющему входу третьего ключа, выход второго ключа подключен к входу второго распределителя импульсов, выходы которого последовательно с первого по 1024-й подключены к вторым управляющим входам разрядов последовательно с первого по 1024-й первых восьми регистров и к вторым управляющим входам разрядов последовательно с первого по 1024-й вторых восьми регистров, последний выход /1024/ второго распределителя импульсов подключен к входу первого счетчика импульсов, к первым управляющим входам четвертого и пятого ключей и через диод к второму управляющему входу второго ключа, выход первого дешифратора подключен к второму управляющему входу пятого ключа, к третьим управляющим входам разрядов первых восьми регистров и через диод к второму управляющему входу второго ключа, выход третьего ключа подключен к входу третьего распределителя импульсов, выходы которого последовательно с первого по последний подключены к первым управляющим входам разрядов вторых восьми регистров: последний /1024/ его выход подключен к второму управляющему входу третьего ключа и является первым управляющим выходом блока регистров, выход четвертого ключа подключен к входу четвертого распределителя импульсов, выходы которого последовательно с первого по последний /1024/ подключены к вторым управляющим входам разрядов первых восьми регистров и вторых восьми регистров, начиная с последнего /1024-го/ разряда к первому разряду регистров, последний выход /1024/ четвертого распределителя импульсов подключен к входу второго счетчика импульсов, к второму управляющему входу четвертого ключа и к сигнальному входу пятого ключа, выход которого подключен к первому управляющему входу второго ключа, выход второго дешифратора подключен параллельно к третьим управляющим входам разрядов вторых восьми регистров, каждый блок импульсных усилителей содержит импульсных усилителей по числу активных строк в кадре и числу разрядов в коде.

Авторы

Даты

2007-09-20—Публикация

2006-02-20—Подача