Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных сигналов, в структуре аналоговых микросхем различного функционального назначения (операционных усилителях, непрерывных стабилизаторов напряжения, перемножителей сигналов и т.д.).

Известны широкополосные дифференциальные усилители (ДУ) на основе параллельно-балансных каскадов, которые стали основой построения современных аналоговых микросхем [1, 2]. Проблема улучшения их параметров - входного сопротивления, частотных свойств - относится к числу основных проблем современной аналоговой микросхемотехники.

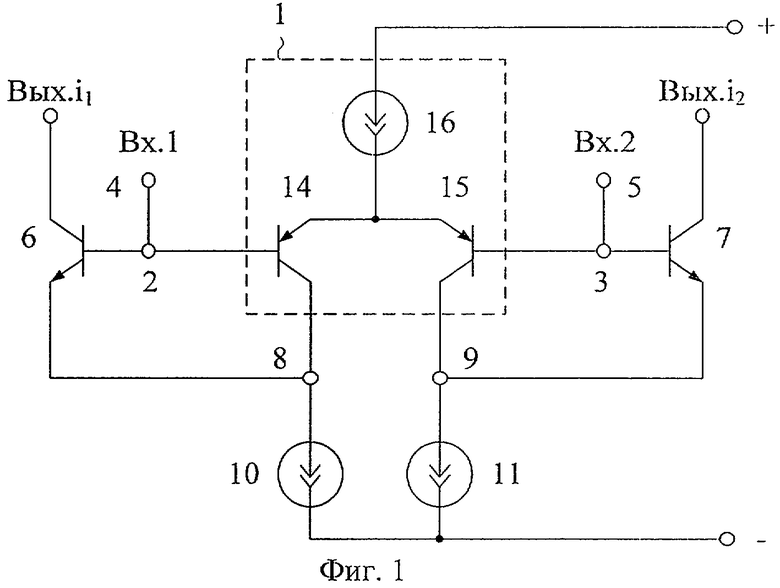

Ближайшим прототипом заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5.424.681, fig. 8, содержащий входной дифференциальный каскад 1, первый 2 и второй 3 входы которого соединены с соответствующими входами дифференциального усилителя 4 и 5 и базами первого 6 и второго 7 выходных транзисторов, а первый 8 и второй 9 токовые выходы - подключены к первому 10 и второму 11 токостабилизирующим двухполюсникам.

Существенный недостаток известного ДУ состоит в том, что он имеет небольшие значения входного сопротивления (Rвх) для переменного тока, зависящие от статического тока эмиттера Iэ и коэффициента усиления по току базы (β) входных транзисторов. Для повышения Rвх приходится уменьшать Iэ - переводить транзисторы в микрорежим, что уменьшает коэффициент усиления ДУ по напряжению (Kу). Второй способ повышения Rвх - введение резисторов Rэ в эмиттерной цепи входных транзисторов, которые также уменьшают Kу.

Основная цель предполагаемого изобретения состоит в увеличении входного сопротивления дифференциального усилителя в широком диапазоне частот без ухудшения его коэффициента усиления по напряжению.

Поставленная цель достигается тем, что в дифференциальном усилителе, содержащем входной дифференциальный каскад 1, первый 2 и второй 3 входы которого соединены с соответствующими входами дифференциального усилителя 4 и 5 и базами первого 6 и второго 7 выходных транзисторов, а первый 8 и второй 9 токовые выходы подключены к первому 10 и второму 11 токостабилизирующим двухполюсникам, предусмотрены новые связи - эмиттер первого 6 выходного транзистора связан со вторым 9 токовым выходом входного дифференциального каскада 1, а эмиттер второго 7 выходного транзистора соединен с первым 8 токовым выходом входного дифференциального каскада 1.

На фиг.1 приведена схема ДУ-прототипа.

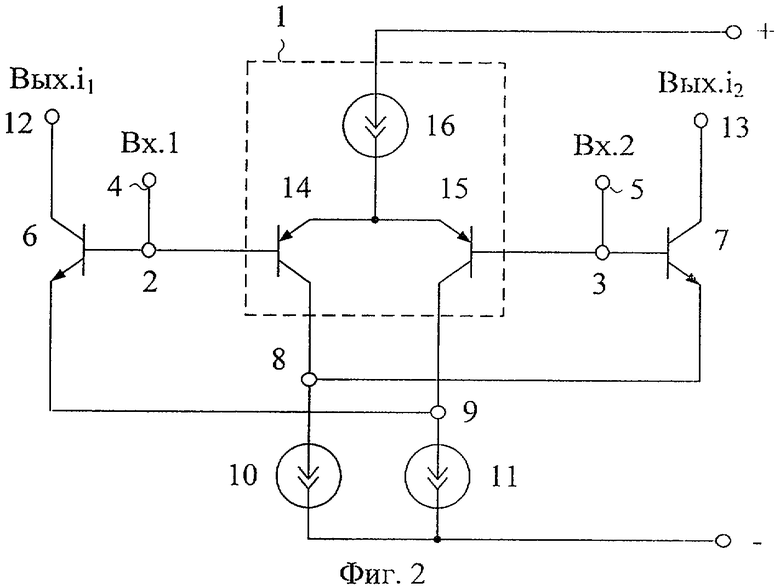

На фиг.2 показана схема заявляемого устройства в соответствии с формулой изобретения.

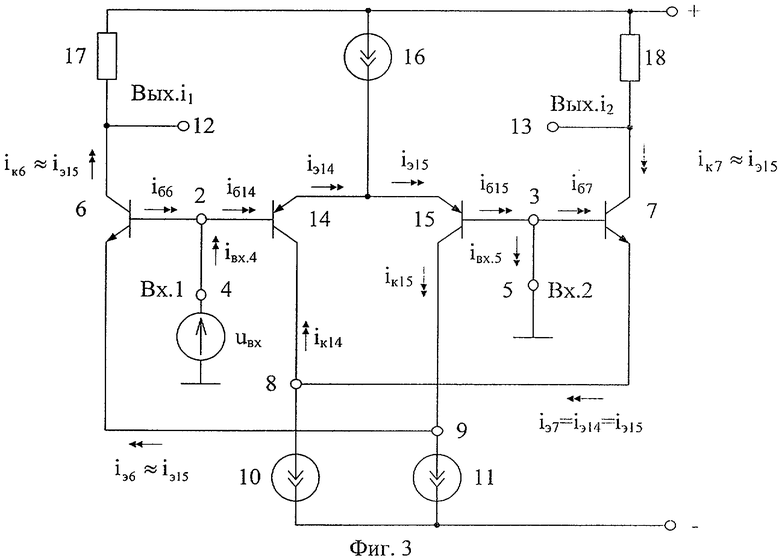

На фиг.3 показаны переменные токи в схеме фиг.2 для положительной полуволны входного напряжения.

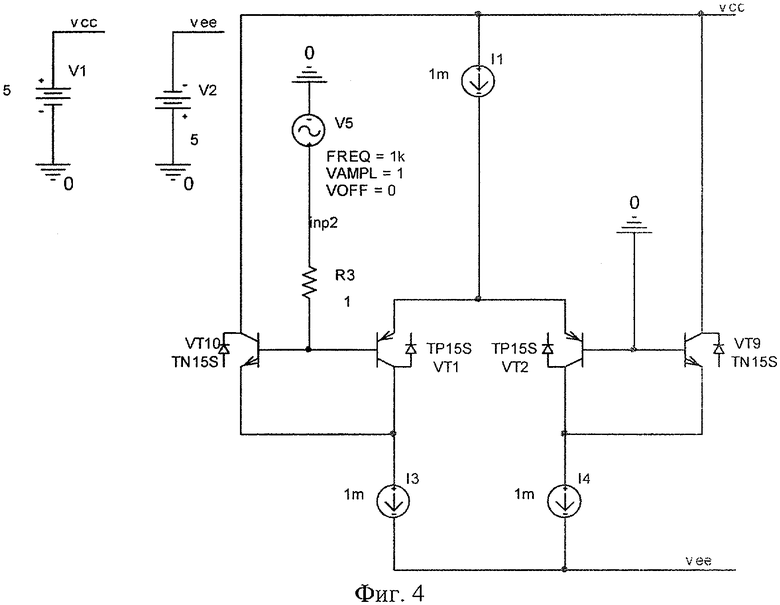

На фиг.4 показана схема фиг.1 в среде компьютерного моделирования PSpice на моделях интегральных транзисторах ФГУП НПП «Пульсар».

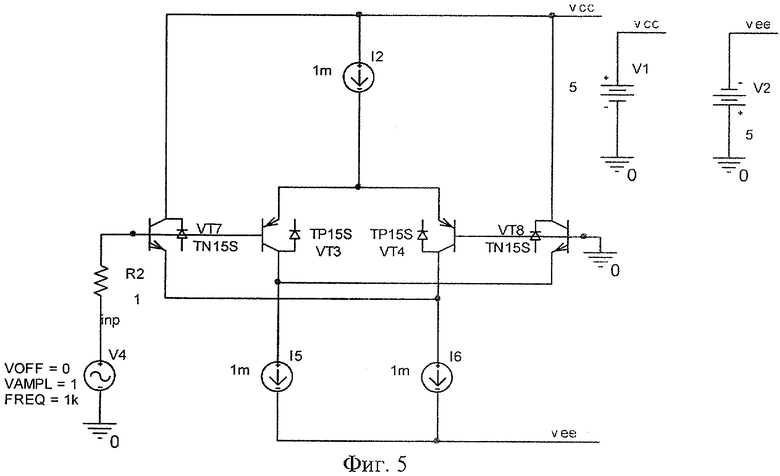

На фиг.5 показана схема фиг.3 в среде компьютерного моделирования PSpice на моделях интегральных транзисторах ФГУП НПП «Пульсар».

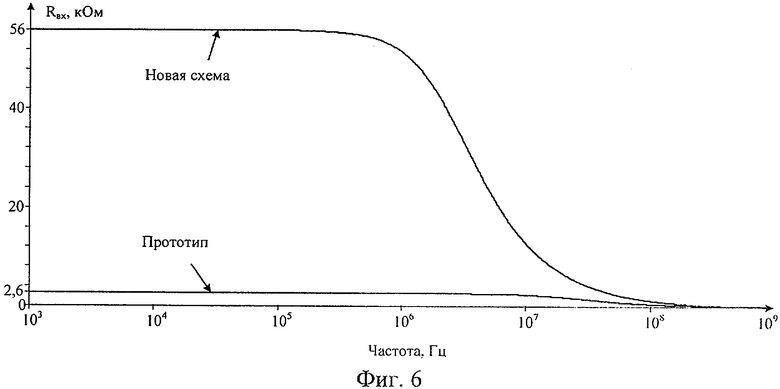

На фиг.6 показаны графики зависимости входного сопротивления ДУ-прототипа (фиг.4) и новой схемы (фиг.5) от частоты.

Предлагаемый дифференциальный усилитель (фиг.2) содержит входной дифференциальный каскад 1, первый 2 и второй 3 входы которого соединены с соответствующими входами дифференциального усилителя 4 и 5 и базами первого 6 и второго 7 выходных транзисторов, а первый 8 и второй 9 токовые выходы подключены к первому 10 и второму 11 токостабилизирующим двухполюсникам. Эмиттер первого 6 выходного транзистора связан со вторым 9 токовым выходом входного дифференциального каскада 1, а эмиттер второго 7 выходного транзистора соединен с первым 8 токовым выходом входного дифференциального каскада 1.

На фиг.2 коллекторы транзисторов 6 и 7 являются токовыми выходами заявляемого устройства 12 и 13, к которым могут быть подключены нагрузки 17 и 18 (фиг.3), а входной дифференциальный каскад 1 выполнен на транзисторах 14 и 15 и источнике тока 16.

Рассмотрим работу схемы фиг.3.

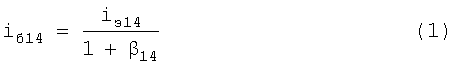

При подаче на вход 4 переменного напряжения uвх в цепи входа 2 входного параллельно-балансного каскада 1 появляется приращение тока iб14:

где iэ14 - приращение тока эмиттера транзистора 14 входного дифференциального каскада 1;

β14 - коэффициент усиления по току базы транзистора 14 входного дифференциального каскада 1.

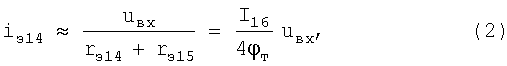

Причем

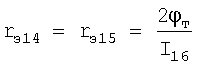

где

φт≈25 мВ - температурный потенциал;

I16 - суммарный ток общей эмиттерной цепи транзисторов 14 и 15.

Таким образом

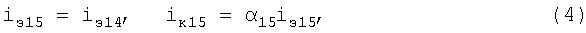

Так как в эмиттерную цепь каскада 1 включен источник не изменяющегося под действием сигнала тока I16=I0=const, то ток эмиттера и, следовательно, ток коллектора транзистора 15 будут связаны с током iэ14 следующими соотношениями:

где α15≈0,98-0,99 - коэффициент усиления по току эмиттера транзистора 15 входного дифференциального каскада 1.

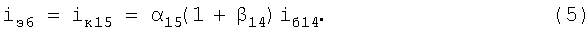

При этом токи в выходных узлах 8 и 9 будут иметь равную величину, но противоположные направления, а все приращение тока iк15 передается в эмиттер транзистора 6:

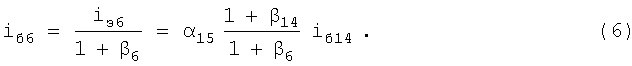

Поэтому ток базы транзистора 6

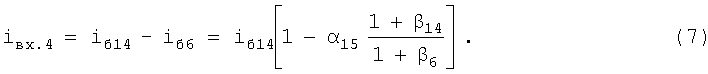

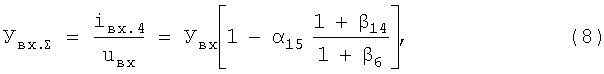

Как следствие, во входном узле 4 произойдет вычитание двух близких по величине, но противоположных по направлению переменных токов iб14 и iб6:

Учитывая, что α15≈0,98÷0,99≈1, а транзисторы в заявляемой схеме имеют близкие по величине коэффициенты усиления по току базы β14≈β6 из (7) получаем, что суммарный входной ток iвх.4 и, следовательно, входная проводимость заявляемого устройства могут быть близки к нулю

Учитывая, что α15≈0,98÷0,99≈1, а транзисторы в заявляемой схеме имеют близкие по величине коэффициенты усиления по току базы β14≈β6 из (7) получаем, что суммарный входной ток iвх.4 и, следовательно, входная проводимость заявляемого устройства могут быть близки к нулю

где

Это является существенным преимуществом усилителя фиг.3.

С другой стороны, входная проводимость усилителя-прототипа фиг.1

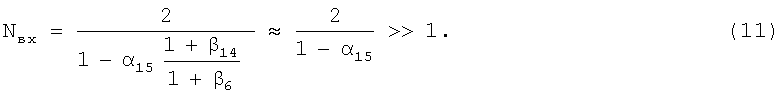

Поэтому заявляемый усилитель имеет по сравнению с прототипом в Nвх раз большее входное сопротивление, где

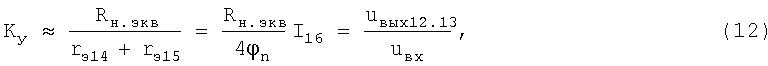

Можно показать, что повышение Rвх в Nвх раз в заявляемом устройстве обеспечивается без снижения коэффициента усиления по напряжению Kу=uвых/uвх.

Действительно, в схеме фиг.3, так же как и в ДУ-прототипе фиг.1, для дифференциального выхода

где Rн.экв≈R17+R18 - эквивалентное сопротивление нагрузки.

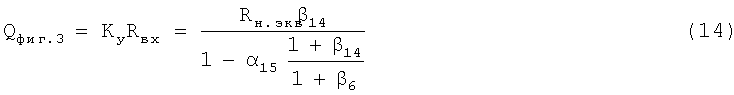

Поэтому с учетом (2) можно для сравниваемых схем фиг.1 и фиг.3 найти произведение Q

Следовательно, обобщенный показатель качества в ДУ фиг.3 Q=KуRвх в Nвх раз больше, чем в ДУ-прототипе, где Nвх>>1.

Полученные выше аналитические оценки подтверждаются результатами компьютерного моделирования (фиг.6) схем фиг.4 и фиг.5 - заявляемый ДУ имеет в 21 раз большее значение входного сопротивления.

Источники информации

1. Алексеенко А.Г. Основы микросхемотехники. Элементы морфологии микроэлектронной аппаратуры / А.Г.Алексеенко. - Изд. 2-е, перераб. и доп. - М.: Сов. радио, 1977. - 408 с.

2. Проектирование и применение операционных усилителей / Под ред. Дж.Грэма, Дж.Тоби, Л.Хьюлсмана // Пер. с англ. В.И.Левина и И.М.Хейфеца под. ред. к.т.н. И.Н.Теплюка. - М.: Изд-во Мир, 1974.

3. Патент США №5.424.681, fig.8.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416147C1 |

| ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390909C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2419192C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416146C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2009 |

|

RU2419961C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450423C1 |

| КОМПЛЕМЕНТАРНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2444115C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных сигналов, в структуре аналоговых микросхем различного функционального назначения (операционных усилителях, непрерывных стабилизаторов напряжения, перемножителей сигналов и т.д.). Технический результат: увеличение входного сопротивления в широком диапазоне частот без ухудшения коэффициента усиления по напряжению. Дифференциальный усилитель (ДУ) содержит входной дифференциальный каскад (ДК) (1), первый (2) и второй (3) входы которого соединены с соответствующими входами (4) и (5) ДУ и базами первого (6) и второго (7) выходных транзисторов (Т), а первый (8) и второй (9) токовые выходы ДК (1) - подключены к первому (10) и второму (11) токостабилизирующим двухполюсникам. Эмиттер первого (6) выходного Т связан со вторым (9) токовым выходом ДК (1), а эмиттер второго (7) выходного Т соединен с первым (8) токовым выходом ДК (1). 6 ил.

Дифференциальный усилитель с повышенным входным сопротивлением, содержащий входной дифференциальный каскад (1), первый (2) и второй (3) входы которого соединены с соответствующими входами дифференциального усилителя (4) и (5) и базами первого (6) и второго (7) выходных транзисторов, а первый (8) и второй (9) токовые выходы подключены к первому (10) и второму (11) токостабилизирующим двухполюсникам, отличающийся тем, что эмиттер первого (6) выходного транзистора связан со вторым (9) токовым выходом входного дифференциального каскада (1), а эмиттер второго (7) выходного транзистора соединен с первым (8) токовым выходом входного дифференциального каскада (1).

| US 5424681 A, 13.06.1995 | |||

| Дифференциальный усилитель | 1985 |

|

SU1246340A1 |

| US 4602172, 22.07.1986 | |||

| US 3551832, 29.12.1970 | |||

| ДОСТАЛ И | |||

| Операционные усилители | |||

| - М.: Мир, 1982, с.83, рис.3.17. | |||

Авторы

Даты

2010-10-10—Публикация

2009-02-20—Подача