Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях (ОУ)).

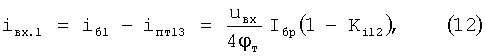

Существует несколько базовых архитектур дифференциальных усилителей (ДУ). Одна из них (фиг.1), реализованная на n-p-n и p-n-p транзисторов, относится к классической архитектуре. Впервые данная схема использована в операционном усилителе µA741. Комплементарные дифференциальные усилители (КДУ) данного класса, наряду с типовым параллельно-балансным каскадом, стали основным усилительным элементом многих аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

Наиболее близким по сущности к заявляемому техническому решению является схема КДУ фиг.1, представленная в монографии Якубовского С.В., Барканова М.В., Кудряшова Б.П. «Аналоговые и цифровые интегральные схемы». - М., Радио и связь, 1979. - С.224, рис.4.12а, которая также присутствует в большом числе патентов, например, [1-17].

Существенный недостаток известного КДУ фиг.1 состоит в том, что он имеет повышенные значения входных статических токов (Iвх.1, Iвх.2) и сравнительно невысокое входное дифференциальное сопротивление (Rвх).

Основная задача предлагаемого изобретения состоит в уменьшении абсолютных значений входных токов ДУ и их температурного дрейфа.

Дополнительная задача - повышение входного сопротивления.

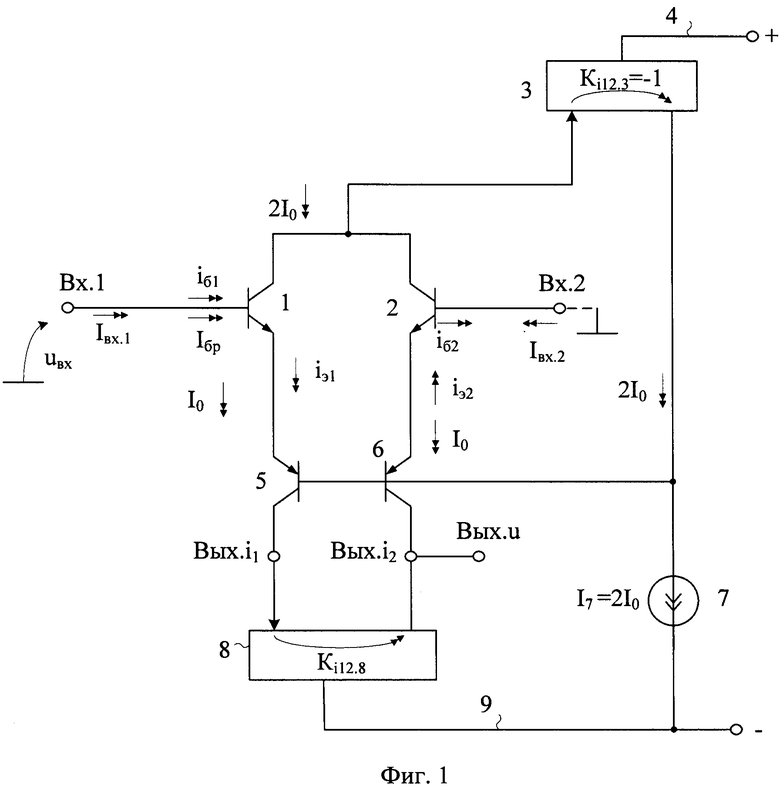

Поставленные задачи решается тем, что в комплементарном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, коллекторы которых объединены и подключены ко входу первого 3 токового зеркала, согласованного с первой 4 шиной источника питания, первый 5 и второй 6 выходные транзисторы, базы которых объединены и соединены с выходом первого 3 токового зеркала, токостабилизирующиий двухполюсник 7, эмиттер первого 5 выходного транзистора соединен с эмиттером первого 1 входного транзистора, эмиттер второго 6 выходного транзистора соединен с эмиттером второго 2 входного транзистора, коллекторы первого 5 и второго 6 выходных транзисторов связаны с цепью нагрузки 8, согласованной со второй 9 шиной источника питания, предусмотрены новые элементы и связи - в схему введены первый 10 и второй 11 дополнительные транзисторы, эмиттеры которых объединены и связаны с базой вспомогательного транзистора 12, база первого 10 дополнительного транзистора соединена с эмиттером первого 1 входного транзистора, база второго 11 дополнительного транзистора соединена с эмиттером второго 2 входного транзистора, коллектор первого 10 дополнительного транзистора соединен со входом первого 13 токового зеркала, согласованного первой 4 шиной источника питания, причем выход первого 13 дополнительного токового зеркала соединен с базой первого 1 входного транзистора, коллектор второго 11 дополнительного транзистора соединен со входом второго 14 токового зеркала, согласованного первой 4 шиной источника питания, причем выход второго 14 дополнительного токового зеркала соединен с базой второго 2 входного транзистора, коллектор вспомогательного транзистора 12 соединен с базами первого 5 и второго 6 выходных транзисторов, а эмиттер вспомогательного транзистора 12 через токостабилизирующий двухполюсник 7 соединен со второй 9 шиной источника питания.

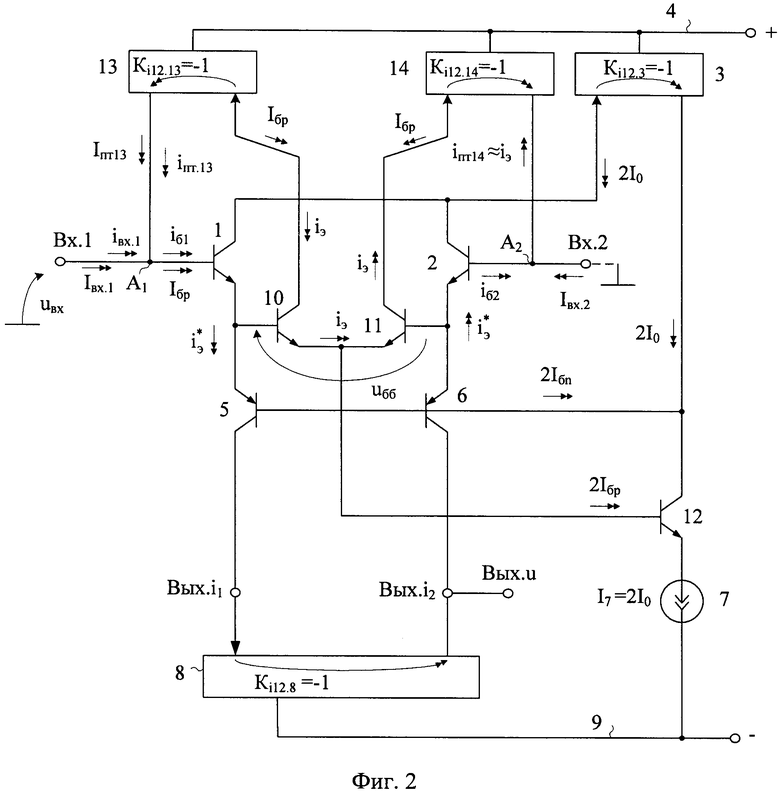

Схема усилителя-прототипа представлена на чертеже фиг.1. На чертеже фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения.

На чертеже фиг.3 показана схема, соответствующая п.2 и п.3 формулы изобретения.

На чертеже фиг.4 и фиг.5 представлены схемы комплементарного дифференциального усилителя - прототипа без цепей компенсации входных токов (фиг.4) и заявляемого КДУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПН «Пульсар».

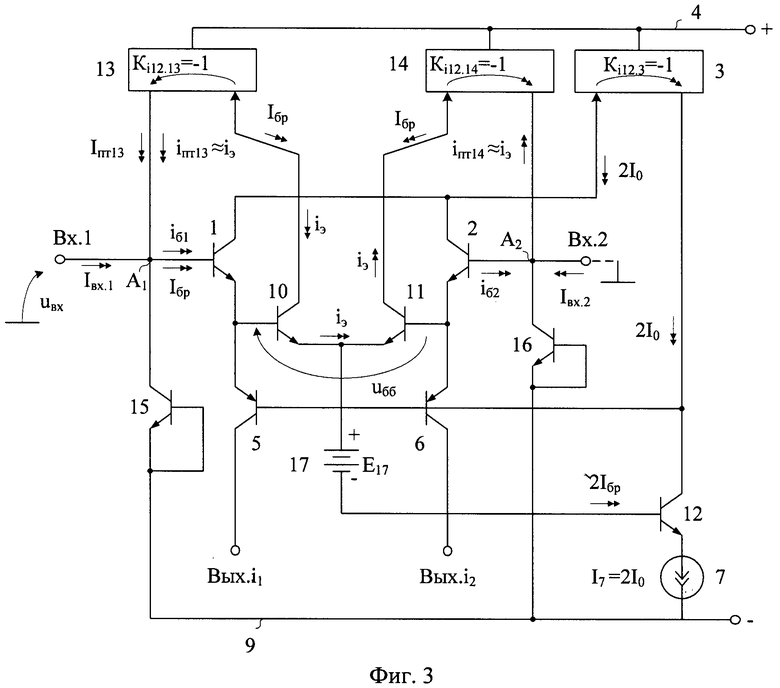

На чертеже фиг.6 приведены температурные зависимости входного тока Iвх.1 сравниваемых схем КДУ фиг.4, фиг.5.

Графики фиг.7 характеризуют частотную зависимость входного сопротивления схем КДУ фиг.4, фиг.5.

Комплементарный дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, коллекторы которых объединены и подключены ко входу первого 3 токового зеркала, согласованного с первой 4 шиной источника питания, первый 5 и второй 6 выходные транзисторы, базы которых объединены и соединены с выходом первого 3 токового зеркала, токостабилизирующиий двухполюсник 7, эмиттер первого 5 выходного транзистора соединен с эмиттером первого 1 входного транзистора, эмиттер второго 6 выходного транзистора соединен с эмиттером второго 2 входного транзистора, коллекторы первого 5 и второго 6 выходных транзисторов связаны с цепью нагрузки 8, согласованной со второй 9 шиной источника питания. В схему введены первый 10 и второй 11 дополнительные транзисторы, эмиттеры которых объединены и связаны с базой вспомогательного транзистора 12, база первого 10 дополнительного транзистора соединена с эмиттером первого 1 входного транзистора, база второго 11 дополнительного транзистора соединена с эмиттером второго 2 входного транзистора, коллектор первого 10 дополнительного транзистора соединен со входом первого 13 токового зеркала, согласованного первой 4 шиной источника питания, причем выход первого 13 дополнительного токового зеркала соединен с базой первого 1 входного транзистора, коллектор второго 11 дополнительного транзистора соединен со входом второго 14 токового зеркала, согласованного первой 4 шиной источника питания, причем выход второго 14 дополнительного токового зеркала соединен с базой второго 2 входного транзистора, коллектор вспомогательного транзистора 12 соединен с базами первого 5 и второго 6 выходных транзисторов, а эмиттер вспомогательного транзистора 12 через токостабилизирующий двухполюсник 7 соединен со второй 9 шиной источника питания. В качестве цепи нагрузки могут использоваться различные токовые зеркала, а также резисторы.

Токовые зеркала 3, 13 и 14 могут выполняться по классическим схемам как на биполярных, так и на полевых КМОП транзисторах. Причем реализация токовых зеркал 3 и 14 на КМОП активных элементах предпочтительнее.

В схеме фиг.3, в соответствии с п.2 формулы изобретения, в схему введены первый 15 и второй 16 транзисторы терморадиационной компенсации, находящейся в режиме отсечки, коллекторы которых соединены с соответствующими базами первого 1 и второго 2 входных транзисторов. При этом объединенные базы и эмиттеры этих транзисторов могут подключаться ко второй 9 шине питания.

В схеме фиг.3, в соответствии с п.3 формулы изобретения, объединенные эмиттеры первого 10 и второго 11 дополнительных транзисторов связаны с базой вспомогательного транзистора 12 через цепь согласования потенциалов 17.

Введение цепи согласования потенциалов 17 в соответствии с п.3 формулы изобретения позволяет повысить идентичность статических токов транзистора 1 и токового зеркала 13, которая зависит от степени влияния напряжения коллектор-база на β транзисторов. В качестве цепи согласования потенциалов 17 могут применяться прямосмещенные p-n переходы.

Рассмотрим факторы, определяющие входные токи и входные сопротивления КДУ фиг.2.

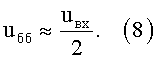

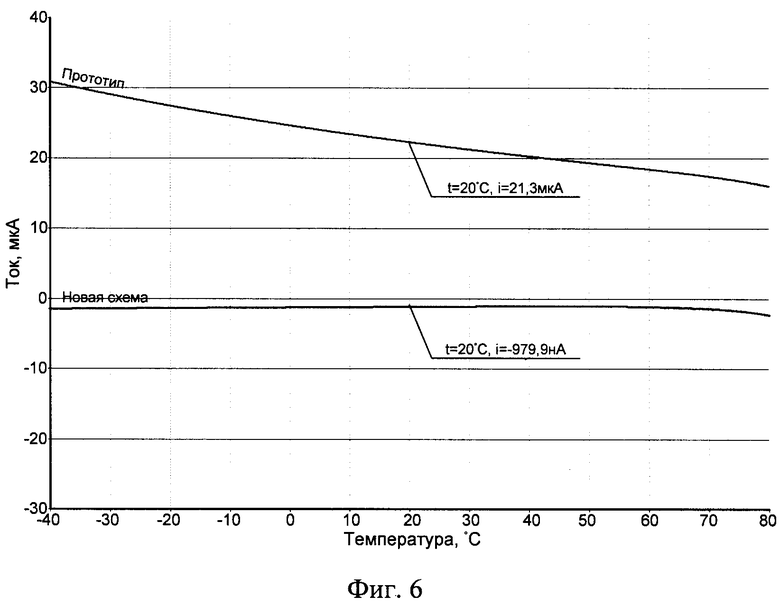

Если ток двухполюсника 7 равен величине 2I0, то токи коллектора (Iк.i), базы (Iб.i) транзисторов и выходные токи Iпт13=Iпт14 токовых зеркал 13, 14 схемы фиг.2:

где Iб,i=Iэ.i/βi, - ток базы n-p-n (Iб.р) транзисторов 1, 2, 5, 6 схемы при эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы i-го транзистора.

Поэтому входные статические токи КДУ при Ki12,13=Ki12.14=Ki12=1 существенно уменьшаются:

где Iпт.13, Iпт.14 - выходные статические токи токовых зеркал 13 и 14. Приращение входного напряжения КДУ (uвх) вызывает изменение напряжения между базами транзисторов 10 и 11, работающих при токах эмиттера, равных половине тока базы транзистора 12:

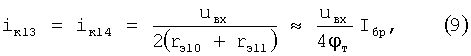

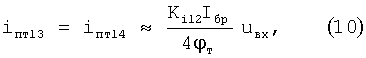

Поэтому переменные коллекторные токи транзисторов 10 и 11, а также соответствующие выходные токи токовых зеркал 13 и 14:

где  - сопротивления эмиттерных p-n переходов транзисторов 10 и 11; φт=25 мВ - температурный потенциал.

- сопротивления эмиттерных p-n переходов транзисторов 10 и 11; φт=25 мВ - температурный потенциал.

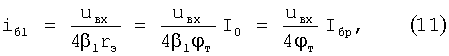

С другой стороны, приращение тока базы входного транзистора 1, определяющее входное сопротивление Rвх КДУ-прототипа:

где  - сопротивления эмиттерных p-n переходов транзисторов 1, 2, 5 и 6.

- сопротивления эмиттерных p-n переходов транзисторов 1, 2, 5 и 6.

Таким образом, входной ток КДУ фиг.2 по входу «Вх.1» и его входное дифференциальное сопротивление

Учитывая, что Ki12=1, из (13) следует, что в предлагаемом КДУ существенно (в Nвх-раз) повышается входное дифференциальное сопротивление, где

Данные выводы подтверждаются результатами компьютерного моделирования КДУ фиг.6 и фиг.7 - входной статический ток (Iвх.1) заявляемого КДУ уменьшается более чем на порядок. Кроме этого, повышается (см. фиг.7) более чем на порядок входное сопротивление заявляемого КДУ для переменного тока.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с КДУ-прототипом.

БИБЛИОГРАФИЧИСКИЙ СПИСОК

1. Интегральные микросхемы. Операционные усилители [Текст]: справочник. М., Издательский дом «Додэка-XXI», 2001, - С.90. Высоковольтный операционный усилитель 1443 УД1.

2. Патент США №4.030.044 fig.1.

3. Патент США №3.786.362 fig.1.

4. Патент США №3.660.773 fig.4.

5. Достал И. Операционные усилители [Текст] / И.Достал. М., Мир, 1982. - С.79, рис.3.14в.

6. Патент США №4.074.205.

7. Патент США №4.560.948 fig.6.

8. Конелли Д. Аналоговые итегральные схемы [Текст] Д.Конелли. - М., Мир, 1977. - С.85.

9. Патент США №4.429.284 fig.1.

10. Патент США №4.855.684 fig.4.

11. Патент ФРГ 2633952 Fig.5.

12. Патент США №4.059.808 fig.5.

13. Патент Японии №57-5364 H03F 3/343.

14. А.св. СССР 375754.

15. А.св. СССР 1107281.

16. А.св. СССР 1107279.

17. M.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411640C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С НИЗКООМНОЙ НАГРУЗКОЙ | 2011 |

|

RU2444114C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455758C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2468504C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455757C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в уменьшении абсолютных значений входных токов ДУ и их температурного дрейфа. Комплементарный дифференциальный усилитель содержит первый и второй входные транзисторы, первое и второе токовые зеркала, дополнительное токовое зеркало, первый и второй выходные транзисторы, первый и второй дополнительные транзисторы, вспомогательный транзистор. 2 з.п. ф-лы, 7 ил.

1. Комплементарный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, коллекторы которых объединены и подключены ко входу первого (3) токовою зеркала, согласованного с первой (4) шиной источника питания, первым (5) и второй (6) выходные транзисторы, базы которых объединены и соединены с выходом первого (3) токового зеркала, токостабилизирующиий двухполюсник (7), эмиттер первого (5) выходного транзистора соединен с эмиттером первого (1) входного транзистора, эмиттер второго (6) выходного транзистора соединен с эмиттером второго (2) входного транзистора, коллекторы первого (5) и второго (6) выходных транзисторов связаны с цепью нагрузки (8), согласованной со второй (9) шиной источника питания, отличающийся тем, что в схему введены первый (10) и второй (11) дополнительные транзисторы, эмиттеры которых объединены и связаны с базой вспомогательного транзистора (12), база первого (10) дополнительного транзистора соединена с эмиттером первого (1) входного транзистора, база второго (11) дополнительного транзистора соединена с эмиттером второго (2) входного транзистора, коллектор первого (10) дополнительного транзистора соединен со входом первого (13) токового зеркала, согласованного первой (4) шиной источника питания, причем выход первого (13) дополнительного токового зеркала соединен с базой первого (1) входного транзистора, коллектор второго (11) дополнительного транзистора соединен со входом второго (14) токового зеркала, согласованного первой (4) шиной источника питания, причем выход второго (14) дополнительного токового зеркала соединен с базой второго (2) входного транзистора, коллектор вспомогательного транзистора (12) соединен с базами первого (5) и второго (6) выходных транзисторов, а эмиттер вспомогательного транзистора (12) через токостабилизирующий двухполюсник (7) соединен со второй (9) шиной источника питания.

2. Комплементарный дифференциальный усилитель по п.1, отличающийся тем, что в схему введены первый (15) и второй (16) транзисторы терморадиационной компенсации, находящейся в режиме отсечки, коллекторы которых соединены с соответствующими базами первого (1) и второго (2) входных транзисторов.

3. Комплементарный дифференциальный усилитель по п.1, отличающийся тем, что объединенные эмиттеры первого (10) и второго (11) дополнительных транзисторов связаны с базой вспомогательного транзистора (12) через цепь согласования потенциалов (17).

| С.В.ЯКУБОВСКИЙ и др | |||

| Аналоговые и цифровые интегральные схемы | |||

| - М.: Советское радио, 1979, с.223-227, рис.4.12а | |||

| US 4030044 А, 14.06.1977 | |||

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2394362C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2320078C1 |

Авторы

Даты

2012-05-10—Публикация

2011-03-11—Подача